$\frac{\text{MITSUBISHI} \left< \text{DIGITAL ASSP} \right>}{M66011FP}$

SERIAL BUS CONTROLLER

#### DESCRIPTION

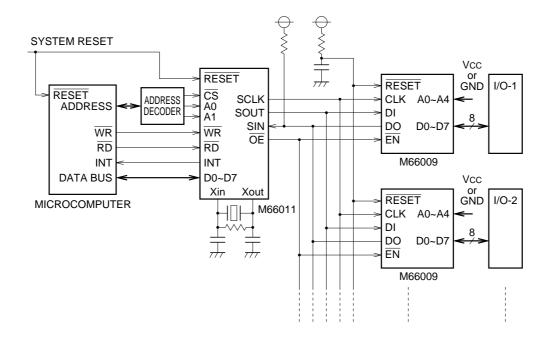

M66011 Semiconductor Integrated Circuit is a serial bus controller. It converts 2-byte parallel data that arrives from microcomputer into serial and outputs it to serial bus. It also converts serial data input from serial bus into parallel and outputs it to microcomputer.

The M66011 is used for the extension of microcomputer I/O ports and two-way communication with peripheral equipment connected with serial buses.

#### FEATURES

- Compatible with general-purpose 8-bit microprocessor busses

- TTL level input (one microcomputer side)

- Interrupt output

- Schmitt input (RESET, CS, SIN)

- Low power dissipation

- Wide operating temperature range (Ta = -20 to  $75^{\circ}$ C)

#### APPLICATION

Microcomputer I/O port extension, etc.

## FUNCTION

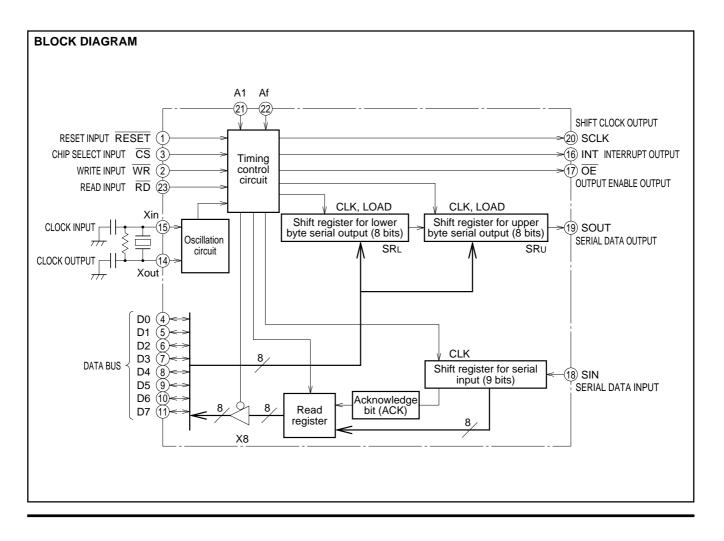

M66011 integrated circuit is a serial bus controller. It is equipped with two 8-bit shift registers used to convert parallel input data into serial for output, as well as with one 9-bit shift register used to convert serial input data into parallel for output.

This IC receives and sends 8-bit parallel in communication with microcomputer. In communication with serial bus, it outputs 16-bit data and receives 9-bit data.

Serial data input/output uses four signal lines: shift clock output SCLK, serial data output SOUT, serial data input SIN and output enable output  $\overline{\text{OE}}$ .

Serial data is output synchronously with shift clock fall edges, while input of serial data is synchronous with shift clock rise edges.

Serial communication data consists of one prefixed acknowledge bit and 8 data bits.

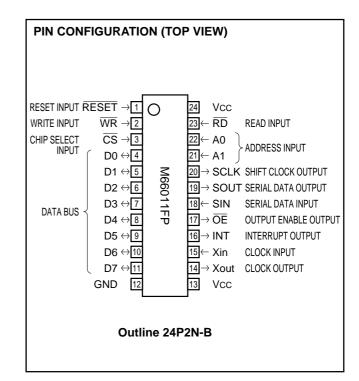

#### **PIN DESCRIPTIONS**

| Pin    | Name                 | Input/Output | Functions                                                                                                           |

|--------|----------------------|--------------|---------------------------------------------------------------------------------------------------------------------|

| RESET  | Reset input          | Input        | "L" level: M66011 is reset to initial state.                                                                        |

| CS     | Chip select input    | Input        | "L" level: M66011 becomes accessible.                                                                               |

| WR     | Write input          | Input        | "L" level: 8-bit parallel data is input from data bus and written on M66011.                                        |

| RD     | Read input           | Input        | "L" level: Serial-input 8-bit data or internal status data is output in parallel to data bus.                       |

| D0~D7  | Data bus             | Input/Output | Bi-directional 8-bit bus buffer. Used for communication with microcomputer (data write and read).                   |

| SCLK   | Shift clock output   | Output       | Outputs clock to serial bus. Active ("H") status normally.                                                          |

| SOUT   | Serial date output   | Output       | Outputs serial data to serial bus. Active ("H") status normally.                                                    |

| SIN    | Serial data input    | Input        | Inputs serial data from serial bus.                                                                                 |

| ŌĒ     | Output enable output | Output       | "L" when serial data communication is executed. Active ("H") otherwise.                                             |

| INT    | Interrupt output     | Output       | Outputs interrupt command signal to microcomputer when serial data communication is finished.                       |

| A0, A1 | Address input        | Input        | Selects register on which data is written during write operation. Designates data to be read during read operation. |

| Xin    | Clock input          | Input        | Connected to ceramic resonator, generates M66011 activation clock and                                               |

| Xout   | Clock output         | Output       | SCLK output clock.<br>If clock is input from outside, use pin Xin and keep pin Xout open.                           |

| Vcc    | Positive supply pin  |              | Connected positive supply (5V).                                                                                     |

| GND    | Grounding pin        |              | Used for grounding (0V).                                                                                            |

## OPERATION

1. Write operation

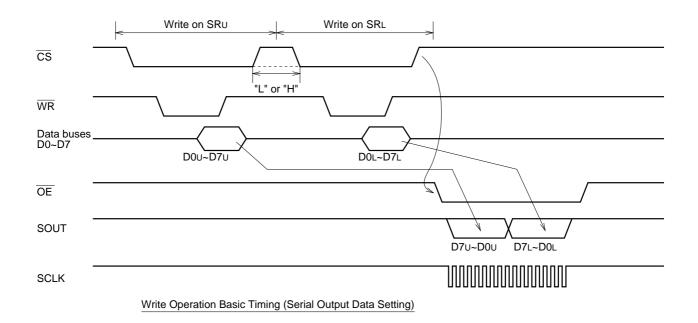

(1) Serial output data setting

The M66011 has two built-in 8-bit shift registers. They are used to set serial output data.

When the address setting is (A1, A0) = (0, 1), 8-bit data on data bus is written on the upper byte serial output shift register (SRU). When the address setting is (A1, A0) = (0, 0), the data is written on the lower byte serial output shift register (SRL). In either case, data write starts when WR is on the "L" level.

(2) Status register setting

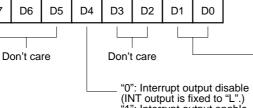

When the address setting is (A1, A0) = (1, 1), written data becomes the setting of status register in M66011. (Refer to the table below.)

#### Write Operation Basic Functions (Note 1)

| CS | A1 | A0 | RD | WR |                                                                                                   | Functions |                           |

|----|----|----|----|----|---------------------------------------------------------------------------------------------------|-----------|---------------------------|

| 0  | 0  | 0  | 1  | 0  | <ul> <li>Lower byte serial output shift register</li> </ul>                                       | <         | Data bus data             |

| 0  | 0  | 1  | 1  | 0  | <ul> <li>Upper byte serial output shift register</li> </ul>                                       | <         | Data bus data             |

| 0  | 1  | 1  | 1  | 0  | <ul> <li>Shift clock divider ratio register</li> <li>Interrupt output control register</li> </ul> | ·         | (Note 2)<br>Data bus data |

Note 1: Figure "0" indicates "L" level, while "1" indicates "H" level.

D7

Note 2

| D1 | D0 | Divider ratio |

|----|----|---------------|

| 0  | 0  | 1/2           |

| 0  | 1  | 1/4           |

| 1  | 0  | 1/8           |

| 1  | 1  | 1/16          |

1": Interrupt output enable

(INT output shifts from "L" to "H" when serial communication is completed.)

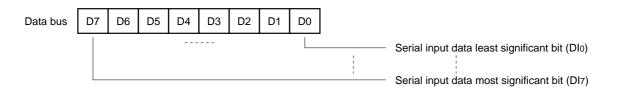

2. Read operation

When a read access arrives, M66011 outputs data in parallel to data bus. The data output at this moment may be serial input data, or data on internal status resister. When a read access arrives when the address setting is (A1, A0) = (1, 0), 8-bits of 9-bit serial input data, excluding the acknowledge bit, is output to data bus While  $\overline{RD}$  is "L". When a read access arrives when the address setting is (A1, A0) =(1, 1), interrupt control register, busy flag, serial-input acknowledge bit and clock dividing ratio register are output to data bus while  $\overline{RD}$  is "L".

### **Read Operation Basic Function**

| CS | A1 | A0 | RD | WR |          | Functions                   |  |  |

|----|----|----|----|----|----------|-----------------------------|--|--|

| 0  | 1  | 0  | 0  | 1  | Date bus | Gerial input shift register |  |  |

| 0  | 1  | 1  | 0  | 1  | Data bus | Katus register              |  |  |

#### **Read Output Data Details**

(1) When (A1, A0) is (1, 0):

#### (2) When (A1, A0) is (1, 1):

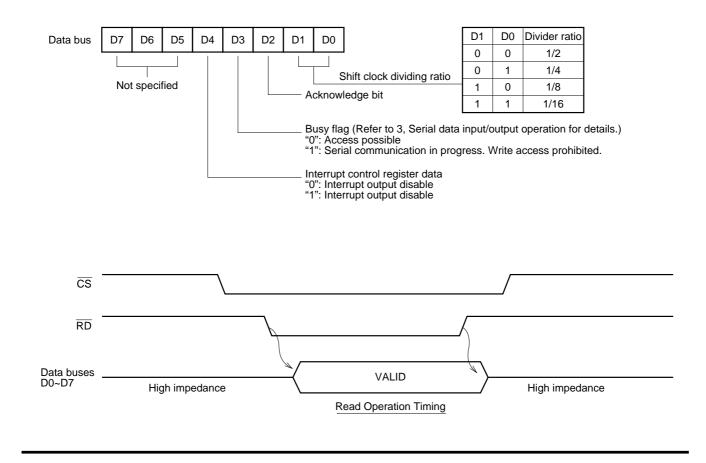

3. Serial data input/output operation

A cycle of 16-bit serial output data setting and serial data communication starts with a write access given by microcomputer to transmission shift registers in M66011.

M66011 has two 8-bit shift registers, on for upper byte (SRU), the other for lower byte (SRL). If the  $\overline{CS}$  status rises from "L" to "H" after a write access is given to SRL, serial data communication is started. SRU 8-bit data and SRL, 8-bit data are output in series in this order. Output of each data starts from its most significant bit.

At the  $\overline{CS}$  rise edge, busy flag in M66011 is set, and  $\overline{OE}$  output shifts from "H" to "L". Shift clock SCLK and serial data SOUT are then output.

At SCLK fall edges, serial output shift register executes shifting operation, and data on shift register is output in series from pin SOUT. Serial input data from pin SIN is taken into input shift register at SCLK 8T thru 16T rise edges. However, data taken in at 8T rise edge is processed as acknowledge bit, while data taken in at 9T thru 16T rise edges are processed as data bits. After the SCLK 16T rise edge, the status of SOUT and  $\overline{OE}$  shifts to "H" after one bit's delay of SCLK, and busy flag is reset. When interrupt output is being set to enable, INT output is set.

#### (Remarks)

- (1) If CS rises after write operation is executed on SRL only and not on SRU, SRU data is unstable.

- (2) When write operations executed on SRL, M66011 becomes ready for start of serial communication and stands by for detection of  $\overline{CS}$  rise. However, if a read access is given after data is written on SRL while  $\overline{CS}$  is maintained on "L" level, this standby status is canceled. To resume serial communication in this case, rewrite data on SRL and raise  $\overline{CS}$ .

Serial Communication Timing Chart

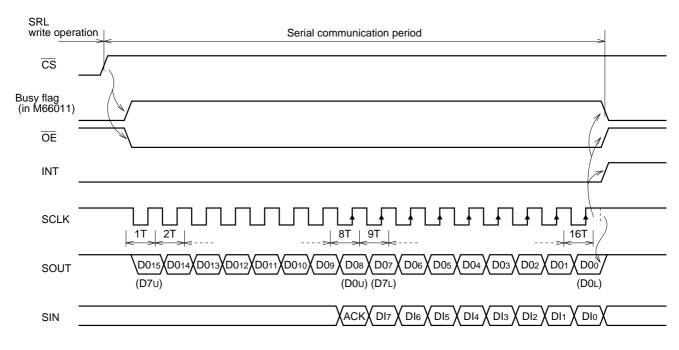

4. Shift clock output

Shift clock output pin (SCLK) outputs clock pulses generated by ceramic resonator oscillation circuit connected between pins X<sub>in</sub> and X<sub>out</sub>, or divided clock pulses input via pin X<sub>in</sub> from external clock. The dividing ratio can be selected from among 1/2, 1/4, 1/8 and 1/16.

5. Interrupt output

When interrupt output control register is set to "1" (interrupt output enable), the status of this output shifts from "L" to "H" at the end of a serial communication cycle, and an interrupt command is given to microcomputer. Interrupt output "H" is reset when read accessed.

When interrupt output control register is set to "0" (interrupt output disable), the status of this output is retained on the "L" level.

6. Conditions when reset

If "L" is input to  $\overline{\text{RESET}}$ , M66011 are put under the conditions as specified below:

| Pin name                  | Status                          |

|---------------------------|---------------------------------|

| OE, SCLK and SOUT outputs | Active ("H")                    |

| Internal busy flag        | Reset ("L")                     |

| Acknowledge bit register  | Set ("H")                       |

| INT output                | Disable (continuous "L" output) |

| Divider ratio             | 1/2                             |

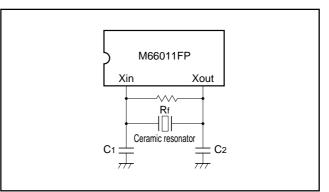

7. Oscillation circuit

An example of circuit connection and circuit constants are given below for the case where a ceramic resonator is used.

#### **Clock Oscillation Circuit**

| Maker  | Ceramic<br>resonator | Frequency<br>(MHz) | C1<br>(pF)        | C2<br>(pF)        | Rf<br>(MΩ) |

|--------|----------------------|--------------------|-------------------|-------------------|------------|

|        | CSA4.00 MG 040       | 4.0                | 100               | 100               | 1.0        |

| Murata | CST4.00 MGW 040      | 4.0                | 100<br>(built-in) | 100<br>(built-in) | 1.0        |

| Mfg.   | CSA8.00 MT           | 8.0                | 30                | 30                | 1.0        |

|        | CSA8.00 MTW          | 8.0                | 30<br>(built-in)  | 30<br>(built-in)  | 1.0        |

#### ABSOLUTE MAXIMUM RATINGS

| Symbol | Parameter           | Ratings          | Unit |

|--------|---------------------|------------------|------|

| Vcc    | supply voltage      | -0.5 ~ +7.0      | V    |

| VI     | Input voltage       | -0.5 ~ VCC + 0.5 | V    |

| Vo     | Output voltage      | -0.5 ~ Vcc + 0.5 | V    |

| Pd     | Power dissipation   | 500              | mW   |

| Tstg   | Storage temperature | -60 ~ 150        | °C   |

## RECOMMENDED OPERATIONAL CONDITIONS

| Symbol | Parameter             |      | Unit |      |      |

|--------|-----------------------|------|------|------|------|

| Symbol | Farameter             | Min. | Тур. | Max. | Unit |

| Vcc    | Supply voltage        | 4.5  | 5.0  | 5.5  | V    |

| Vi     | Input voltage         | 0    |      | Vcc  | V    |

| Vo     | Output voltage        | 0    |      | Vcc  | V    |

| Topr   | Operating temperature | -20  |      | 75   | °C   |

### **ELECTRICAL CHARACTERISTICS** (Ta = $-20 \sim 75^{\circ}$ C, Vcc = 5V ± 10% and GND = 0V unless otherwise noted)

| Course had | Parameter                           |                                        | Toot open ditions       |         |      |         |      |

|------------|-------------------------------------|----------------------------------------|-------------------------|---------|------|---------|------|

| Symbol     | Paramet                             | er                                     | Test conditions         | Min.    | Тур. | Max.    | Unit |

| VIH        | "H" input voltage                   | WR, RD, A0, A1,                        |                         | 2.0     |      |         | V    |

| VIL        | "L" input voltage                   | D0~D7                                  |                         |         |      | 0.8     | V    |

| VIH        | "H" input voltage                   | Xin                                    |                         | Vcc×0.8 |      |         | V    |

| VIL        | "L" input voltage                   |                                        |                         |         |      | Vcc×0.2 | V    |

| VT+        | Positive threshold voltage          |                                        |                         |         |      | 2.4     | V    |

| VT-        | Negative threshold voltage          | $\overline{RESET}, \overline{CS}, SIN$ |                         | 0.7     |      |         | V    |

| Vh         | Hysteresis width                    |                                        |                         |         | 0.6  |         | V    |

| Voh        | "H" output voltage                  | D0~D7, SCLK,                           | IOH=-4mA                | Vcc-0.8 |      |         | V    |

| Vol        | "L" output voltage                  | INT, SOUT, OE                          | IOL=4mA                 |         |      | 0.4     | V    |

| li         | Input leak current                  |                                        | VI=0~VCC                |         |      | ±10     | μA   |

| loz        | Output leak current<br>in off state | D0~D7                                  | Vo=0~Vcc                |         |      | ±10     | μA   |

| Icc        | Quiescent supply current            |                                        | VI=VCC, GND output open |         |      | 200     | μA   |

| CI/O       | Input/output pin capacitance        | D0~D7                                  |                         |         |      | 20      | pF   |

Note 3: Standard value measuring conditions: Ta =  $25^{\circ}$ C and Vcc = 5V

SERIAL BUS CONTROLLER

| O washed                            | Demonster                                             | Testereditions  |        | Limits  |        |        |  |

|-------------------------------------|-------------------------------------------------------|-----------------|--------|---------|--------|--------|--|

| Symbol                              | Parameter                                             | Test conditions | Min.   | Тур.    | Max.   | - Unit |  |

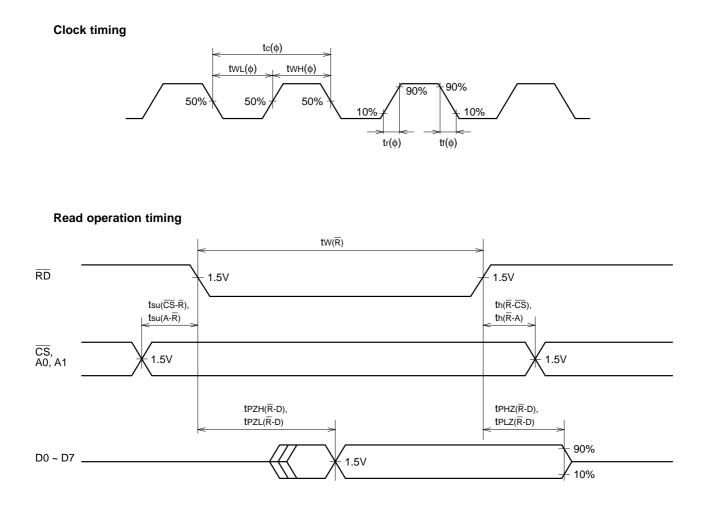

| tc(\phi)                            | Clock cycle                                           |                 | 120    |         | 520    | ns     |  |

| tWH(φ)                              | Clock "H" pulse width                                 |                 |        | tc(φ)/2 |        | ns     |  |

| tWL(φ)                              | Clock "L" pulse width                                 |                 |        | tc(φ)/2 |        | ns     |  |

| tr(¢)                               | Clock rise time                                       |                 |        |         | 20     | ns     |  |

| tf(\$)                              | Clock fall time                                       |                 |        |         | 20     | ns     |  |

| tW(R)                               | Read pulse width                                      |                 | 100    |         |        | ns     |  |

| tw( <del>w</del> )                  | Write pulse width                                     |                 | 100    |         |        | ns     |  |

| tsu( <del>CS</del> - <del>R</del> ) | Chip select setup time before read                    |                 | 0      |         |        | ns     |  |

| tsu(A-R)                            | Address setup time before read                        |                 | 0      |         |        | ns     |  |

| tsu( <del>CS</del> - <del>W</del> ) | Chip select setup time before write                   |                 | 0      |         |        | ns     |  |

| tsu(A-W)                            | Address setup time before write                       |                 | 0      |         |        | ns     |  |

| tsu(D-W)                            | Data setup time before write                          |                 | 40     |         |        | ns     |  |

| th(R-CS)                            | Chip select hold time after read                      |                 | 0      |         |        | ns     |  |

| th(R-A)                             | Address hold time after read                          |                 | 0      |         |        | ns     |  |

| th(W-CS)                            | Chip select hold time after write                     |                 | 0      |         |        | ns     |  |

| th(W-A)                             | Address hold time after write                         |                 | 0      |         |        | ns     |  |

| th(W-D)                             | Data hold time after write                            |                 | 0      |         |        | ns     |  |

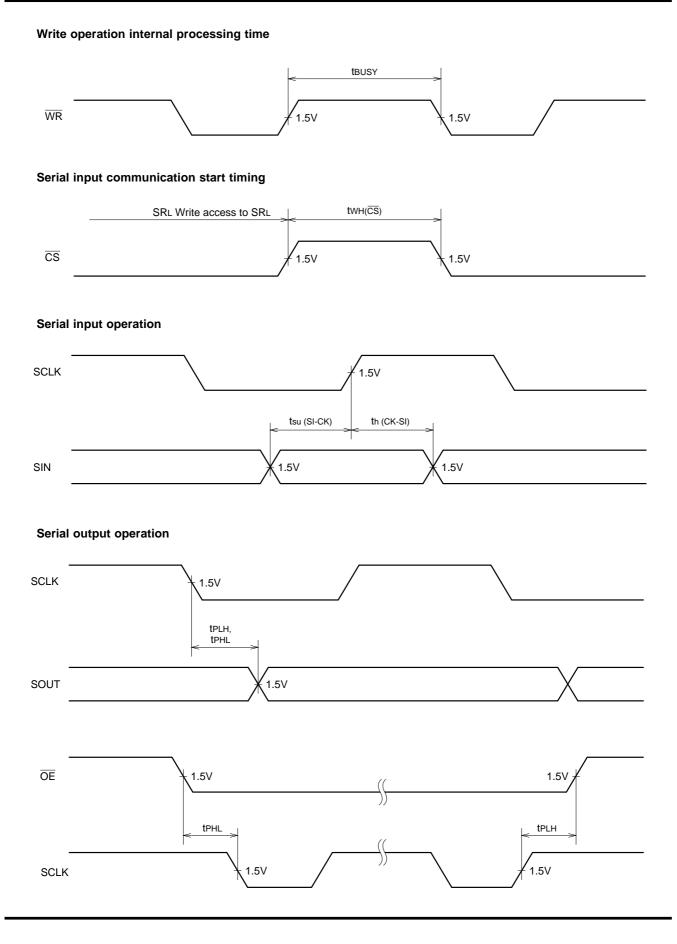

| tsu(SI-CK)                          | Serial data setup time                                |                 | 100    |         |        | ns     |  |

| th(CK-SI)                           | Serial data hold time                                 |                 | 100    |         |        | ns     |  |

| tBUSY                               | Internal processing time after write                  |                 |        |         | 5tc(ø) | ns     |  |

| tWH(CS)                             | Chip select "H" time at serial communication start up |                 | 5tc()) |         |        | ns     |  |

### TIMING CONDITIONS (Ta = $-20 \sim 75^{\circ}$ C, Vcc = 5V ± 10%, GND = 0V)

### SWITCHING CHARACTERISTICS (Ta = $-20 \sim 75^{\circ}$ C, Vcc = 5V ± 10%, GND = 0V)

| Symbol                                           | Parameter                           |           | Test conditions    |          | Limits                                         | Unit |      |

|--------------------------------------------------|-------------------------------------|-----------|--------------------|----------|------------------------------------------------|------|------|

| Symbol                                           |                                     |           | Test conditions    | Min.     | Тур.                                           | Max. | Unit |

| $tPZH(\overline{R}-D)$<br>$tPZL(\overline{R}-D)$ | Data output enable time after read  |           |                    |          |                                                | 80   | ns   |

| $tPHZ(\overline{R}-D)$<br>$tPLZ(\overline{R}-D)$ | Data output disable time after read |           | CL=150pF           | 5        |                                                | 50   | ns   |

|                                                  |                                     | SCLK-SOUT | RL=2KΩ<br>(Note 4) |          |                                                | 60   | ns   |

| tPLH, tPHL                                       | Serial output propagation           | OE-SCLK   |                    | tc(φ)+20 |                                                |      | ns   |

|                                                  | delay time                          | SCLK-OE   |                    |          | $\frac{\mathbf{n} \cdot \mathbf{tc}(\phi)}{2}$ |      | ns   |

n: Divider ratio

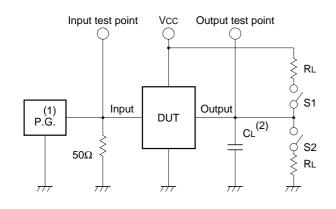

#### NOTE 4: TEST CIRCUIT

| Symbol     | S1     | S2     |

|------------|--------|--------|

| tPZH(R-D)  | Open   | Closed |

| tPZL(R-D)  | Closed | Open   |

| tPHZ(R-D)  | Open   | Closed |

| tPLZ(R-D)  | Closed | Open   |

| tPLH, tPHL | Open   | Open   |

(1) Pulse generator (PG) characteristics: tr=tf=6ns, Zo=50Ω

(2) Capacitance CL includes connection floating capacitance and probe input capacitance.

SERIAL BUS CONTROLLER

### **TIMING CHARTS**

Write operation timing tw(W)  $\overline{\mathsf{WR}}$ 1.5V 1.5V  $th(\overline{W}-\overline{CS}),$  $tsu(\overline{CS}-\overline{W}),$ tsu(A-W) th(W-A) <del>CS</del>, A0, A1 1.5V 1.5V tsu(D-W)  $th(\overline{W}-D)$ D0 ~ D7 1.5V 1.5V

SERIAL BUS CONTROLLER

SERIAL BUS CONTROLLER

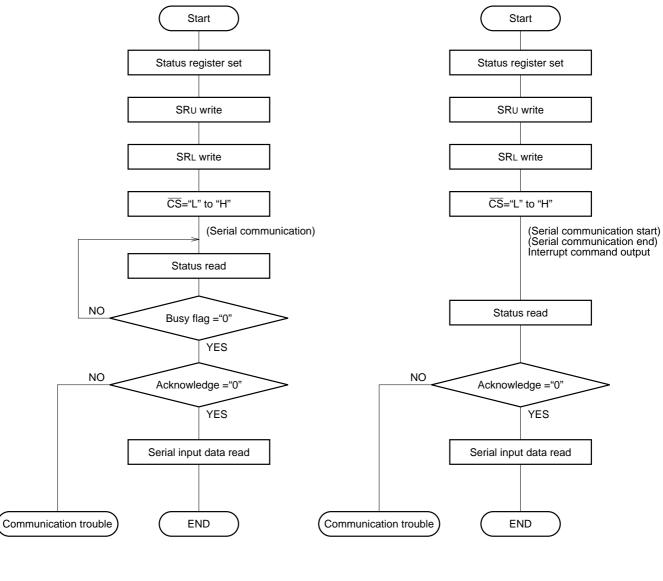

#### **Operation Flow Chart**

When Busy Flag Is Used

When INT Output Is Used

SERIAL BUS CONTROLLER

#### **APPLICATION EXAMPLE**