## M6MF16S2AVP

16777216-BIT (2097152-WORD BY 8-BIT) CMOS 3.3V-ONLY **FLASH MEMORY &**

2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM Stacked-MCP (Multi Chip Package)

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

#### **DESCRIPTION**

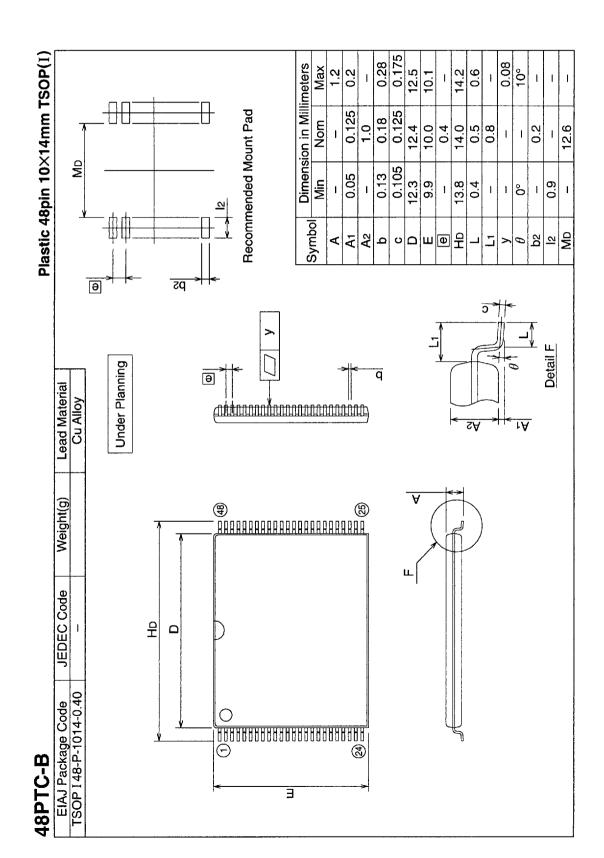

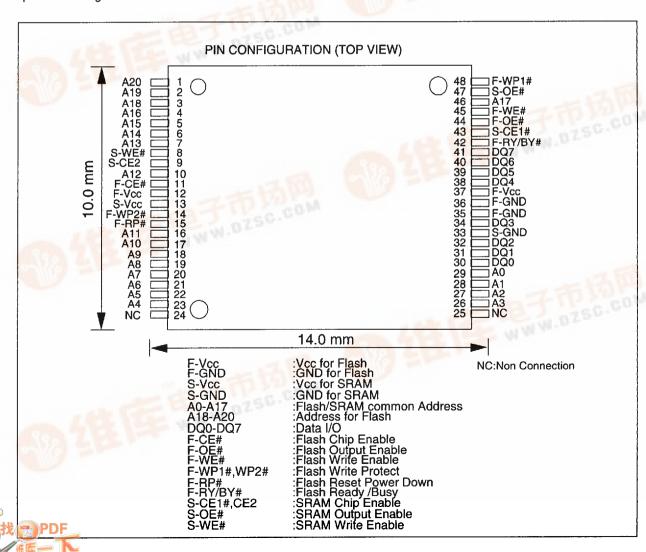

The MITSUBISHI M6MF16S2AVP is a Stacked Muti Chip Package (S-MCP) that contents 16M-bit flash memory and 2M-bit Static RAM in a 48-pin TSOP (TYPE-I).

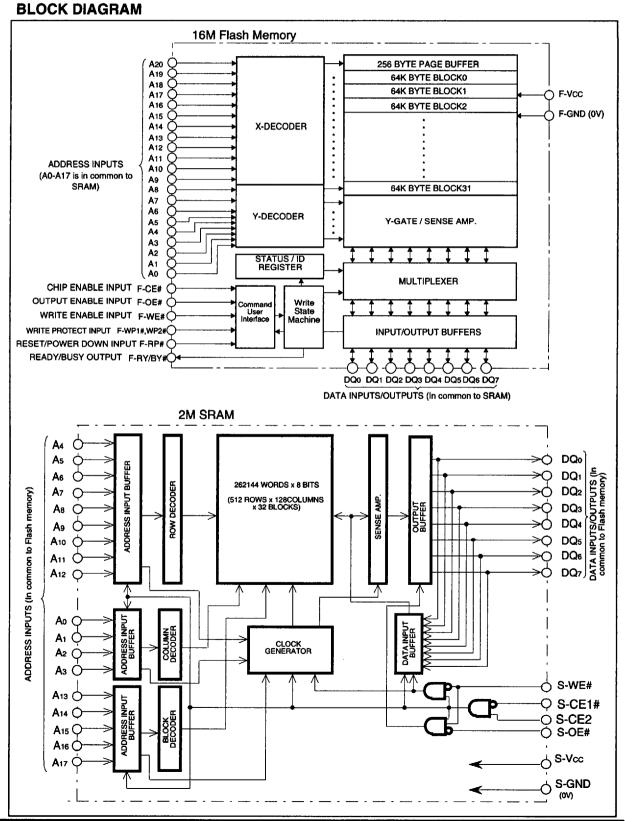

16M-bit Flash memory is a 2097152 bytes, 3.3V-only, and high performance non-volatile memory fabricated by CMOS technology for the peripheral circuit and DINOR(Divided bit-line NOR) architecture for the memory cell.

2M-bit SRAM is a 262144 bytes unsynchronous SRAM fabricated by silicon-gate CMOS technology.

M6MF16S2AVP is suitable for the application of the mobile-communication-system to reduce both the mount space and weight.

### **FEATURES**

- Access time (Flash Memory, SRAM)

- 110ns (Max.)

- Ambient temperature ----- Ta=-20 ~ 85°C

- Package: 48-pin TSOP (Type-I), 0.4mm lead pitch

#### **APPLICATION**

Mobile communication products

# M6MF16S2AVP

16777216-BIT (2097152-WORD BY 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY &

2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM Stacked-MCP (Multi Chip Package)

# **PRELIMINARY**

Notice: This is not a final specification.

Some parametric limits are subject to change.

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT)

CMOS 3.3V-ONLY FLASH MEMORY

## 1. Flash Memory

#### **FUNCTION**

The Flash Memory of M6MF16S2AVP includes on-chip program/erase control circuitry. The Write State Machine (WSM) controls block erase, page (256byte) program operations. Operational modes are selected by the commands written to the Command User Interface (CUI). The Status Register indicates the status of the WSM and when the WSM successfully completes the desired program or block erase operation.

A Deep Powerdown mode is enabled when the RP# pin is at GND, minimizing power consumption.

#### Read

The Flash Memory of M6MF16S2AVP has three read modes, which accesses to the memory array, the Device Identifier and the Status Register. The appropriate read command are required to be written to the CUI. Upon initial device powerup or after exit from deep powerdown, the Flash Memory automatically resets to read array mode. In the read array mode, low level input to CE# and OE#, high level input to WE# and RP#, and address signals to the address inputs (A0-A20) output the data of the addressed location to the data input/output(D0-D7).

#### Write

Writes to the CUI enable reading of memory array data, device identifiers and reading and clearing of the Status Register. they also enable block erase and program. The CUI is written by bringing WE# to low level, while CE# is at low level and OE# is at high level. Addresses and data are latched on the earlier rising edge of WE# and CE#. Standard micro-processor write timings are used.

#### **Output Disable**

When OE# is at VIH, output from the devices is disabled. Data input/output are in a high-impedance(High-Z) state.

#### Standby

When CE# is at VIH, the device is in the standby mode and its power consumption is reduced. Data input/output are in a high-impedance(High-Z) state. If the memory is deselected during block erase or program, the internal control circuits remain active and the device consume normal active power until the operation completes.

#### Deep Power-Down

When RP# is at VIL, the device is in the deep powerdown mode and its power consumption is substantially low. During read modes, the memory is deselected and the data input/output are in a high-impedance(High-Z) state. After return from powerdown, the CUI is reset to Read Array , and the Status Register is cleared to value 80H.

During block erase or program modes, RP# low will abort either operation. Memory array data of the block being altered become invalid

#### SOFTWARE COMMAND DEFINITIONS

The device operations are selected by writing specific software command into the CUI.

#### Read Array Command (FFH)

The device is in Read Array mode on initial device powerup and after exit from deep powerdown, or by writing FFH to the CUI. The device remains in Read Array mode until the other commands are written

#### Read Device Identifier Command (90H)

The Device Identifier is read after writing the Read Device Identifier command of 90H to the Command User Interface. Following the command write, the manufacturer code and the device code can be read from address 000000H and 000001H, respectively.

#### Read Status Register Command (70H)

The Status Register is read after writing the Read Status Register command of 70H to the Command User Interface.

The contents of Status Register are latched on the later falling edge of OE# or CE#. So CE# or OE# must be toggled every status read.

#### Clear Status Register Command (50H)

The Erase Status and Program Status bits are set to "1"s by the Write State Machine and can be reset by the Clear Status Register command of 50H. These bits indicates various failure conditions.

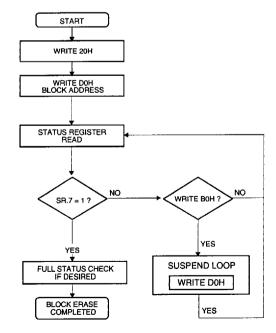

### Block Erase / Confirm Command (20H/D0H)

Automated block erase is initiated by writing the Block Erase command of 20H followed by the Confirm command of D0H. An address within the block to be erased is required. The WSM executes iterative erase pulse application and erase verify operation.

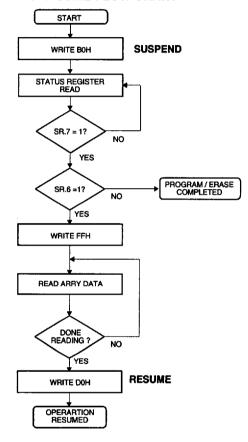

#### Suspend/Resume Command (B0H/D0H)

Writing the Suspend command of B0H during block erase operation interrupts the block erase operation and allows read out from another block of memory. Writing the Suspend command of B0H during program operation interrupts the program operation and allows read out from another block of memory. The device continues to output Status Register data when read, after the Suspend command is written to it. Polling the WSM Status and Suspend Status bits will determine when the erase operation or program operation has been suspended. At this point, writing of the Read Array command to the CUI enables reading data from blocks other than that which is suspended. When the Resume command of D0H is written to the CUI, the WSM will continue with the erase or program processes.

# **PRELIMINARY**

Notice: This is not a final specification.

Some parametric limits are subject to change.

# MITSUBISHI LSIS M6MF16S2AVP

16777216-BIT (2 M x 8-BIT)

CMOS 3.3V-ONLY FLASH MEMORY

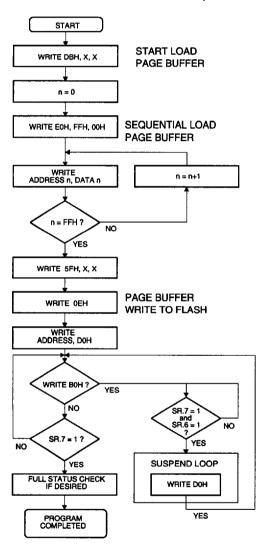

#### **Program Command**

Program consists of data load sequence to page buffer and data program sequence to flash memory array.

#### A) Start Load Page Buffer (DBH/XXH/XXH)

Writing Start Load Page Buffer command allows data load to page buffer. DBH is written to the CUI, follwed by two write cyclie of a certain command except for Block Erase Command(20H/D0H) and Lock Bit Program Command(77H/D0H).

#### B) Sequential Load to Page Buffer (DBH/FFH/00H)

Writing Sequential Load to Page Buffer command allows 256 bytes data load to page buffer sequentially. Follwing a three-command sequence(DBH/FFH/00H), 256 writes cycle specifying the address and data executes loading to page buffer. In this mode, only A0-7 is used and A8-A20 is a don't care.

#### C) End Load Page Buffer (5FH/XXH/XXH)

Writing End Load Page Buffer command ends data load to page buffer. 5FH is written to the CUI, follwed by two write cyclle of a certain command except for Block Erase Command(20H/D0H) and Lock Bit Program command(77H/D0H). The data of page command is stored while Vcc power is on or until writing Page Buffer Write to Flash command or Page Buffer Clear command. The stored data in page buffer can be changed by data load sequence follwed by re-start load page buffer.

### D) Page Buffer Write to Flash (0EH/D0H)

Programming to flash memory array from page buffer is executed by Page Buffer Write to Flash command. The Page Buffer Write to Flash setup command (0EH) is witten to the CUI, followed by the confirm commasnd (D0H). In this mode, A8-A20 is used. The WSM controls the program pulse application and verify operation. After programming, each page buffer is cleared to "FFH". And the page buffer data is invaid in the suspend mode.

Basically re-program must not be done on a page which has already programmed.

#### **DATA PROTECTION**

The Flash Memory of M6MF16S2AVP provides hardware-locking of memory blocks. Each block has an associated nonvolatile lock-bit which determines the lock status of the block. In addition, this flash memory has a master Write Protect pin (WP) which prevents any modifications to memory blocks.

When WP2# is at low, all memory blocks are locked. And when both WP1# and WP2# are at low, this part is in read array only mode.(not be accepted any write command)

When WP1# is at low and WP2# is at high, the memory blocks whose lock-bits are set to "0" are locked.

When both WP1# and WP2# are at high, lock-bits can be programmed (to "0"), all blocks can be programmed or erased regardless of the state of the lock-bits, and lock-bits are cleared to "1" by this erase. See the BLOCK LOCKING table on P.6 for details.

#### **Power Supply Voltage**

When the power supply voltage (Vcc) is less than 2.2V, the device is set to the Read-only mode.

A delay time of 2 us is required before any device operation is initiated. The delay time is measured from the time Vcc reaches Vccmin. During power up, F-RP#=GND is recommended. Falling in Busy status is not recommended for possibility of damaging the device.

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) CMOS 3.3V-ONLY FLASH MEMORÝ

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

### **MEMORY MAP**

| 1F0000H-1FFFFFH | 32Kword BLOCK |

|-----------------|---------------|

| 1E0000H-1EFFFFH | 32Kword BLOCK |

| 1D0000H-1DFFFFH | 32Kword BLOCK |

| 1C0000H-1CFFFFH | 32Kword BLOCK |

| 1B0000H-1BFFFFH | 32Kword BLOCK |

| 1A0000H-1AFFFFH | 32Kword BLOCK |

| 190000H-19FFFFH | 32Kword BLOCK |

|                 |               |

| 060000H-06FFFFH | 32Kword BLOCK |

| 050000H-05FFFFH | 32Kword BLOCK |

| 040000H-04FFFFH | 32Kword BLOCK |

| 030000H-03FFFFH | 32Kword BLOCK |

| 020000H-02FFFFH | 32Kword BLOCK |

| 010000H-01FFFFH | 32Kword BLOCK |

| 000000H-00FFFFH | 32Kword BLOCK |

| Ao - Azo        |               |

Flash Memory Memory Map

### **BUS OPERATIONS**

| Mode     | Pins            | F-CE# | F-OE# | F-WE# | F-RP# | DQ0-7                | F-RY/BY#                    |

|----------|-----------------|-------|-------|-------|-------|----------------------|-----------------------------|

|          | Array           | VIL   | VIL   | Viн   | ViH   | Data out             | <b>V</b> он(ні - z)         |

| Read     | Status Register | VIL   | VIL   | Vін   | ViH   | Status Register Data | X 1)                        |

|          | Lock Bit Status | VIL   | VIL   | Vін   | ViH   | Lock Bit Data (DQ6)  | Х                           |

|          | Identifier Code | VIL   | VIL   | Vıн   | ViH   | Identifier Code      | <b>V</b> он(Hi - <b>z</b> ) |

| Output E | Disable         | VIL   | ViH   | Vıн   | ViH   | Hi-Z                 | Х                           |

| Stand by | 1               | ViH   | X 2)  | Х     | ViH   | Hi-Z                 | X                           |

|          | Program         | VIL   | ViH   | VIL   | ViH   | Command/Data in      | Х                           |

| Write    | Erase           | VIL   | ViH   | VIL   | ViH   | Command              | X                           |

|          | Others          | VIL   | ViH   | VIL   | ViH   | Command              | Х                           |

| Deep Po  | Deep Power Down |       | Х     | Х     | VIL   | Hi-Z                 | Voh(Hi - Z)                 |

<sup>1)</sup> X at RY/BY# is VOL or VOH(Hi-Z).

"The RY/BY# is an open drain output pin and indicates status of the internal WSM. When low,it indicates that the WSM is Busy performing an operation. A pull-up resistor of 10K-100K Ohms is required to allow the RY/BY# signal to transition high indicating a Ready WSM condition.

2) X can be VIH or VIL for control pins.

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

#### MITSUBISHI LSIs

## M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY

#### SOFTWARE COMMAND DEFINITION

| 0                                   |       | 1st bus cycl | e           | 2     | nd bus cycle | •                | 3     | 3rd bus cycle |                   |

|-------------------------------------|-------|--------------|-------------|-------|--------------|------------------|-------|---------------|-------------------|

| Command                             | Mode  | Address      | Data        | Mode  | Address      | Data             | Mode  | Address       | Data              |

| Read Array                          | Write | Х            | FFH         |       |              |                  |       |               |                   |

| Device Identifier                   | Write | Х            | 90H         | Read  | IA 1)        | ID 1)            |       |               |                   |

| Read Status Register                | Write | Х            | 70H         | Read  | Х            | SRD 2)           |       |               |                   |

| Clear Status Register               | Write | Х            | 50H         |       |              |                  |       |               |                   |

| Block Erase / Confirm               | Write | Х            | 20H         | Write | BA 3)        | DOH              |       |               |                   |

| Suspend                             | Write | Х            | B0H         |       |              |                  |       |               |                   |

| Resume                              | Write | Х            | D0H         |       |              |                  |       |               |                   |

| Start Load Page Buffer 4)           | Write | Х            | DBH         | Write | Х            | Х                | Write | Х             | X                 |

| Sequential Load Page Buffer         | Write | Х            | E0H         | Write | Х            | FFH              | Write | X             | 00H <sup>5)</sup> |

| End Load Page Buffer                | Write | X            | 5 <b>FH</b> | Write | Х            | Х                | Write | Х             | Х                 |

| Page Buffer Write to Flash          | Write | Х            | 0EH         | Write | WA 6)        | D0H              |       |               |                   |

| Read Lock Bit Status                | Write | Х            | 71H         | Read  | BA           | D6 <sup>7)</sup> |       |               |                   |

| Lock Bit Program / Confirm          | Write | Х            | 77H         | Write | BA           | DOH              |       |               |                   |

| Erase All Unlocked Blocks / Confirm | Write | Х            | A7H         | Write | Х            | D0H              |       |               |                   |

| Sleep 8)                            | Write | Х            | FOH         |       |              |                  |       | 1             |                   |

- IA=ID Code Address : A0=VIL (Manufacture's Code) : A0=VIH (Device Code), !D=ID Code, A1-A20=VIL SRD=Status Register Data BA=Block Address (A16-A20)

- 3) BA=BIOCK AD0ress (An-A20)

4) Two dummy write cycle is necessary, except for Block Erase/Confirm command(20H/D0H) and Lock Bit Program/Confirm command(77H/D0H), after Start Page Buffer Load command and End Load Page Buffer command.

6) WA=Write Address: Page Buffer Data is programmed to the same page address in the memory arrary, and address A0-7 is ignored.

7) DQ6 provides Block Lock Bit Status, DQ6=1: Block Unlock, DQ6=0: Block Locked.

8) Sleep command (F0H) put the device into the sleep mode after completing the current operation. The active current is reduced to deep power -down levels. The Read Array command (FFH) must be written to get the device out of sleep mode.

#### **BLOCK LOCKING**

| RP# | WP1#       | WP2#  | Erase/Program              | n Operation                                                                                                                                                                                                                                                                                                                      | White Protection Provided                              |  |  |

|-----|------------|-------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|

| Dr# | VVF1#      | VVF2# | Memory Block               | Write Protection Provided  Lock Bit  Unlock All Blocks/Lock Bits Unlocked (Erase/Program enable) Unlock All Blocks/Lock Bits Unlocked (Erase/Program enable) Lock All Blocks/Lock Bits Locked Locked by Lock Bit Lock All Blocks/Lock Bits Locked (Read Array Only Mode) Lock All Blocks/Lock Bits Locked (Deep Power Down Mode) |                                                        |  |  |

| Vнн | Х          | Х     | Unlock                     | Unlock                                                                                                                                                                                                                                                                                                                           | All Blocks/Lock Bits Unlocked (Erase/Program enable)   |  |  |

|     | ViH        | ViH   | Unlock                     | Unlock                                                                                                                                                                                                                                                                                                                           | All Blocks/Lock Bits Unlocked (Erase/Program enable)   |  |  |

| ١., | <b>***</b> | VIL   | Lock                       | Lock                                                                                                                                                                                                                                                                                                                             | All Blocks/Lock Bits Locked                            |  |  |

| ViH | VIL        | ViH   | Depend on Lock Bit Data 1) | Lock                                                                                                                                                                                                                                                                                                                             | Locked by Lock Bit                                     |  |  |

|     | VIL.       | VIL   | Lock                       | Lock                                                                                                                                                                                                                                                                                                                             | AllI Blocks/Lock Bits Locked (Read Array Only Mode) 4) |  |  |

| VIL | Х          | Х     | Lock                       | Lock                                                                                                                                                                                                                                                                                                                             | All Blocks/Lock Bits Locked (Deep Power Down Mode)     |  |  |

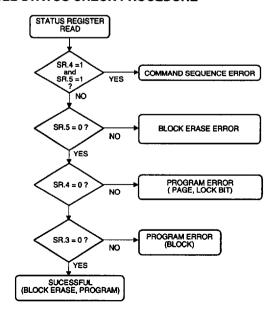

## STATUS REGISTER DATA (SRD)

| Symbol                 | Status                     |                 | Definition                        |

|------------------------|----------------------------|-----------------|-----------------------------------|

| Symbol                 | Siaius                     | *1*             | "O"                               |

| SR.7 (D7)              | Write State Machine Status | Ready           | Busy                              |

| SR.6 (D <sub>6</sub> ) | Suspend Status             | Suspended       | Operation in Progress / Completed |

| SR.5 (Ds)              | Erase Status               | Error           | Successful                        |

| SR.4 (D4)              | Program Status             | Error           | Successful                        |

| SR.3 (D3)              | Block Status after Program | Error           | Successful                        |

| SR.2 (D <sub>2</sub> ) | Reserved                   | -               | -                                 |

| SR.1 (D1)              | Reserved                   | •               | -                                 |

| SR.0 (Do)              | Device Sleep Status        | Device in Sleep | Device Not in Sleep               |

\*DQ3 indicates the block status after the page programming. When DQ3 is \*1\*, the page has the over-programed cell. If over-program occurs, the device is block fail. However if DQ3 is \*1\*, please try the block erase to the block. The block may revive.

<sup>1)</sup> When the Lock bit is '0", its block cannot be programed and erased.

Lock bit is set to "0" by LOCK BIT PROGRAM.

Locked bit("0") is cleared to "1" with block memory by BLOCK ERASE on setting unlock mode.

2) DQ6 provides Lock Bit Status of each block after writing the Read Lock Status command (71H).

3) WP# pin must not be switched during performing Read / Write operations or WSM Busy (WSMS = 0).

4) The device provides a complete read array only mode.

(not be accepted any write command, including read mode command, ex:device identifier, read status register.)

5) X can be ViH or VIL for control pins.

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) **CMOS 3.3V-ONLY FLASH MEMORY**

### **DEVICE IDENTIFIER CODE**

| Code              | Ao  | D7 | D6 | D <sub>5</sub> | D4 | Dз | D2 | D1 | D <sub>0</sub> | Hex. Data |

|-------------------|-----|----|----|----------------|----|----|----|----|----------------|-----------|

| Manufacturer Code | VIL | 0  | 0  | 0              | 1  | 1  | 1  | 0  | 0              | 1CH       |

| Device Code       | Vıн | 0  | 1  | 1              | 0  | 1  | 0  | 0  | 1              | 69H       |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                                                   | Conditions             | Min. | Max. | Unit |

|--------|-------------------------------------------------------------|------------------------|------|------|------|

| F-Vcc  | Vcc voltage (Flash Memory)                                  |                        | -0.2 | 4.6  | V    |

| Vit    | All input or output voltage except <sup>1</sup> for Vcc,RP# | with respect to Ground | -0.2 | 4.6  | V    |

| VI2    | RP# supply voltage                                          |                        | -0.6 | 14.0 | ٧    |

| Ta     | Ambient temperature                                         |                        | -20  | 85   | °C   |

| Tbs    | Temperature under bias                                      |                        | -30  | 85   | °C   |

| Tstg   | Storage temperature                                         |                        | -65  | 125  | °C   |

| Гоит   | Output short circuit current                                |                        |      | 100  | mA   |

<sup>1)</sup> Minimum DC voltage is -0.5V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <20ns. Maximum DC voltage on input/output pins is Vcc+0.5V which, during transitions, may overshoot to Vcc+1.5V for periods <20ns.

### **CAPACITANCE**

|        | -                                         |                                 |      | Limits |      |      |

|--------|-------------------------------------------|---------------------------------|------|--------|------|------|

| Symbol | Parameter                                 | Test conditions                 | Min. | Тур.   | Max. | Unit |

| Cin    | Input capacitance (address, Control Pins) | Ta = 25°C, f=1MHz, Vin=Vout=0V  |      |        | 8    | pF   |

| Соит   | Output capacitance                        | 1a = 25 C, I= IMHz, VIN=VOOI=0V |      |        | 12   | pF   |

Note: The value of common pins to SRAM is the sum of Flash Memory and SRAM.

## DC ELECTRICAL CHARACTERISTICS (Ta = -20 ~ 85°C, Vcc = 2.7V ~ 3.6V, unless otherwise noted)

| C      | Desembles                   | To a harman distance                                                             | Limits  |      |         | Unit |

|--------|-----------------------------|----------------------------------------------------------------------------------|---------|------|---------|------|

| Symbol | Parameter                   | Test conditions                                                                  | Min     | Тур  | Max     | Unit |

| lu     | Input leakage current       | 0V ≤ Vin ≤ F-Vcc                                                                 |         |      | ±1.0    | μΑ   |

| llo    | Output leakage current      | 0V ≤ Vouτ ≤ F-Vcc                                                                |         |      | ±10     | μA   |

| ISB1   |                             | F-Vcc = 3.6V, VIN=VIL/VIH, F-CE#=F-RP#=F-WP1#,WP2#=VIH                           |         | 50   | 200     | μΑ   |

| ISB2   | Vcc standby current         | F-Vcc=3.6V,VIN=F-GND or F-Vcc, F-CE#=F-RP#=F-WP1#,WP2#=Vcc±0.3V                  |         | 0.1  | 5       | μA   |

| ISB3   | V d                         | F-Vcc = 3.6V, Vin=ViL/Vin, F-RP#= ViL                                            |         | 5    | 15      | μΑ   |

| ISB4   | Vcc deep powerdown current  | F-Vcc = 3.6V, VIN=F-GND or F-Vcc, F-RP#=F-GND±0.3V                               |         | 0.1  | 5       | μΑ   |

| ICC1   | Vcc read currenr            | F-Vcc = 3.6V, Vin=ViL/Vih, F-CE# = ViL,<br>F-RP#=F-OE#=Vih, f = 5MHz, lout = 0mA |         | 7    | 25      | mA   |

| ICC2   | Vcc write current           | F-Vc=3.6V,VIN=VIL/VIH,F-CE#=F-WE#=VIL,F-RP#=F-OE#=VIH                            |         |      | 30      | mA   |

| Іссз   | Vcc program currenrt        | F-Vcc = 3.6V, VIN=VIL/VIH, F-CE# = F-RP# =F-WP1#,WP2# = VIH                      |         |      | 30      | mA   |

| ICC4   | Vcc erase current           | F-Vcc = 3.6V, VIN=VIL/VIH, F-CE# = F-RP# =F-WP1#,WP2# = VIH                      |         |      | 40      | mA   |

| ICC5   | Vcc suspend current         | F-Vcc = 3.6V, VIN=VIL/VIH, F-CE# = F-RP# =F-WP1#,WP2# = VIH                      |         |      | 200     | μA   |

| RP     | RP# block unlock current    | F-RP# = VHH max                                                                  |         |      | 500     | μA   |

| Vінн   | RP# block unlock voltage    |                                                                                  | 11.4    | 12.0 | 12.6    | ٧    |

| VIL    | Input low voltage           |                                                                                  | - 0.5   |      | 0.8     | ٧    |

| ViH    | Input high voltage          |                                                                                  | 2.0     |      | Vcc+0.5 | V    |

| Vol    | Output low voltage          | loL = 4.0mA                                                                      |         |      | 0.45    | V    |

| Vон1   | Outroot bish collapse       | Iон = -2.5mA                                                                     | 0.85Vcc |      |         | ٧    |

| VOH2   | Output high voltage         | loн = −100μA                                                                     | Vcc-0.4 |      |         | V    |

| VLKO   | Low Vcc Lock-Out voltage 2) |                                                                                  | 1.5     |      | 2.5     | V    |

May.1998, Rev.1.2

All currents are in RMS unless otherwise noted.

1) Typical values at Vcc=3.3V, Ta=25°C

2) To protect against initiation of write cycle during Vcc power-up/ down, a write cycle is locked out for Vcc less than VLKO.

If Vcc is less than VLKO, Write State Machine is reset to read mode. When the Write State Machine is in Busy state, if Vcc is less than VLKO, the alteration of memory contents

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

### MITSUBISHI LSIs

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY

## AC ELECTRICAL CHARACTERISTICS (Ta = -20 ~ 85°C, Vcc = 2.7V ~ 3.6V, unless othe

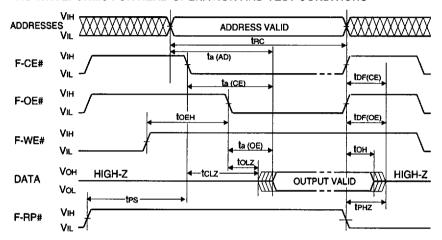

### **Read-Only Mode**

| •       |               | Barrantan                              |     | Limits |     |      |

|---------|---------------|----------------------------------------|-----|--------|-----|------|

| Syn     | nbol          | Parameter                              | Min | Тур    | Max | Unit |

| tRC     | tavav         | Read cycle time                        | 110 |        |     | ns   |

| ta (AD) | tavov         | Address access time                    |     |        | 110 | ns   |

| ta (CE) | tELQV         | Chip enable access time                |     |        | 110 | ns   |

| ta (OE) | tGLQV         | Output enable access time              |     |        | 55  | ns   |

| tcız    | tELQX         | Chip enable to output in low-Z         | 0   |        |     | ns   |

| tDF(CE) | <b>t</b> EHQZ | Chip enable high to output in high Z   |     |        | 30  | ns   |

| tolz    | tGLQX         | Output enable to output in low-Z       | 0   |        |     | ns   |

| tDF(OE) | tghoz         | Output enable high to output in high Z |     |        | 30  | ns   |

| tPHZ    | tPLQZ         | RP# low to output high-Z               |     |        | 300 | ns   |

| toн     | tон           | Output hold from CE#, OE#, addresses   | 0   |        |     | ns   |

| toeh    | twhal         | OE# hold from WE# high                 | 110 |        |     | ns   |

| tes     | <b>t</b> PHEL | RP# high recovery to CE# low           | 500 |        |     | ns   |

Timing measurements are made under AC waveforms for read operations.

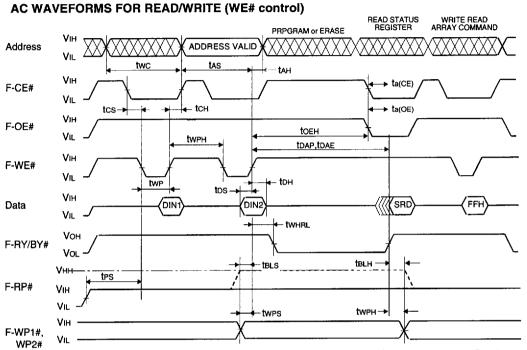

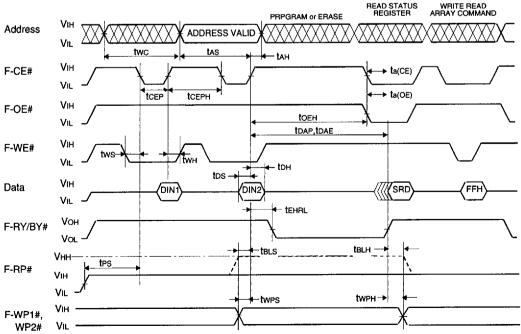

### Read/Write Mode (WE# control)

| •            |        | Parameter                              |     | Limits |     | 11-14 |

|--------------|--------|----------------------------------------|-----|--------|-----|-------|

| Syn          | nbol   | Parameter                              | Min | Тур    | Max | Unit  |

| twc          | tavav  | Write cycle time                       | 110 |        |     | ns    |

| tas          | tavwl  | Address set-up time                    | 50  |        |     | ns    |

| tah          | twlax  | Address hold time                      | 10  |        |     | ns    |

| tos          | tovwn  | Data set-up time                       | 50  |        |     | ns    |

| tон          | twnox  | Data hold time                         | 10  |        |     | ns    |

| tcs          | tELWL  | Chip enable set-up time                | 0   |        |     | ns    |

| tch          | twhen  | Chip enable hold time                  | 0   |        |     | ns    |

| twp          | twLwH  | Write pulse width                      | 60  |        |     | ns    |

| twpH         | twnwl  | Write pulse width high                 | 20  |        |     | ns    |

| tBLS<br>twps | tрннwн | Block Lock set-up to write enable high | 110 |        |     | ns    |

| tBLH<br>tWPH | tрннwн | Block Lock hold from valid SRD         | 0   |        |     | ns    |

| tDAP         | twnRH1 | Duration of auto-program operation     |     | 5      | 80  | ms    |

| tDAE         | twnRH2 | Duraruin of auto-erase operation       |     | 50     | 600 | ms    |

| twhrt.       | twhrL  | Write enable high to RY/BY# low        |     |        | 110 | ns    |

| tPS          | tpHwL  | F-RP# high recovery to F-WE# low       | 500 |        |     | ns    |

Read timing parameters during command write operations mode are the same as during read-only operations mode. Typical values at Vcc=3.3V, Ta=25°C

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) **CMOS 3.3V-ONLY FLASH MEMORY**

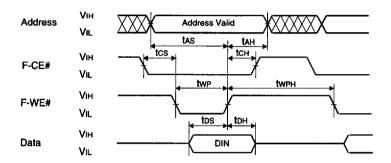

#### Read/Write Mode (CE# control)

|              |        |                                        |     | Limits |     |      |

|--------------|--------|----------------------------------------|-----|--------|-----|------|

| Syr          | nbol   | Parameter                              |     | Тур    | Max | Unit |

| twc          | tavav  | Write cycle time                       | 110 |        |     | ns   |

| tas          | tavwl  | Address set-up time                    | 50  |        |     | ns   |

| tan          | twLax  | Address hold time                      | 10  |        |     | ns   |

| tos          | tovwn  | Data set-up time                       | 50  |        |     | ns   |

| ton          | twhox  | Data hole time                         | 10  |        |     | ns   |

| tws          | tELWL  | Write enable set-up time               | 0   |        |     | ns   |

| twn          | twhen  | Write enable hold time                 | 0   |        |     | ns   |

| tCEP         | twLwH  | CE# pulse width                        | 60  |        |     | ns   |

| tCEPH        | twhwL  | CE# pulse width high                   | 20  |        |     | ns   |

| tBLS         | tPHHWH | Block Lock set-up to write enable high | 110 |        |     | ns   |

| tBLH<br>twpH | tphhwh | Block lock hold from valid SRD         | 0   |        |     | ns   |

| tDAP         | twnRH1 | Duration of auto-program operation     |     | 5      | 80  | ms   |

| tdae         | twhRH2 | Duration of auto-erase operation       |     | 50     | 600 | ms   |

| tehal        | tehru  | Chip enable high to RY/BY# low         |     |        | 110 | ns   |

| tps          | tehwl  | RP# high recovery to write enable low  | 500 |        |     | ns   |

Read timing parameters during command write operations mode are the same as during read-only operations mode. Typical values at Vcc=3.3V, Ta=25°C

### **Erase and Program Performance**

| Parameter                      |     | Unit |     |        |

|--------------------------------|-----|------|-----|--------|

| raidinetei                     | Min | Тур  | Max | J.III. |

| Block Erase Time               |     | 40   | 600 | ms     |

| Block Program Time (Page Mode) |     | 1.3  | 5   | sec    |

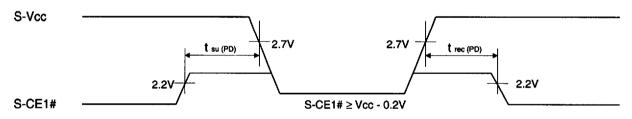

| Page Program Time              |     | 4    | 80  | ms     |

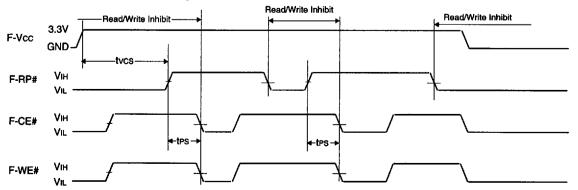

### **Vcc Power UP/Down Timing**

| Symbol | D                                     |     | Unit |     |      |

|--------|---------------------------------------|-----|------|-----|------|

|        | Parameter                             | Min | Тур  | Max | OTHL |

| tvcs   | RP# =VIH set-up time from Vcc at 2.7V | 2   |      |     | μs   |

During power up/down, by the noise pulses on control pins, the device has possibility of accidental erasure or programming. The device must be protected against initiation of write cycle for memory contents during power up/down.

The delay time of min.2usec is always required before read operation or write operation is initiated from the time Vcc reaches 2.7V during power up. By holding RP# VIL, the contents of memory is protected during Vcc power up/down.

During power down, RP# must be held VIL for min.2us from the time Vcc reaches 2.7V.

During power down, RP# must be held VIL utill Vcc reaches GND.

RP# doesn't have latch mode ,so RP# must be held VIH during read operation or erase/program operation.

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

### AC WAVEFORMS FOR READ OPERATION AND TEST CONDITIONS

### **TEST CONDITIONS FOR AC CHARACTERISTICS**

| Test Configuration                  |                                         | Vcc=2.7V ~ 3.6V |  |

|-------------------------------------|-----------------------------------------|-----------------|--|

| Innut valtage                       | VIL                                     | ov              |  |

| Input voltage                       | ViH                                     | 3.0V            |  |

| Input rise and fall times (10%-90%) | Input rise and fall times (10%-90%)     |                 |  |

| Reference voltage at timing measure | Reference voltage at timing measurement |                 |  |

| Capacitance load value              | CL                                      | 100pF           |  |

Output load : 1TTL gate + CL

#### **Vcc POWER UP / DOWN TIMING**

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY

# **PRELIMINARY**

Notice: This is not a final specification.

Some parametric limits are subject to change.

Note, (1) Block Rrase: DIN1=20H, DIN2=D0H (tDAE : Duration of Block Erase)

- (2) Page Buffer Write to Flash : DIN1=0EH, DIN2=D0H (tDAP : Duration of program)

- (3) Lock Bit Program / Confirm: DIN1=77H, DIN2=D0H (tDAP : Duration of program)

- (4) Erase All Unlocked Blocks / Confirm: DIN1=A7H, DIN2=D0H (tFERS: Duration of Chip Erase)

## AC WAVEFORMS FOR READ/WRITE (CE# control)

Note, (1) Block Rrase: DIN1=20H, DIN2=D0H (tDAE : Duration of Block Erase)

- (2) Page Buffer Write to Flash : DIN1=0EH, DIN2=D0H (tDAP : Duration of program)

- (3) Lock Bit Program / Confirm: DIN1=77H, DIN2=D0H (tDAP : Duration of program)

- (4) Erase All Unlocked Blocks / Confirm : DIN1=A7H, DIN2=D0H (tFERS : Duration of Chip Erase)

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

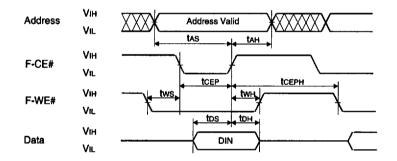

## AC WAVEFORMS FOR PAGE BUFFER WRITE OPERATION (WE# control)

## AC WAVEFORMS FOR PAGE BUFFER WRITE (CE# control)

#### **FULL STATUS CHECK PROCEDURE**

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY

# PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to change.

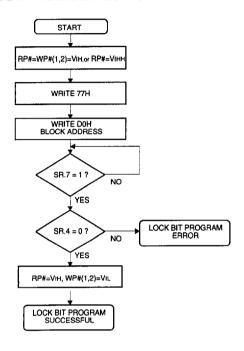

## LOCK BIT PROGRAM FLOW CHART

### **BLOCK ERASE FLOW CHART**

# M6MF16S2AVP

16777216-BIT (2 M x 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY

# **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

# PROGRAM FLOW CHART (PAGE BUFFER WRITE TO FLASH FLOW)

Note; Block Erase /Confirm command(20H/DOH) and Lock Bit Program /Confirm command is not allowed as two-dummy cycles after Start Page Buffer load command and End Page Buffer Load command is written.

#### SUSPEND / RESUME FLOW CHART

# M6MF16S2AVP

2097152-BIT (256k x 8-BIT)

CMOS STATIC RAM

# PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to change.

## 2. SRAM

### **FUNCTION**

The SRAM of the M6MFT/B16S2TP is the same chip with M5M5V208 and its operation mode is determined by a combination of the device control inputs S-CE1#, S-CE2, S-WE# and S-OE#.

Each mode is summarized in the function table.

A write cycle is executed whenever the low level S-WE# overlaps with the low level S-CE1# and the high level S-CE2. The address must be set up before the write cycle and must be stable during the entire cycle. The data is latched into a cell on the trailing edge of S-WE#,S-CE1# or S-CE2,whichever occurs first,requiring the set-up and hold time relative to these edge to be maintained. The output enable input S-OE# directly controls the output stage. Setting the S-OE# at a high level, the output stage is in a high-impedance state, and the data bus contention problem in the write cycle is eliminated.

A read cycle is executed by setting S-WE# at a high level and S-OE# at a low level while S-CE1# and S-CE2 are in an active state(S-CE1#=L,S-CE2=H).

When setting S-CE1# at a high level or S-CE2 at a low level, the chip are in a non-selectable mode in which both reading and writing are disabled. In this mode, the output stage is in a high-impedance state, allowing OR-tie with other chips and memory expansion by S-CE1# and S-CE2. The power supply current is reduced as low as the stand-by current which is specified as ICC3 or ICC4, and the memory data can be held at +2V power supply, enabling battery back-up operation during power failure or power-down operation in the non-selected mode.

#### **FUNCTION TABLE**

| S-CE1# | S-CE2 | S-WE# | S-OE# | Mode          | DQ              | lcc     |

|--------|-------|-------|-------|---------------|-----------------|---------|

| Х      | L     | Х     | х     | Non selection | High impedance  | Standby |

| Н      | Х     | Х     | Х     | Non selection | High impedance  | Standby |

| L      | Н     | L     | Х     | Write         | D <sub>IN</sub> | Active  |

| L      | Н     | Н     | L     | Read          | D оит           | Active  |

| L      | Н     | H     | Н     |               | High impedance  | Active  |

# M6MF16S2AVP

2097152-BIT (256k x 8-BIT) CMOS STATIC RAM

# PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to change.

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter             | Conditions          | Ratings                         | Unit |

|------------------|-----------------------|---------------------|---------------------------------|------|

| S-Vcc            | Supply voltage (SRAM) |                     | - 0.3*~4.6                      | ٧    |

| Vı               | Inout voltage         | With respect to GND | - 0.3* ~ Vcc + 0.5<br>(Max 4.6) | ٧    |

| Vo               | Output voltage        |                     | 0 ~ Vcc                         | V    |

| Pd               | Power dissipation     | Ta=25°C             | 700                             | mW   |

| Topr             | Operating temperature |                     | -20 ~ 85                        | °C   |

| T <sub>stg</sub> | Storage temperature   |                     | - 65 ~150                       | °C   |

<sup>\* -3.0</sup>V in case of AC (Pulse Width ≤ 30ns)

### DC ELECTRICAL CHARACTERISRICS (Ta=-20~85°C, Vcc=2.7V~3.6V, Unless otherwise noted)

| Symbol           | Parameter                               | Parameter Test conditions                                                                                        |           | Limits       |     |              | l lmit |

|------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------|--------------|-----|--------------|--------|

|                  | raiameter                               |                                                                                                                  |           | Min          | Тур | Мах          | Unit   |

| Vін              | High-level input voltage                |                                                                                                                  |           | 2.0          |     | Vcc<br>+0.3V | ٧      |

| VIL              | Low-level input voltage                 |                                                                                                                  | ·         | -0.3         |     | 0.6          | V      |

| V <sub>OH1</sub> | High-level output voltage1              | lон= -0.5mA                                                                                                      |           | 2.4          |     |              | ٧      |

| Vон2             | High-level output voltage2              | Iон= −0.05mA                                                                                                     |           | Vcc<br>-0.5V |     |              | ٧      |

| Vol              | Low-level output voltage                | loL=2mA                                                                                                          |           |              |     | 0.4          | v      |

| h                | Input current                           | V <sub>I</sub> =0 ~ Vcc                                                                                          |           |              |     | ±1           | μA     |

| lo               | Output current in off-state             | S-CE1#=VIH or S-CE2=VIL or S-OE#=VIH<br>Vvo=0 ~ Vcc                                                              |           |              |     | ±1           | μA     |

|                  | Active events everent                   | S-CE1# $\leq$ 0.2V, S-CE2 $\geq$ S-Vcc-0.2V other inputs $\leq$ 0.2V or $\geq$ S-Vcc-0.2V Output-open(duty 100%) | 10MHz     | -            | 20  | 25           |        |

| lcc1             | Active supply current (MOS level input) |                                                                                                                  | 5MHz      | -            | 10  | 13           | mΑ     |

|                  | ,,                                      |                                                                                                                  | 1MHz      | -            | 3   | 5            |        |

|                  |                                         | S-CE1#=Vil, S-CE2=ViH                                                                                            | 10MHz     | _            | 22  | 27           |        |

| lcc2             | Active supply current                   | other inputs = Vін or Vі∟                                                                                        | 5MHz      | -            | 12  | 15           | mΑ     |

|                  | (TTL level input)                       | Output-open(duty 100%)                                                                                           | 1MHz      | -            | 3   | 5            |        |

|                  |                                         | 1) S-CE2 ≤ 0.2V ,<br>other inputs = 0 ~ Vcc                                                                      | -20~+85°C | -            | •   | 40           |        |

| lcc3             | Stand-by current                        | 2) S-CE1# ≥ Vcc-0.2V,                                                                                            | -20~+40°C | -            | -   | 5            | μΑ     |

|                  |                                         | S-CE2 ≥ Vcc-0.2V<br>other inputs = 0 ~ Vcc                                                                       | +25°C     | -            | 0.3 | 2            | •      |

| lcc4             | Stand-by current                        | S-CE1# = VIH or S-CE2 = VIL,<br>other inputs = 0 ~ Vcc                                                           |           | -            | -   | 0.33         | mA     |

<sup>\* -3.0</sup>V in case of AC (Pulse Width ≤ 30ns)

### CAPACITANCE (Ta = -20 ~ 85°C, Vcc = 2.7V ~ 3.6V, unless otherwise noted)

| Symbol | Parameter          | Test conditions                                      | Limits |     |     |      |

|--------|--------------------|------------------------------------------------------|--------|-----|-----|------|

| Symbol | rarameter          | rest conditions                                      | Min    | Tvp | Max | Unit |

| Cı     | Input capacitance  | V <sub>I</sub> =GND, V <sub>I</sub> =25mVrms, f=1MHz |        |     | 7   | pF   |

| Co     | Output capacitance | Vo=GND.Vo=25mVrms, f=1MHz                            |        |     | 9   | pF   |

Note 1: Direction for current flowing into an IC is positive (no mark).

<sup>2:</sup> Typical value is Vcc = 3V, Ta = 25°C

<sup>3:</sup> The value of common pins to Flash Memory is the sum of Flash Memory and SRAM.

# PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

# M6MF16S2AVP

2097152-BIT (256k x 8-BIT)

CMOS STATIC RAM

### AC ELECTRICAL CHARACTERISTICS (Ta=-20 ~ 85°C, Vcc=2.7V ~ 3.6V, unless otherwise noted)

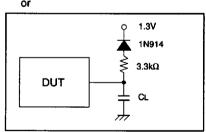

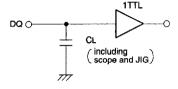

## (1) MEASUREMENT CONDITIONS

Vcc ......2.7V ~ 3.6V Input pulse level VIH=2.2V, VIL=0.4V

Input rise and fall time ..... 5ns

Reference level ......VoH=VoL=1.5V Output loads .....Fig.1,CL = 30pF

CL = 5pF (for ten,tdis)

Transition is measured ±500mV from steady

state voltage. (for ten,tdis)

Fig.1 Output load

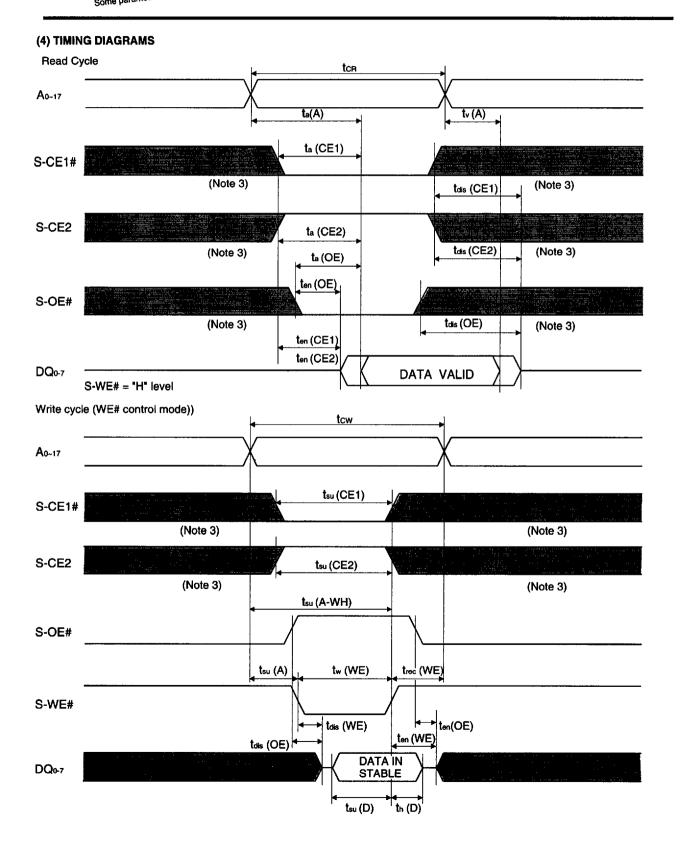

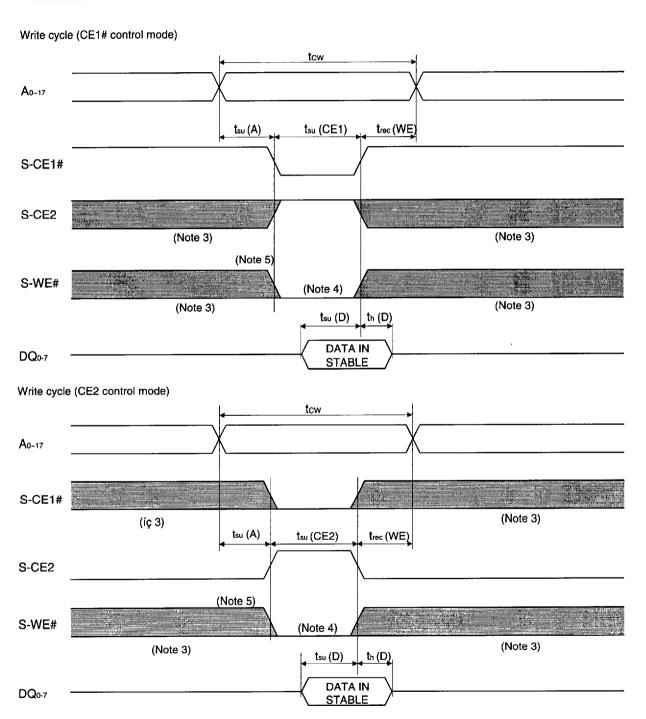

### (2) READ CYCLE

| Symbol    |                                       | Lin |     |      |

|-----------|---------------------------------------|-----|-----|------|

|           | Parameter                             | Min | Max | Unit |

| tca       | Read cycle time                       | 110 | •   | ns   |

| ta(A)     | Address access time                   |     | 110 | ns   |

| ta(CE1)   | Chip select1 access time              |     | 110 | ns   |

| ta(CE2)   | Chip select2 access time              |     | 110 | ns   |

| ta(OE)    | Output enable access time             |     | 55  | ns   |

| tdis(CE1) | Output disable time after S-CE1# high |     | 40  | ns   |

| tdis(CE2) |                                       |     | 40  | ns   |

| tdis(OE)  | Output disable time after S-OE# high  |     | 40  | ns   |

| ten(CE1)  | Output enable time after S-CE1# low   | 10  |     | ns   |

| ten(CE2)  | Output enable time after S-CE2 high   | 10  |     | ns   |

| ten(OE)   | Output enable time after S-OE# low    | 5   |     | ns   |

| t∨(A)     | Data valid time after address         | 10  |     | ns   |

## (3) WRITE CYCLE

| Symbol              | Parameter                                | Lim |                                         |      |

|---------------------|------------------------------------------|-----|-----------------------------------------|------|

|                     |                                          | Min | Max                                     | Unit |

| tcw                 | Write cycle time                         | 110 |                                         | ns   |

| t <sub>w</sub> (WE) | Write pulse width                        | 85  |                                         | ns   |

| tsu(A)              | Address setup time                       | 0   |                                         | ns   |

| tsu(A-WH)           | Address setup time with respect to S-WE# | 100 |                                         | ns   |

| tsu(CE1)            | Chip select1 setup time                  | 100 |                                         | ns   |

| tsu(CE2)            | Chip select2 setup time                  | 100 |                                         | ns   |

| tsu(D)              | Data setup time                          | 45  |                                         | ns   |

| th(D)               | Data hold time                           | 0   |                                         | ns   |

| trec(WE)            | Write recovery time                      | 0   |                                         | ns   |

| tdis(WE)            | Output disable time from S-WE# low       |     | 40                                      | ns   |

| tdis(OE)            | Output disable time from S-OEh# hig      |     | 40                                      | ns   |

| ten(WE)             | Output enable time from S-WE# high       | 5   |                                         | ns   |

| ten(OE)             | Output enable time from S-OE# low        | 5   | • • • • • • • • • • • • • • • • • • • • | ns   |

# M6MF16S2AVP

2097152-BIT (256k x 8-BIT) CMOS STATIC RAM

# PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to change.

# M6MF16S2AVP

2097152-BIT (256k x 8-BIT) **CMOS STATIC RAM**

# PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to change.

- Note 3: Hatching indicates the state is "don't care".

4: Writing is executed while S-CE2 high overlaps S-CE1# and S-WE# low.

5: When the falling edge of S-WE# is simultaneously or prior to the falling edge of S-CE1# or rising edge of S-CE2, the outputs are maintained in the high impedance state.

- 6: Don't apply inverted phase signal externally when DQ pin is output mode.

# PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to change.

# M6MF16S2AVP

2097152-BIT (256k x 8-BIT) CMOS STATIC RAM

## **POWER DOWN CHARACTERISTICS**

(1) ELECTRIAL CHARACTERISTICS (Ta=-20 ~ 85°C, unless otherwise noted)

|           |                           |                                                      | Limits    |     |     |     |      |

|-----------|---------------------------|------------------------------------------------------|-----------|-----|-----|-----|------|

| Symbol    | Parameter                 | Test conditions                                      |           | Min | Түр | Max | Unit |

| VCC (PD)  | Power down supply voltage |                                                      |           | 2   |     |     | ٧    |

| VI (CE1#) | Chip select input S-CE1#  |                                                      |           | 2.0 |     |     | V    |

| VI (CE2)  | Chip select input S-CE2   |                                                      |           |     |     | 0.2 | V    |

| ICC (PD)  | Power down supply current | S-Vcc = 3V<br>1) S-CE2 ≤ 0.2V, other input = 0 ~ Vcc | -20~+85°C |     |     | 30  |      |

|           |                           | 2) S-CE1# ≥ Vcc-0.2V,S-CE2 ≥ Vcc-0.2V                | -20~+40°C |     |     | 3   | μΑ   |

|           |                           | other inputs = 0 ~ Vcc                               | +25°C     | ,   | 0.3 | 1   |      |

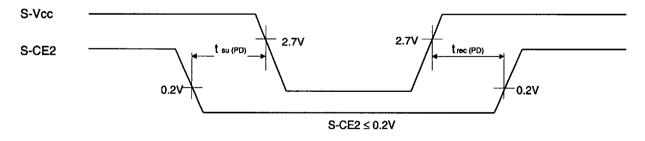

## (2) TIMING REQUIREMENTS (Ta=-20 ~ 85°C, unless otherwise noted)

| Symbol    | Paramwter                | Test conditions |     | I Imit |     |      |

|-----------|--------------------------|-----------------|-----|--------|-----|------|

|           |                          |                 | Min | Тур    | Max | Unit |

| tsu (PD)  | Power down set up time   |                 | 0   |        |     | ns   |

| trec (PD) | Power down recovery time |                 | 5   |        |     | ms   |

## (3) POWER DOWN CHARACTERISTICS

## CE1# control mode

## CE2 control mode