## Am79213/Am79C203/031

Advanced Subscriber Line Interface Circuit (ASLIC™) Device Advanced Subscriber Line Audio-Processing Circuit (ASLAC™) Device

#### DISTINCTIVE CHARACTERISTICS

- Performs all of the functions of a codec-filter

- Single channel architecture

- Performs Battery-feed, Ring-trip, Signaling, Coding, Hybrid and Test (BORSCHT) functions

- Single hardware design meets multiple country requirements through software programming

- Standard microprocessor interface

- Industry standard PCM interface with full-time slot assignment

- Monitor of two-wire interface voltage and current for subscriber line diagnostics

- Low idle power per line

- On-hook transmission

- Only battery and +5 V supplies needed

- Exceeds LSSGR and CCITT central office requirements

- Off-hook and ground-key detectors with programmable thresholds

- Programmable line feed characteristics independent of battery voltage

- Built-in voice path test modes

- Analog and digital hybrid balance capability

- Adaptive hybrid balance capability

- Linear power feed with power management and thermal shutdown features

- Abrupt and smooth polarity reversal

- Power-cross detection in Ringing and Nonringing states

- Software programmable

- DC loop feed characteristics and current limit

- Loop supervision detection thresholds

- Off-hook detect debounce interval

- Two-wire AC impedance

- Transhybrid balance

- Transmit and receive gains

- Equalization

- Digital I/O pins

- A-law/µ-law selection

- Linear data available on PCM ports for custom compression and expansion

- Compatible with inexpensive protection networks. Accommodates low tolerance fuse resistors while maintaining longitudinal balance to Bellcore specifications.

- **■** Power/Service Denial state

- Small physical size

- Integrated ring trip function

- Four relay drivers with built-in energy absorption zener diodes

- Synchronized ring relay operation: zero volts ac on, zero current off

- Software enabled Normal or Automatic Ring-Trip state

- On-chip 12 kHz and 16 kHz metering generation with on and off meter pulse shaping

- Supports loop-start and ground-start signaling

- 0°C to +70°C commercial operation guaranteed by production testing

- -40°C to +85°C temperature range operation available

#### TABLE OF CONTENTS

| Distinctive Characteristics                                    | 1    |

|----------------------------------------------------------------|------|

| Linecard Block Diagram                                         | 4    |

| Ordering Information                                           | 5    |

| ASLIC Device                                                   | 5    |

| ASLAC Device                                                   | 6    |

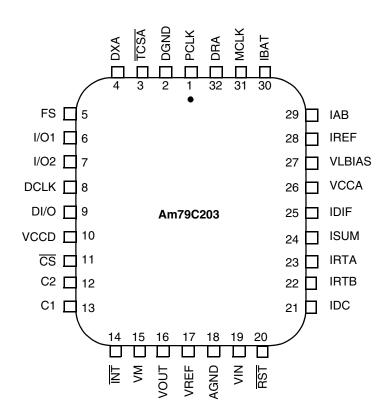

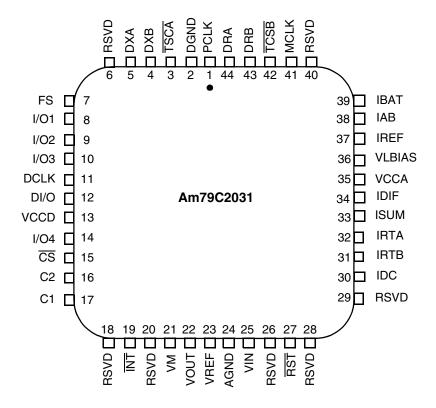

| Connection Diagrams                                            | 7    |

| 32-Pin PLCC                                                    | 7    |

| 44-Pin PLCC                                                    | 8    |

| Pin Descriptions                                               | 9    |

| ASLIC Device                                                   | 9    |

| ASLAC Device                                                   |      |

| ASLIC/ASLAC Devices Functional Description                     |      |

| Electrical Requirements                                        |      |

| Power Dissipation                                              | . 15 |

| Absolute Maximum Electrical and Thermal Ratings                | . 16 |

| ASLIC Device                                                   | . 16 |

| ASLAC Device                                                   | . 16 |

| Operating ranges                                               | . 16 |

| Environmental                                                  | . 16 |

| Performance Specifications                                     | . 17 |

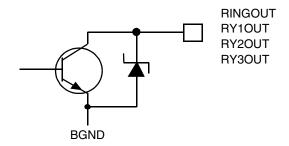

| ASLIC Device Relay Driver Schematic                            | . 18 |

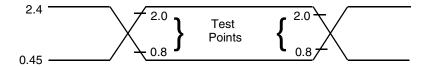

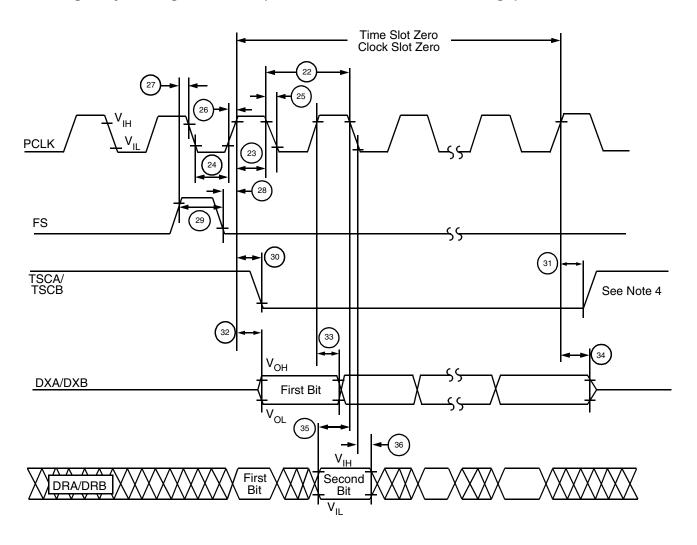

| Switching Characteristics                                      | . 31 |

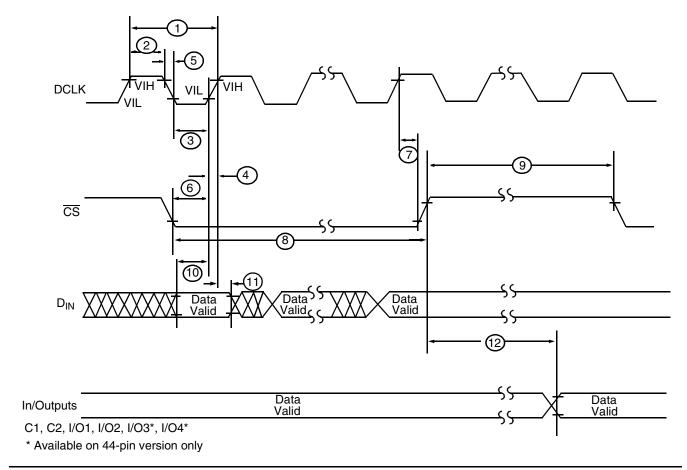

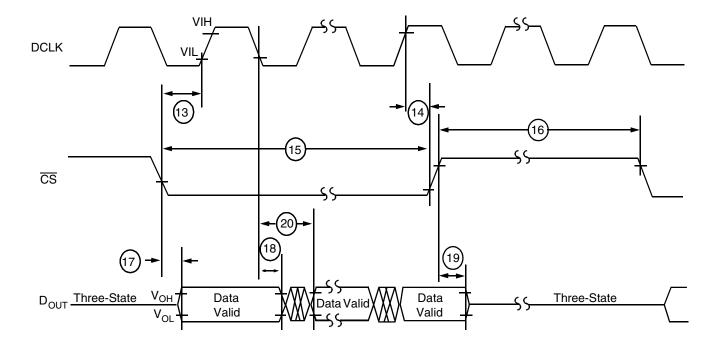

| Microprocessor Interface                                       | . 31 |

| Switching Waveforms                                            | . 34 |

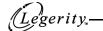

| Input and Output Waveforms for AC Tests                        |      |

| Master Clock Timing                                            | . 34 |

| Microprocessor Interface (Input Mode)                          | . 35 |

| Microprocessor Interface (Output Mode)                         | . 35 |

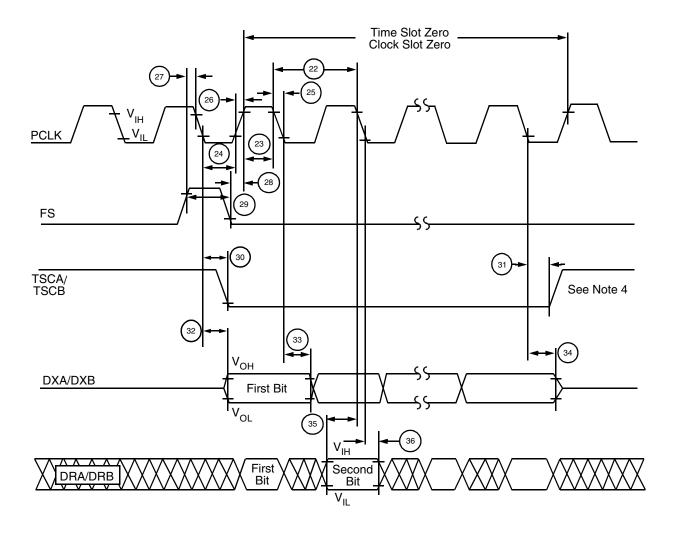

| PCM Highway Timing for XE = 0 (Transmit on Negative PCLK Edge) | . 36 |

| PCM Highway Timing for XE = 1 (Transmit on Positive PCLK Edge) | . 37 |

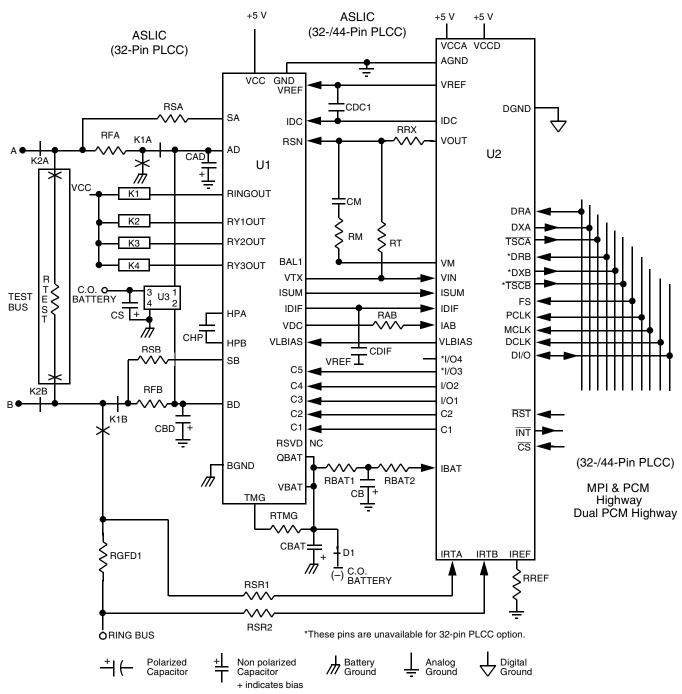

| ASLIC/ASLAC Devices Linecard Schematic                         | . 39 |

| Programmable Filters                                           | . 41 |

| General Description of CSD Coefficients                        | . 41 |

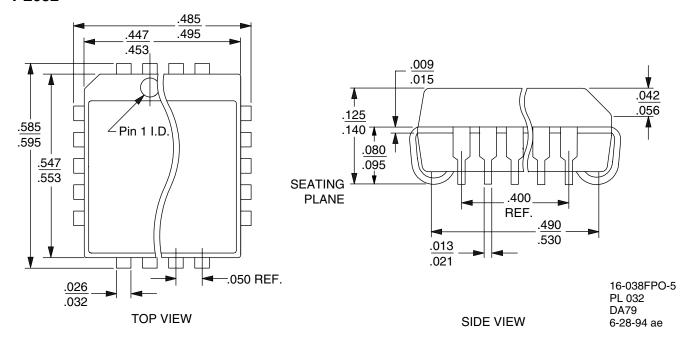

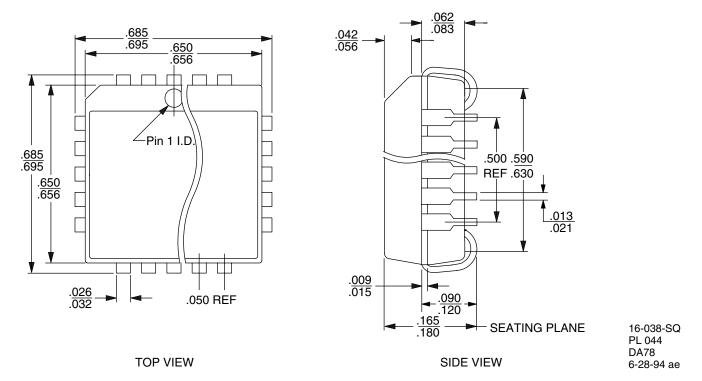

| Physical Dimension                                             | . 43 |

| PL032                                                          | . 43 |

| PL044                                                          | . 43 |

| Rovision Summany                                               | 11   |

| LIST OF FIGURES |                                                        |    |

|-----------------|--------------------------------------------------------|----|

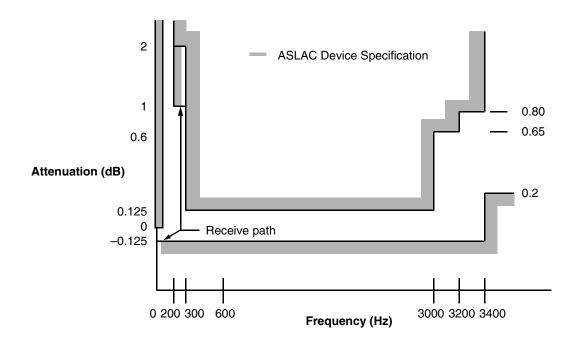

| Figure 1.       | Transmit and Receive Path Attenuation vs. Frequency    | 26 |

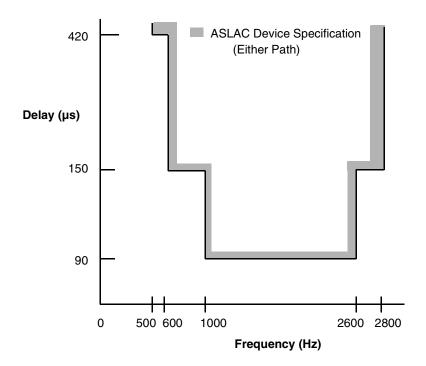

| Figure 2.       | Group Delay Distortion                                 | 27 |

| Figure 3.       | A-law Gain Linearity with Tone Input (Both Paths)      | 28 |

| Figure 4.       | μ-law Gain Linearity with Tone Input (Both Paths)      | 28 |

| Figure 5.       | Total Distortion with Tone Input (Both Paths)          |    |

| Figure 6.       | A/A Overload Compression                               | 30 |

| Figure 7.       | ASLIC/ASLAC Typical Linecard Schematic                 | 39 |

| LIST OF TABLES  |                                                        |    |

| Table 1.        | Power Dissipation                                      | 15 |

| Table 2.        | ASLIC Device DC Specifications                         | 17 |

| Table 3.        | ASLIC Device Relay Driver Specifications               |    |

| Table 4.        | ASLIC Device Transmission Specifications               |    |

| Table 5.        | ASLAC Device DC Specifications                         |    |

| Table 6.        | ASLAC Device Transmission and Signaling Specifications |    |

| Table 7.        | Microprocessor Interface                               |    |

| Table 8.        | PCM Interface                                          |    |

| Table 9.        | Master Clock                                           | 33 |

| Table 10.       | User-Programmable Components                           |    |

| Table 11        | ASLIC/ASLAC Devices Linecard Parts List                |    |

The Am79213/Am79C203/031 Advanced Subscriber Line Interface chip set implements a universal telephone line interface function. This enables the design of a single, low cost, high performance, fully software programmable line interface card for multiple country applications world wide. All AC, DC, and signaling parameters are fully programmable via the microprocessor interface.

Additionally, the ASLIC device and ASLAC device have integrated self test and line test capabilities to resolve faults to the line or line circuit. The integrated test capability is crucial for remote applications where dedicated test hardware is not cost effective. The Technical Reference, PID 21325A is recommended to be used with this document.

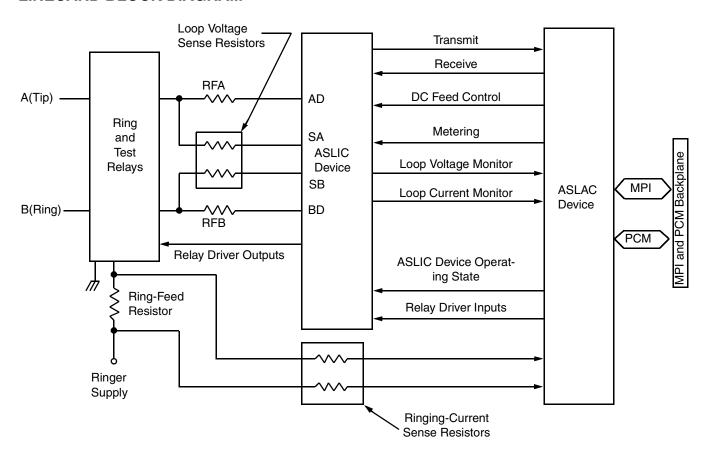

### LINECARD BLOCK DIAGRAM

### **ORDERING INFORMATION**

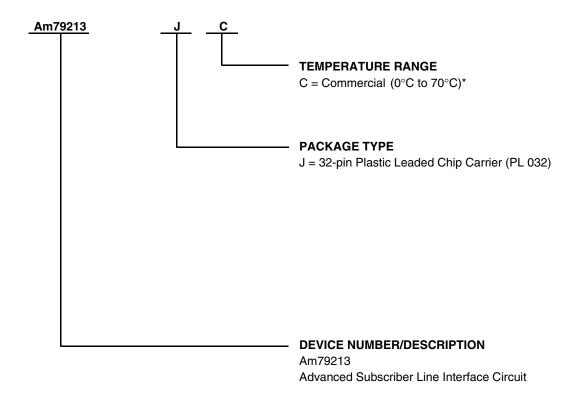

### **ASLIC Device**

Must order Am79C203 or Am79C2031 with the device below.

| Valid Com | binations |

|-----------|-----------|

| Am79213   | JC        |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local Legerity sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### Note:

<sup>\*</sup> Functionality of the device from 0°C to +70°C is guaranteed by production testing. Performance from –40°C to +85°C is guaranteed by characterization and periodic sampling of production units.

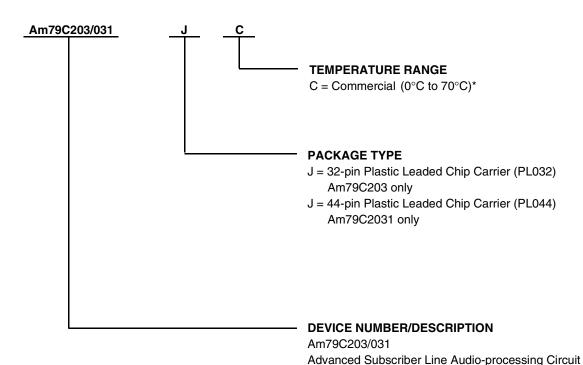

### **ORDERING INFORMATION (continued)**

### **ASLAC Device**

Must order Am79213 with the device below.

| Valid Com | binations |

|-----------|-----------|

| Am79C203  | JC        |

| Am79C2031 |           |

### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local Legerity sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### Note:

<sup>\*</sup> Functionality of the device from  $0^{\circ}$ C to  $+70^{\circ}$ C is guaranteed by production testing. Performance from  $-40^{\circ}$ C to  $+85^{\circ}$ C is guaranteed by characterization and periodic sampling of production units.

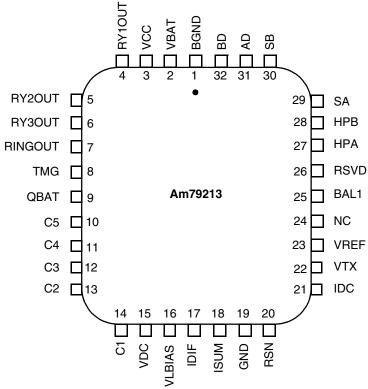

### **CONNECTION DIAGRAMS**

# Top View 32-Pin PLCC

Notes

1. RSVD = Reserved. Do not connect to this pin.

2. NC = No Connect

### **CONNECTION DIAGRAMS (continued)**

# Top View 44-Pin PLCC

#### Note:

RSVD = Reserved. Do not connect to this pin.

### **PIN DESCRIPTIONS**

### **ASLIC Device**

| Pin Names                                | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AD, BD                                   | Output    | A and B Line Drivers. These pins provide the currents to the A and B leads of the subscriber loop.                                                                                                                                                                                                                                                                                                                                                                  |  |

| BAL1                                     | Input     | Pre-balance. This pin receives voltages that are added to the VTX output signal. They can be used to cancel out the metering echo in the transmit path.                                                                                                                                                                                                                                                                                                             |  |

| BGND                                     | Gnd       | Battery Ground. This pin connects to the ground return for Central Office or talk battery.                                                                                                                                                                                                                                                                                                                                                                          |  |

| C2-C1                                    | Input     | ASLIC Device Control. These ternary logic input pins control the operating state of the ASLIC device.                                                                                                                                                                                                                                                                                                                                                               |  |

| C5–C3                                    | Input     | Test Relay Control. These are control inputs for the test relay drivers in the ASLIC device. A logic Low turns on the relay driver and activates the relay. C3 controls RY1OUT, C4 controls RY2OUT, and C5 controls RY3OUT.                                                                                                                                                                                                                                         |  |

| GND                                      | Gnd       | Analog and digital ground return for VCC.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| HPA, HPB                                 | Capacitor | High-Pass Filter Capacitor Connections. These pins connect to CHP, the external high-pass filter capacitor that isolates the DC control loop from the voice transmission path.                                                                                                                                                                                                                                                                                      |  |

| IDC                                      | Input     | DC Loop Control Current. The DC loop current control line from the ASLAC device is connected to this pin. An internal resistance is provided between the IDC pin and RSN. An external noise filter capacitor should be connected between this pin and VREF.                                                                                                                                                                                                         |  |

| IDIF                                     | Output    | A – B Leg Current. The current at this pin is proportional to the difference of the currents flowing out of the AD pin and into the BD pin of the ASLIC device.                                                                                                                                                                                                                                                                                                     |  |

| ISUM                                     | Output    | A + B Leg Current. The current at this pin is proportional to the absolute value of the sum of the currents flowing out of the AD pin and into the BD pin of the ASLIC device.                                                                                                                                                                                                                                                                                      |  |

| QBAT                                     | Power     | Quiet Battery Voltage. The QBAT pin is connected to the substrate.                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| RINGOUT,<br>RY1OUT,<br>RY2OUT,<br>RY3OUT | Output    | Relay Drivers. These are open collector, high current relay driver outputs with emitters internally connected to BGND. To absorb the inductive pulse from the relay coils, an internal Zener diode is connected between the collector of each driver and BGND.                                                                                                                                                                                                      |  |

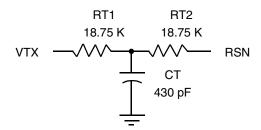

| RSN                                      | Input     | Receive Summing Node. The metallic current (both AC and DC) between AD and BD is equal to ASLIC device current gain, K1, times the current into this pin. Networks that program receive gain and two-wire impedance connect to this node. This input is nominally at VREF potential.                                                                                                                                                                                |  |

| RSVD                                     | Input     | Reserved. This is used during Legerity testing. In the application, this pin must be floating.                                                                                                                                                                                                                                                                                                                                                                      |  |

| SA, SB                                   | Input     | A and B Lead Voltage Sense. These pins sense the voltages on the line side of the fuse resistors at the A and B leads. External sense resistors, RSA and RSB, are required to protect these pins from lightning or power cross conditions.                                                                                                                                                                                                                          |  |

| TMG                                      | Thermal   | Thermal Management. A resistor connected from this pin to VBAT reduces the on-chip power dissipation by absorbing excess power from the ASLIC device for short-loop conditions.                                                                                                                                                                                                                                                                                     |  |

| VBAT                                     | Power     | Battery Voltage. This pin supplies battery voltage to the line drivers.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| VCC                                      | Power     | Power Supply. This is the positive supply for low voltage analog and digital circuits in the ASLIC device.                                                                                                                                                                                                                                                                                                                                                          |  |

| VDC                                      | Output    | DC Loop VoltageThe voltage on this output is referenced to VREF and is proportional to the negative absolute value of the DC subscriber loop voltage between A and B. This voltage is a fraction ( $\beta$ ) of the voltage between HPA and HPB. This pin connects to the IAB pin on the ASLAC device through external resistor RAB. A voltage that is significantly more positive than VREF on the VDC pin indicates that the ASLIC device is in thermal shutdown. |  |

| Pin Names | Туре   | Description                                                                                                                                                                                                                                                                                         |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VLBIAS    | Input  | Longitudinal Offset Voltage. The input to this pin is the offset reference voltage for the ASLIC device longitudinal control loop.                                                                                                                                                                  |

| VREF      | Input  | Analog Reference. This voltage is provided by the ASLAC device and is used by the ASLIC device for internal reference purposes. All analog input and output signals interfacing to the ASLAC device are referenced to this pin. Nominally set to 2.1 V.                                             |

| VTX       | Output | Four-Wire Transmit Signal. The voltage between this pin and VREF is a scaled version of the AC component of the voltage sensed between the SA and SB pins. One end of the two-wire input impedance programming network connects to VTX. The voltage at VTX swings positive and negative about VREF. |

### **ASLAC Device**

| Pin Names | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND      | Gnd                  | Analog (Quiet) Ground. VREF is referenced to this ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| C2-C1     | Output               | ASLIC Device Control. These ternary logic output pins are dedicated to controlling the operating state of the ASLIC device. The levels of these outputs are logic High, logic Low, and high impedance.                                                                                                                                                                                                                                                                                                                  |

| CS        | Input, Active<br>Low | Chip Select. The chip select input (active Low) enables the device so commands and data can be written to or read from it. If chip select is held Low for 16 or more DCLK cycles (independent of MCLK or PCLK), a hardware reset is executed at the time chip select returns to logic 1.                                                                                                                                                                                                                                |

| DCLK      | Input                | Data Clock. The data clock input shifts data into or out of the microprocessor interface of the ASLAC device. The maximum clock rate is 4.096 MHz.                                                                                                                                                                                                                                                                                                                                                                      |

| DGND      | Gnd                  | Digital Ground. Digital ground return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DI/O      | Input/Output         | Data Input/Output. Control data is serially written into and read out of the ASLAC device via the DI/O pin, with the most significant bit first. The data clock (DCLK) determines the data rate. DI/O is high impedance except when data is being transmitted from the ASLAC device under control of CS.                                                                                                                                                                                                                |

| DRA, DRB  | Input                | Receive PCM Data. Receive PCM data is received serially on either the DRA or DRB port, with port selection under user program control. Data is received, most significant bit first, in 8-bit PCM or 16-bit linear 2's complement bursts every 125 µs at the PCLK rate. The receive port is unaffected by the setting of the SMODE bit. (DRB – 44-pin PLCC only.)                                                                                                                                                       |

| DXA, DXB  | Output               | Transmit PCM Data. Transmit PCM data is transmitted serially through either the DXA or DXB port, with port selection under user control. The transmission data output is available every 125 µs and is shifted out, most significant bit first, in 8-bit PCM or 16-bit linear 2's complement bursts at the PCLK rate. DXA/B are high impedance between bursts and while the device is in the Inactive state.  For signaling register operation on the PCM highway, see the SMODE description. (DXB – 44-pin PLCC only.) |

| FS        | Input                | Frame Sync. The frame sync signal is an 8 kHz pulse that identifies the beginning of a frame. The ASLAC device references individual time slots with respect to this input, which must be synchronized to PCLK.                                                                                                                                                                                                                                                                                                         |

| IAB       | Input                | Loop Voltage Sense. The IAB pin is a current summing node referenced to VREF. An external resistor (RAB) is connected between this pin and the VDC pin of the ASLIC device, In normal operation, current flows <u>out</u> of this pin. When the ASLIC device is in thermal shutdown, current will be forced <u>into</u> this pin.                                                                                                                                                                                       |

| IBAT      | Input                | Battery Voltage Sense. The IBAT pin is a current summing node referenced to AGND and receives a current that is proportional to the system battery voltage. A sense resistor/capacitor network is connected between the QBAT pin of the ASLIC device and the IBAT pin.                                                                                                                                                                                                                                                  |

| Pin Names                                                                    | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDC                                                                          | Output                | DC Loop Control Current. The IDC output supplies a current to the ASLIC device for proportional control of the DC loop current flowing through the subscriber loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IDIF                                                                         | Input                 | Longitudinal Sense. IDIF is a current input pin fed by the IDIF pin of the ASLIC device. The current in this pin is used by the ASLAC device for supervisory and diagnostic functions. The IDIF pin has an internal input resistance so an external longitudinal noise filter capacitor can be connected.                                                                                                                                                                                                                                                                                                                                                  |

| ĪNT                                                                          | Output, Active<br>Low | Interrupt. A logic 0 on this pin indicates one or more of the bits in the signaling register has changed states. An interrupt will be generated when activity is sensed on any signal in the Signaling Register not masked by the Mask Register. Once an unmasked activity is sensed, the $\overline{\text{INT}}$ output will be driven Low and held at that state until cleared. See the description of configuration register 6 for operation.                                                                                                                                                                                                           |

| I/O <sub>1</sub> , I/O <sub>2</sub> , I/O <sub>3</sub> ,<br>I/O <sub>4</sub> | Input/output          | Control Ports. These control lines are TTL compatible and each can be programmed as an input or an output. When programmed as inputs, they can monitor external, TTL compatible logic circuits. When programmed as outputs, they can control an external logic device or they can be connected to pin C3, C4, or C5 of the ASLIC device to control test relay drivers RY1OUT, RY2OUT and RY3OUT (I/O <sub>3</sub> , I/O <sub>4</sub> , 44-pin PLCC version only). In the Output mode, these pins are controlled by the I/O <sub>1</sub> , I/O <sub>2</sub> , I/O <sub>3</sub> , and I/O <sub>4</sub> bits in the Channel Control Register, MPI Command 17. |

| IREF                                                                         | Reference             | Current Reference. An external resistor (RREF) connected between this pin and analog ground generates an accurate on-chip reference current. This current is used by the ASLAC device in its DC Feed and loop-supervision circuits.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IRTA, IRTB                                                                   | Inputs                | Ring Trip Sense. These pins are current summing nodes referenced to VREF. They provide terminations for external resistors RSR1 and RSR2, which sense the voltages on both sides of the ringing feed resistor connected to the ring bus. To determine the ringing current in the loop, the ASLAC device senses the difference between the currents in these pins.                                                                                                                                                                                                                                                                                          |

| ISUM                                                                         | Input                 | Metallic Sense. ISUM is a current input pin and is fed by the ISUM pin of the ASLIC device. The absolute value of the current in this pin is used by the ASLAC device for supervisory and diagnostic functions.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MCLK                                                                         | Input                 | Master Clock. The master clock is used to operate the digital signal processor. MCLK can be 2.048 MHz, 4.096 MHz or 8.192 MHz. MCLK may be asynchronous to PCLK. Upon initialization, the MCLK input is disabled and relevant circuitry is driven by a connection to PCLK. The MCLK connection may be reestablished under user control.                                                                                                                                                                                                                                                                                                                    |

| PCLK                                                                         | Input                 | PCM Clock. The PCM clock determines the rate at which PCM data is serially shifted into or out of the PCM ports. PCLK is an integer multiple of the frame sync frequency. The maximum clock frequency is 8.192 MHz and the minimum clock frequency is 128 kHz for companded data. The minimum clock frequency for linear or companded data plus signaling data is 256 kHz. The PCLK clock may be asynchronous to MCLK if the initial connection state is disabled under user control.                                                                                                                                                                      |

| RST                                                                          | Input, Active<br>Low  | Reset. A logic 0 on this pin resets the ASLAC device to initial default conditions. It is equivalent to a hardware reset command. A signal less than 100 ns should not cause a reset. To ensure proper reset, the minimum length of a reset pulse is 50 µs.                                                                                                                                                                                                                                                                                                                                                                                                |

| TSCA, TSCB                                                                   | Open Drain<br>Outputs | Time Slot Control. The time slot control outputs are open drain (requiring an external pull-up resistor to VCCD) and are normally inactive (high impedance). TSCA is active (Low) when PCM data is present on DXA, and TSCB is active (Low) when PCM data is present on DXB. (TSCB and DRB – 44-pin PLCC only.)                                                                                                                                                                                                                                                                                                                                            |

| VCCA                                                                         | Power                 | Analog Power Supply. VCCA is internally connected to substrate near the analog I/O section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VCCD                                                                         | Power                 | Digital Power Supply. VCCD is internally connected to substrate near the digital section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VIN                                                                          | Input                 | Analog Input. The analog output (VTX) from the ASLIC device is applied to the ASLAC device transmit path input, VIN. The signal is sampled, processed, encoded, and transmitted on the PCM Highway.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin Names | Туре   | Description                                                                                                                                                                           |

|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VLBIAS    | Output | Longitudinal Reference. VLBIAS is programmed by VOFF and supplies the longitudinal reference voltage for the longitudinal control loop to the ASLIC device.                           |

| VM        | Output | 12/16 kHz Metering Signal. For 12/16 kHz teletax, an internally generated and shaped 12 or 16 kHz sine wave metering pulse is output from this pin.                                   |

| VOUT      | Output | Analog Output. The voice data from the received PCM channel (timeslot) is digitally processed and converted to an analog signal which is present on the VOUT pin of the ASLAC device. |

| VREF      | Output | Analog Reference. This pin provides a voltage reference to be used as the analog zero level reference on the ASLIC device.                                                            |

# ASLIC/ASLAC DEVICES FUNCTIONAL DESCRIPTION

The ASLIC/ASLAC devices chip set integrates all functions of the subscriber line. The chip set comprises an ASLIC device and an ASLAC device. The set provides two basic functions: 1) the ASLIC device, a high-voltage, bipolar device that drives the subscriber line, maintains longitudinal balance, and senses line conditions; and 2) the ASLAC device, a low-voltage CMOS device that combines CODEC, DC Feed control, and line supervision. A complete schematic of a linecard using the ASLIC/ASLAC devices chip set is shown in the Figure 7.

The ASLIC device uses reliable, bipolar technology to provide the power necessary to drive a wide variety of subscriber lines. It can be programmed by the ASLAC device to operate in eight different states that control Power Consumption and Signaling states. This enables full control over the subscriber loop. The ASLIC device is customized to be used exclusively with the ASLAC device, providing a two-chip universal line interface. The ASLIC device requires only a +5 V power supply and a negative battery supply for its operation.

The ASLIC device implements a linear loop current feeding method with the enhancement of thermal management to limit the amount of power dissipated on the ASLIC device by dissipating excess power in an external resistor.

The ASLAC device is a high-performance, CMOS CO-DEC/filter device with additional digital filters and circuits that allow software control of transmission, DC Feed, and supervision.

Advanced CMOS technology makes the ASLAC device an economical device that has both the functionality and the low power consumption required by linecard designers to maximize linecard density at minimum cost.

When used with an ASLIC device, the ASLAC device provides a complete software-configurable solution to linecard functions. In addition, the ASLIC/ASLAC devices chip set provides system-level solutions for loop supervisory functions and metering. In total, the ASLIC/ASLAC devices chip set provides a programmable solution that can satisfy worldwide linecard requirements by software configuration.

All software-programmed coefficients and DC Feed parameters are easily calculated with the AmSLAC3  $^{\!\!\!\!\!^{\mathsf{TM}}}$  software. This software is provided free of charge and runs on an IBM-compatible PC. It allows the designer to enter a description of system requirements, then the software returns the necessary coefficients and the predicted system response.

The ASLAC device uses the industry standard microprocessor (MPI) and PCM interfaces to communicate with the system and for interfacing to the 64 kilobit per second voice network. The ASLIC device interface unit inside the ASLAC device processes information regarding line voltages, loop currents, and battery voltage levels. These inputs allow the ASLAC device to place several key ASLIC device performance parameters under programmable supervision.

The main functions that can be observed and/or controlled through the ASLAC device control interface are:

- DC Feed characteristics

- Ground-key detection

- Off-hook detection

- Metering signal

- Longitudinal operating point

- Subscriber line voltage and currents

- Ring trip

- Abrupt and smooth battery polarity reversal

To accomplish these functions, the ASLAC device collects the following information from the ASLIC device and the Central Office system:

- The sum and difference of the currents in each loop leg, ISUM, and IDIF

- Currents proportional to the:

- voltage across the loop (IAB)

- battery voltage (IBAT)

- ringing current in the loop (IRTA IRTB)

The outputs supplied by the ASLAC device are then:

- A current proportional to the desired DC loop current (IDC)

- A voltage proportional to the desired longitudinal offset voltage (VLBIAS)

- A 12/16 kHz metering signal (appears on VM for 12/16 kHz teletax)

The ASLAC device performs the CODEC and filter functions associated with the four-wire section of the subscriber line circuitry in a digital switch. These functions involve converting an analog voice signal into digital PCM samples and converting digital PCM samples back into an analog signal. During conversion, digital filters are used to band-limit the voice signals.

The user-programmable filters set the receive and transmit gain, perform the transhybrid balancing function, permit adjustment of the two-wire termination impedance, and provide frequency response adjustment (equalization) of the receive and transmit paths. Adaptive transhybrid balancing is also included.

The PCM data can be either 8-bit companded A-law code, 8-bit companded  $\mu$ -law code, or 16-bit linear code. Voice data is transmitted and received via the PCM highway; control information is written to and read from the ASLAC/ASLIC devices chip set over the microprocessor interface.

Besides the CODEC functions, the ASLAC device provides all the sensing, feedback, and clocking necessary to completely control ASLIC device functions with programmable parameters. The line status is continuously available in the ASLAC Device Signaling Register, which is continuously available via the MPI interface, or on the PCM highway via a user-programmable mode. A programmable interrupt provides added flexibility in monitoring line status. System-level parameters under programmable control include active and disable loop-current limits, feed resistance, and apparent battery-feed voltage. The longitudinal operating point is programmable to optimize the ASLIC device signal swing capability.

The ASLAC device provides signals at 12 or 16 kHz for metering functions. The frequency and level of these signals are programmable.

The ASLAC device provides extensive loop supervision capability, including off-hook, ring-trip, and ground-key detection. Detection thresholds for these functions are programmable. A programmable debounce timer is available that eliminates false detection due to contact bounce. For subscriber line diagnostics, AC and DC line conditions can be monitored using special test modes. Results are read using the MPI commands.

### **ELECTRICAL REQUIREMENTS**

### **Power Dissipation**

Loop resistance = 0 to  $\infty$  (not including fuse resistors), 2 x 50  $\Omega$  fuse resistors, VBAT = QBAT = -48 V, VCC = +5 V. For power dissipation measurements, DC Feed conditions are programmed as follows:

VAPP (apparent voltage) = 50.2 V

ILA (Active state current limit) = 42.3 mA

ILD (Disable state current limit) = 21.2 mA

RFD (feed resistance) = 807  $\Omega$

VAS (anti-sat activate voltage) = 8.2 V

N2 (anti-sat feed resistance factor) = 2

VOFF (longitudinal offset voltage) = 6 V

RTMG (thermal management resistor) = 1200  $\Omega$

RREF (reference current setting resistor) =  $7.87 \text{ k}\Omega$

**Table 1. Power Dissipation**

| Description                    | Test Conditions                                         | Min | Тур | Max  | Unit |

|--------------------------------|---------------------------------------------------------|-----|-----|------|------|

| ASLIC device power dissipation | On-hook Disconnect                                      |     | 30  | 70   |      |

| Normal polarity                | On-hook Standby                                         |     | 50  | 105  |      |

|                                | On-hook Disable                                         |     | 120 | 215  |      |

|                                | On-hook Active                                          |     | 330 | 450  |      |

|                                | Off-hook Active $R_L = 294 \Omega$                      |     | 850 | 1200 |      |

|                                | Off-hook Disable R <sub>L</sub> = 600 $\Omega$          |     | 800 | 950  | mW   |

| ASLAC device power dissipation | ASLAC device activated                                  |     | 85  | 110  |      |

| MCLK, PCLK = 2.048 MHz         | ASLAC device inactive, MPI Standby state command issued |     | 22  | 25   |      |

| ASLAC device power dissipation | ASLAC device activated                                  |     | 95  | 120  |      |

| MCLK, PCLK > 2.048 MHz         | ASLAC device inactive, MPI Standby state command issued |     | 23  | 26   |      |

#### **Thermal Resistance**

The junction-to-air thermal resistance of the ASLIC device in a 32-pin PLCC package will be less than 45°C/W.

The junction-to-air thermal resistance of the ASLAC device in a 32-pin PLCC package will be less than 45°C/W.

The junction-to-air thermal resistance of the ASLAC device in a 44-pin PLCC package will be less than 44°C/W.

# ABSOLUTE MAXIMUM ELECTRICAL AND THERMAL RATINGS

### **ASLIC Device**

| Storage temperature55°C $\leq$ T <sub>A</sub> $\leq$ +150°C   |

|---------------------------------------------------------------|

| Ambient temperature, under bias40°C $\leq$ $T_{A} \leq$ +85°C |

| Ambient relative humidity                                     |

| (noncondensing)5% to 100%                                     |

| $V_{CC}$ with respect to AGND/DGND–0.4 V to +7 V              |

| $V_{BAT},Q_{BAT}$ with respect to BGND+0.4 V to –75 V         |

| $V_{CC}$ with respect to $V_{BAT},Q_{BAT}$ +80 V              |

| BGND with respect to                                          |

| AGND/DGND0.5 V to +0.5 V                                      |

| Voltage on relay outputs+7 V                                  |

| AD or BD to BGND:                                             |

| Continuous–75 V to +1 V                                       |

| 10 ms (f = 0.1 Hz)75 V to +5 V                                |

| 1 μs (f = 0.1 Hz)90 V to +10 V                                |

| 250 ns (f = 0.1 Hz)120 V to +15 V                             |

| Current into SA or SB: 10 µs rise to Ipeak;                   |

| 1000 μs fall to 0.5 lpeak;                                    |

| 2000 µs fall to I = 0 lpeak = ±5 mA                           |

| Current into SA or SB: 2 µs rise to Ipeak;                    |

| 10 μs fall to 0.5 lpeak;                                      |

| 20 $\mu$ s fall to I = 0 Ipeak = $\pm 12.5$ mA                |

| Current through AD or BD ±150 mA                              |

| C5–C1                                                         |

| to DGND or AGND $-0.4 \text{ V}$ to $V_{CC} + 0.4 \text{ V}$  |

| Maximum power dissipation, $T_A = 70^{\circ}C$ 1.67 W         |

**Note:** Thermal limiting circuitry on chip will shut down the circuit at a junction temperature of about 160°C. The device should never be exposed to this temperature. Operation above 145°C junction temperature may degrade device reliability. See the SLIC Packaging Considerations for more information.

### **ASLAC Device**

| Storage temperature $-60^{\circ}C \le T_{A} \le +125^{\circ}C$                                       |

|------------------------------------------------------------------------------------------------------|

| Ambient temperature, $-40^{\circ}C \leq T_{A} \leq +85^{\circ}C$ under bias                          |

| Ambient relative humidity (noncondensing)                                                            |

| $V_{CCA}$ with respect to $V_{CCD}\pm 0.4~\text{V}$                                                  |

| $V_{\mbox{\footnotesize{IN}}}$ with respect to DGND–0.4 V to $V_{\mbox{\footnotesize{CCA}}}$ + 0.4 V |

| AGND DGND ±0.4 V                                                                                     |

| Latch up immunity (any pin)±100 mA                                                                   |

| Any other pin with respect to DGND0.4 V to V <sub>CC</sub> + 0.4 V                                   |

|                                                                                                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

### **OPERATING RANGES**

### **Environmental**

| Environmental                                                   |

|-----------------------------------------------------------------|

| Ambient temperature0°C to +70°C Commercial*                     |

| Ambient relative humidity15% to 85%                             |

| ASLIC Device                                                    |

| V <sub>CC</sub> +5 V ± 5%                                       |

| V <sub>BAT</sub> , Q <sub>BAT</sub> 18 V to -70 V               |

| BGND with respect to GND $-100\mathrm{mV}$ to $+100\mathrm{mV}$ |

| Load resistance on $V_{TX}$ to ground 10 $k\Omega$ min          |

| ASLAC Device                                                    |

| Supplies $V_{CCA}$ , $V_{CCD}$ +5 $V \pm 5\%$                   |

| DGND0 V                                                         |

| AGNDDGND ± 50 mV                                                |

Operating ranges define those limits over which the functionality of the device is guaranteed by production testing.

<sup>\*</sup> Functionality of the device from 0°C to +70°C is guaranteed by production testing. Performance from -40°C to +85°C is guaranteed by characterization and periodic sampling of production units.

### PERFORMANCE SPECIFICATIONS

(See note 1)  $T_A$  = 0°C to 70°C unless otherwise noted.

**Table 2. ASLIC Device DC Specifications**

| No. | Item                                                                                           | Condition                                                                                                                                            | Min                    | Тур                    | Max                    | Unit | Note |

|-----|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|------|------|

| 1   | 2-wire loop voltage                                                                            | Standby state, $R_L = 1 M\Omega$                                                                                                                     | Q <sub>BAT</sub> – 1.8 | Q <sub>BAT</sub> – 1.1 | Q <sub>BAT</sub> – 0.5 |      | 4    |

|     |                                                                                                | Active state, RL <sub>AD-BD</sub> = 600 $\Omega$ IRSN = 140 $\mu$ A                                                                                  | 19.51                  | 21.1                   | 22.68                  | V    |      |

|     |                                                                                                | Disable state, $RL_{AD-BD}$ = 600 $\Omega$ IRSN = 80 $\mu A$                                                                                         | 11.34                  | 12.19                  | 13.04                  |      |      |

| 2   | Feed resistance per leg at pins AD and BD                                                      | Standby state                                                                                                                                        | 130                    | 250                    | 375                    | Ω    |      |

| 3   | ISUM current                                                                                   | Standby state, $R_L = 1930 \Omega$                                                                                                                   | 44.6                   | 56                     |                        |      |      |

|     | IDIF current                                                                                   | Standby state<br>A to Q <sub>BAT</sub><br>B to ground                                                                                                | 35.4<br>43.4           |                        |                        | μΑ   |      |

| 4   |                                                                                                | undaries for C2–C1 pins. Mid-<br>e high impedance or 3-state                                                                                         |                        |                        |                        |      |      |

|     | Low boundary                                                                                   |                                                                                                                                                      |                        |                        | 0.8                    | V    |      |

|     | High boundary                                                                                  |                                                                                                                                                      | V <sub>CC</sub> – 1    |                        |                        | V    |      |

|     | Logic inputs C2–C1 Input High current                                                          |                                                                                                                                                      |                        | -80                    | 200                    | μA   |      |

|     | Input Low current                                                                              |                                                                                                                                                      |                        | 90                     | 200                    |      |      |

|     | 3-state voltage                                                                                | I <sub>C1</sub> = I <sub>C2</sub> = 1 μA                                                                                                             | 0.8                    |                        | 3.5                    |      | 4    |

| 5   | Logic inputs C5–C3<br>Input High voltage                                                       |                                                                                                                                                      | 2.0                    |                        |                        | V    |      |

|     | Input Low voltage                                                                              |                                                                                                                                                      |                        |                        | 0.8                    |      |      |

|     | Input High current                                                                             |                                                                                                                                                      | -200                   |                        | 40                     |      |      |

|     | Input Low current                                                                              |                                                                                                                                                      | -400                   |                        | 40                     | μΑ   |      |

| 6   | V <sub>TX</sub> output offset                                                                  | BAL1 pin open                                                                                                                                        | -50                    |                        | +50                    | mV   |      |

| 7   | V <sub>REF</sub> input voltage                                                                 | IREF = ±1 mA                                                                                                                                         | 2.0                    | 2.1                    | 2.2                    | ٧    |      |

| 8   | $\beta$ , Ratio of V <sub>DC</sub> to loop voltage: $\beta = \frac{ VDC  - VREF}{ VSA - VSB }$ | $T_{\rm J}$ < 145°C, $V_{\rm DC}$ is referenced to $V_{\rm REF}$ , 35.7 kΩ resistor connected from $V_{\rm DC}$ to $V_{\rm REF}$ . VSA – VSB = 40 V. | 0.0253                 | 0.0242                 | 0.0232                 | V/V  |      |

| 9   | Thermal shutdown threshold voltage output on V <sub>DC</sub>                                   | I <sub>VDC</sub> = 20 μA                                                                                                                             | 4.2                    | V <sub>CC</sub> - 0.4  |                        | V    | 4    |

| 10  | Gain from VLBIAS pin to<br>AD or BD pin                                                        |                                                                                                                                                      | 5.58                   | 6.0                    | 6.42                   | V/V  |      |

| 11  | Input resistance to AGND, VLBIAS pin                                                           | VLBIAS = 3 V                                                                                                                                         | 20                     | 33.3                   |                        | kΩ   |      |

**Table 2. ASLIC Device DC Specifications (continued)**

| No. | Item                              | Condition                   | Min   | Тур   | Max   | Unit | Note |

|-----|-----------------------------------|-----------------------------|-------|-------|-------|------|------|

| 12  | ISUM/ILOOP                        | ILOOP = 10 mA               | 1/333 | 1/300 | 1/273 |      |      |

| 13  | IDIF/ILONG                        | ILONG = 10 mA               | 1/667 | 1/600 | 1/546 |      |      |

| 14  | Input current,<br>SA and SB pins  |                             |       | 1     | 3     | μΑ   |      |

| 15  | Input current<br>HPA and HPB pins |                             |       | 0.1   | 3     | μΑ   | 4    |

| 16  | IDC input impedance               |                             | 1.26  | 1.8   | 3     | kΩ   |      |

| 17  | K1                                | Incremental DC current gain |       | 254   |       | A/A  | 13   |

| 18  | Metallic offset current           |                             |       | 0     | -0.4  | mA   | 13   |

### **ASLIC Device Relay Driver Schematic**

**Table 3. ASLIC Device Relay Driver Specifications**

| Item                           | Condition              | 1           | Min | Тур   | Max | Unit | Note |

|--------------------------------|------------------------|-------------|-----|-------|-----|------|------|

|                                | 25 mA per relay sink   | 1 relay on  |     | 0.225 | 0.3 |      |      |

| On voltage                     |                        | 4 relays on |     | 0.4   | 0.5 | V    | 4    |

| On vollage                     | 40 mA per relay sink   | 1 relay on  |     | 0.45  | 0.7 | V    |      |

|                                |                        | 4 relays on |     | 0.8   | 1.0 |      | 4    |

| Off leakage, each relay driver | V <sub>OH</sub> = +6 V |             | 0   |       | 100 | μΑ   |      |

**Table 4. ASLIC Device Transmission Specifications**

| No. | Item                             | Condition             | Min  | Тур | Max | Unit | Note |

|-----|----------------------------------|-----------------------|------|-----|-----|------|------|

| 1   | R <sub>SN</sub> input impedance  | f = 300 Hz to 3400 Hz |      | 1   |     | Ω    | 4    |

| 2   | V <sub>TX</sub> output impedance |                       |      | 3   |     | 52   | -    |

| 3   | Gain, BAL1 to V <sub>TX</sub>    |                       | 1.4  | 1.5 | 1.6 | V/V  |      |

| 4   | BAL1 input impedance             |                       | 3.17 | 5   | 7.5 | kΩ   |      |

| 5   | Input impedance<br>A or B to GND |                       |      | 70  | 135 | Ω    | 4    |

### **Table 4. ASLIC Device Transmission Specifications (continued)**

| No. | Item                                                     | Condition                                                                                                                                                                                                                                 | Min                  | Тур      | Max                 | Unit              | Note |

|-----|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|---------------------|-------------------|------|

| 6   | 2- to 4-wire gain                                        | -10 dBm, 1 kHz<br>T <sub>A</sub> = -40°C to 0°C/70°C to 85°C                                                                                                                                                                              | -12.19<br>-12.24     | -12.04   | -11.89<br>-11.84    |                   |      |

| 7   | 2- to 4-wire gain variation with frequency               | 300 to 3400 Hz relative to 1 kHz<br>T <sub>A</sub> = -40°C to 0°C/70°C to 85°C                                                                                                                                                            | -0.1<br>-0.15        |          | +0.1<br>+0.15       | ,                 |      |

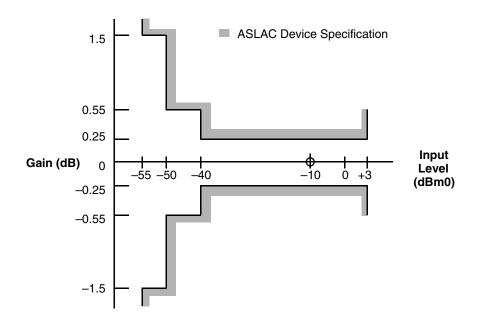

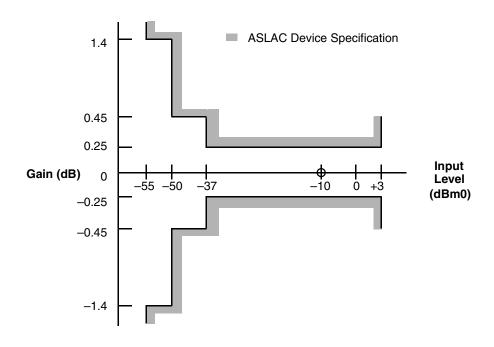

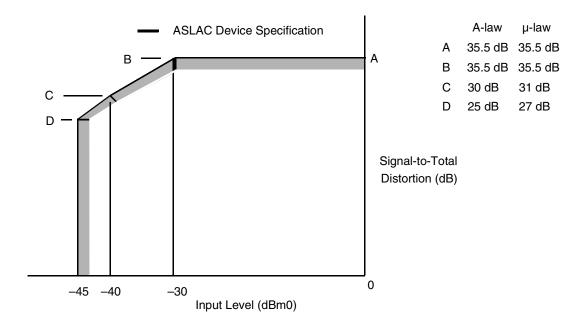

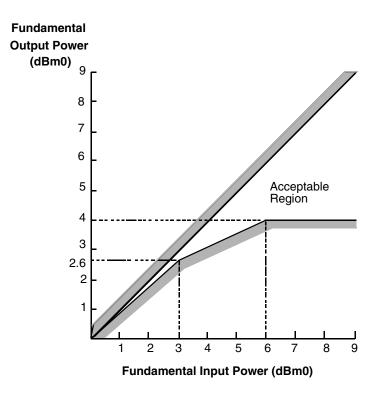

| 8   | 2- to 4-wire gain tracking                               | +3 dBm to -55 dBm<br>Reference: -10 dBm<br>T <sub>A</sub> = -40°C to 0°C/70°C to 85°C                                                                                                                                                     | -0.1<br>-0.15        |          | +0.1<br>+0.15       |                   |      |

| 9   | 4- to 2-wire gain                                        | -10 dBm, 1 kHz<br>T <sub>A</sub> = -40°C to 0°C/70°C to 85°C                                                                                                                                                                              | -0.15<br>-0.20       | 0        | +0.15<br>+0.20      |                   |      |

| 10  | 4- to 2-wire gain variation with frequency               | 300 to 3400 Hz relative to 1 kHz<br>T <sub>A</sub> = -40°C to 0°C/70°C to 85°C                                                                                                                                                            | -0.1<br>-0.15        |          | +0.1<br>+0.15       | dB                |      |

| 11  | 4- to 2-wire gain tracking                               | +3 dBm to -55 dBm<br>Reference: -10 dBm                                                                                                                                                                                                   | -0.1                 |          | +0.1                |                   |      |

| 12  | Total harmonic distortion 2-wire                         | 300 Hz to 3400 Hz<br>0 dBm<br>+4 dBm                                                                                                                                                                                                      | -0.15                |          | +0.15<br>-50<br>-40 |                   |      |

| •   | 4-wire                                                   | –12 dBm<br>–8 dBm                                                                                                                                                                                                                         |                      |          | -50<br>-40          |                   |      |

|     | 2-wire metering overload level                           | VLBIAS = 2.4 V, ILOOP = 30 mA, $V_{BAT} = Q_{BAT} = -60 \text{ V, DC LOAD} = 200 \ \Omega,$ Load at 16 kHz = 10 k $\Omega$                                                                                                                |                      | 42       |                     | Vp-p              | 4    |

| 13  | Idle channel noise<br>C-message<br>weighted              | Active and Disable states 2-wire T <sub>A</sub> = -40°C to 0°C/70°C to 85°C                                                                                                                                                               |                      | +7       | +11<br>+15          | dBrnC             | 4    |

|     |                                                          | 4-wire                                                                                                                                                                                                                                    |                      | -5       |                     |                   | 4    |

|     | Psophometric weighted                                    | 2-wire<br>T <sub>A</sub> = -40°C to 0°C/70°C to 85°C                                                                                                                                                                                      |                      | -83      | –79<br>–75          | Vp-p  dBrnC  dBmp |      |

|     |                                                          | 4-wire                                                                                                                                                                                                                                    |                      | -95      |                     |                   | 4    |

| 14  | Longitudinal balance<br>(IEEE method)<br>Normal polarity | L - T 200 to 1000 Hz<br>$T_A = -40^{\circ}\text{C}$ to $0^{\circ}\text{C}/70^{\circ}\text{C}$ to $85^{\circ}\text{C}$<br>1000 to 3400 Hz<br>$T_A = -40^{\circ}\text{C}$ to $0^{\circ}\text{C}/70^{\circ}\text{C}$ to $85^{\circ}\text{C}$ | 58<br>53<br>53<br>48 | 63<br>58 |                     |                   |      |

|     |                                                          | T - L 200 to 3400 Hz                                                                                                                                                                                                                      | 40                   |          |                     |                   |      |

|     |                                                          | L - T, IL = 0 50 to 3400 Hz                                                                                                                                                                                                               |                      | 63       |                     |                   | 4    |

|     | Reverse polarity                                         | L - T 200 to 1000 Hz<br>T <sub>A</sub> = -40°C to 0°C/70°C to 85°C                                                                                                                                                                        | 50<br>48             |          |                     | dB                |      |

| 15  | PSRR (V <sub>BAT</sub> , Q <sub>BAT</sub> )              | 50 to 3400 Hz                                                                                                                                                                                                                             | 25                   | 45       |                     |                   | 3, 5 |

|     |                                                          | 3.4 kHz to 50 kHz                                                                                                                                                                                                                         | 25                   | 40       |                     |                   | 4    |

|     |                                                          | ASLIC device in Anti-Sat state (loop open) f = 50 Hz, CB = 100 nF f = 200 to 3400 Hz, CB = 100 nF                                                                                                                                         | 2<br>12              |          |                     |                   | 4, 8 |

### **Table 4. ASLIC Device Transmission Specifications (continued)**

| No. | Item                                 | Condition                                                           | Min | Тур | Max | Unit  | Note |

|-----|--------------------------------------|---------------------------------------------------------------------|-----|-----|-----|-------|------|

| 16  | PSRR (V <sub>CC</sub> )              | 50 to 3400 Hz                                                       | 25  | 45  |     | dB    | 3, 5 |

|     |                                      | 3.4 kHz to 50 kHz                                                   | 25  | 35  |     | ub.   | 2, 4 |

| 17  | Low frequency induction (REA method) | Active state, VLONG = 30 Vrms,<br>I <sub>L</sub> = 20 mA, f = 60 Hz |     |     | +23 | dBrnC | 4    |

| 18  | Longitudinal AC current per wire     | f = 15 to 60 Hz                                                     | 20  |     |     | mArms | 7    |

### **Table 5. ASLAC Device DC Specifications**

| No. | Item                                                                                                                                              | Condition                                                                           | Min                    | Тур    | Max                   | Unit | Note |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------|--------|-----------------------|------|------|

| 1   | Input Low voltage                                                                                                                                 | (Any digital input)                                                                 | -0.5                   |        | 0.8                   | V    |      |

| 2   | Input High voltage                                                                                                                                | (Any digital input)                                                                 | 2.0                    |        | V <sub>CC</sub> + 0.5 | V    |      |

| 3   | Input leakage current                                                                                                                             | (Any digital input)                                                                 | -10                    |        | +10                   | μA   | 15   |

| 4   | Input hysteresis (FS and RST only)                                                                                                                |                                                                                     |                        | 0.5    |                       | V    | 4    |