# Am79C960

# PCnet<sup>™</sup>-ISA Single-Chip Ethernet Controller

# **DISTINCTIVE CHARACTERISTICS**

- Single-chip Ethernet controller for the Industry Standard Architecture (ISA) and Extended Industry Standard Architecture (EISA) buses

- Supports IEEE 802.3/ANSI 8802-3 and Ethernet standards

- Direct interface to the ISA or EISA bus

- Software compatible with AMD's Am7990 LANCE register and descriptor architecture

- Low power, CMOS design with sleep mode allows reduced power consumption for critical battery powered applications

- Individual 136-byte transmit and 128-byte receive FIFOs provide packet buffering for increased system latency, and support the following features:

- Automatic retransmission with no FIFO reload

- Automatic receive stripping and transmit padding (individually programmable)

- Automatic runt packet rejection

- Automatic deletion of received collision frames

- Dynamic transmit FCS generation programmable on a frame-by-frame basis

- Single +5 V power supply

- Internal/external loopback capabilities

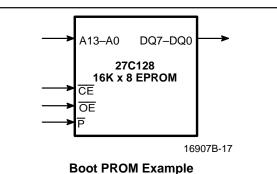

- Supports optional Boot PROM for diskless node applications

### Provides integrated Attachment Unit Interface (AUI) and 10BASE-T transceiver with 3 modes of port selection:

- Automatic selection of AUI or 10BASE-T

- Software selection of AUI or 10BASE-T

- Jumper selection of AUI or 10BASE-T

- Automatic Twisted Pair receive polarity detection and automatic correction of the receive polarity

- Supports bus-master and shared-memory architectures to fit in any PC application

- Supports edge and level-sensitive interrupts

- DMA Buffer Management Unit for reduced CPU intervention

- Integral DMA controller allows higher throughput by by-passing the platform DMA

- JTAG Boundary Scan (IEEE 1149.1) test access port interface for board level production test

- Integrated Manchester Encoder/Decoder

- Supports the following types of network interfaces:

- AUI to external 10BASE2, 10BASE5, 10BASE-T or 10BASE-F MAU

- Internal 10BASE-T transceiver with Smart Squelch to Twisted Pair medium

- Supports LANCE General Purpose Serial Interface (GPSI)

- 120-pin PQFP package

# **GENERAL DESCRIPTION**

The PCnet-ISA controller, a single-chip Ethernet controller, is a highly integrated system solution for the PC-AT Industry Standard Architecture (ISA) architecture. It is designed to provide flexibility and compatibility with any existing PC application. This highly integrated 120-pin VLSI device is specifically designed to reduce parts count and cost, and addresses applications where higher system throughput is desired. The PCnet-ISA controller is fabricated with AMD's advanced low-power CMOS process to provide low stand by current for power sensitive applications.

The PCnet-ISA controller is a DMA-based device with a dual architecture that can be configured in two different

operating modes to suit a particular PC application. In the Bus Master Mode all transfers are performed using the integrated DMA controller. This configuration enhances system performance by allowing the PCnet-ISA controller to bypass the platform DMA controller and directly address the full 24-bit memory space. The implementation of Bus Master Mode allows minimum parts count for the majority of PC applications. The PCnet-ISA controller can be configured to perform Shared Memory operations for compatibility with lowend machines, such as PC/XTs that do not support Bus Master and high-end machines that require local packet buffering for increased system latency. The PCnet-ISA controller is designed to directly interface with the ISA or EISA system bus. It contains an ISA bus interface unit, DMA Buffer Management Unit, IEEE 802.3 Media Access Control function, individual 136-byte transmit and 128-byte receive FIFOs, IEEE 802.3 defined Attachment Unit Interface (AUI), and a Twisted Pair Transceiver Media Attachment Unit. The PCnet-ISA controller is also register compatible with the LANCE (Am7990) Ethernet controller. The DMA Buffer Management Unit supports the LANCE descriptor software model. External remote boot and Ethernet physical address PROMs are also supported.

This advanced Ethernet controller has the built-in capability of automatically selecting either the AUI port or the Twisted Pair transceiver. Only one interface is active at any one time. The individual 136-byte transmit and 128-byte receive FIFOs optimize system overhead, providing sufficient latency during packet transmission and reception, and minimizing intervention during normal network error recovery. The integrated Manchester encoder/decoder eliminates the need for an external Serial Interface Adapter (SIA) in the node system. If support for an external encoding/decoding scheme is desired, the embedded General Purpose Serial Interface (GPSI) allows direct access to/from the MAC. In addition, the device provides programmable on-chip LED drivers for transmit, receive, collision, receive polarity, link integrity, or jabber status. The PCnet-ISA controller also provides an External Address Detection Interface™ (EADI™) to allow external hardware address filtering in internetworking applications.

| Part No. | Description                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------|

| Am79C98  | Twisted Pair Ethernet Transceiver (TPEX)                                                               |

| Am79C100 | Twisted Pair Ethernet Transceiver Plus (TPEX+)                                                         |

| Am7996   | IEEE 802.3/Ethernet/Cheapernet Transceiver                                                             |

| Am79C981 | Integrated Multiport Repeater Plus™ (IMR+™)                                                            |

| Am79C987 | Hardware Implemented Management Information Base™ (HIMIB™)                                             |

| Am79C940 | Media Access Controller for Ethernet (MACE™)                                                           |

| Am7990   | Local Area Network Controller for Ethernet (LANCE)                                                     |

| Am79C90  | CMOS Local Area Network Controller for Ethernet (C-LANCE)                                              |

| Am79C900 | Integrated Local Area Communications Controller™ (ILACC™)                                              |

| Am79C961 | PCnet-ISA <sup>+</sup> Single-Chip Ethernet Controller for ISA (with Microsoft® Plug n' Play® Support) |

| Am79C965 | PCnet-32 Single-Chip 32-Bit Ethernet Controller                                                        |

| Am79C970 | PCnet-PCI Single-Chip Ethernet Controller (for PCI bus)                                                |

| Am79C974 | PCnet-SCSI Combination Ethernet and SCSI Controller for PCI Systems                                    |

# **RELATED PRODUCTS**

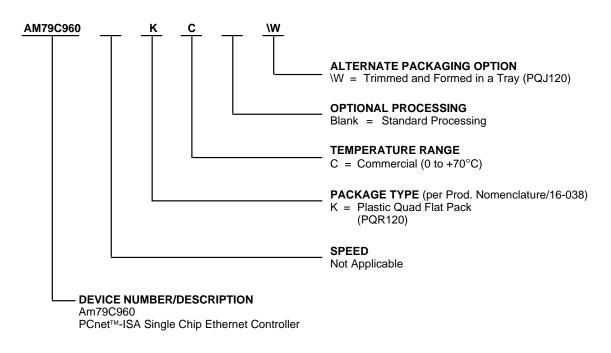

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |          |  |  |  |

|--------------------|----------|--|--|--|

| AM79C960           | KC, KC\W |  |  |  |

# Valid Combinations

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

| TABLE OF CONTENTS                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| DISTINCTIVE CHARACTERISTICS                                                                                                                         |

| GENERAL DESCRIPTION 1-343                                                                                                                           |

| RELATED PRODUCTS 1-344                                                                                                                              |

| ORDERING INFORMATION                                                                                                                                |

| BLOCK DIAGRAM: BUS MASTER MODE                                                                                                                      |

| CONNECTION DIAGRAM: BUS MASTER 1-353                                                                                                                |

| PIN DESIGNATIONS: BUS MASTER<br>LISTED BY PIN NUMBER                                                                                                |

| PIN DESCRIPTION: BUS MASTER MODE1-358ISA INTERFACE1-358BOARD INTERFACE1-359                                                                         |

| BLOCK DIAGRAM: SHARED MEMORY 1-361                                                                                                                  |

| CONNECTION DIAGRAM: SHARED MEMORY 1-362                                                                                                             |

| PIN DESIGNATIONS: SHARED MEMORYLISTED BY PIN NUMBER1-363LISTED BY PIN NAME1-364LISTED BY GROUP1-365                                                 |

| PIN DESCRIPTION: SHARED MEMORY MODE1-367ISA INTERFACE1-367BOARD INTERFACE1-368                                                                      |

| PIN DESCRIPTION: NETWORK INTERFACES (mode independent)1-370AUI INTERFACE1-370TWISTED PAIR INTERFACE1-370IEEE 1149.1 TEST ACCESS PORT INTERFACE1-370 |

| PIN DESCRIPTION: POWER SUPPLIES (mode independent) 1-371                                                                                            |

| FUNCTIONAL DESCRIPTION1-372BUS MASTER MODE1-372SHARED MEMORY MODE1-373NETWORK INTERFACE1-373                                                        |

| DETAILED FUNCTIONS                                                     | -374 |

|------------------------------------------------------------------------|------|

| BUS INTERFACE UNIT (BIU)                                               | -374 |

| DMA Transfers                                                          | -374 |

| 1. Initialization Block DMA Transfers 1                                | -374 |

| 2. Descriptor DMA Transfers                                            | -374 |

| 3. Burst-Cycle DMA Transfers                                           | -374 |

| BUFFER MANAGEMENT UNIT (BMU)                                           |      |

| Initialization                                                         |      |

|                                                                        | -    |

| Buffer Management                                                      |      |

| Descriptor Rings                                                       |      |

| Descriptor Ring Access Mechanism                                       |      |

| Polling                                                                |      |

| Transmit Descriptor Table Entry (TDTE)                                 |      |

| Receive Descriptor Table Entry (RDTE)                                  | -378 |

| MEDIA ACCESS CONTROL                                                   | -379 |

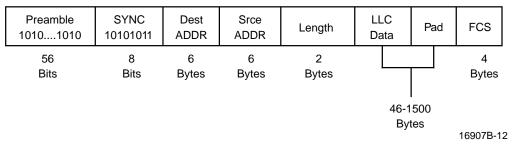

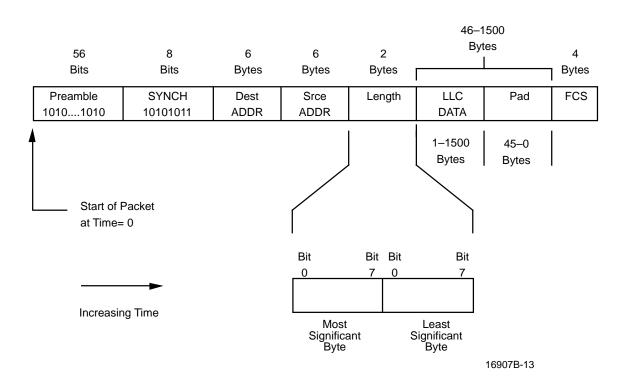

| Transmit and Receive Message Data Encapsulation                        | -379 |

| Media Access Management                                                | -380 |

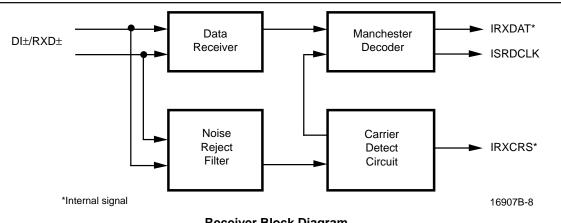

| MANCHESTER ENCODER/DECODER (MENDEC)                                    | -382 |

| External Crystal Characteristics                                       |      |

| External Clock Drive Characteristics                                   |      |

| MENDEC Transmit Path                                                   |      |

| Transmitter Timing and Operation                                       |      |

| Receive Path                                                           |      |

| Input Signal Conditioning                                              |      |

| Clock Acquisition                                                      |      |

| PLL Tracking                                                           |      |

| Carrier Tracking and End of Message                                    |      |

| Data Decoding                                                          |      |

| Jitter Tolerance Definition                                            | -384 |

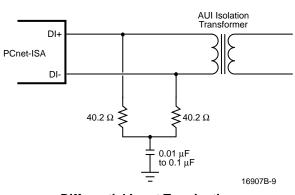

| Attachment Unit Interface (AUI)                                        |      |

| Differential Input Terminations                                        | -384 |

| Collision Detection                                                    | -384 |

| TWISTED PAIR TRANSCEIVER (T-MAU)                                       | -385 |

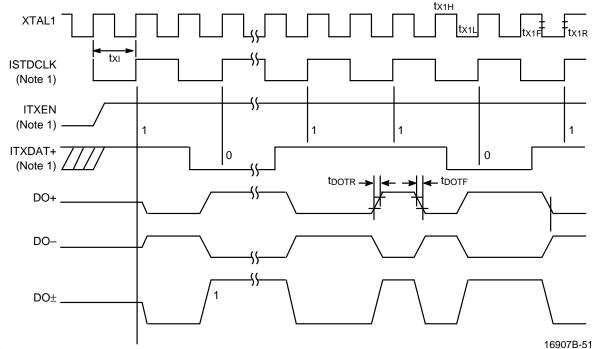

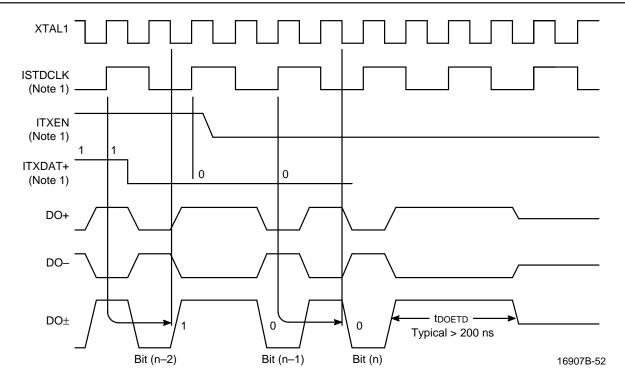

| Twisted Pair Transmit Function                                         |      |

| Twisted Pair Receive Function                                          |      |

| Link Test Function                                                     |      |

| Polarity Detection and Reversal                                        |      |

| Twisted Pair Interface Status                                          |      |

| Collision Detect Function                                              |      |

| Signal Quality Error (SQE) Test (Heartbeat) Function                   |      |

| Jabber Function                                                        |      |

| Power Down                                                             |      |

| EADI <sup>™</sup> (External Address Detection Interface <sup>™</sup> ) |      |

| GENERAL PURPOSE SERIAL INTERFACE (GPSI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

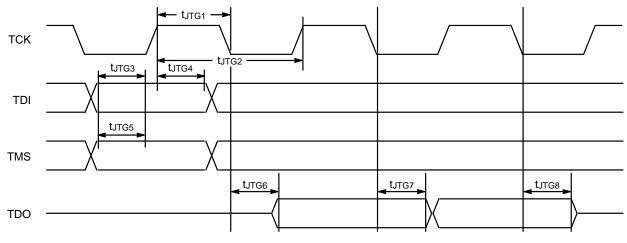

| IEEE 1149.1 TEST ACCESS PORT INTERFACE       1-389         Boundary Scan Circuit       1-389         TAP FSM       1-389         Supported Instructions       1-389         Instruction Register and Decoding Logic       1-389         Boundary Scan Register (BSR)       1-389         Other Data Register       1-389                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| POWER SAVINGS MODES 1-390                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ACCESS OPERATIONS (SOFTWARE)<br>I/O Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

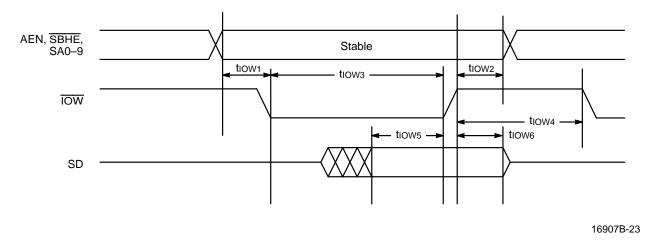

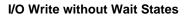

| BUS CYCLES (HARDWARE) 1-390                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BUS CYCLES (HARDWARE)1-390Bus Master Mode1-391Refresh Cycles1-392Address PROM Cycles1-392Ethernet Controller Register Cycles1-392RESET Cycles1-392ISA Configuration Register Cycles1-392Boot PROM Cycles1-392Current Master Operation1-393Master Mode Memory Read Cycle1-393Master Mode Memory Write Cycle1-393Shared Memory Mode1-394Address PROM Cycles1-394Ethernet Controller Register Cycles1-394RESET Cycles1-394Current Master Operation1-394Master Mode Memory Write Cycle1-394Shared Memory Mode1-394Address PROM Cycles1-394Ethernet Controller Register Cycles1-394RESET Cy |

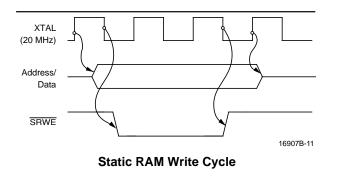

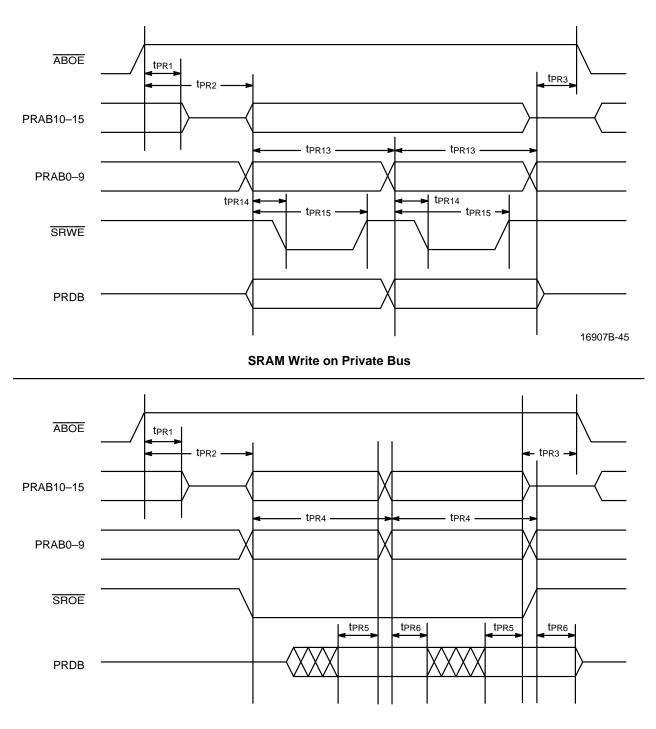

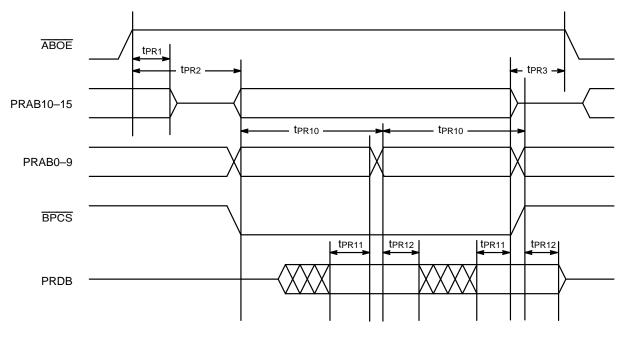

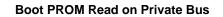

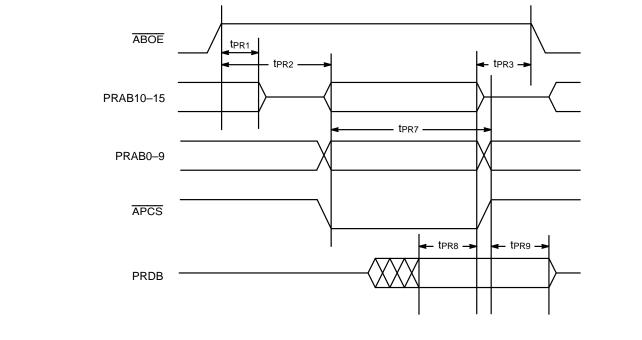

| Boot PROM Cycles         1-394           Static RAM Cycles         1-395                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TRANSMIT OPERATION       1-396         Transmit Function Programming       1-396         Automatic Pad Generation       1-396         Transmit FCS Generation       1-397         Transmit Exception Conditions       1-397         Loss of Carrier       1-397                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RECEIVE OPERATION       1-398         Receive Function Programming       1-398         Automatic Pad Stripping       1-398         Receive FCS Checking       1-399         Receive Exception Conditions       1-399                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LOOPBACK OPERATION                                | 1-399 |

|---------------------------------------------------|-------|

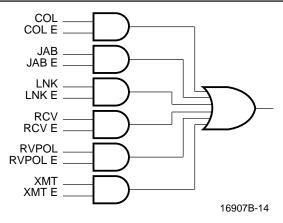

| LEDs                                              | 1-399 |

| PCnet-ISA CONTROLLER REGISTERS                    | 1-401 |

| REGISTER ACCESS                                   |       |

| CONTROL AND STATUS REGISTERS                      |       |

| CSR0: PCnet-ISA Controller Status Register        |       |

| CSR1: IADR[15:0]                                  |       |

| CSR2: IADR[23:16]                                 |       |

| CSR3: Interrupt Masks and Deferral Control        |       |

| CSR4: Test and Features Control                   |       |

| CSR6: RCV/XMT Descriptor Table Length             |       |

| CSR8: Logical Address Filter, LADRF[15:0]         |       |

| CSR9: Logical Address Filter, LADRF[31:16]        |       |

| CSR10: Logical Address Filter, LADRF[47:32]       |       |

| CSR11: Logical Address Filter, LADRF[63:48]       |       |

| CSR12: Physical Address Register, PADR[15:0]      |       |

| CSR13: Physical Address Register, PADR[31:16]     |       |

| CSR14: Physical Address Register, PADR[47:32]     |       |

| CSR15: Mode Register                              |       |

| CSR16: Initialization Block Address               |       |

| CSR17: Initialization Block Address               |       |

| CSR18–19: Current Receive Buffer Address          |       |

| CSR10–19. Current Transmit Buffer Address         |       |

| CSR22–23: Next Receive Buffer Address             |       |

|                                                   |       |

| CSR24–25: Base Address of Receive Ring            |       |

| CSR26–27: Next Receive Descriptor Address         |       |

| CSR28–29: Current Receive Descriptor Address      |       |

| CSR30–31: Base Address of Transmit Ring           |       |

| CSR32–33: Next Transmit Descriptor Address        |       |

| CSR34–35: Current Transmit Descriptor Address     | 1-409 |

| CSR36–37: Next Next Receive Descriptor Address    |       |

| CSR38–39: Next Next Transmit Descriptor Address   |       |

| CSR40–41: Current Receive Status and Byte Count   |       |

| CSR42–43: Current Transmit Status and Byte Count  |       |

| CSR44–45: Next Receive Status and Byte Count      |       |

| CSR46: Poll Time Counter                          |       |

| CSR47: Polling Interval                           |       |

| CSR48–49: Temporary Storage                       |       |

| CSR50–51: Temporary Storage                       |       |

| CSR52–53: Temporary Storage                       |       |

| CSR54–55: Temporary Storage                       |       |

| CSR56–57: Temporary Storage                       |       |

| CSR58–59: Temporary Storage                       |       |

| CSR60–61: Previous Transmit Descriptor Address    |       |

| CSR62–63: Previous Transmit Status and Byte Count |       |

| CSR64–65: Next Transmit Buffer Address            | 1-411 |

| CSR66–67: Next Transmit Status and Byte Count    |

|--------------------------------------------------|

| CSR68–69: Transmit Status Temporary Storage      |

| CSR70–71: Temporary Storage 1-412                |

| CSR72: Receive Ring Counter 1-412                |

| CSR74: Transmit Ring Counter 1-412               |

| CSR76: Receive Ring Length 1-412                 |

| CSR78: Transmit Ring Length 1-412                |

| CSR80: Burst and FIFO Threshold Control 1-412    |

| CSR82: Bus Activity Timer 1-413                  |

| CSR84–85: DMA Address 1-414                      |

| CSR86: Buffer Byte Counter 1-414                 |

| CSR88–89: Chip ID                                |

| CSR92: Ring Length Conversion 1-414              |

| CSR94: Transmit Time Domain Reflectometry Count  |

| CSR96–97: Bus Interface Scratch Register 0 1-415 |

| CSR98–99: Bus Interface Scratch Register 1 1-415 |

| CSR104–105: SWAP 1-415                           |

| CSR108–109: Buffer Management Scratch            |

| CSR112: Missed Frame Count 1-415                 |

| CSR114: Receive Collision Count 1-415            |

| CSR124: Buffer Management Unit Test              |

| ISA BUS CONFIGURATION REGISTERS                  |

|                                                  |

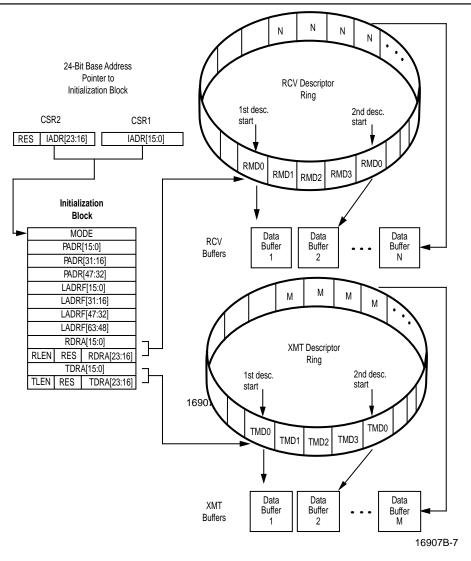

| INITIALIZATION BLOCK 1-419                       |

| RLEN and TLEN 1-419                              |

| RDRA and TDRA                                    |

| LADRF                                            |

| PADR                                             |

| MODE                                             |

| RECEIVE DESCRIPTORS 1-420                        |

| RMD0                                             |

| RMD1                                             |

| RMD2                                             |

| RMD3                                             |

|                                                  |

| TRANSMIT DESCRIPTORS 1-421                       |

| TMD0                                             |

| TMD1                                             |

| TMD2                                             |

| TMD3                                             |

| REGISTER SUMMARY 1-424                           |

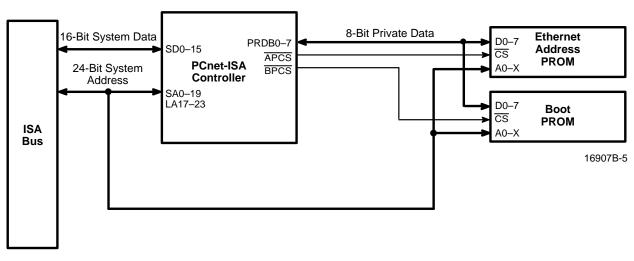

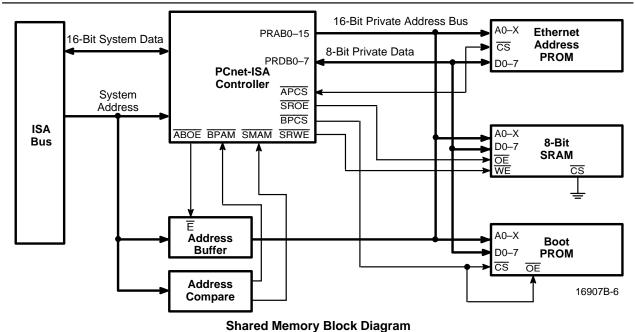

| SYSTEM APPLICATION       1-427         ISA BUS INTERFACE       1-427         Compatibility Consideration       1-427         Bus Masters       1-427         Shared Memory       1-427                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDRESS PROM INTERFACE 1-428                                                                                                                                                                                                                                                       |

| BOOT PROM INTERFACE                                                                                                                                                                                                                                                                |

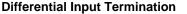

| STATIC RAM INTERFACE                                                                                                                                                                                                                                                               |

| AUI INTERFACE                                                                                                                                                                                                                                                                      |

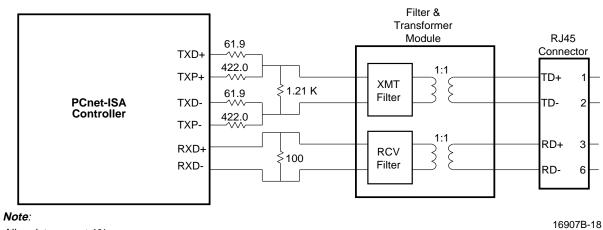

| 10BASE-T INTERFACE                                                                                                                                                                                                                                                                 |

| ABSOLUTE MAXIMUM RATINGS 1-430                                                                                                                                                                                                                                                     |

| OPERATING RANGES                                                                                                                                                                                                                                                                   |

| DC CHARACTERISTICS                                                                                                                                                                                                                                                                 |

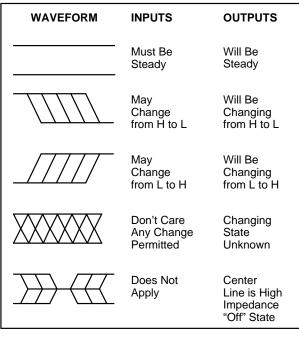

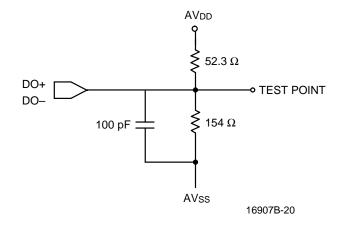

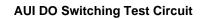

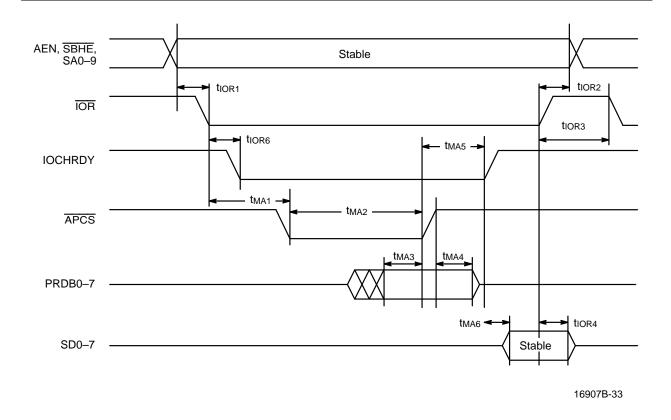

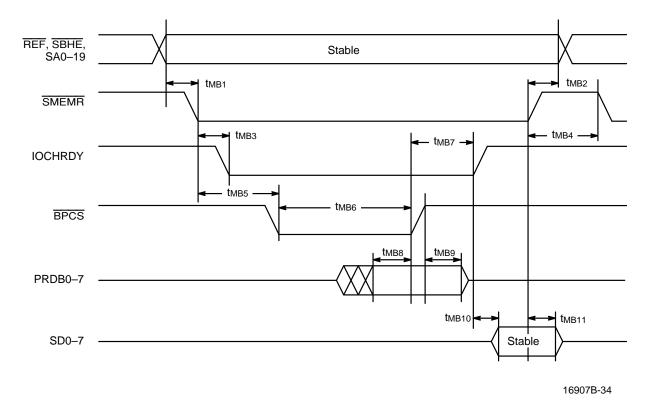

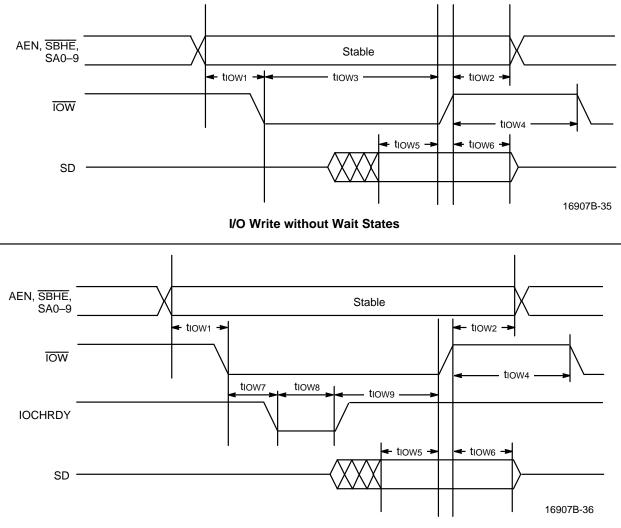

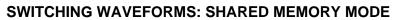

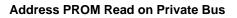

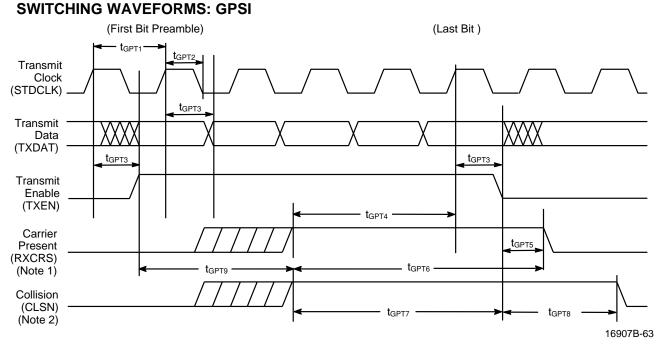

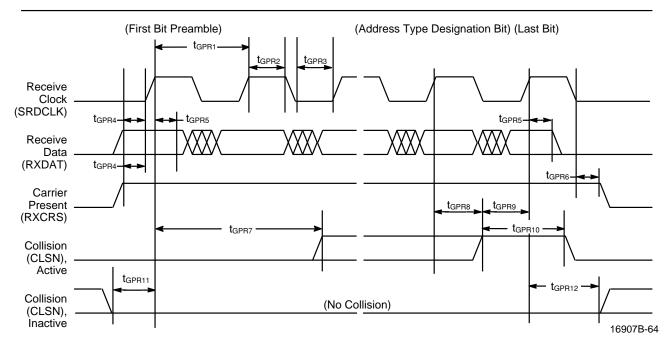

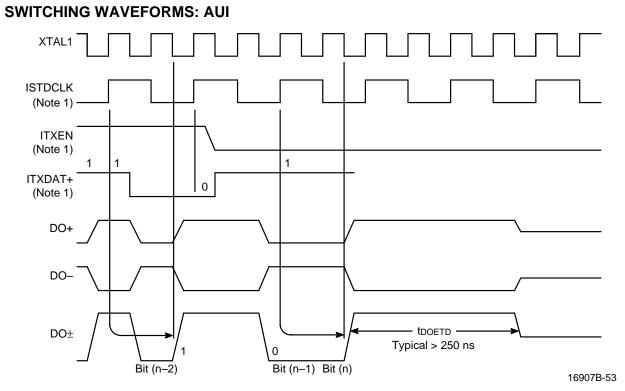

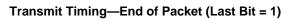

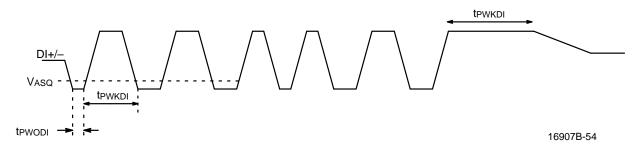

| SWITCHING CHARACTERISTICS       1-433         BUS MASTER MODE       1-433         SHARED MEMORY MODE       1-436         EADI       1-439         JTAG (IEEE 1149.1) INTERFACE       1-439         GPSI       1-440         AUI       1-441         10BASE-T INTERFACE       1-442 |

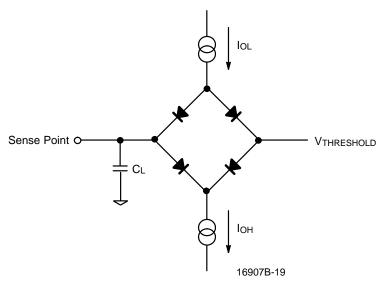

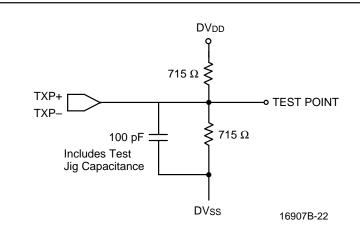

| SWITCHING TEST CIRCUITS                                                                                                                                                                                                                                                            |

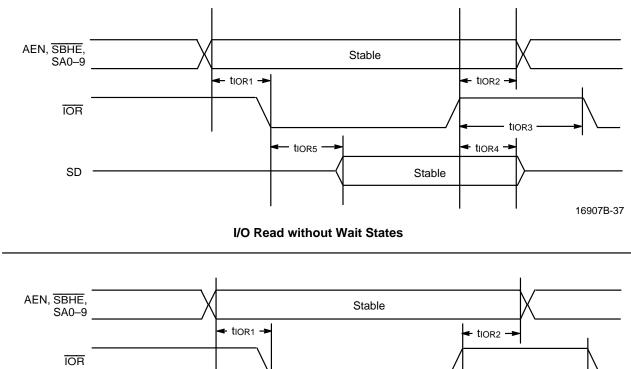

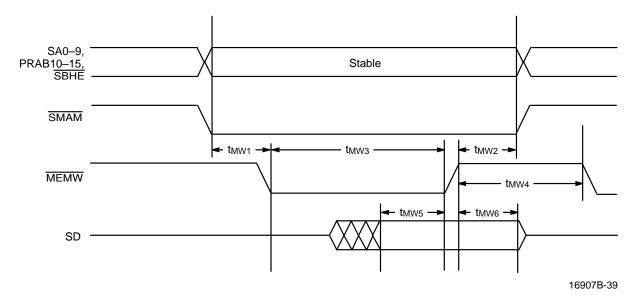

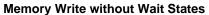

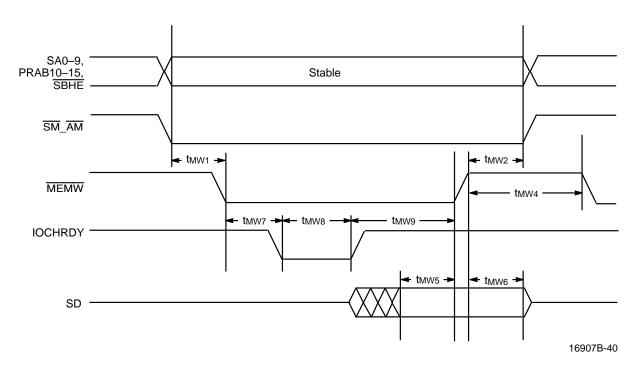

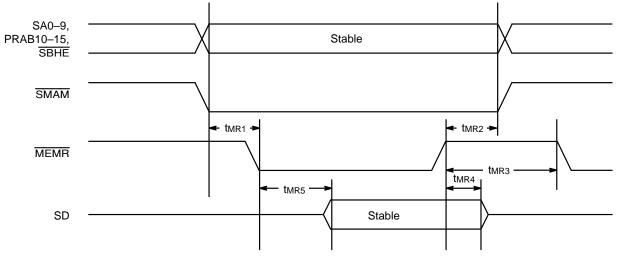

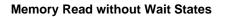

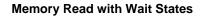

| SWITCHING WAVEFORMS       1-445         BUS MASTER MODE       1-445         SHARED MEMORY MODE       1-451         GPSI       1-458         EADI       1-459         JTAG (IEEE 1149.1) INTERFACE       1-450         AUI       1-460         10BASE-T INTERFACE       1-463       |

| APPENDIX A: PCnet-ISA COMPATIBLE MEDIA INTERFACE MODULES<br>10BASE-T FILTERS and TRANSFORMERS                                                                                                                                                                                      |

| MANUFACTURER CONTACT INFORMATION 1-466                                                                                                                                                                                                                                             |

| APPENDIX B: RECOMMENDATION FOR REDUCING NOISE INJECTION<br>DECOUPLING LOW-PASS RC FILTER DESIGN                                                                                                                                                                                    |

| APPENDIX C: ALTERNATIVE METHOD FOR INITIALIZATION                                                                                                                                                                                                                                  |

| DATA SHEET REVISION SUMMARY                                                                                                                                                                                                                                                        |

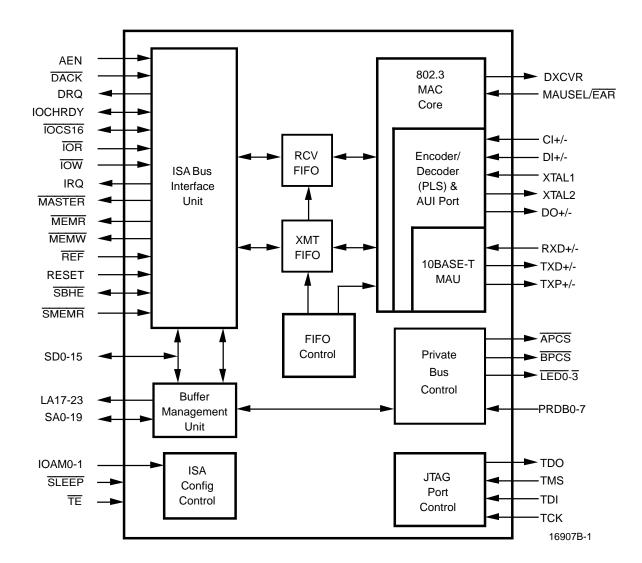

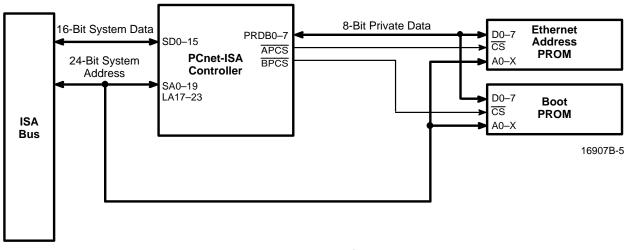

**BLOCK DIAGRAM: BUS MASTER MODE**

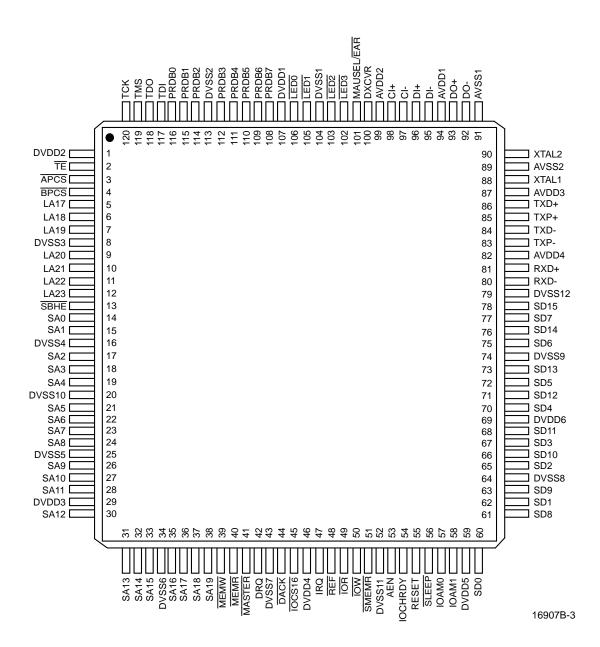

# CONNECTION DIAGRAM: BUS MASTER

# PIN DESIGNATIONS: BUS MASTER Listed by Pin Number

| Pin # | Name   | Pin # | Name    | Pin # | Name   | Pin # | Name       |

|-------|--------|-------|---------|-------|--------|-------|------------|

| 1     | DVDD2  | 31    | SA13    | 61    | SD8    | 91    | AVSS1      |

| 2     | TE     | 32    | SA14    | 62    | SD1    | 92    | DO-        |

| 3     | APCS   | 33    | SA15    | 63    | SD9    | 93    | DO+        |

| 4     | BPCS   | 34    | DVSS6   | 64    | DVSS8  | 94    | AVDD1      |

| 5     | LA17   | 35    | SA16    | 65    | SD2    | 95    | DI–        |

| 6     | LA18   | 36    | SA17    | 66    | SD10   | 96    | DI+        |

| 7     | LA19   | 37    | SA18    | 67    | SD3    | 97    | CI–        |

| 8     | DVSS3  | 38    | SA19    | 68    | SD11   | 98    | CI+        |

| 9     | LA20   | 39    | MEMW    | 69    | DVDD6  | 99    | AVDD2      |

| 10    | LA21   | 40    | MEMR    | 70    | SD4    | 100   | DXCVR      |

| 11    | LA22   | 41    | MASTER  | 71    | SD12   | 101   | MAUSEL/EAR |

| 12    | LA23   | 42    | DRQ     | 72    | SD5    | 102   | LED3       |

| 13    | SBHE   | 43    | DVSS7   | 73    | SD13   | 103   | LED2       |

| 14    | SA0    | 44    | DACK    | 74    | DVSS9  | 104   | DVSS1      |

| 15    | SA1    | 45    | IOCS16  | 75    | SD6    | 105   | LED1       |

| 16    | DVSS4  | 46    | DVDD4   | 76    | SD14   | 106   | LED0       |

| 17    | SA2    | 47    | IRQ     | 77    | SD7    | 107   | DVDD1      |

| 18    | SA3    | 48    | REF     | 78    | SD15   | 108   | PRDB7      |

| 19    | SA4    | 49    | ĪOR     | 79    | DVSS12 | 109   | PRDB6      |

| 20    | DVSS10 | 50    | ĪŌŴ     | 80    | RXD-   | 110   | PRDB5      |

| 21    | SA5    | 51    | SMEMR   | 81    | RXD+   | 111   | PRDB4      |

| 22    | SA6    | 52    | DVSS11  | 82    | AVDD4  | 112   | PRDB3      |

| 23    | SA7    | 53    | AEN     | 83    | TXP-   | 113   | DVSS2      |

| 24    | SA8    | 54    | IOCHRDY | 84    | TXD-   | 114   | PRDB2      |

| 25    | DVSS5  | 55    | RESET   | 85    | TXP+   | 115   | PRDB1      |

| 26    | SA9    | 56    | SLEEP   | 86    | TXD+   | 116   | PRDB0      |

| 27    | SA10   | 57    | IOAM0   | 87    | AVDD3  | 117   | TDI        |

| 28    | SA11   | 58    | IOAM1   | 88    | XTAL1  | 118   | TDO        |

| 29    | DVDD3  | 59    | DVDD5   | 89    | AVSS2  | 119   | TMS        |

| 30    | SA12   | 60    | SD0     | 90    | XTAL2  | 120   | ТСК        |

# PIN DESIGNATIONS: BUS MASTER Listed by Pin Name

| Name  | Pin # | Name       | Pin # | Name  | Pin # | Name  | Pin # |

|-------|-------|------------|-------|-------|-------|-------|-------|

| AEN   | 53    | DVSS8      | 64    | PRDB2 | 114   | SBHE  | 13    |

| APCS  | 3     | DVSS9      | 74    | PRDB3 | 112   | SD0   | 60    |

| AVDD1 | 94    | DVSS10     | 20    | PRDB4 | 111   | SD1   | 62    |

| AVDD2 | 99    | DVSS11     | 52    | PRDB5 | 110   | SD2   | 65    |

| AVDD3 | 87    | DVSS12     | 79    | PRDB6 | 109   | SD3   | 67    |

| AVDD4 | 82    | DXCVR      | 100   | PRDB7 | 108   | SD4   | 70    |

| AVSS1 | 91    | IOAM0      | 57    | REF   | 48    | SD5   | 72    |

| AVSS2 | 89    | IOAM1      | 58    | RESET | 55    | SD6   | 75    |

| BPCS  | 4     | IOCHRDY    | 54    | RXD-  | 80    | SD7   | 77    |

| CI–   | 97    | IOCS16     | 45    | RXD+  | 81    | SD8   | 61    |

| Cl+   | 98    | IOR        | 49    | SA0   | 14    | SD9   | 63    |

| DACK  | 44    | IOW        | 50    | SA1   | 15    | SD10  | 66    |

| DI–   | 95    | IRQ        | 47    | SA2   | 17    | SD11  | 68    |

| DI+   | 96    | LA17       | 5     | SA3   | 18    | SD12  | 71    |

| DO-   | 92    | LA18       | 6     | SA4   | 19    | SD13  | 73    |

| DO+   | 93    | LA19       | 7     | SA5   | 21    | SD14  | 76    |

| DRQ   | 42    | LA20       | 9     | SA6   | 22    | SD15  | 78    |

| DVDD1 | 107   | LA21       | 10    | SA7   | 23    | SLEEP | 56    |

| DVDD2 | 1     | LA22       | 11    | SA8   | 24    | SMEMR | 51    |

| DVDD3 | 29    | LA23       | 12    | SA9   | 26    | тск   | 120   |

| DVDD4 | 46    | LED0       | 106   | SA10  | 27    | TDI   | 117   |

| DVDD5 | 59    | LED1       | 105   | SA11  | 28    | TDO   | 118   |

| DVDD6 | 69    | LED2       | 103   | SA12  | 30    | TE    | 2     |

| DVSS1 | 104   | LED3       | 102   | SA13  | 31    | TMS   | 119   |

| DVSS2 | 113   | MASTER     | 41    | SA14  | 32    | TXD-  | 84    |

| DVSS3 | 8     | MAUSEL/EAR | 101   | SA15  | 33    | TXD+  | 86    |

| DVSS4 | 16    | MEMR       | 40    | SA16  | 35    | TXP-  | 83    |

| DVSS5 | 25    | MEMW       | 39    | SA17  | 36    | TXP+  | 85    |

| DVSS6 | 34    | PRDB0      | 116   | SA18  | 37    | XTAL1 | 88    |

| DVSS7 | 43    | PRDB1      | 115   | SA19  | 38    | XTAL2 | 90    |

# PIN DESIGNATIONS: BUS MASTER Listed by Group

\_\_\_\_

| in Name Pin Function |                                    | I/O | Driver |

|----------------------|------------------------------------|-----|--------|

| ISA Bus Interface    | ·                                  | ·   |        |

| AEN                  | Address Enable                     | I   |        |

| DACK                 | DMA Acknowledge                    | I   |        |

| DRQ                  | DMA Request                        | 0   | TS3    |

| IOCHRDY              | I/O Channel Ready                  | I/O | OD3    |

| IOCS16               | I/O Chip Select 16                 | I/O | OD3    |

| ĪOR                  | I/O Read Select                    | I   |        |

| ĪOW                  | I/O Write Select                   | I   |        |

| IRQ                  | Interrupt Request                  | 0   | OD3    |

| LA17-23              | Unlatched Address Bus              | 0   | TS3    |

| MASTER               | Master Transfer in Progress        | 0   | OC3    |

| MEMR                 | Memory Read Select                 | 0   | TS3    |

| MEMW                 | Memory Write Select                | 0   | TS3    |

| REF                  | Memory Refresh Active              | I   |        |

| RESET                | System Reset                       | I   |        |

| SA0-19               | System Address Bus                 | I/O | TS3    |

| SBHE                 | System Byte High Enable            | I/O | TS3    |

| SD0-15               | System Data Bus                    | I/O | TS3    |

| SMEMR                | System Memory Read Select          | I   |        |

| Board Interfaces     | •                                  |     |        |

| APCS                 | Address PROM Chip Select           | 0   | TS1    |

| BPCS                 | Boot PROM Chip Select              | 0   | TS1    |

| DXCVR                | Disable Transceiver                | 0   | TS1    |

| IOAM0-1              | Input/Output Address Map           | I   |        |

| LED0                 | LED0/LNKST                         | 0   | TS2    |

| LED1                 | LED1/SFBD/RCVACT                   | 0   | TS2    |

| LED2                 | LED2/SRD/RXPOL                     | 0   | TS2    |

| LED3                 | LED3/SRDCLK/XMTACT                 | 0   | TS2    |

| MAUSEL/EAR           | MAU SELect/External Address Reject | 1   |        |

| PRDB0-7              | PROM Data Bus                      | 1   |        |

| SLEEP                | Sleep Mode                         | 1   |        |

| TE                   | Test Enable                        | 1   |        |

| XTAL1                | Crystal Input                      | I   |        |

| XTAL2                | Crystal Output                     | 0   |        |

# PIN DESIGNATIONS: BUS MASTER (continued) Listed by Group

| Pin Name                         | Pin Function                   | I/O | Driver |

|----------------------------------|--------------------------------|-----|--------|

| Attachment Unit Interface (AUI)  |                                | ·   |        |

| CI±                              | Collision Inputs               | I   |        |

| DI±                              | Receive Data                   | I   |        |

| DO±                              | Transmit Data                  | 0   |        |

| Twisted Pair Transceiver Interfa | ace (10BASE-T)                 |     |        |

| RXD±                             | 10BASE-T Receive Data          | I   |        |

| TXD±                             | 10BASE-T Transmit Data         | 0   |        |

| TXP±                             | 10BASE-T Predistortion Control | 0   |        |

| IEEE 1149.1 Test Access Port In  | nterface (JTAG)                |     |        |

| тск                              | Test Clock                     | I   |        |

| TDI                              | Test Data Input                | I   |        |

| TDO                              | Test Data Output               | 0   | TS2    |

| TMS                              | Test Mode Select               | I   |        |

| Power Supplies                   |                                |     |        |

| AVDD                             | Analog Power                   |     |        |

| AVSS                             | Analog Ground                  |     |        |

| DVDD                             | Digital Power                  |     |        |

| DVSS                             | Digital Ground                 |     |        |

# Table: Output Driver Types

| Name | Туре       | lol (mA) | loh (mA) | pF  |

|------|------------|----------|----------|-----|

| TS1  | Tri-State  | 4        | -1       | 50  |

| TS2  | Tri-State  | 12       | -4       | 50  |

| TS3  | Tri-State  | 24       | -3       | 120 |

| OD3  | Open Drain | 24       | -3       | 120 |

# PIN DESCRIPTION: BUS MASTER MODE

These pins are part of the bus master mode. In order to understand the pin descriptions, definition of some terms from a draft of IEEE P996 are included.

# **IEEE P996 Terminology**

Alternate Master: Any device that can take control of the bus through assertion of the MASTER signal. It has the ability to generate addresses and bus control signals in order to perform bus operations. All Alternate Masters must be 16 bit devices and drive SBHE.

**Bus Ownership**: The Current Master possesses bus ownership and can assert any bus control, address and data lines.

**Current Master**: The Permanent Master, Temporary Master or Alternate Master which currently has ownership of the bus.

**Permanent Master**: Each P996 bus will have a device known as the Permanent Master that provides certain signals and bus control functions as described in Section 3.5 (of the IEEE P996 spec), "Permanent Master". The Permanent Master function can reside on a Bus Adapter or on the backplane itself.

**Temporary Master**: A device that is capable of generating a DMA request to obtain control of the bus and directly asserting only the memory and I/O strobes during bus transfer. Addresses are generated by the DMA device on the Permanent Master.

### **ISA Interface**

#### AEN Address Enable

# Input

This signal must be driven LOW when the bus performs an I/O access to the device.

# DACK

DMA Acknowledge

### Input

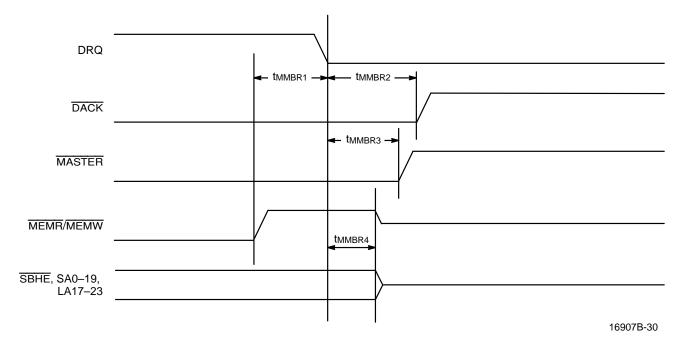

Asserted LOW when the Permanent Master acknowledges a DMA request. When DACK is asserted the PCnet-ISA controller becomes the Current Master by asserting the MASTER signal.

# DRQ

# DMA Request

Output

When the PCnet-ISA controller needs to perform a DMA transfer, it asserts DRQ. The Permanent Master acknowledges DRQ with assertion of DACK. When the PCnet-ISA controller does not need the bus it deasserts DRQ.

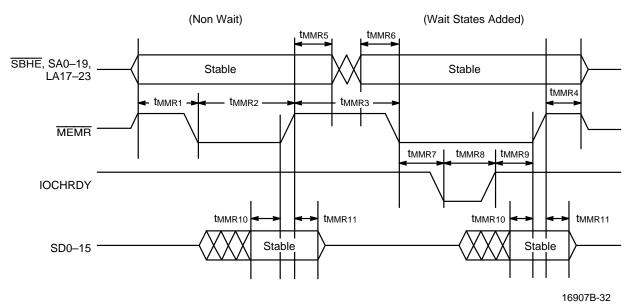

# **IOCHRDY**

I/O Channel Ready

Input/Output

When the PCnet-ISA controller is being accessed, IOCHRDY HIGH indicates that valid data exists on the

data bus for reads and that data has been latched for writes. When the PCnet-ISA controller is the Current Master on the ISA bus, it extends the bus cycle as long as IOCHRDY is LOW.

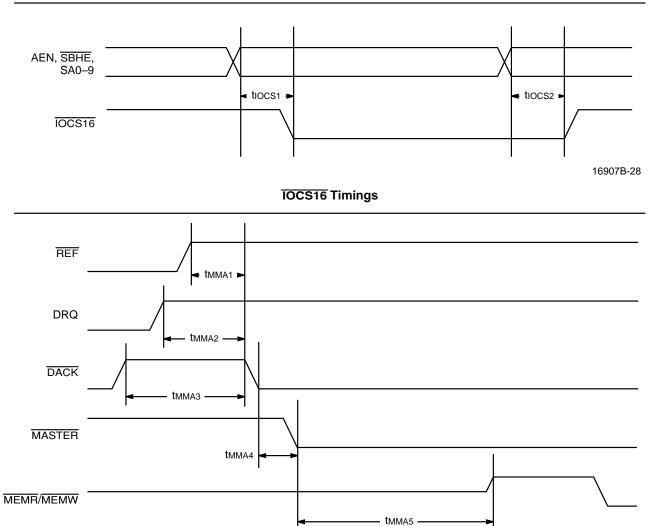

### IOCS16 I/O Chip Select 16

#### Input/Output

When an I/O read or write operation is performed, the PCnet-ISA controller will drive the IOCS16 pin LOW to indicate that the chip supports a 16-bit operation at this address. (If the motherboard does not receive this signal, then the motherboard will convert a 16-bit access to two 8-bit accesses.) The IOCS16 pin is also an input and must go HIGH at least once after reset for the PCnet-ISA controller to perform 16-bit I/O operations. If this pin is grounded then the PCnet-ISA controller only performs 8-bit I/O operations.

The PCnet-ISA controller follows the IEEE P996 specification that recommends this function be implemented as a pure decode of SA0-9 and AEN, with no dependency on SMEMR, MEMR, MEMW, IOR, or IOW; however, some PC/AT clone systems are not compatible with this approach. For this reason, the PCnet-ISA controller is recommended to be configured to run 8-bit I/O on all machines. Since data is moved by memory cycles there is virtually no performance loss incurred by running 8-bit I/O and compatibility problems are virtually eliminated. The PCnet-ISA controller can be configured to run 8-bit-only I/O by disconnecting the IOCS16 pin from the ISA bus and tying the IOCS16 pin to ground instead.

# IOR

### I/O Read

### Input

Input

IOR is driven LOW by the host to indicate that an Input/ Output Read operation is taking place. IOR is only valid if the AEN signal is LOW and the external address matches the PCnet-ISA controller's predefined I/O address location. If valid, IOR indicates that a slave read operation is to be performed.

# IOW

# I/O Write

$\overline{IOW}$  is driven LOW by the host to indicate that an Input/ Output Write operation is taking place.  $\overline{IOW}$  is only valid if AEN signal is LOW and the external address matches the PCnet-ISA controller's predefined I/O address location. If valid,  $\overline{IOW}$  indicates that a slave write operation is to be performed.

# IRQ

#### Interrupt Request

An attention signal which indicates that one or more of the following status flags is set: BABL, MISS, MERR, RINT, IDON, RCVCCO, JAB, MFCO, or TXSTRT. All status flags have a mask bit which allows for suppression of INTR assertion. These flags have the following meaning:

Output

| BABL   | Babble                           |  |

|--------|----------------------------------|--|

| RCVCCO | Receive Collision Count Overflow |  |

| JAB    | Jabber                           |  |

| MISS   | Missed Frame                     |  |

| MERR   | Memory Error                     |  |

| MFCO   | Missed Frame Count Overflow      |  |

| RINT   | Receive Interrupt                |  |

| IDON   | Initialization Done              |  |

| TXSTRT | Transmit Start                   |  |

# LA17-23

# Unlatched Address Bus Output

The unlatched address bus is driven by the PCnet-ISA controller during bus master cycle.

The functions of these unlatched address pins will change when GPSI mode is invoked. The table below shows the pin configuration in GPSI mode. Please refer to the section on General Purpose Serial Interface for detailed information on accessing this mode.

| Pin<br>Number | Pin Function in<br>Bus Master Mode | Pin Function in<br>GPSI Mode |

|---------------|------------------------------------|------------------------------|

| 5             | LA17                               | RXDAT                        |

| 6             | LA18                               | SRDCLK                       |

| 7             | LA19                               | RXCRS                        |

| 9             | LA20                               | CLSN                         |

| 10            | LA21                               | STDCLK                       |

| 11            | LA22                               | TXEN                         |

| 12            | LA23                               | TXDAT                        |

#### MASTER Master Mode

Output

This signal indicates that the PCnet-ISA controller has become the Current Master of the ISA bus. After the PCnet-ISA controller has received a DMA Acknowledge (DACK) in response to a DMA Request (DRQ), the Ethernet controller asserts the MASTER signal to indicate to the Permanent Master that the PCnet-ISA controller is becoming the Current Master.

# MEMR

# Output

MEMR goes LOW to perform a memory read operation.

# MEMW

#### Memory Write

Memory Read

Output

Input

MEMW goes LOW to perform a memory write operation.

# REF

# Memory Refresh

When REF is asserted, a memory refresh is active. The PCnet-ISA controller uses this signal to mask inadvertent DMA Acknowledge assertion during memory

refresh periods. If DACK is asserted when REF is active, DACK assertion is ignored. REF is monitored to eliminate a bus arbitration problem observed on some ISA platforms.

#### RESET Reset

### Input

When RESET is asserted HIGH the PCnet-ISA controller performs an internal system reset. RESET must be held for a minimum of 10 XTAL1 periods before being deasserted. While in a reset state, the PCnet-ISA controller will tristate or deassert all outputs to predefined reset levels. The PCnet-ISA controller resets itself upon power-up.

# SA0-19

### System Address Bus

Input/Output

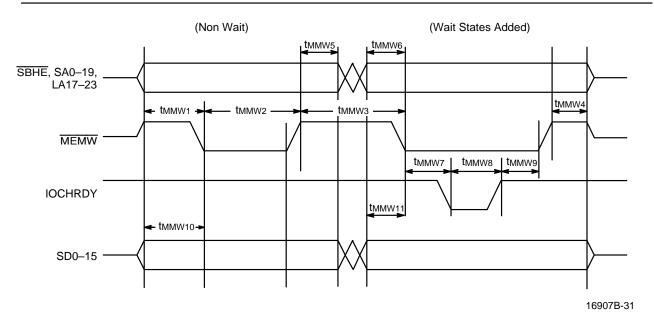

This bus contains address information, which is stable during a bus operation, regardless of the source. SA17-19 contain the same values as the unlatched address LA17-19. When the PCnet-ISA controller is the Current Master, SA0-19 will be driven actively. When the PCnet-ISA controller is not the Current Master, the SA0-19 lines are continuously monitored to determine if an address match exists for I/O slave transfers or Boot PROM accesses.

# SBHE

# System Byte High Enable Input/Output

This signal indicates the high byte of the system data bus is to be used. SBHE is driven by the PCnet-ISA controller when performing bus mastering operations.

#### SD0-15 System Data Bus

# Input/Output

These pins are used to transfer data to and from the PCnet-ISA controller to system resources via the ISA data bus. SD0-15 is driven by the PCnet-ISA controller when performing bus master writes and slave read operations. Likewise, the data on SD0-15 is latched by the PCnet-ISA controller when performing bus master reads and slave write operations.

#### SMEMR System Memory Read

Input

This pin is used during Boot PROM access. The Boot PROM can be disabled by not connecting this pin.

# **Board Interface**

# APCS

# Address PROM Chip Select Output

This signal is asserted when the external Address PROM is read. When an I/O read operation is performed on the first 16 bytes in the PCnet-ISA controller's I/O space, APCS is asserted. The outputs of the external Address PROM drive the PROM Data Bus. The PCnet-ISA controller buffers the contents of the PROM data bus and drives them on the lower eight bits of the System Data Bus.

#### BPCS Boot PROM Chip Select

This signal is asserted when the Boot PROM is read. If SA0-19 lines match a predefined address block and SMEMR is active and REF inactive, the BPCS signal will be asserted. The outputs of the external Boot PROM drive the PROM Data Bus. The PCnet-ISA controller buffers the contents of the PROM data bus and drives them on the lower eight bits of the System Data Bus.

# DXCVR

**Disable Transceiver**

#### Output

Output

This pin disables the transceiver. The DXCVR output is configured in the initialization sequence. A HIGH level indicates the Twisted Pair port is active and the AUI port is inactive, or SLEEP mode has been entered. A LOW level indicates the AUI port is active and the Twisted Pair port is inactive.

# IOAM0-1

### Input/Output Address Map Input

These inputs configure I/O address space for the PCnet-ISA controller and memory address space for the optional Remote Boot PROM with user selectable jumpers. The pins are pulled HIGH internally. The SA1-9 inputs are used for I/O address comparisons and the SA14-19 inputs are used for Boot PROM matching.

| IOAM1,0 | I/O Base | Memory Base |

|---------|----------|-------------|

| 0 0     | 300 Hex  | C8000 Hex   |

| 0 1     | 320 Hex  | CC000 Hex   |

| 10      | 340 Hex  | D0000 Hex   |

| 1 1     | 360 Hex  | D4000 Hex   |

# LED Drivers

# Output

These pins sink 12 mA each for driving LEDs. Their meaning is software configurable (see section *ISA Bus Configuration Registers*) and they are active LOW.

When EADI mode is selected, the pins named  $\overline{\text{LED1}}$ ,  $\overline{\text{LED2}}$ , and  $\overline{\text{LED3}}$  change in function while  $\overline{\text{LED0}}$  continues to indicate 10BASE-T Link Status. The MAUSEL input becomes the  $\overline{\text{EAR}}$  input.

| LED | EADI Function |

|-----|---------------|

| 1   | SF/BD         |

| 2   | SRD           |

| 3   | SRDCLK        |

#### MAUSEL/EAR MAU Select/ External Address Reject

This pin selects the 10BASE-T MAU when HIGH and the AUI interface when LOW if the XMAUSEL register bit in ISACSR2 (ISA Configuration Register) is set. If the XMAUSEL register bit is cleared, the MAUSEL pin is ignored and the network interface is software selected. This pin has a default value of HIGH if left unconnected.

If EADI mode is selected, this pin becomes the  $\overline{\text{EAR}}$  input. The incoming frame will be checked against the internally active address detection mechanisms and the result of this check will be OR'd with the value on the  $\overline{\text{EAR}}$  pin. The  $\overline{\text{EAR}}$  pin is defind as  $\overline{\text{REJECT}}$ . See the EADI section for details regarding the function and timing of this signal.

# PRDB0-7

# Private Data Bus

### Input

Input

This is the data bus for the Boot PROM and the Address PROM.

#### SLEEP Sleep

### )

### Input

Input

Input

When SLEEP pin is asserted (active LOW), the PCnet-ISA controller performs an internal system reset and proceeds into a power savings mode. All outputs will be placed in their normal reset condition. All PCnet-ISA controller inputs will be ignored except for the SLEEP pin itself. Deassertion of SLEEP results in wake-up. The system must delay the starting of the network controller by 0.5 seconds to allow internal analog circuits to stabilize.

# TE

### Test Enable

This pin is for factory use only. It has a default value of HIGH if left unconnected. It is recommended that this pin always be connected to  $V_{DD}$ .

# XTAL1

# Crystal Connection

The internal clock generator uses a 20 MHz crystal that is attached to pins XTAL1 and XTAL2. Alternatively, an external 20 MHz CMOS-compatible clock signal can be used to drive this pin. Refer to the section on External Crystal Characteristics for more details.

#### XTAL2 Crystal Connection

# Output

The internal clock generator uses a 20 MHz crystal that is attached to pins XTAL1 and XTAL2. If an external clock is used, this pin should be left unconnected.

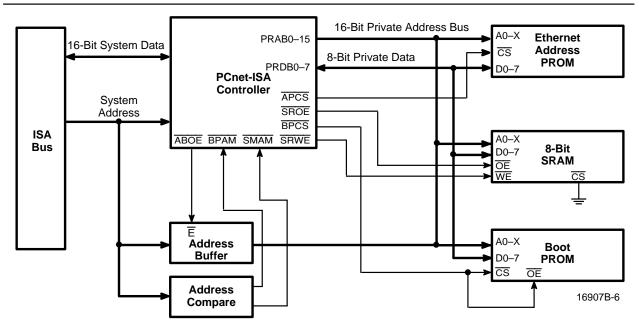

# **BLOCK DIAGRAM: SHARED MEMORY MODE**

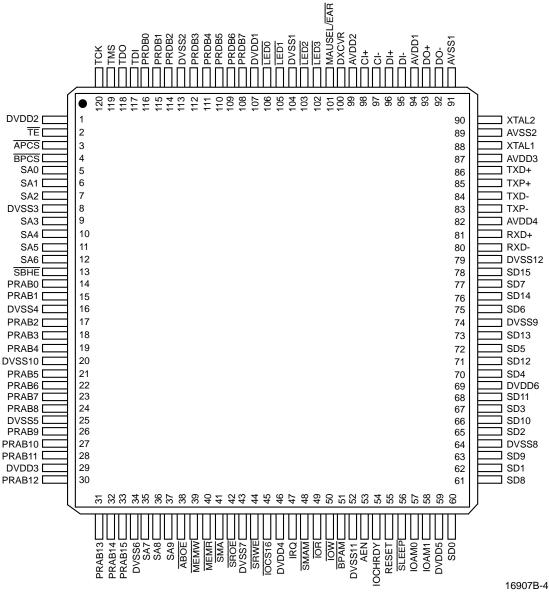

# **CONNECTION DIAGRAM: SHARED MEMORY**

16907B-4

# PIN DESIGNATIONS: SHARED MEMORY Listed by Pin Number

| Pin # | Name   | Pin # | Name    | Pin # | Name   | Pin # | Name       |

|-------|--------|-------|---------|-------|--------|-------|------------|

| 1     | DVDD2  | 31    | PRAB13  | 61    | SD8    | 91    | AVSS1      |

| 2     | TE     | 32    | PRAB14  | 62    | SD1    | 92    | DO-        |

| 3     | APCS   | 33    | PRAB15  | 63    | SD9    | 93    | DO+        |

| 4     | BPCS   | 34    | DVSS6   | 64    | DVSS8  | 94    | AVDD1      |

| 5     | SA0    | 35    | SA7     | 65    | SD2    | 95    | DI–        |

| 6     | SA1    | 36    | SA8     | 66    | SD10   | 96    | DI+        |

| 7     | SA2    | 37    | SA9     | 67    | SD3    | 97    | CI–        |

| 8     | DVSS3  | 38    | ABOE    | 68    | SD11   | 98    | CI+        |

| 9     | SA3    | 39    | MEMW    | 69    | DVDD6  | 99    | AVDD2      |

| 10    | SA4    | 40    | MEMR    | 70    | SD4    | 100   | DXCVR      |

| 11    | SA5    | 41    | SMA     | 71    | SD12   | 101   | MAUSEL/EAR |

| 12    | SA6    | 42    | SROE    | 72    | SD5    | 102   | LED3       |

| 13    | SBHE   | 43    | DVSS7   | 73    | SD13   | 103   | LED2       |

| 14    | PRAB0  | 44    | SRWE    | 74    | DVSS9  | 104   | DVSS1      |

| 15    | PRAB1  | 45    | IOCS16  | 75    | SD6    | 105   | LED1       |

| 16    | DVSS4  | 46    | DVDD4   | 76    | SD14   | 106   | LED0       |

| 17    | PRAB2  | 47    | IRQ     | 77    | SD7    | 107   | DVDD1      |

| 18    | PRAB3  | 48    | SMAM    | 78    | SD15   | 108   | PRDB7      |

| 19    | PRAB4  | 49    | ĪOR     | 79    | DVSS12 | 109   | PRDB6      |

| 20    | DVSS10 | 50    | ĪŌŴ     | 80    | RXD–   | 110   | PRDB5      |

| 21    | PRAB5  | 51    | BPAM    | 81    | RXD+   | 111   | PRDB4      |

| 22    | PRAB6  | 52    | DVSS11  | 82    | AVDD4  | 112   | PRDB3      |

| 23    | PRAB7  | 53    | AEN     | 83    | TXP–   | 113   | DVSS2      |

| 24    | PRAB8  | 54    | IOCHRDY | 84    | TXD-   | 114   | PRDB2      |

| 25    | DVSS5  | 55    | RESET   | 85    | TXP+   | 115   | PRDB1      |

| 26    | PRAB9  | 56    | SLEEP   | 86    | TXD+   | 116   | PRDB0      |

| 27    | PRAB10 | 57    | IOAM0   | 87    | AVDD3  | 117   | TDI        |

| 28    | PRAB11 | 58    | IOAM1   | 88    | XTAL1  | 118   | TDO        |

| 29    | DVDD3  | 59    | DVDD5   | 89    | AVSS2  | 119   | TMS        |

| 30    | PRAB12 | 60    | SD0     | 90    | XTAL2  | 120   | ТСК        |

# PIN DESIGNATIONS: SHARED MEMORY Listed by Pin Name

| Name  | Pin # | Name       | Pin # | Name   | Pin # | Name  | Pin # |

|-------|-------|------------|-------|--------|-------|-------|-------|

| ABOE  | 38    | DVSS8      | 64    | PRAB10 | 27    | SD2   | 65    |

| AEN   | 53    | DVSS9      | 74    | PRAB11 | 28    | SD3   | 67    |

| APCS  | 3     | DVSS10     | 20    | PRAB12 | 30    | SD4   | 70    |

| AVDD1 | 94    | DVSS11     | 52    | PRAB13 | 31    | SD5   | 72    |

| AVDD2 | 99    | DVSS12     | 79    | PRAB14 | 32    | SD6   | 75    |

| AVDD3 | 87    | DXCVR      | 100   | PRAB15 | 33    | SD7   | 77    |

| AVDD4 | 82    | IOAM0      | 57    | PRDB0  | 116   | SD8   | 61    |

| AVSS1 | 91    | IOAM1      | 58    | PRDB1  | 115   | SD9   | 63    |

| AVSS2 | 89    | IOCHRDY    | 54    | PRDB2  | 114   | SD10  | 66    |

| BPAM  | 51    | IOCS16     | 45    | PRDB3  | 112   | SD11  | 68    |

| BPCS  | 4     | IOR        | 49    | PRDB4  | 111   | SD12  | 71    |

| CI–   | 97    | TOW        | 50    | PRDB5  | 110   | SD13  | 73    |

| CI+   | 98    | IRQ        | 47    | PRDB6  | 109   | SD14  | 76    |

| DI–   | 95    | LED0       | 106   | PRDB7  | 108   | SD15  | 78    |

| DI+   | 96    | LED1       | 105   | RESET  | 55    | SLEEP | 56    |

| DO-   | 92    | LED2       | 103   | RXD-   | 80    | SMA   | 41    |

| DO+   | 93    | LED3       | 102   | RXD+   | 81    | SMAM  | 48    |

| DVDD1 | 107   | MAUSEL/EAR | 101   | SA0    | 5     | SROE  | 42    |

| DVDD2 | 1     | MEMR       | 40    | SA1    | 6     | SRWE  | 44    |

| DVDD3 | 29    | MEMW       | 39    | SA2    | 7     | тск   | 120   |

| DVDD4 | 46    | PRAB0      | 14    | SA3    | 9     | TDI   | 117   |

| DVDD5 | 59    | PRAB1      | 15    | SA4    | 10    | TDO   | 118   |

| DVDD6 | 69    | PRAB2      | 17    | SA5    | 11    | TE    | 2     |

| DVSS1 | 104   | PRAB3      | 18    | SA6    | 12    | TMS   | 119   |

| DVSS2 | 113   | PRAB4      | 19    | SA7    | 35    | TXD-  | 84    |

| DVSS3 | 8     | PRAB5      | 21    | SA8    | 36    | TXD+  | 86    |

| DVSS4 | 16    | PRAB6      | 22    | SA9    | 37    | TXP–  | 83    |

| DVSS5 | 25    | PRAB7      | 23    | SBHE   | 13    | TXP+  | 85    |

| DVSS6 | 34    | PRAB8      | 24    | SD0    | 60    | XTAL1 | 88    |

| DVSS7 | 43    | PRAB9      | 26    | SD1    | 62    | XTAL2 | 90    |

AMD 🎝

# PIN DESIGNATIONS: SHARED MEMORY Listed by Group

| Pin Name          | Pin Function                       | I/O | Driver |

|-------------------|------------------------------------|-----|--------|

| ISA Bus Interface | •                                  | •   | •      |

| AEN               | Address Enable                     | 1   |        |

| IOCHRDY           | I/O Channel Ready                  | 0   | OD3    |

| IOCS16            | I/O Chip Select 16                 | I/O | OD3    |

| IOR               | I/O Read Select                    | I   |        |

| ĪOW               | I/O Write Select                   | I   |        |

| IRQ               | Interrupt Request                  | 0   | OD3    |

| MEMR              | Memory Read Select                 | I   |        |

| MEMW              | Memory Write Select                | 1   |        |

| RESET             | System Reset                       | 1   |        |

| SA0-9             | System Address Bus                 | 1   |        |

| SBHE              | System Byte High Enable            | 1   |        |

| SD0-15            | System Data Bus                    | I/O | TS3    |

| Board Interfaces  | •                                  |     |        |

| ABOE              | Address Buffer Output Enable       | 0   | TS3    |

| APCS              | Address PROM Chip Select           | 0   | TS1    |

| BPAM              | Boot PROM Address Match            | 1   |        |

| BPCS              | Boot PROM Chip Select              | 0   | TS1    |

| DXCVR             | Disable Transceiver                | 0   | TS1    |

| IOAM0-1           | Input/Output Address Map           | 1   |        |

| LED0              | LED0/LNKST                         | 0   | TS2    |

| LED1              | LED1                               | 0   | TS2    |

| LED2              | LED2                               | 0   | TS2    |

| LED3              | LED3                               | 0   | TS2    |

| MAUSEL/EAR        | MAU SELect/External Address Reject | 1   |        |

| PRAB0-15          | PRivate Address Bus                | I/O | TS3    |

| PRDB0-7           | PRivate Data Bus                   | I/O | TS1    |

| SLEEP             | Sleep Mode                         | 1   |        |

| SMA               | Shared Memory Architecture         | I   |        |

| SMAM              | Shared Memory Address Match        | 1   |        |

| SROE              | Static RAM Output Enable           | 0   | TS3    |

| SRWE              | Static RAM Write Enable            | 0   | TS1    |

| TE                | Test Enable                        | 1   |        |

| XTAL1             | Crystal Oscillator Input           | 1   |        |

| XTAL2             | Crystal Oscillator OUTPUT          | 0   |        |

# PIN DESIGNATIONS: SHARED MEMORY (continued) Listed by Group

| Pin Name                         | Pin Function                   | I/O | Driver |  |  |

|----------------------------------|--------------------------------|-----|--------|--|--|

| Attachment Unit Interface (AUI)  |                                |     |        |  |  |

| Cl±                              | Collision Inputs I             |     |        |  |  |

| DI±                              | Receive Data                   | I   |        |  |  |

| DO±                              | Transmit Data                  | 0   |        |  |  |

| Twisted Pair Transceiver Interfa | ace (10BASE–T)                 |     |        |  |  |

| RXD±                             | 10BASE-T Receive Data          | I   |        |  |  |

| TXD±                             | 10BASE-T Transmit Data         | 0   |        |  |  |

| TXP±                             | 10BASE-T Predistortion Control | 0   |        |  |  |

| IEEE 1149.1 Test Access Port In  | nterface (JTAG)                |     |        |  |  |

| ТСК                              | Test Clock                     | I   |        |  |  |

| TDI                              | Test Data Input                | I   |        |  |  |

| TDO                              | Test Data Output               | 0   | TS2    |  |  |

| TMS                              | Test Mode Select               | I   |        |  |  |

| Power Supplies                   |                                |     |        |  |  |

| AVDD                             | Analog Power                   |     |        |  |  |

| AVSS                             | Analog Ground                  |     |        |  |  |

| DVDD                             | Digital Power                  |     |        |  |  |

| DVSS                             | Digital Ground                 |     |        |  |  |

# Table: Output Driver Types

| Name | Туре       | lol (mA) | loh (mA) | pF  |

|------|------------|----------|----------|-----|

| TS1  | Tri-State  | 4        | -1       | 50  |

| TS2  | Tri-State  | 12       | -4       | 50  |

| TS3  | Tri-State  | 24       | -3       | 120 |

| OD3  | Open Drain | 24       | -3       | 120 |

### PIN DESCRIPTION: SHARED MEMORY MODE

### **ISA Interface**

### AEN

#### Address Enable

This signal must be driven LOW when the bus performs an I/O access to the device.

# **IOCHRDY**

### I/O Channel Ready

#### Output

Input

When the PCnet-ISA controller is being accessed, a HIGH on IOCHRDY indicates that valid data exists on the data bus for reads and that data has been latched for writes.

# IOCS16

#### I/O Chip Select 16

### Input/Output

When an I/O read or write operation is performed, the PCnet-ISA controller will drive this pin LOW to indicate that the chip supports a 16-bit operation at this address. (If the motherboard does not receive this signal, then the motherboard will convert a 16-bit access to two 8-bit accesses.) The IOCS16 pin is also an input and must go HIGH at least once after reset for the PCnet-ISA controller to perform 16-bit I/O operations. If this pin is grounded then the PCnet-ISA controller only performs 8-bit I/O operations.

The PCnet-ISA controller follows the IEEE P996 specification that recommends this function be implemented as a pure decode of SA0-9 and AEN, with no dependency on SMEMR, MEMR, MEMW, IOR, or IOW; however, some PC/AT clone systems are not compatible with this approach. For this reason, the PCnet-ISA controller is recommended to be configured to run 8-bit I/O on all machines. Since data is moved by memory cycles there is virtually no performance loss incurred by running 8-bit I/O and compatibility problems are virtually eliminated. The PCnet-ISA controller can be configured to run 8-bit-only I/O by disconnecting the IOCS16 pin from the ISA bus and tying the IOCS16 pin to ground instead.

#### IOR I/O Read

### Input

To perform an Input/Output Read operation on the device IOR must be asserted. IOR is only valid if the AEN signal is LOW and the external address matches the PCnet-ISA controller's predefined I/O address location. If valid, IOR indicates that a slave read operation is to be performed.

#### IOW I/O Write

#### Input

To perform an Input/Output write operation on the device IOW must be asserted. IOW is only valid if AEN signal is LOW and the external address matches the PCnet-ISA controller's predefined I/O address location. If valid, IOW indicates that a slave write operation is to be performed.

# IRQ

# Interrupt Request

An attention signal which indicates that one or more of the following status flags is set: BABL, MISS, MERR, RINT, IDON or TXSTRT. All status flags have a mask bit which allows for suppression of INTR assertion. These flags have the following meaning:

| BABI   | Babble                           |

|--------|----------------------------------|

|        | Dabble                           |

| RCVCCO | Receive Collision Count Overflow |

| JAB    | Jabber                           |

| MISS   | Missed Frame                     |

| MERR   | Memory Error                     |

| MFCO   | Missed Frame Count Overflow      |

| RINT   | Receive Interrupt                |

| IDON   | Initialization Done              |

| TXSTRT | Transmit Start                   |

# MEMR

Input

Output

MEMR goes LOW to perform a memory read operation.

# MEMW

### Memory Write

Memory Read

MEMW goes LOW to perform a memory write operation.

# RESET

#### Reset

# Input

Input

Input

When RESET is asserted HIGH, the PCnet-ISA controller performs an internal system reset. RESET must be held for a minimum of 10 XTAL1 periods before being deasserted. While in a reset state, the PCnet-ISA controller will tristate or deassert all outputs to predefined reset levels. The PCnet-ISA controller resets itself upon power-up.

# SA0-9

# System Address Bus

This bus carries the address inputs from the system address bus. Address data is stable during command active cycle.

# SBHE

# System Bus High Enable Input

This signal indicates the HIGH byte of the system data bus is to be used. There is a weak pull-up resistor on this pin. If the PCnet-ISA controller is installed in an 8-bit only system like the PC/XT, SBHE will always be HIGH and the PCnet-ISA controller will perform only 8-bit operations. There must be at least one LOW going edge on this signal before the PCnet-ISA controller will perform 16-bit operations.

#### SD0-15 System Data Bus

#### Input/Output

This bus is used to transfer data to and from the PCnet-ISA controller to system resources via the ISA data bus. SD0-15 is driven by the PCnet-ISA controller when performing slave read operations.

Likewise, the data on SD0-15 is latched by the PCnet-ISA controller when performing slave write operations.

### **Board Interface**

### ABOE

#### Address Buffer Output Enable Output

This pin goes LOW to enable an external octal buffer to drive the contents of SA10-15 onto PRAB10-15. Only six of the eight buffers are needed.

### APCS

#### Address PROM Chip Select Output

This signal is asserted when the external Address PROM is read. When an I/O read operation is performed on the first 16 bytes in the PCnet-ISA controller's I/O space, APCS is asserted. The outputs of the external Address PROM drive the PROM Data Bus. The PCnet-ISA controller buffers the contents of the PROM data bus and drives them on the lower eight bits of the System Data Bus. IOCS16 is not asserted during this cycle.

### **BPAM**

#### Boot PROM Address Match Input

This pin indicates a Boot PROM access cycle. If no Boot PROM is installed, this pin has a default value of HIGH and thus may be left connected to  $V_{DD}$ .

# BPCS

#### Boot PROM Chip Select Output

This signal is asserted when the Boot PROM is read. If BPAM is active and MEMR is active, the BPCS signal will be asserted. The outputs of the external Boot PROM drive the PROM Data Bus. The PCnet-ISA controller buffers the contents of the PROM data bus and drives them on the System Data Bus. IOCS16 is not asserted during this cycle. If 16-bit cycles are performed, it is the responsibility of external logic to assert MEMCS16 signal.

# DXCVR

#### **Disable Transceiver**

#### Output

This pin disables the transceiver. A high level indicates the Twisted Pair Interface is active and the AUI interface is inactive, or SLEEP mode has been entered. A low level indicates the AUI interface is active and the Twisted Pair interface is inactive.

# IOAM0-1

#### Input/Output Address Map Input

These inputs configure I/O address space for the PCnet-ISA controller. The pins have an on-chip pullup resistor and are pulled HIGH internally. The SA1-9 inputs are used for I/O address comparisons.

| IOAM1,0 | I/O Base |

|---------|----------|

| 0 0     | 300 Hex  |

| 0 1     | 320 Hex  |

| 1 0     | 340 Hex  |

| 1 1     | 360 Hex  |

### LED0-3 LED Drivers

#### Output

These pins sink 12 mA each for driving LEDs. Their meaning is software configurable (see section *ISA Bus Configuration Registers*) and they are active LOW.

When EADI mode is selected, the pins named  $\overline{\text{LED1}}$ ,  $\overline{\text{LED2}}$ , and  $\overline{\text{LED3}}$  change in function while  $\overline{\text{LED0}}$  continues to indicate 10BASE-T Link Status. The MAUSEL input becomes the  $\overline{\text{EAR}}$  input.

| LED | EADI Function |

|-----|---------------|

| 1   | SF/BD         |

| 2   | SRD           |

| 3   | SRDCLK        |

#### MAUSEL/EAR MAU Select/ External Address Reject Input

This pin selects the 10BASE-T MAU when HIGH and the AUI interface when LOW if the XMAUSEL register bit in ISACSR2 (ISA Configuration Register) is set. If the XMAUSEL register bit is cleared, the MAUSEL pin is ignored and the network interface is software selected. This pin has a default value of HIGH if left unconnected.

If EADI mode is selected, this pin becomes the  $\overline{EAR}$  input. The incoming frame will be checked against the internally active address detection mechanisms and the result of this check will be OR'd with the value on the  $\overline{EAR}$  pin. The  $\overline{EAR}$  pin is defined as  $\overline{REJECT}$ . See the EADI section for details regarding the function and timing of this signal.

# **PRAB0-15**

#### **Private Address Bus**

Input/Output

The Private Address Bus is the address bus used to drive the Address PROM, Remote Boot PROM, and SRAM. PRAB10-15 are required to be buffered by a Bus Buffer with ABOE as its control and SA10-15 as its inputs.

### PRDB0-7 Private Data Bus

# Input/Output

This is the data bus for the static RAM, the Boot PROM, and the Address PROM.

# SLEEP

### Sleep

### Input

When SLEEP input is asserted (active LOW), the PCnet-ISA controller performs an internal system reset and proceeds into a power savings mode. All outputs will be placed in their normal reset condition. All PCnet-ISA controller inputs will be ignored except for the SLEEP pin itself. Deassertion of SLEEP results in wake-up. The system must delay the starting of the network controller by 0.5 seconds to allow internal analog circuits to stabilize.

# SMA

### Shared Memory Architecture Input

This pin is sampled after the hardware RESET sequence. The pin must be pulled permanently LOW for operation in the shared memory mode.

# SMAM

### Shared Memory Address Match Input

This pin indicates an access to shared memory when active. The type of access is decided by  $\overline{\text{MEMR}}$  or  $\overline{\text{MEMW}}.$

# SROE

# Static RAM Output Enable Output

This pin directly controls the external SRAM's  $\overline{\text{OE}}$  pin.

# SRWE

# Static RAM Write Enable Output

This pin directly controls the external SRAM's WE pin.

# ΤE

### Test Enable

Input

This pin is for factory use only. It has a default value of HIGH if left unconnected. It is strongly recommended that this pin always be connected to  $V_{\text{DD}}$ .

# XTAL1

# Crystal Connection

Input

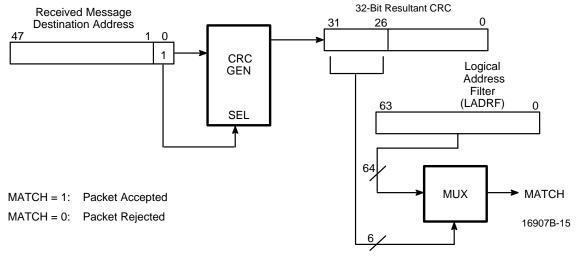

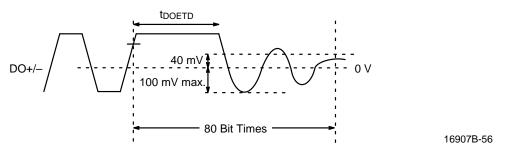

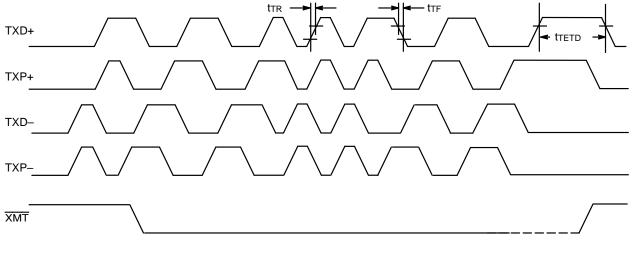

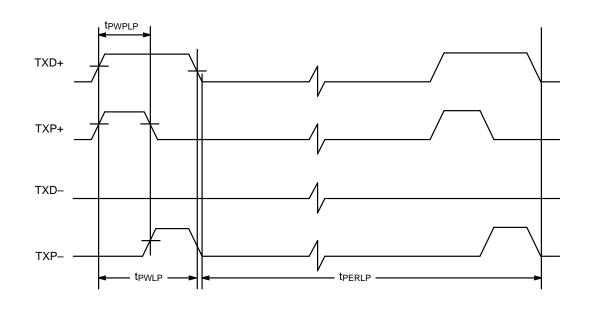

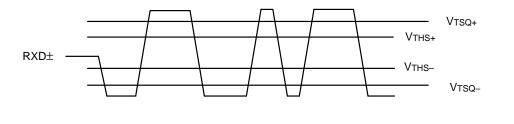

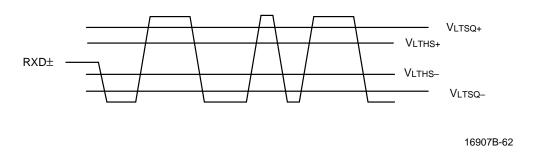

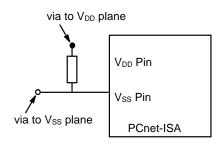

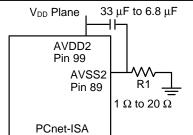

Output