## 读WH.DIL PHY 捷多邦,专业PCB打样工厂,24小时加急

**OKI** Semiconductor

出货 This version: Jan. 1998 Previous version: Aug. 1996 VJS

# MSM82C55A-2RS/GS/VJS

#### CMOS PROGRAMMABLE PERIPHERAL INTERFACE

## **GENERAL DESCRIPTION**

The MSM82C55A-2 is a programmable universal I/O interface device which operates as high speed and on low power consumption due to  $3\mu$  silicon gate CMOS technology. It is the best fit as an I/O port in a system which employs the 8-bit parallel processing MSM80C85AH CPU. This device has 24-bit I/O pins equivalent to three 8-bit I/O ports and all inputs/outputs are TTL interface compatible.

W.DZSC.COM

#### FEATURES

- High speed and low power consumption due to 3µ silicon gate CMOS technology

- 3 V to 6 V single power supply

- Full static operation

- Programmable 24-bit I/O ports

- Bidirectional bus operation (Port A)

- Bit set/reset function (Port C)

- TTL compatible

- Compatible with 8255A-5

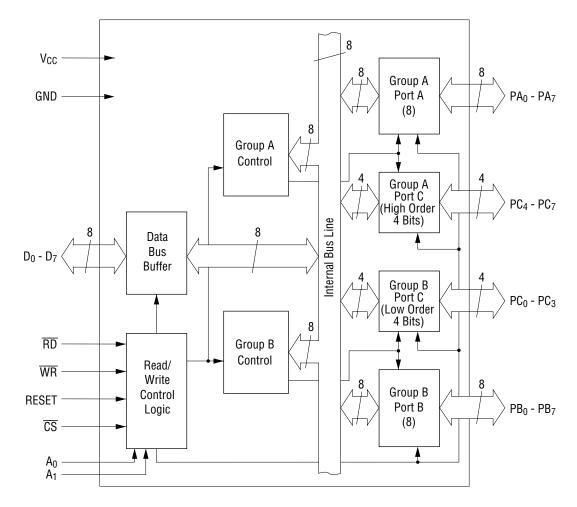

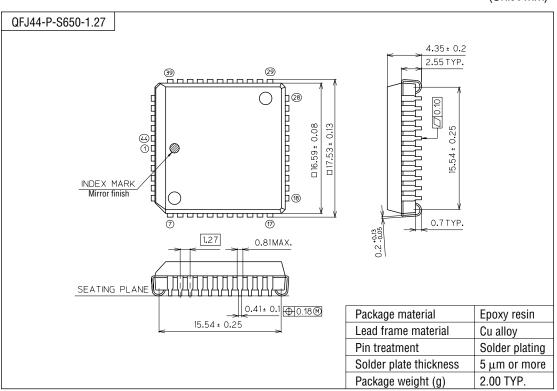

- 40-pin Plastic DIP (DIP40-P-600-2.54): (Product name: MSM82C55A-2RS)

- 44-pin Plastic QFJ (QFJ44-P-S650-1.27): (Product name: MSM82C55A-2VJS)

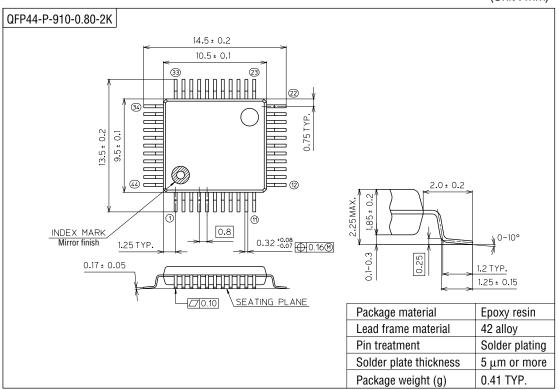

- 44-pin Plastic QFP (QFP44-P-910-0.80-2K): (Product name: MSM82C55A-2GS-2K)

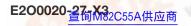

## **CIRCUIT CONFIGURATION**

#### **PIN CONFIGURATION (TOP VIEW)**

| Parameter           | Sumbal           | Conditions   |                              | Rating                       |                | Unit |  |  |

|---------------------|------------------|--------------|------------------------------|------------------------------|----------------|------|--|--|

| Parameter           | Symbol           | Conditions   | MSM82C55A-2RS                | MSM82C55A-2GS                | MSM82C55A-2vJS |      |  |  |

| Supply Voltage      | V <sub>CC</sub>  | Ta = 25°C    |                              | -0.5 to +7                   |                | V    |  |  |

| Input Voltage       | V <sub>IN</sub>  | with respect |                              | –0.5 to V <sub>CC</sub> +0.5 |                |      |  |  |

| Output Voltage      | V <sub>OUT</sub> | to GND       | –0.5 to V <sub>CC</sub> +0.5 |                              |                |      |  |  |

| Storage Temperature | T <sub>STG</sub> | —            | -55 to +150                  |                              |                |      |  |  |

| Power Dissipation   | PD               | Ta = 25°C    | 1.0                          | 0.7                          | 1.0            | W    |  |  |

## ABSOLUTE MAXIMUM RATINGS

#### **OPERATING RANGE**

| Parameter             | Symbol          | Range     | Unit |  |  |

|-----------------------|-----------------|-----------|------|--|--|

| Supply Voltage        | V <sub>CC</sub> | 3 to 6    | V    |  |  |

| Operating Temperature | T <sub>op</sub> | -40 to 85 | °C   |  |  |

## **RECOMMENDED OPERATING RANGE**

| Parameter             | Symbol          | Min. | Тур. | Max.                  | Unit |

|-----------------------|-----------------|------|------|-----------------------|------|

| Supply Voltage        | Vcc             | 4.5  | 5    | 5.5                   | V    |

| Operating Temperature | T <sub>op</sub> | -40  | +25  | +85                   | °C   |

| "L" Input Voltage     | VIL             | -0.3 | _    | +0.8                  | V    |

| "H" Input Voltage     | V <sub>IH</sub> | 2.2  |      | V <sub>CC</sub> + 0.3 | V    |

#### **DC CHARACTERISTICS**

|                                    |                 |                                                                                                                                          |                                  | MS   | A-2  | llmit |      |

|------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|------|-------|------|

| Parameter                          | Symbol          | Condi                                                                                                                                    | tions                            | Min. | Тур. | Max.  | Unit |

| "L" Output Voltage                 | V <sub>OL</sub> | I <sub>0L</sub> = 2.5 mA                                                                                                                 |                                  | _    |      | 0.4   | V    |

| "H" Output Voltage                 | V <sub>OH</sub> | I <sub>OH</sub> = −40 μA                                                                                                                 |                                  | 4.2  | —    | _     | V    |

|                                    | VOH             | I <sub>0H</sub> = -2.5 mA                                                                                                                |                                  | 3.7  | —    | —     | V    |

| Input Leak Current                 | ILI             | $0 \le V_{IN} \le V_{CC}$                                                                                                                | V <sub>CC</sub> = 4.5 V to 5.5 V | -1   | —    | 1     | μA   |

| Output Leak Current                | ILO             | $0 \le V_{OUT} \le V_{CC}$                                                                                                               | Ta = -40°C to +85°C              | -10  | —    | 10    | μA   |

| Supply Current<br>(Standby)        | Iccs            | $\label{eq:VCC} \begin{split} \overline{CS} &\geq V_{CC} - 0.2 \ V \\ V_{IH} &\geq V_{CC} - 0.2 \ V \\ V_{IL} &\leq 0.2 \ V \end{split}$ | (C <sub>L</sub> = 0 pF)          | —    | 0.1  | 10    | μA   |

| Average Supply<br>Current (Active) | Icc             | I/O Wire Cycle<br>82C55A-2<br>8 MHzCPU Timing                                                                                            |                                  |      |      | 8     | mA   |

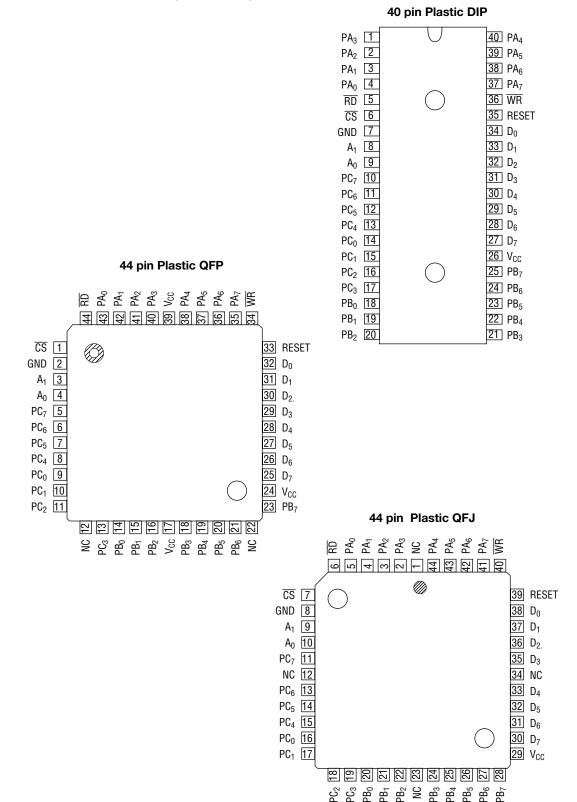

## **AC CHARACTERISTICS**

|                                                                                         | <b>.</b>         | MSM82 | 2C55A-2 |      | Dame    |

|-----------------------------------------------------------------------------------------|------------------|-------|---------|------|---------|

| Parameter                                                                               | Symbol           | Min.  | Max.    | Unit | Remarks |

| Setup Time of Address to the Falling Edge of RD                                         | t <sub>AR</sub>  | 20    | _       | ns   |         |

| Hold Time of Address to the Rising Edge of RD                                           | t <sub>RA</sub>  | 0     | _       | ns   |         |

| RD Pulse Width                                                                          | t <sub>RR</sub>  | 100   | _       | ns   |         |

| Delay Time from the Falling Edge of $\overline{	ext{RD}}$ to the Output of Defined Data | t <sub>RD</sub>  | _     | 120     | ns   | _       |

| Delay Time from the Rising Edge of <del>RD</del> to the Floating of<br>Data Bus         | t <sub>DF</sub>  | 10    | 75      | ns   |         |

| Time from the Rising Edge of RD or WR to the Next Falling<br>Edge of RD or WR           | t <sub>RV</sub>  | 200   | _       | ns   |         |

| Setup Time of Address before the Falling Edge of WR                                     | t <sub>AW</sub>  | 0     | _       | ns   |         |

| Hold Time of Address after the Rising Edge of WR                                        | t <sub>WA</sub>  | 20    | _       | ns   |         |

| WR Pulse Width                                                                          | tww              | 150   | _       | ns   |         |

| Setup Time of Bus Data before the Rising Edge of $\overline{WR}$                        | t <sub>DW</sub>  | 50    | _       | ns   |         |

| Hold Time of Bus Data after the Rising Edge of $\overline{WR}$                          | t <sub>WD</sub>  | 30    |         | ns   |         |

| Delay Time from the rising Edge of WR to the Output of<br>Defined Data                  | t <sub>WB</sub>  | _     | 200     | ns   |         |

| Setup Time of Port Data before the Falling Edge of $\overline{RD}$                      | t <sub>IR</sub>  | 20    | _       | ns   |         |

| Hold Time of Port Data after the Rising Edge of $\overline{RD}$                         | t <sub>HR</sub>  | 10    | _       | ns   |         |

| ACK Pulse Width                                                                         | t <sub>AK</sub>  | 100   | _       | ns   | Load    |

| STB Pulse Width                                                                         | t <sub>ST</sub>  | 100   | _       | ns   | 150 pF  |

| Setup Time of Port Data before the rising Edge of STB                                   | t <sub>PS</sub>  | 20    |         | ns   |         |

| Hold Time of Port Bus Data after the rising Edge of STB                                 | t <sub>PH</sub>  | 50    | _       | ns   |         |

| Delay Time from the Falling Edge of ACK to the Output of Defined Data                   | t <sub>AD</sub>  | _     | 150     | ns   |         |

| Delay Time from the Rising Edge of ACK to the Floating of Port (Port A in Mode 2)       | t <sub>KD</sub>  | 20    | 250     | ns   |         |

| Delay Time from the Rising Edge of WR to the Falling Edge of OBF                        | t <sub>WOB</sub> | _     | 150     | ns   |         |

| Delay Time from the Falling Edge of ACK to the Rising Edge of OBF                       | t <sub>AOB</sub> | _     | 150     | ns   |         |

| Delay Time from the Falling Edge of STB to the Rising Edge of IBF                       | t <sub>SIB</sub> | _     | 150     | ns   |         |

| Delay Time from the Rising Edge of $\overline{	ext{RD}}$ to the Falling Edge of IBF     | t <sub>RIB</sub> | _     | 150     | ns   |         |

| Delay Time from the the Falling Edge of RD to the Falling Edge of INTR                  | t <sub>RIT</sub> | _     | 200     | ns   |         |

| Delay Time from the Rising Edge of STB to the Rising Edge of INTR                       | t <sub>SIT</sub> | _     | 150     | ns   |         |

| Delay Time from the Rising Edge of ACK to the Rising Edge of INTR                       | t <sub>AIT</sub> | _     | 150     | ns   |         |

| Delay Time from the Falling Edge of $\overline{WR}$ to the Falling Edge of INTR         | t <sub>WIT</sub> | _     | 250     | ns   |         |

|                                                                                         |                  |       |         |      |         |

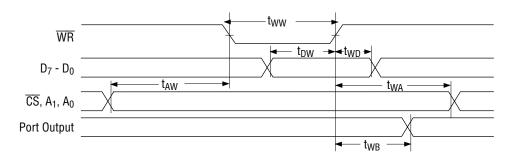

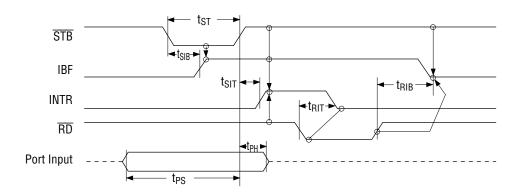

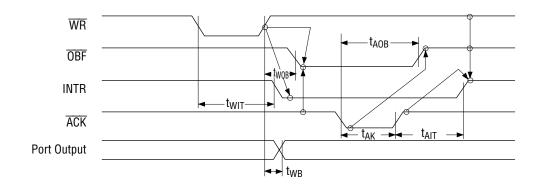

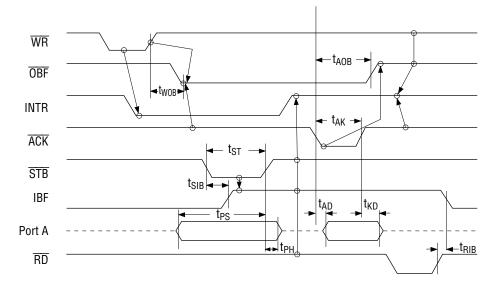

#### TIMING DIAGRAM

#### **Basic Input Operation (Mode 0)**

#### **Basic Output Operation (Mode 0)**

## Strobe Input Operation (Mode 1)

#### Strobe Output Operation (Mode 1)

#### **Bidirectional Bus Operation (Mode 2)**

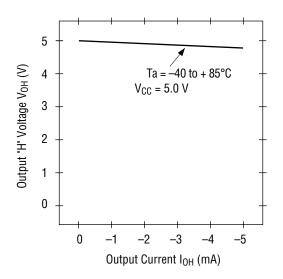

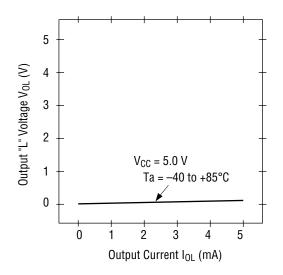

#### **OUTPUT CHARACTERISTICS (REFERENCE VALUE)**

1 Output "H" Voltage (V<sub>OH</sub>) vs. Output Current (I<sub>OH</sub>)

2 Output "L" Voltage (VoL) vs. Output Current (IoL)

Note: The direction of flowing into the device is taken as positive for the output current.

## **PIN DESCRIPTION**

| Pin No.                           | Item                           | Input/Output        | Function                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-----------------------------------|--------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| D <sub>7</sub> - D <sub>0</sub>   | Bidirectional<br>Data Bus      | Input and<br>Output | These are three-state 8-bit bidirectional buses used to write and read data upon receipt of the $\overline{WR}$ and $\overline{RD}$ signals from CPU and also used when control words and bit set/reset data are transferred from CPU to MSM82C55A-2.                                                                             |  |  |  |  |

| RESET                             | Reset Input                    | Input               | This signal is used to reset the control register and all internal<br>registers when it is in high level. At this time, ports are all made int<br>the input mode (high impedance status).<br>all port latches are cleared to 0.<br>and all ports groups are set to mode 0.                                                        |  |  |  |  |

| CS                                | Chip Select<br>Input           | Input               | When the $\overline{\text{CS}}$ is in low level, data transmission is enabled with CPU.<br>When it is in high level, the data bus is made into the high impedance<br>status where no write nor read operation is performed. Internal<br>registers hold their previous status, however.                                            |  |  |  |  |

| RD                                | Read Input                     | Input               | When $\overline{\text{RD}}$ is in low level, data is transferred from MSM82C55A-2 to CPU.                                                                                                                                                                                                                                         |  |  |  |  |

| WR                                | Write Input                    | Input               | When $\overline{\rm WR}$ is in low level, data or control words are transferred from CPU to MSM82C55A-2.                                                                                                                                                                                                                          |  |  |  |  |

| A <sub>0</sub> , A <sub>1</sub>   | Port Select Input<br>(Address) | Input               | By combination of $A_0$ and $A_1$ , either one is selected from among port A, port B, port C, and control register. These pins are usually connected to low order 2 bits of the address bus.                                                                                                                                      |  |  |  |  |

| PA <sub>7</sub> - PA <sub>0</sub> | Port A                         | Input and<br>Output | These are universal 8-bit I/O ports. The direction of inputs/ outputs can be determined by writing a control word. Especially, port A can be used as a bidirectional port when it is set to mode 2.                                                                                                                               |  |  |  |  |

| PB <sub>7</sub> - PB <sub>0</sub> | Port B                         | Input and<br>Output | These are universal 8-bit I/O ports. The direction of inputs/outputs ports can be determined by writing a control word.                                                                                                                                                                                                           |  |  |  |  |

| PC <sub>7</sub> - PC <sub>0</sub> | Port C                         | Input and<br>Output | These are universal 8-bit I/O ports. The direction of inputs/outputs can be determined by writing a control word as 2 ports with 4 bits each. When port A or port B is used in mode 1 or mode 2 (port A only), they become control pins. Especially, when port C is used as an output port, each bit can set/reset independently. |  |  |  |  |

| V <sub>CC</sub>                   | -                              | -                   | +5V power supply.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| GND                               | -                              | -                   | GND                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

#### **BASIC FUNCTIONAL DESCRIPTION**

#### Group A and Group B

When setting a mode to a port having 24 bits, set it by dividing it into two groups of 12 bits each.

Group A: Port A (8 bits) and high order 4 bits of port C ( $PC_7 \sim PC_4$ ) Group B: Port B (8 bits) and low order 4 bits of port C ( $PC_3 \sim PC_0$ )

#### Mode 0, 1, 2

There are 3 types of modes to be set by grouping as follows:

Mode 0: Basic input operation/output operation (Available for both groups A and B) Mode 1: Strobe input operation/output operation (Available for both groups A and B) Mode 2: Bidirectional bus operation (Available for group A only)

When used in mode 1 or mode 2, however, port C has bits to be defined as ports for control signal for operation ports (port A for group A and port B for group B) of their respective groups.

#### Port A, B, C

The internal structure of 3 ports is as follows:

Port A: One 8-bit data output latch/buffer and one 8-bit data input latch Port B: One 8-bit data input/output latch/buffer and one 8-bit data input buffer Port C: One 8-bit data output latch/buffer and one 8-bit data input buffer (no latch for input)

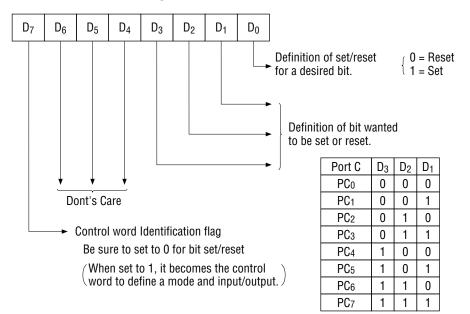

#### Single bit set/reset function for port C

When port C is defined as an output port, it is possible to set (to turn to high level) or reset (to turn to low level) any one of 8 bits individually without affecting other bits.

#### **OPERATIONAL DESCRIPTION**

#### **Control Logic**

Operations by addresses and control signals, e.g., read and write, etc. are as shown in the table below:

| Operaiton |   |   |   |   | Operation |                                           |

|-----------|---|---|---|---|-----------|-------------------------------------------|

|           | 0 | 0 | 0 | 1 | 0         | Port A $\rightarrow$ Data Bus             |

| Input     | 0 | 1 | 0 | 1 | 0         | Port B $\rightarrow$ Data Bus             |

|           | 1 | 0 | 0 | 1 | 0         | Port C $\rightarrow$ Data Bus             |

|           | 0 | 0 | 0 | 0 | 1         | Data Bus $\rightarrow$ Port A             |

| Output    | 0 | 1 | 0 | 0 | 1         | Data Bus $\rightarrow$ Port B             |

|           | 1 | 0 | 0 | 0 | 1         | Data Bus $\rightarrow$ Port C             |

| Control   | 1 | 1 | 0 | 0 | 1         | Data Bus $\rightarrow$ Control Register   |

| Others    | 1 | 1 | 0 | 1 | 0         | Illegal Condition                         |

|           | × | × | 1 | × | ×         | Data bus is in the high impedance status. |

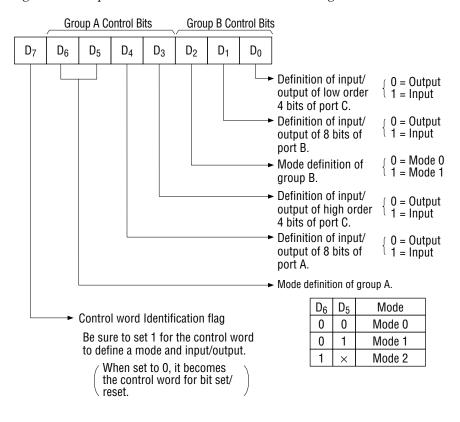

#### Setting of Control Word

The control register is composed of 7-bit latch circuit and 1-bit flag as shown below.

#### Precaution for Mode Selection

The output registers for ports A and C are cleared to  $\phi$  each time data is written in the command register and the mode is changed, but the port B state is undefined.

#### **Bit Set/Reset Function**

When port C is defined as output port, it is possible to set (set output to 1) or reset (set output to 0) any one of 8 bits without affecting other bits as shown below.

#### **Interrupt Control Function**

When the MSM82C55A-2 is used in mode 1 or mode 2, the interrupt signal for the CPU is provided. The interrupt request signal is output from port C. When the internal flip-flop INTE is set beforehand at this time, the desired interrupt request signal is output. When it is reset beforehand, however, the interrupt request signal is not output. The set/reset of the internal flip-flop is made by the bit set/reset operation for port C virtually.

Bit set  $\rightarrow$  INTE is set  $\rightarrow$  Interrupt allowed Bit reset  $\rightarrow$  INTE is reset  $\rightarrow$  Interrupt inhibited

#### **Operational Description by Mode**

#### 1. Mode 0 (Basic input/output operation)

Mode 0 makes the MSM82C55A-2 operate as a basic input port or output port. No control signals such as interrupt request, etc. are required in this mode. All 24 bits can be used as two-8-bit ports and two 4-bit ports. Sixteen combinations are then possible for inputs/ outputs. The inputs are not latched, but the outputs are.

|      |            |          | Co | ntro | ol W           | ord |                |                |        | Group A                        |        | Group B                       |

|------|------------|----------|----|------|----------------|-----|----------------|----------------|--------|--------------------------------|--------|-------------------------------|

| Туре | <b>D</b> 7 | D7 D6 D5 |    | D4   | D <sub>3</sub> | D2  | D <sub>1</sub> | D <sub>0</sub> | Port A | High Order 4 Bits<br>of Port C | Port B | Low Order 4 Bits<br>of Port C |

| 1    | 1          | 0        | 0  | 0    | 0              | 0   | 0              | 0              | Output | Output                         | Output | Output                        |

| 2    | 1          | 0        | 0  | 0    | 0              | 0   | 0              | 1              | Output | Output                         | Output | Input                         |

| 3    | 1          | 0        | 0  | 0    | 0              | 0   | 1              | 0              | Output | Output                         | Input  | Output                        |

| 4    | 1          | 0        | 0  | 0    | 0              | 0   | 1              | 1              | Output | Output                         | Input  | Input                         |

| 5    | 1          | 0        | 0  | 0    | 1              | 0   | 0              | 0              | Output | Input                          | Output | Output                        |

| 6    | 1          | 0        | 0  | 0    | 1              | 0   | 0              | 1              | Output | Input                          | Output | Input                         |

| 7    | 1          | 0        | 0  | 0    | 1              | 0   | 1              | 0              | Output | Input                          | Input  | Ouput                         |

| 8    | 1          | 0        | 0  | 0    | 1              | 0   | 1              | 1              | Output | Input                          | Input  | Input                         |

| 9    | 1          | 0        | 0  | 1    | 0              | 0   | 0              | 0              | Input  | Output                         | Output | Output                        |

| 10   | 1          | 0        | 0  | 1    | 0              | 0   | 0              | 1              | Input  | Output                         | Output | Input                         |

| 11   | 1          | 0        | 0  | 1    | 0              | 0   | 1              | 0              | Input  | Output                         | Input  | Output                        |

| 12   | 1          | 0        | 0  | 1    | 0              | 0   | 1              | 1              | Input  | Output                         | Input  | Input                         |

| 13   | 1          | 0        | 0  | 1    | 1              | 0   | 0              | 0              | Input  | Input                          | Output | Output                        |

| 14   | 1          | 0        | 0  | 1    | 1              | 0   | 0              | 1              | Input  | Input                          | Output | Input                         |

| 15   | 1          | 0        | 0  | 1    | 1              | 0   | 1              | 0              | Input  | Input                          | Input  | Output                        |

| 16   | 1          | 0        | 0  | 1    | 1              | 0   | 1              | 1              | Input  | Input                          | Input  | Input                         |

Notes: When used in mode 0 for both groups A and B

#### 2. Mode 1 (Strobe input/output operation)

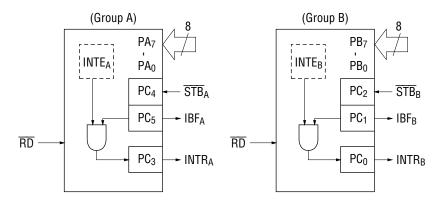

In mode 1, the strobe, interrupt and other control signals are used when input/output operations are made from a specified port. This mode is available for both groups A and B. In group A at this time, port A is used as the data line and port C as the control signal. Following is a description of the input operation in mode 1.

#### **STB** (Strobe input)

When this signal is low level, the data output from terminal to port is fetched into the internal latch of the port. This can be made independent from the CPU, and the data is not output to the data bus until the RD signal arrives from the CPU.

#### **IBF** (Input buffer full flag output)

This is the response signal for the  $\overline{\text{STB}}$ . This signal when turned to high level indicates that data is fetched into the input latch. This signal turns to high level at the falling edge of  $\overline{\text{STB}}$  and to low level at the rising edge of  $\overline{\text{RD}}$ .

#### **INTR (Interrupt request output)**

This is the interrupt request signal for the CPU of the data fetched into the input latch. It is indicated by high level only when the internal INTE flip-flop is set. This signal turns to high level at the rising edge of the  $\overline{\text{STB}}$  (IBF = 1 at this time) and low level at the falling edge of the  $\overline{\text{RD}}$  when the INTE is set.

INTE  $_A$  of group A is set when the bit for PC<sub>4</sub> is set, while INTE  $_B$  of group B is set when the bit for PC<sub>2</sub> is set.

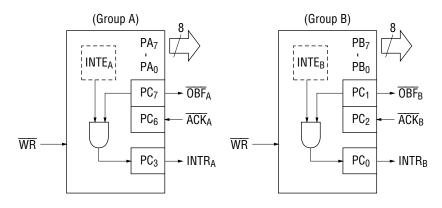

Following is a description of the output operation of mode 1.

#### **OBF** (Output buffer full flag output)

This signal when turned to low level indicates that data is written to the specified port upon receipt of the  $\overline{WR}$  signal from the CPU. This signal turns to low level at the rising edge of the  $\overline{WR}$  and high level at the falling edge of the ACK.

#### **ACK** (Acknowledge input)

This signal when turned to low level indicates that the terminal has received data.

#### **INTR (Interrupt request output)**

This is the signal used to interrupt the CPU when a terminal receives data from the CPU via the MSM82C55A-5. It indicates the occurrence of the interrupt in high level only when the internal INTE flip-flop is set. This signal turns to high level at the rising edge of the  $\overline{ACK}$  (OBF = 1 at this time) and low level at the falling edge of  $\overline{WR}$  when the INTE B is set. INTE A of group A is set when the bit for PC<sub>6</sub> is set, while INTE B of group B is set when the bit for PC<sub>2</sub> is set.

#### Mode 1 Input

**Note:** Although belonging to group B, PC<sub>3</sub> operates as the control signal of group A functionally.

#### Mode 1 Output

| Combination of<br>Input/Output<br>Port C | Group A: Input<br>Group B: Input | Group A: Input<br>Group B: Output | Group A: Output<br>Group B: Input | Group A: Output<br>Group B: Output |  |

|------------------------------------------|----------------------------------|-----------------------------------|-----------------------------------|------------------------------------|--|

| PC <sub>0</sub>                          | INTR <sub>B</sub>                | INTR <sub>B</sub>                 | INTR <sub>B</sub>                 | INTRв                              |  |

| PC <sub>1</sub>                          | IBF <sub>B</sub>                 | <b>OBF</b> <sub>B</sub>           | IBF <sub>B</sub>                  | OBF <sub>B</sub>                   |  |

| PC <sub>2</sub>                          | <b>STB</b> <sub>B</sub>          | ACKB                              | STBB                              | ACKB                               |  |

| PC <sub>3</sub>                          | INTR <sub>A</sub>                | INTR <sub>A</sub>                 | INTRA                             | INTRA                              |  |

| PC <sub>4</sub>                          | STBA                             | STBA                              | I/O                               | I/O                                |  |

| PC <sub>5</sub>                          | IBF <sub>A</sub>                 | IBF <sub>A</sub>                  | I/O                               | I/O                                |  |

| PC <sub>6</sub>                          | I/O                              | I/0                               | ACKA                              | ACKA                               |  |

| PC <sub>7</sub>                          | I/O                              | I/0                               | OBFA                              | OBFA                               |  |

#### Port C Function Allocation in Mode 1

Note: I/O is a bit not used as the control signal, but it is available as a port of mode 0.

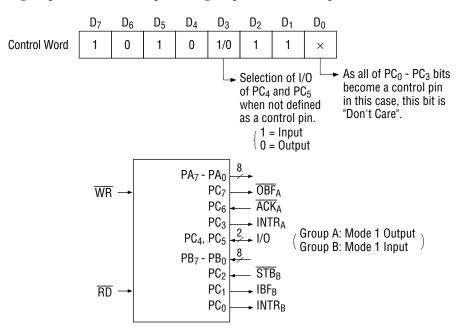

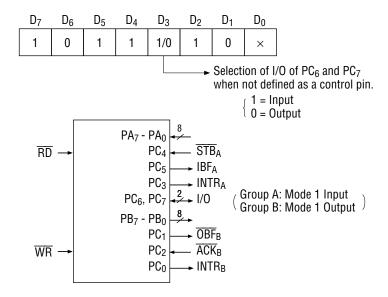

Examples of the relation between the control words and pins when used in mode 1 are shown below:

(a) When group A is mode 1 output and group B is mode 1 input.

(b) When group A is mode 1 input and group B is mode 1 output.

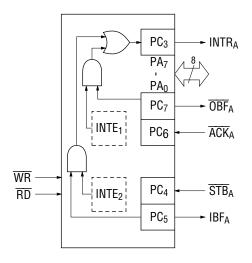

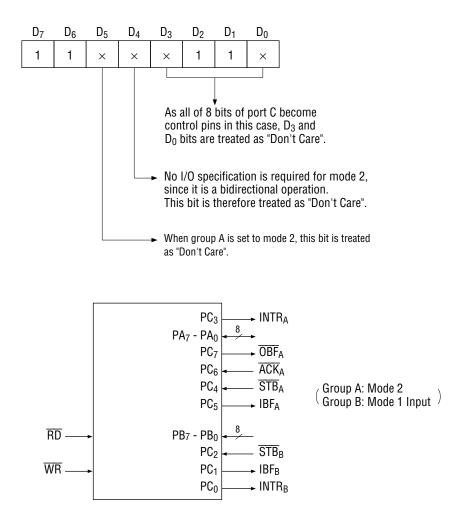

#### 3. Mode 2 (Strobe bidirectional bus I/O operation)

In mode 2, it is possible to transfer data in 2 directions through a single 8-bit port. This operation is akin to a combination between input and output operations. Port C waits for the control signal in this case, too. Mode 2 is available only for group A, however. Next, a description is made on mode 2.

#### **OBF** (Output buffer full flag output)

This signal when turned to low level indicates that data has been written to the internal output latch upon receipt of the  $\overline{WR}$  signal from the CPU. At this time, port A is still in the high impedance status and the data is not yet output to the outside. This signal turns to low level at the rising edge of the WR and high level at the falling edge of the  $\overline{ACK}$ .

#### **ACK** (Acknowledge input)

When a low level signal is input to this pin, the high impedance status of port A is cleared, the buffer is enabled, and the data written to the internal output latch is output to port A. When the input returns to high level, port A is made into the high impedance status.

#### **STB** (Strobe input)

When this signal turns to low level, the data output to the port from the pin is fetched into the internal input latch. The data is output to the data bus upon receipt of the RD signal from the CPU, but it remains in the high impedance status until then.

#### IBF (Input buffer full flag output)

This signal when turned to high level indicates that data from the pin has been fetched into the input latch. This signal turns to high level at the falling edge of the  $\overline{\text{STB}}$  and low level at the rising edge of the  $\overline{\text{RD}}$ .

#### **INTR (Interrupt request output)**

This signal is used to interrupt the CPU and its operation in the same as in mode 1. There are two INTE flip-flops internally available for input and output to select either interrupt of input or output operation. The INTE1 is used to control the interrupt request for output operation and it can be reset by the bit set for PC6. INTE2 is used to control the interrupt request for the input operation and it can be set by the bit set for PC4.

#### Mode 2 I/O Operation

#### Port C Function Allocation in Mode 2

| Port C          | Function                      |

|-----------------|-------------------------------|

| PC <sub>0</sub> |                               |

| PC <sub>1</sub> | Confirmed to the Group B Mode |

| PC <sub>2</sub> |                               |

| PC <sub>3</sub> | INTR <sub>A</sub>             |

| PC <sub>4</sub> | STBA                          |

| PC <sub>5</sub> | IBF <sub>A</sub>              |

| PC <sub>6</sub> | ACKA                          |

| PC <sub>7</sub> | OBF <sub>A</sub>              |

Following is an example of the relation between the control word and the pin when used in mode 2.

When input in mode 2 for group A and in mode 1 for group B.

#### 4. When Group A is Different in Mode from Group B

Group A and group B can be used by setting them in different modes each other at the same time. When either group is set to mode 1 or mode 2, it is possible to set the one not defined as a control pin in port C to both input and output as port which operates in mode 0 at the 3rd and 0th bits of the control word.

|   | 0                | 0                |                  |                 |                  | Po              | ort C             |                         |                  |                   |

|---|------------------|------------------|------------------|-----------------|------------------|-----------------|-------------------|-------------------------|------------------|-------------------|

|   | Group A          | Group B          | PC <sub>7</sub>  | PC <sub>6</sub> | PC <sub>5</sub>  | PC <sub>4</sub> | PC <sub>3</sub>   | PC <sub>2</sub>         | PC <sub>1</sub>  | PC <sub>0</sub>   |

| 1 | Mode 1<br>input  | Mode 0           | I/O              | I/O             | IBF <sub>A</sub> | STBA            | INTR <sub>A</sub> | I/O                     | I/0              | I/O               |

| 2 | Mode 0<br>Output | Mode 0           | OBF <sub>A</sub> | ACKA            | I/0              | I/0             | INTR <sub>A</sub> | I/O                     | I/0              | I/0               |

| 3 | Mode 0           | Mode 1<br>Input  | I/0              | I/O             | I/O              | I/0             | I/O               | <u>STB</u> <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |

| 4 | Mode 0           | Mode 1<br>Output | I/0              | I/O             | I/0              | I/O             | I/O               | <b>ACK</b> <sub>B</sub> | OBF <sub>B</sub> | INTR <sub>B</sub> |

| 5 | Mode 1<br>Input  | Mode 1<br>Input  | I/0              | I/O             | IBF <sub>A</sub> | STBA            | INTR <sub>A</sub> | <u>STB</u> <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |

| 6 | Mode 1<br>Input  | Mode 1<br>Output | I/0              | I/O             | IBF <sub>A</sub> | STBA            | INTRA             | <b>ACK</b> <sub>B</sub> | OBF <sub>B</sub> | INTR <sub>B</sub> |

| 7 | Mode 1<br>Output | Mode 1<br>Input  | OBF <sub>A</sub> | ACKA            | I/O              | I/O             | INTR <sub>A</sub> | <b>STB</b> <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |

| 8 | Mode 1<br>Output | Mode 1<br>Output | OBF <sub>A</sub> | ACKA            | I/O              | I/O             | INTR <sub>A</sub> | ACKB                    | 0BF <sub>B</sub> | INTR <sub>B</sub> |

| 9 | Mode 2           | Mode 0           | OBFA             | ACKA            | IBF <sub>A</sub> | STBA            | INTR <sub>A</sub> | I/0                     | I/0              | I/0               |

#### (Mode combinations that define no control bit at port C)

Controlled at the 3rd bit (D<sub>3</sub>) of the Control Word

Controlled at the 0th bit  $(D_0)$  of the Control Word

When the I/O bit is set to input in this case, it is possible to access data by the normal port C read operation.

When set to output,  $PC_7$ - $PC_4$  bits can be accessed by the bit set/reset function only. Meanwhile, 3 bits from  $PC_2$  to  $PC_0$  can be accessed by normal write operation.

The bit set/reset function can be used for all of  $PC_3$ - $PC_0$  bits. Note that the status of port C varies according to the combination of modes like this.

#### **OKI** Semiconductor

#### 5. Port C Status Read

When port C is used for the control signal, that is, in either mode 1 or mode 2, each control signal and bus status signal can be read out by reading the content of port C. The status read out is as follows:

|    |                  | <b>•</b> •       |                  |                   | State            | us Read o         | on the Da         | ta Bus            |                  |                   |

|----|------------------|------------------|------------------|-------------------|------------------|-------------------|-------------------|-------------------|------------------|-------------------|

|    | Group A          | Group B          | D <sub>7</sub>   | D <sub>6</sub>    | D <sub>5</sub>   | D <sub>4</sub>    | D <sub>3</sub>    | D <sub>2</sub>    | D <sub>1</sub>   | D <sub>0</sub>    |

| 1  | Mode 1<br>Input  | Mode 0           | I/0              | I/O               | IBF <sub>A</sub> | INTE <sub>A</sub> | INTR <sub>A</sub> | I/O               | I/0              | I/O               |

| 2  | Mode 1<br>Output | Mode 0           | OBF <sub>A</sub> | INTE <sub>A</sub> | I/O              | I/0               | INTR <sub>A</sub> | I/O               | I/0              | I/O               |

| 3  | Mode 0           | Mode 1<br>Input  | I/0              | I/O               | I/O              | I/O               | I/O               | INTE <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |

| 4  | Mode 0           | Mode 1<br>Output | I/0              | I/O               | I/O              | I/O               | I/O               | INTE <sub>B</sub> | OBF <sub>B</sub> | INTR <sub>B</sub> |

| 5  | Mode 1<br>Input  | Mode 1<br>Input  | I/0              | I/O               | IBF <sub>A</sub> | INTE <sub>A</sub> | INTR <sub>A</sub> | INTE <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |

| 6  | Mode 1<br>Input  | Mode 1<br>Output | I/0              | I/O               | IBF <sub>A</sub> | INTE <sub>A</sub> | INTR <sub>A</sub> | INTE <sub>B</sub> | OBF <sub>B</sub> | INTR <sub>B</sub> |

| 7  | Mode 1<br>Output | Mode 1<br>Input  | OBF <sub>A</sub> | INTE <sub>A</sub> | I/0              | I/O               | INTR <sub>A</sub> | INTE <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |

| 8  | Mode 1<br>Output | Mode 1<br>Output | OBF <sub>A</sub> | INTEA             | I/0              | I/O               | INTR <sub>A</sub> | INTE <sub>B</sub> | 0BF <sub>B</sub> | INTR <sub>B</sub> |

| 9  | Mode 2           | Mode 0           | OBFA             | INTE <sub>1</sub> | IBF <sub>A</sub> | INTE <sub>2</sub> | INTR <sub>A</sub> | I/0               | I/0              | I/0               |

| 10 | Mode 2           | Mode 1<br>Input  | OBF <sub>A</sub> | INTE <sub>1</sub> | IBF <sub>A</sub> | INTE <sub>2</sub> | INTR <sub>A</sub> | INTE <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |

| 11 | Mode 2           | Mode 1<br>Output | OBF <sub>A</sub> | INTE <sub>1</sub> | IBF <sub>A</sub> | INTE <sub>2</sub> | INTR <sub>A</sub> | INTE <sub>B</sub> | OBF <sub>B</sub> | INTR <sub>B</sub> |

#### 6. Reset of MSM82C55A-2

Be sure to keep the RESET signal at power ON in the high level at least for 50  $\mu$ s. Subsequently, it becomes the input mode at a high level pulse above 500 ns.

#### Note: Comparison of MSM82C55A-5 and MSM82C55A-2

#### MSM82C55A-5

After a write command is executed to the command register, the internal latch is cleared in PORTA PORTC. For instance, 00H is output at the beginning of a write command when the output port is assigned. However, if PORTB is not cleared at this time, PORTB is unstable. In other words, PORTB only outputs ineffective data (unstable value according to the device) during the period from after a write command is executed till the first data is written to PORTB.

#### MSM82C55A-2

After a write command is executed to the command register, the internal latch is cleared in All Ports (PORTA, PORTB, PORTC). 00H is output at the beginning of a write command when the output port is assigned

#### NOTICE ON REPLACING LOW-SPEED DEVICES WITH HIGH-SPEED DEVICES

The conventional low speed devices are replaced by high-speed devices as shown below. When you want to replace your low speed devices with high-speed devices, read the replacement notice given on the next pages.

| High-speed device (New) | Low-speed device (Old) | Remarks         |

|-------------------------|------------------------|-----------------|

| M80C85AH                | M80C85A/M80C85A-2      | 8bit MPU        |

| M80C86A-10              | M80C86A/M80C86A-2      | 16bit MPU       |

| M80C88A-10              | M80C88A/M80C88A-2      | 8bit MPU        |

| M82C84A-2               | M82C84A/M82C84A-5      | Clock generator |

| M81C55-5                | M81C55                 | RAM.I/O, timer  |

| M82C37B-5               | M82C37A/M82C37A-5      | DMA controller  |

| M82C51A-2               | M82C51A                | USART           |

| M82C53-2                | M82C53-5               | Timer           |

| M82C55A-2               | M82C55A-5              | PPI             |

#### Differences between MSM82C55A-5 and MSM82C55A-2

#### 1) Manufacturing Process

These devices use a 3 µ Si-Gate CMOS process technology.

The MSM82C55A-2 is about 7% smaller in chip size than the MSM82C55A-5 as the MSM82C55A-2 changed its output characteristics.

#### 2) Function

| Item                                                    | MSM82C55A-5                                               | MSM82C55A-2            |

|---------------------------------------------------------|-----------------------------------------------------------|------------------------|

| Internal latch during writing into the command register | Only ports A and C are cleared.<br>Port B is not cleared. | All ports are cleared. |

The above function has been improved to remove bugs and other logics are not different between the two devices.

#### 3) Electrical Characteristics 3-1) DC Characteristics

| Parameter                 | Symbol | MSM82C55A-5                        | MSM82C55A-2                          |

|---------------------------|--------|------------------------------------|--------------------------------------|

| "L" Output Voltage        | Vol    | 0.45 V<br>(IoL = +2.5 mA)          | 0.40 V<br>(IoL = +2.5 mA)            |

| ''H'' Output Voltage      | Voн    | 2.4 V<br>(Іон = -400 µА)           | 3.7 V<br>(Іон = -2.5 mA)             |

| Average Operating Current | Icc    | 5 mA maximum<br>(I/O Cycle = 1 μs) | 8 mA maximum<br>(I/O Cycle = 375 ns) |

As shown above, the DC characteristics of the MSM82C55A-2 satisfies the DC characteristics of the MSM82C55A-5.

#### 3-2) AC Characteristics

| Parameter                                           | Symbol | MSM82C55A-5    | MSM82C55A-2    |

|-----------------------------------------------------|--------|----------------|----------------|

| Address Hold Time for $\overline{\text{RD}}$ Rising | tra    | 20 ns minimum  | 0 ns minimum   |

| RD Pulse Width                                      | trr    | 300 ns minimum | 100 ns minimum |

| Difined Data Output Delay Time<br>From RD Falling   | trd    | 200 ns maximum | 120 ns maximum |

| Data Floating Delay Time From RD Rising             | trf    | 100 ns maximum | 75 ns maximum  |

| RD/WR Recovery Time                                 | trv    | 850 ns minimum | 200 ns minimum |

#### **OKI** Semiconductor

| Parameter                                             | Symbol | MSM82C55A-5     | MSM82C55A-2    |

|-------------------------------------------------------|--------|-----------------|----------------|

| Address Hold Time for $\overline{\mathrm{WR}}$ Rising | twa    | 30 ns minimum   | 20 ns minimum  |

| WR Pulse Width                                        | tww    | 300 ns minimum  | 150 ns minimum |

| Data Setup Time for $\overline{\text{WR}}$ Rising     | tow    | 1000 ns minimum | 50 ns minimum  |

| Data Hold Time for $\overline{\mathrm{WR}}$ Rising    | twp    | 40 ns minimum   | 30 ns minimum  |

| Defined Data Output Time<br>From WR Rising            | twв    | 350 ns maximum  | 200 ns maximum |

| Port Data Hold Time for $\overline{\text{RD}}$ Rising | thr    | 20 ns minimum   | 10 ns minimum  |

| ACK Pulse Width                                       | tак    | 300 ns minimum  | 100 ns minimum |

| STB Pulse Width                                       | tsт    | 300 ns minimum  | 100 ns minimum |

| Port Data Hold Time for STB Falling                   | tрн    | 180 ns minimum  | 50 ns minimum  |

| ACK Falling to Defined Data Output                    | tad    | 300 ns maximum  | 150 ns maximum |

| WR Falling to OBF Falling Delay Time                  | twoв   | 650 ns maximum  | 150 ns maximum |

| ACK Falling to OBF Rising Delay Time                  | tаов   | 350 ns maximum  | 150 ns maximum |

| STB Falling to IBF Rising Delay Time                  | tsiв   | 300 ns maximum  | 150 ns maximum |

| RD Rising to IBF Falling Delay Time                   | trib   | 300 ns maximum  | 150 ns maximum |

| RD Falling to INTR Falling Delay Time                 | trit   | 400 ns maximum  | 200 ns maximum |

| STB Rising to INTR Rising Delay Time                  | tsıт   | 300 ns maximum  | 150 ns maximum |

| ACK Rising to INTR Rising Delay Time                  | tait   | 350 ns maximum  | 150 ns maximum |

| WR Falling to INTR Falling Delay Time                 | twit   | 850 ns minimum  | 250 ns maximum |

As shown above, the MSM82C55A-2 satisfies the characteristics of the MSM82C55A-5.

#### DIP40-P-600-2.54 $51.98 \pm 0.3$ 21 (40 13.7± 0.2 20 1 INDEX MARK 4.57 MAX. 5.08 MAX. 1.27 15.24 SEATING пппп пппг ннн PLANE U U U U 0.25 +0.11 0.3 MIN. 3.18 0.46 +0.13 -0.08 \@0.25@ 2.54 1.86 TYP. Package material Epoxy resin Lead frame material 42 alloy Pin treatment Solder plating Solder plate thickness $5 \,\mu m$ or more Package weight (g) 6.10 TYP.

## PACKAGE DIMENSIONS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit : mm)