# ÷2, ÷4, ÷8 Clock Generation Chip

The MC10/100EL34 is a low skew  $\div 2$ ,  $\div 4$ ,  $\div 8$  clock generation chip designed explicitly for low skew clock generation applications. The internal dividers are synchronous to each other, therefore, the common output edges are all precisely aligned. The device can be driven by either a differential or single-ended ECL or, if positive power supplies are used, PECL input signal. In addition, by using the VBB output, a sinusoidal source can be AC coupled into the device (see Interfacing section of the ECLinPSTD Data Book DL140/D). If a single-ended input is to be used, the VBB output should be connected to the CLK input and bypassed to ground via a  $0.01\mu$ F capacitor. The VBB output is designed to act as the switching reference for the input of the EL34 under single-ended input conditions, as a result, this pin can only source/sink up to 0.5mA of current.

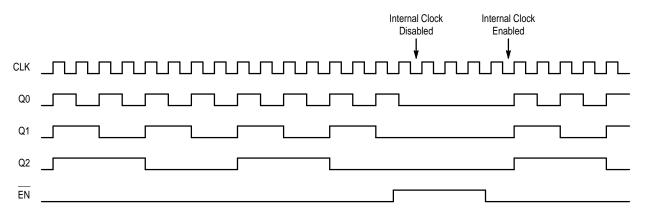

The common enable (EN) is synchronous so that the internal dividers will only be enabled/disabled when the internal clock is already in the LOW state. This avoids any chance of generating a runt clock pulse on the internal clock when the device is enabled/disabled as can happen with an asynchronous control. An internal runt pulse could lead to losing synchronization between the internal divider stages. The internal enable flip-flop is clocked on the falling edge of the input clock, therefore, all associated specification limits are referenced to the negative edge of the clock input.

Upon startup, the internal flip-flops will attain a random state; the master reset (MR) input allows for the synchronization of the internal dividers, as well as multiple EL34s in a system.

- 50ps Output-to-Output Skew

- Synchronous Enable/Disable

- Master Reset for Synchronization

- 75kΩ Internal Input Pulldown Resistors

- >1000V ESD Protection

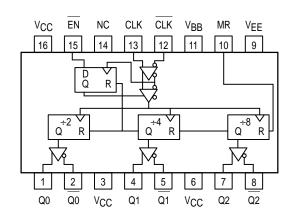

#### LOGIC DIAGRAM AND PINOUT ASSIGNMENT

## MC10EL34 MC100EL34

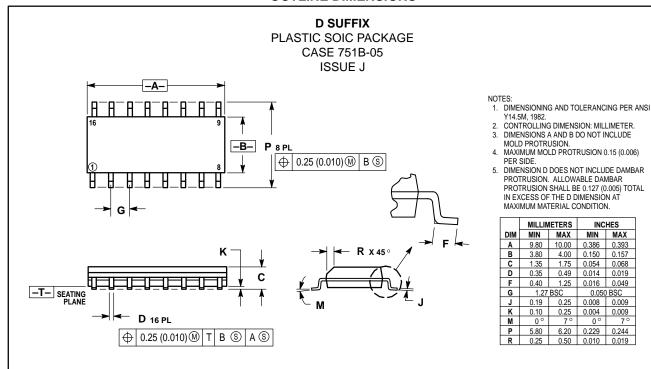

**D SUFFIX**PLASTIC SOIC PACKAGE

CASE 751B-05

#### **PIN DESCRIPTION**

| PIN | FUNCTION          |

|-----|-------------------|

| CLK | Diff Clock Inputs |

| EN  | Sync Enable       |

| MR  | Master Reset      |

| VBB | Reference Output  |

| Q0  | Diff ÷2 Outputs   |

| Q1  | Diff ÷4 Outputs   |

| Q2  | Diff ÷8 Outputs   |

#### **FUNCTION TABLE**

| CLK | EN | MR | FUNCTION               |

|-----|----|----|------------------------|

| Z   | L  | L  | Divide                 |

| ZZ  | Н  | L  | Hold Q <sub>0-3</sub>  |

| Х   | Х  | Н  | Reset Q <sub>0-3</sub> |

Z = Low-to-High Transition ZZ = High-to-Low Transition

MOTOROLA

### **AC/DC CHARACTERISTICS** ( $V_{EE} = V_{EE}(min)$ to $V_{EE}(max)$ ; $V_{CC} = GND$ )

|                                      |                                                        | –40°C             |     |                      | 0°C               |     |                      | 25°C              |     |                      | 85°C              |     |                      |      |

|--------------------------------------|--------------------------------------------------------|-------------------|-----|----------------------|-------------------|-----|----------------------|-------------------|-----|----------------------|-------------------|-----|----------------------|------|

| Symbol                               | Characteristic                                         | Min               | Тур | Max                  | Unit |

| fMAX                                 | Max Toggle Frequency                                   | 1100              |     |                      | 1100              |     |                      | 1100              |     |                      | 1100              |     |                      | MHz  |

| IEE                                  | Power Supply 10EL<br>Current 100EL                     |                   |     | 39<br>39             |                   |     | 39<br>39             |                   |     | 39<br>39             |                   |     | 39<br>42             | mA   |

| V <sub>BB</sub>                      | Output Reference 10EL<br>Voltage 100EL                 | -1.43<br>-1.38    |     | -1.30<br>-1.26       | -1.38<br>-1.38    |     | -1.27<br>-1.26       | -1.35<br>-1.38    |     | -1.25<br>-1.26       | -1.31<br>-1.38    |     | -1.19<br>-1.26       | V    |

| lн                                   | Input High Current                                     | 150               |     |                      |                   |     | 150                  |                   |     | 150                  |                   |     | 150                  | μΑ   |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation CLK→Q0<br>Delay to CLK→Q1,2<br>Output MR→Q | 960<br>900<br>750 |     | 1200<br>1140<br>1060 | 960<br>900<br>750 |     | 1200<br>1140<br>1060 | 960<br>900<br>750 |     | 1200<br>1140<br>1060 | 970<br>910<br>790 |     | 1210<br>1150<br>1090 | ps   |

| tSKEW                                | Within-Device Skew                                     |                   | 100 |                      |                   | 100 |                      |                   | 100 |                      |                   | 100 |                      | ps   |

| tS                                   | Setup Time EN                                          | 400               |     |                      | 400               |     |                      | 400               |     |                      | 400               |     |                      | ps   |

| tH                                   | Hold Time EN                                           | 250               |     |                      | 250               |     |                      | 250               |     |                      | 250               |     |                      | ps   |

| VPP                                  | Minimum Input Swing<br>CLK                             | 250               |     |                      | 250               |     |                      | 250               |     |                      | 250               |     |                      | mV   |

| VCMR                                 | Common Mode Range<br>CLK                               | -2.0              |     | -0.4                 | -2.0              |     | -0.4                 | -2.0              |     | -0.4                 | -2.0              |     | -0.4                 | V    |

| t <sub>r</sub><br>t <sub>f</sub>     | Output Rise/Fall Times Q (20% – 80%)                   | 275               |     | 525                  | 275               |     | 525                  | 275               |     | 525                  | 275               |     | 525                  | ps   |

The EN signal will freeze the internal clocks to the flip—flops on the first falling edge of CLK after its assertion. The internal dividers will maintain their state during the internal clock freeze and will return to clocking once the internal clocks are unfrozen. The outputs will transition to their next states in the same manner, time and relationship as they would have had the EN signal not been asserted.

Figure 1. Timing Diagram

MOTOROLA 3–2

INCHES

0.393

#### **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1-800-441-2447 or 602-303-5454

MFAX: RMFAX0@email.sps.mot.com - TOUCHTONE 602-244-6609 INTERNET: http://Design-NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi-SPD-JLDC, 6F Seibu-Butsuryu-Center, 3-14-2 Tatsumi Koto-Ku, Tokyo 135, Japan. 03-81-3521-8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from:

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com