# **Passive Line Termination Circuit**

Advance Information

#### **Features**

- Passive Line Termination (PLT) for MT8910 DSLIC

- High precision trimmed resistors

- Excellent resistor matching required to meet longitudinal balance as specified in ANSI-T1.601

- Compact SIL package

## **Applications**

- Pair gain system

- ISDN NT1 and NT2 interfaces

- Digital multiplexers and concentrators

- ISDN U-interface terminals

ISSUE 1 August 1991

#### **Ordering Information**

MH89101

6 Pin SIL Package

0°C to +70°C

#### **Description**

The MH89101 is a thick film hybrid device which is used in conjunction with the MT8910 to perform two to four wire conversion and analog signal conditioning on the received 2B1Q signal.

The signal conditioning is necessary to enable the DSLIC to interface to the Digital Subscriber Line as defined in ANSI T1.601-1988. The precanceller block will perform two to four wire conversion and provide adequate isolation between transmit and receive paths.

The small size and the precise resistor matching on the hybrid makes it suitable for line card or terminals which use the MT8910 2B1Q U-Interface Transceiver.

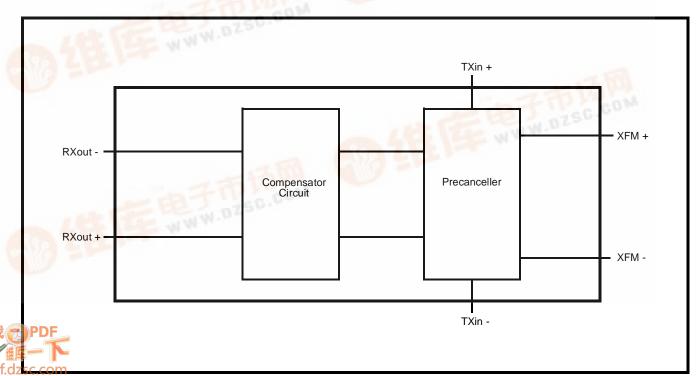

Figure 1 - Functional Block Diagram

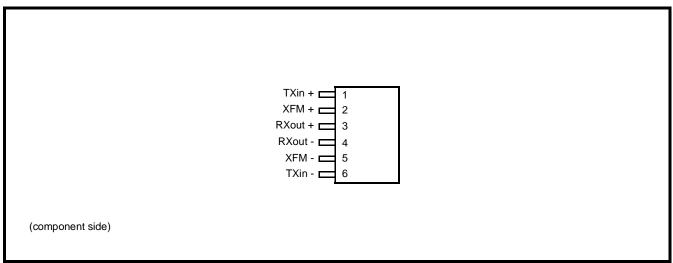

Figure 2 - Pin Connections

# **Pin Description**

| Pin # | Name                | Description                                                                                                                              |

|-------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | TX <sub>in+</sub>   | Transmit Line Signal Input. Must be connected to the L <sub>out+</sub> output of the DSLIC.                                              |

| 2     | XFM+                | <b>Transformer.</b> Node of the 2 to 4 wire converter which must be connected to the primary of the line transformer.                    |

| 3     | RX <sub>out+</sub>  | Receive Line Signal Output. Output of the compensator circuit which must be connected to the $L_{\text{in+}}$ input of the DSLIC.        |

| 4     | RX <sub>out</sub> - | <b>Receive Line Signal Output.</b> Output of the compensator circuit which must be connected to the $L_{\text{in-}}$ input of the DSLIC. |

| 5     | XFM-                | <b>Transformer.</b> Node of the 2 to 4 wire converter which must be connected to the primary of the line transformer.                    |

| 6     | TX <sub>in-</sub>   | Transmit Line Signal Input. Must be connected to the L <sub>out-</sub> output of the DSLIC.                                              |

Advance Information MH89101

### **Functional Description**

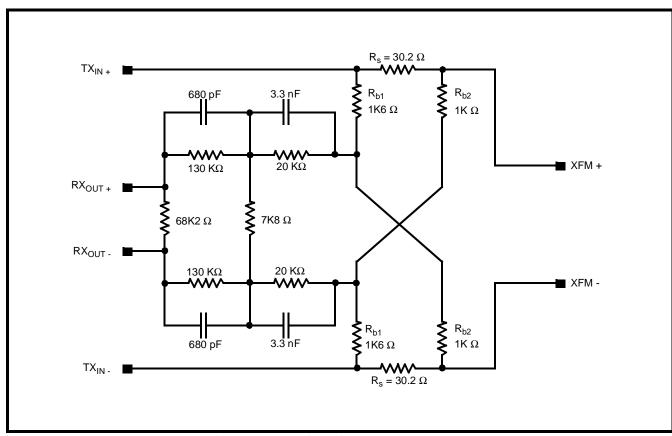

The termination network is an all passive circuit which allows the DSLIC to interface to the DSL through a pulse transformer. The equivalent circuit of the Passive Line Termination Network can be seen in Figure 3 below.

The PLT consists of two blocks which includes a hybrid network and a compensator circuit.

The hybrid network is a 2 to 4 wire converter which provides a large degree of precancellation of the near end signal while presenting little attenuation to the far end signal. This is performed using a summing junction which effectively subtracts the transmit signal from the receive path.

The compensator circuit, in conjunction with the transformer, acts as a highpass filter reducing the low frequency content in the received line signal. This, in turn, decreases the effects of ISI and near end echo, and improves the transceiver performance.

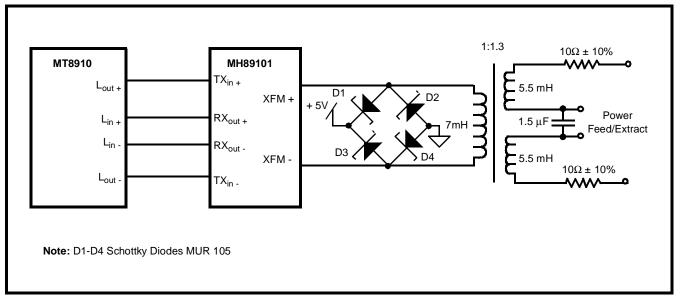

#### **Typical Application**

Figure 4 shows a typical connection diagram of the MT8910 DSLIC and the Passive Line Termination Circuit. As seen in Figure 4, the PLT is positioned between the DSLIC and the line pulse transformer. Two series protection resistors on the secondary of the line pulse transformer are used to dissipate any extraneous energy which may be induced onto the transmission line.

Figure 3 - Passive Line Termination Network

Figure 4 - Typical Connection Diagram

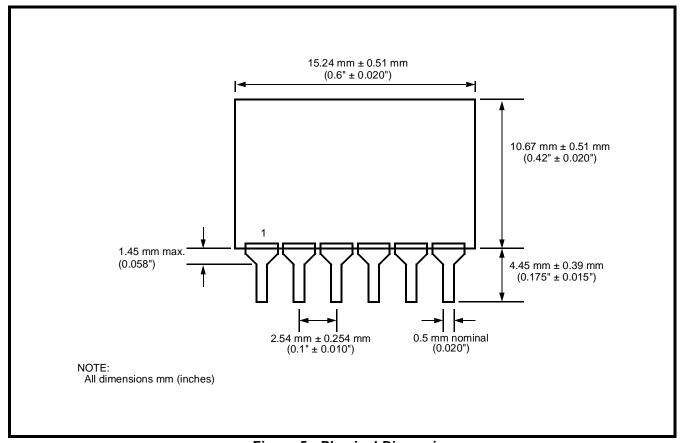

Figure 5 - Physical Dimensions