## **MIC1232**

μP Supervisory Circuit

### **Description**

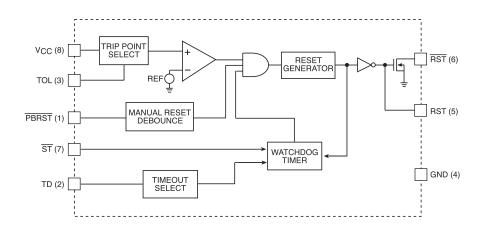

The MIC1232 is a multifunction circuit which monitors microprocessor activity, external reset and power supplies in microprocessor based systems. The circuit functions include a watchdog timer, power supply monitor, microprocessor reset, and manual pushbutton reset input.

The power supply line is monitored with a comparator and an internal voltage reference. RST is forced low when an out-of-tolerance condition exists and remains asserted for at least 250ms after V<sub>CC</sub> rises above the threshold voltage (4.5V or 4.75V). The RST pin will remain logic low with V<sub>CC</sub> as low as 1.4V.

The Watchdog input ( $\overline{ST}$ ) monitors  $\mu P$  activity and will assert  $\overline{RST}$  if no  $\mu P$  activity has occurred within the watchdog timeout period. The watchdog timeout period is selectable with nominal periods of 150, 600, or 1200 milliseconds.

## **Typical Applications**

- Automotive Systems

- Intelligent Instruments

- Critical Microprocessor Power Monitoring

- Battery Powered Computers

- Controllers

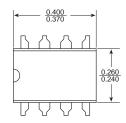

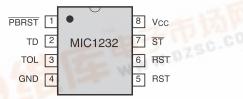

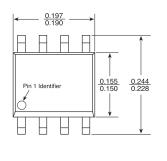

## **Pin Configuration**

Top View

MIC1232N - 8 Lead Plastic DIP Package MIC1232M - 8 Lead Plastic SOIC Package

### **Features**

- Power OK/Reset Time Delay, 250ms min.

- Watchdog Timer, 150ms, 600ms, or 1.2s typical

- Precision Supply Voltage Monitor, Select Between 5% or 10% of Supply Voltage

- Available in 8-pin Surface Mount (SO)

- Debounced External Reset Input

- Low Supply Current, < 18μA Typ.</li>

## **Ordering Information**

| _Part_   | <u>Package</u> | Temp. Range    |

|----------|----------------|----------------|

| MIC1232N | 8-Lead PDIP    | -40°C to +85°C |

| MIC1232M | 8-Lead SOIC    | -40°C to +85°C |

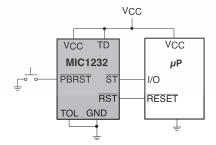

# **Typical Operating Circuit**

## **Absolute Maximum Ratings**

| Terminal Voltage     |                      |

|----------------------|----------------------|

| VCC,                 | 0.3V to 6.0V         |

| All Other Inputs     | 0.3V to (VCC + 0.3V) |

| Input Current        | , ,                  |

| Vcc                  | 250mA                |

| Gnd All Other Inputs | 25mA                 |

| Operating temperature Range            |               |

|----------------------------------------|---------------|

| MIC1232M/N                             | 40°C to 85°C  |

| MIC1232D                               | 0°C to 70°C   |

| Storage Temperature Range              | 65°C to 150°C |

| Lead Temperature (Soldering - 10 sec.) | 300°C         |

| Power Dissipation                      | 700mW         |

|                                        |               |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability. Operating ranges define those limits between which the functionality of the device is guaranteed.

### **Electrical Characteristics**

VCC = 4.5V to 5.5V,  $T_A$  = Operating Temperature Range, unless otherwise noted.

| Parameter                                                   | Conditions                          | Min         | Тур  | Max      | Units |

|-------------------------------------------------------------|-------------------------------------|-------------|------|----------|-------|

| Supply Voltage Range                                        | Vcc                                 | 4.5         |      | 5.5      | V     |

| Supply Current                                              | ICC (See Note 1)                    |             | 18   | 40       | μΑ    |

| ST and PBRST Input Levels                                   | V <sub>IH</sub> (See Note 2)<br>VIL | 2.0<br>-0.3 |      | VCC +0.3 | V     |

| Input Leakage                                               | I <sub>IL</sub>                     |             |      | ±1       | μΑ    |

| Output Source Current, RST                                  | V <sub>OH</sub> = 2.4V              | 1.0         | 10   |          | mA    |

| Output Sink Current, RST, RST                               | V <sub>OL</sub> = 0.4V              | 2.0         | 10   |          | mA    |

| V <sub>CC</sub> 5% Trip Point (Reset<br>Threshold Voltage)  | TOL = Gnd                           | 4.50        | 4.62 | 4.74     | V     |

| V <sub>CC</sub> 10% Trip Point (Reset<br>Threshold Voltage) | TOL = VCC                           | 4.25        | 4.37 | 4.49     | V     |

| Input Capacitance, ST, TOL                                  | C <sub>IN</sub> (See Note 3)        |             |      | 5        | pF    |

| Output Capacitance, RST, RST                                | COUT (See Note 3)                   |             |      | 7        | pF    |

### A.C. Electrical Characteristics

VCC = 4.5V to 5.5V,  $T_A$  = Operating Temperature Range, unless otherwise noted.

| Parameter                                                        | Conditions                           | Min                | Тур                | Max                 | Units |

|------------------------------------------------------------------|--------------------------------------|--------------------|--------------------|---------------------|-------|

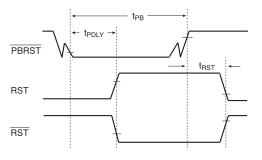

| PBRST Min. Pulse Width, tpB                                      | PBRST = V <sub>IL</sub> (see note 4) | 20                 |                    |                     | ms    |

| PBRST Delay, tPBD                                                |                                      | 1                  | 4                  | 20                  | ms    |

| Reset Active Time, tRST                                          |                                      | 250                | 610                | 1000                | ms    |

| ST Pulse Width, tST                                              |                                      | 20                 |                    |                     | ns    |

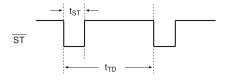

| ST Timeout Period, t <sub>TD</sub>                               | TD = 0V<br>TD = Open<br>TD = VCC     | 62.5<br>250<br>500 | 150<br>600<br>1200 | 250<br>1000<br>2000 | ms    |

| VCC Fall Time, tF                                                |                                      | 10                 |                    |                     | μs    |

| V <sub>CC</sub> Rise Time, t <sub>R</sub>                        |                                      | 0                  |                    |                     | ns    |

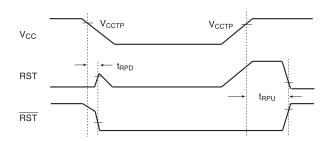

| V <sub>CC</sub> Detect to RST Low and RST High, t <sub>RPD</sub> | V <sub>CC</sub> Falling (see note 5) |                    | 50                 | 150                 | μs    |

| V <sub>CC</sub> Detect to RST Open and RST Low, t <sub>RPU</sub> | V <sub>CC</sub> Rising (see note 6)  | 250                | 610                | 1000                | ms    |

Note 1: ICC is measured with outputs open and inputs within 0.5V of supply rails.

Note 2:  $\overline{\mathsf{PBRST}}$  has an internal pull-up resistor to VCC (typ.  $40k\Omega$ ).

Note 3: Guaranteed by design.

Note 4: PBRST must be held low for a minimum of 20ms to guarantee a reset.

Note 5: VCC falling at 1.66mv/µs.

Note 6:  $\overline{\text{RST}}$  has an open drain output.

#### **Pin Functions**

- Pin 1: PBRST Pushbutton reset input. This input is debounced and can be driven with external logic signals or by means of a mechanical pushbutton to actively force a reset. All pulses less than 1ms in duration on the PBRST pin are ignored, whereas, any pulse with a duration of 20ms or greater is guaranteed to cause a reset.

- Pin 2: **TD** Time delay input. This input selects the timebase used by the watchdog timer. When TD = 0V, the watchdog timeout period is set to a nominal value of 150ms, when TD = open, the watchdog timeout period is set to a nominal value of 600ms and when TD = V<sub>CC</sub>, the watchdog timeout period is 1.2sec nominally.

- Pin 3: **TOL** Tolerance select input. Selects whether 5% or 10% of V<sub>CC</sub> is used as the reset threshold voltage. When TOL = 0V, the 5% tolerance level is selected and when TOL = V<sub>CC</sub>, a 10% tolerance level is selected.

- Pin 4: **GND** IC ground pin, 0V reference.

- Pin 5: **RST** RST is asserted high if either V<sub>CC</sub> goes below the reset threshold, the watchdog times out or PBRST is pulled low for a minimum of 20ms. RST remains asserted for one reset timeout period after V<sub>CC</sub> exceeds the reset threshold or after the watchdog times out or after PBRST goes high.

- Pin 6: RST RST is asserted low if either VCC goes below the reset threshold, the watchdog times out or PBRST is pulled low for a minimum of 20ms. RST remains asserted for one reset timeout period after VCC exceeds the reset threshold or after the watchdog times out or after PBRST goes high. Open-drain output.

- Pin 7: ST Input to the watchdog timer. If ST does not see a transition from high to low within the watchdog timeout period, RST and RST will be asserted.

- Pin 8: Vcc Primary supply input, +5V.

## **Block Diagram**

## **Circuit Description**

| TD Pin                  | Min.   | t <sub>TD</sub><br>Typ. | Max.   |

|-------------------------|--------|-------------------------|--------|

| Gnd                     | 62.5ms | 150ms                   | 250ms  |

| Open                    | 250ms  | 600ms                   | 1000ms |

| Open<br>V <sub>CC</sub> | 500ms  | 1200ms                  | 2000ms |

**Table 1. Watchdog Timeout Period**

## **Circuit Description**

#### **Power Monitor**

The RST and RST pins are asserted whenever VCC falls below the reset threshold voltage as determined by the TOL pin. A 5% tolerance level (4.62V reset threshold voltage) can be selected by connecting the TOL pin to ground and a 10% tolerance (4.37V reset threshold voltage) can be selected by connecting the TOL pin to VCC. The reset pins will remain asserted for a period of 250ms after VCC has risen above the reset threshold voltage. The reset function ensures the microprocessor is properly reset and powers up into a known condition after a power failure. RST will remain valid with VCC as low as 1.4V.

Figure 1. Power-Up/Power-Down Sequence

Note: The maximum time between high-to-low transitions (t<sub>TD</sub>) on the watchdog input (ST) is determined by the voltage applied to the TD pin. If the watchdog input sees a high-to-low transition prior to the timeout period, the watchdog timer will be reset.

Figure 2. Watchdog Input

#### **Watchdog Timer**

The microprocessor can be monitored by connecting the  $\overline{ST}$  pin (watchdog input) to a bus line or I/O line. If a high-to-low transition doesn't occur on the  $\overline{ST}$  pin within the watchdog timeout period (determined by TD pin, see Table 1), the  $\overline{RST}$  and RST pins will be asserted resulting in a microprocessor reset.  $\overline{RST}$  and RST will remain asserted for 250ms when this occurs. A minimum pulse of 75ns or any transition high-to-low on the  $\overline{ST}$  pin will reset the watchdog timer. The watchdog timer will be reset if  $\overline{ST}$  sees a valid transition within the watchdog timeout period.

#### **Pushbutton Reset Input**

The PBRST input can be driven with a manual pushbutton switch or with external logic signals. The input is internally debounced and requires an active low signal to force the reset outputs into their active states. The PBRST input will recognize any pulse that is 20ms in duration or greater and will ignore all pulses that are less than 1ms in duration.

Figure 3. Pushbutton Reset

# **Alternate Source Cross Reference Guide**

|              | MIC Direct  |

|--------------|-------------|

| Industry P/N | Replacement |

| DS1232LP     | MIC1232N    |

| DS1232LPS-2  | MIC1232M    |

| DS1232       | MIC1232N    |

| DS1232LPN    | MIC1232N    |

| DS1232LPSN-2 | MIC1232M    |

| DS1232N      | MIC1232N    |

| MAX1232CPA   | MIC1232N    |

| MAX1232CSA   | MIC1232M    |

| MAX1232EPA   | MIC1232N    |

| MAX1232ESA   | MIC1232M    |

| MAX1232C/D   | MIC1232D    |

# **Packaging Information**

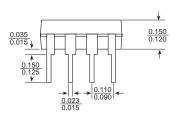

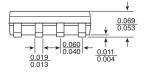

### M Package, 8-Pin Small Outline

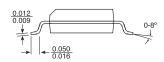

#### N Package, 8-Pin Plastic Dual-In-Line