# MIC5821/5822

### 8-Bit Serial-Input Latched Drivers

### Final Information

## **General Description**

BiCMOS technology gives the MIC5821/5822 family flexibility beyond the reach of standard logic buffers and power driver arrays. These devices each have an eight-bit CMOS shift register, CMOS control circuitry, eight CMOS data latches, and eight bipolar current-sink Darlington output drivers. The 500mA outputs are suitable for use with incandescent bulbs and other moderate to high current loads. The drivers can be operated with a split supply where the negative supply is down to -20V. Except for maximum driver output voltage ratings, the MIC5821 and MIC5822 are identical.

These devices have greatly improved data-input rates. With a 5V logic supply they will typically operate faster than 5 MHz. With a 12V supply significantly higher speeds are obtained. The CMOS inputs are compatible with standard CMOS, PMOS, and NMOS logic levels. TTL and DTL circuits may require the use of appropriate pull-up resistors. By using the serial data output, the drivers can be cascaded for interface applications requiring additional drive lines.

### Features

- 3.3 MHz Minimum Data-Input Rate

- CMOS, PMOS, NMOS, TTL Compatible

- Internal Pull-Down or Pull-Up Resistors

- Low-Power CMOS Logic and Latches

- High-Voltage Current-Sink Outputs

- Single or Split Supply Operation

## **Ordering Information**

| Part Number | Temperature Range                 | Package            |  |

|-------------|-----------------------------------|--------------------|--|

| MIC5821BN   | -40°C to +85°C 16-Pin Plastic DIP |                    |  |

| MIC5822BN   | –40°C to +85°C                    | 16-Pin Plastic DIP |  |

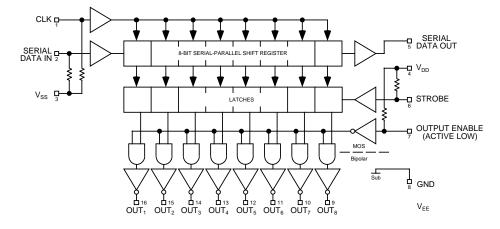

## **Functional Diagram**

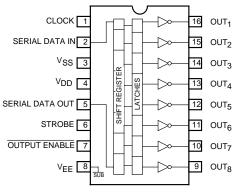

## **Pin Configuration**

#### (Plastic DIP)

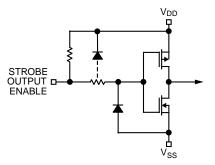

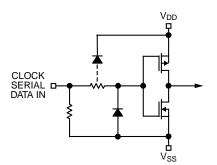

# **Typical Input Circuits**

# Absolute Maximum Ratings (Note 1)

at 25°C Free-Air Temperature and  $V_{SS} = 0V$

| Output Voltage, V <sub>CE</sub>   | (MIC5821)                     | 50V        |

|-----------------------------------|-------------------------------|------------|

|                                   | (MIC5822)                     | 80V        |

| Output Voltage, VCE SUS           | (MIC5821)(No                  | ote 3) 35V |

|                                   | (MIC5822)(No                  | ote 3) 50V |

| Logic Supply Voltage, VDI         | C                             | 15V        |

| Input Voltage Range, VIN          | .3V to V <sub>DD</sub> + 0.3V |            |

| V <sub>DD</sub> – V <sub>EE</sub> |                               | 25V        |

| Emitter Supply Voltage, V         | –20V                          |            |

| Continuous Output Curren          | 500mA                         |            |

| Package Power Dissipatio          | 1.67W                         |            |

| Operating Temperature Ra          | –55°C to +85°C                |            |

| Storage Temperature Ran           | –65°C to +150°C               |            |

- Note 1: Derate at the rate of 16.7mW/°C above  $T_A = 25^{\circ}C$ .

- Note 2: CMOS devices have input static protection but are susceptible to damage when exposed to extremely high static electrical charges.

Note 3: For inductive load applications.

Note 4: Specification for packaged product only.

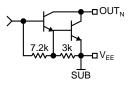

# **Typical Output Driver**

# Maximum Allowable Duty Cycle (Plastic DIP)

| Number of Outputs ON<br>(I <sub>OUT</sub> = 200mA | Maximum Allowable Duty Cycle at Ambient Temperature of |      |      |      |      |  |  |  |  |  |

|---------------------------------------------------|--------------------------------------------------------|------|------|------|------|--|--|--|--|--|

| V <sub>DD</sub> = 12V)                            | 25°C                                                   | 40°C | 50°C | 60°C | 70°C |  |  |  |  |  |

| 8                                                 | 73%                                                    | 62%  | 55%  | 47%  | 40%  |  |  |  |  |  |

| 7                                                 | 83%                                                    | 71%  | 62%  | 54%  | 46%  |  |  |  |  |  |

| 6                                                 | 97%                                                    | 82%  | 72%  | 63%  | 53%  |  |  |  |  |  |

| 5                                                 | 100%                                                   | 98%  | 87%  | 75%  | 63%  |  |  |  |  |  |

| 4                                                 | 100%                                                   | 100% | 100% | 93%  | 79%  |  |  |  |  |  |

| 3                                                 | 100%                                                   | 100% | 100% | 100% | 100% |  |  |  |  |  |

| 2                                                 | 100%                                                   | 100% | 100% | 100% | 100% |  |  |  |  |  |

| 1                                                 | 100%                                                   | 100% | 100% | 100% | 100% |  |  |  |  |  |

# MIC5821/5822 Electrical Characteristics (Note 4) at T<sub>A</sub> = 25°C V<sub>DD</sub> = 5V, V<sub>EE</sub> = V<sub>SS</sub> = 0V (unless otherwise specified)

|                        |                      | Applicable |                                                             | Limits |      |      |  |

|------------------------|----------------------|------------|-------------------------------------------------------------|--------|------|------|--|

| Characteristic         | Symbol               | Devices    | Test Conditions                                             | Min.   | Max. | Unit |  |

| Output Leakage Current | ICEX                 | MIC5821    | $V_{OUT} = 50V$                                             |        | 50   | μA   |  |

|                        |                      |            | $V_{OUT} = 50V, T_A = +70^{\circ}C$                         |        | 100  |      |  |

|                        |                      | MIC5822    | $V_{OUT} = 80V$                                             |        | 50   |      |  |

|                        |                      |            | V <sub>OUT</sub> = 80V, T <sub>A</sub> = +70°C              |        | 100  |      |  |

| Collector-Emitter      | V <sub>CE(SAT)</sub> | Both       | I <sub>OUT</sub> = 100mA                                    |        | 1.1  | V    |  |

| Saturation Voltage     |                      |            | I <sub>OUT</sub> = 200mA                                    |        | 1.3  |      |  |

|                        |                      |            | I <sub>OUT</sub> = 350mA, V <sub>DD</sub> = 7.0V            |        | 1.6  |      |  |

| Input Voltage          | V <sub>IN(0)</sub>   | Both       |                                                             |        | 0.8  | V    |  |

|                        | V <sub>IN(1)</sub>   | Both       | $V_{DD} = 12V$                                              | 10.5   |      |      |  |

|                        |                      |            | V <sub>DD</sub> = 10V                                       | 8.5    |      |      |  |

|                        |                      |            | V <sub>DD</sub> = 5.0V                                      | 3.5    |      |      |  |

| Input Resistance       | R <sub>IN</sub>      | Both       | $V_{DD} = 12V$                                              | 50     |      | kΩ   |  |

|                        |                      |            | $V_{DD} = 10V$                                              | 50     |      |      |  |

|                        |                      |            | $V_{DD} = 5.0 V$                                            | 50     |      |      |  |

| Supply Current         | I <sub>DD(ON)</sub>  | Both       | One Driver ON, V <sub>DD</sub> = 12V                        |        | 4.5  | mA   |  |

|                        |                      |            | One Driver ON, V <sub>DD</sub> = 10V                        |        | 3.9  |      |  |

|                        |                      |            | One Driver ON, V <sub>DD</sub> = 5.0V                       |        | 2.4  |      |  |

|                        |                      |            | All Drivers ON, V <sub>DD</sub> = 12V                       |        | 16   |      |  |

|                        |                      |            | All Drivers ON, V <sub>DD</sub> = 10V                       |        | 14   |      |  |

|                        |                      |            | All Drivers ON, $V_{DD} = 5.0V$                             |        | 8    |      |  |

|                        | IDD(OFF)             | Both       | All Drivers OFF, V <sub>DD</sub> = 5.0V,<br>All Inputs = 0V |        | 1.6  |      |  |

|                        |                      |            | All Drivers OFF, V <sub>DD</sub> = 12V,<br>All Inputs= 0V   |        | 2.9  |      |  |

# **Electrical Characteristics (Note 4)** $T_A = -55^{\circ}C$ , $V_{DD} = 5V$ , $V_{SS} = V_{EE} = 0V$ (unless otherwise noted)

|                        |                      |                                                  | Limits |      |      |  |  |

|------------------------|----------------------|--------------------------------------------------|--------|------|------|--|--|

| Characteristic         | Symbol               | Test Conditions                                  | Min.   | Max. | Unit |  |  |

| Output Leakage Current | ICEX                 | V <sub>OUT</sub> = 80V                           |        | 50   | μΑ   |  |  |

| Collector-Emitter      | V <sub>CE(SAT)</sub> | I <sub>OUT</sub> = 100mA                         |        | 1.3  | V    |  |  |

| Saturation Voltage     |                      | I <sub>OUT</sub> = 200mA                         |        | 1.5  |      |  |  |

|                        |                      | I <sub>OUT</sub> = 350mA, V <sub>DD</sub> = 7.0V |        | 1.8  |      |  |  |

| Input Voltage          | V <sub>IN0)</sub>    |                                                  |        | 0.8  | V    |  |  |

|                        | V <sub>IN(1)</sub>   | V <sub>DD</sub> = 12V                            | 10.5   |      |      |  |  |

|                        |                      | $V_{DD} = 5.0 V$                                 | 3.5    |      |      |  |  |

| Input Resistance       | RIN                  | V <sub>DD</sub> = 12V                            | 35     |      | kΩ   |  |  |

|                        |                      | V <sub>DD</sub> = 10V                            | 35     |      |      |  |  |

|                        |                      | $V_{DD} = 5.0 V$                                 | 35     |      |      |  |  |

| Supply Current         | I <sub>DD(ON)</sub>  | One Driver ON, V <sub>DD</sub> = 12V             |        | 5.5  | mA   |  |  |

|                        |                      | One Driver ON, V <sub>DD</sub> = 10V             |        | 4.5  |      |  |  |

|                        |                      | One Driver ON, $V_{DD} = 5.0V$                   |        | 3.0  |      |  |  |

|                        |                      | All Drivers ON, V <sub>DD</sub> = 12V            |        | 16   |      |  |  |

|                        |                      | All Drivers ON, V <sub>DD</sub> = 10V            |        | 14   |      |  |  |

|                        |                      | All Drivers ON, $V_{DD} = 5.0V$                  |        | 10   |      |  |  |

|                        | IDD(OFF)             | All Drivers OFF, V <sub>DD</sub> = 12V           |        | 3.5  | ]    |  |  |

|                        |                      | All Drivers OFF, V <sub>DD</sub> = 5.0V          |        | 2.0  |      |  |  |

|                        |                      |                                                  | Limits |      |      |  |  |

|------------------------|----------------------|--------------------------------------------------|--------|------|------|--|--|

| Characteristic         | Symbol               | Test Conditions                                  | Min.   | Max. | Unit |  |  |

| Output Leakage Current | ICEX                 | $V_{OUT} = 80V$                                  |        | 500  | μΑ   |  |  |

| Collector-Emitter      | V <sub>CE(SAT)</sub> | I <sub>OUT</sub> = 100mA                         |        | 1.3  | V    |  |  |

| Saturation Voltage     |                      | I <sub>OUT</sub> = 200mA                         |        | 1.5  |      |  |  |

|                        |                      | I <sub>OUT</sub> = 350mA, V <sub>DD</sub> = 7.0V |        | 1.8  |      |  |  |

| Input Voltage          | V <sub>IN(0)</sub>   |                                                  |        | 0.8  | V    |  |  |

|                        | V <sub>IN(1)</sub>   | V <sub>DD</sub> = 12V                            | 10.5   |      |      |  |  |

|                        |                      | $V_{DD} = 5.0 V$                                 | 3.5    |      |      |  |  |

| Input Resistance       | R <sub>IN</sub>      | V <sub>DD</sub> = 12V                            | 50     |      | kΩ   |  |  |

|                        |                      | V <sub>DD</sub> = 10V                            | 50     |      |      |  |  |

|                        |                      | $V_{DD} = 5.0 V$                                 | 50     |      |      |  |  |

| Supply Current         | I <sub>DD(ON)</sub>  | One Driver ON, V <sub>DD</sub> = 12V             |        | 4.5  | mA   |  |  |

|                        |                      | One Driver ON, V <sub>DD</sub> = 10V             |        | 3.9  |      |  |  |

|                        |                      | One Driver ON, V <sub>DD</sub> = 5.0V            |        | 2.4  |      |  |  |

|                        |                      | All Drivers ON, V <sub>DD</sub> = 12V            |        | 16   |      |  |  |

|                        |                      | All Drivers ON, V <sub>DD</sub> = 10V            |        | 14   |      |  |  |

|                        |                      | All Drivers ON, $V_{DD} = 5.0V$                  |        | 8    | ]    |  |  |

|                        | IDD(OFF)             | All Drivers OFF, V <sub>DD</sub> = 12V           |        | 2.9  | ]    |  |  |

|                        |                      | All Drivers OFF, V <sub>DD</sub> = 5.0V          |        | 1.6  | ]    |  |  |

# MIC5821/5822 Electrical Characteristics (Note 4) T<sub>A</sub> = +125°C, V<sub>DD</sub> = 5V, V<sub>SS</sub> = V<sub>EE</sub> = 0V (unless otherwise noted)

## MIC5821/5822 Family Truth Table

| Serial        |                | Shi            | ft Reg         | jister Co      | ntents         | Serial         | Latch Contents  |                |                |                |                    | Outpu            | ıt Co          | ntents         | 5              |  |                |

|---------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|----------------|--------------------|------------------|----------------|----------------|----------------|--|----------------|

| Data<br>Input | Clock<br>Input | I <sub>1</sub> | l <sub>2</sub> | l <sub>3</sub> | I <sub>8</sub> | Data<br>Output | Strobe<br>Input | 11             | l <sub>2</sub> | l <sub>3</sub> | <br>I <sub>8</sub> | Output<br>Enable | I <sub>1</sub> | l <sub>2</sub> | l <sub>3</sub> |  | I <sub>8</sub> |

| н             |                | Н              | R <sub>1</sub> | R <sub>2</sub> | R <sub>7</sub> | R <sub>7</sub> |                 |                |                |                |                    |                  |                |                |                |  |                |

| L             |                | L              | R <sub>1</sub> | R <sub>2</sub> | R <sub>7</sub> | R <sub>7</sub> | 1               |                |                |                |                    |                  |                |                |                |  |                |

| Х             |                | R <sub>1</sub> | $R_2$          | R <sub>3</sub> | R <sub>8</sub> | R <sub>8</sub> |                 |                |                |                |                    |                  |                |                |                |  |                |

|               |                | Х              | Х              | Х              | X              | Х              | L               | R <sub>1</sub> | $R_2$          | $R_3$          | <br>R <sub>8</sub> |                  |                |                |                |  |                |

|               |                | P <sub>1</sub> | $P_2$          | P <sub>3</sub> | P <sub>8</sub> | P <sub>8</sub> | Н               | P <sub>1</sub> | $P_2$          | $P_3$          | <br>P <sub>8</sub> | L                | Р <sub>1</sub> | $P_2$          | $P_3$          |  | P8             |

|               |                |                |                |                |                |                |                 | Х              | Х              | Х              | <br>Х              | Н                | Н              | Н              | Н              |  | Н              |

L = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous State

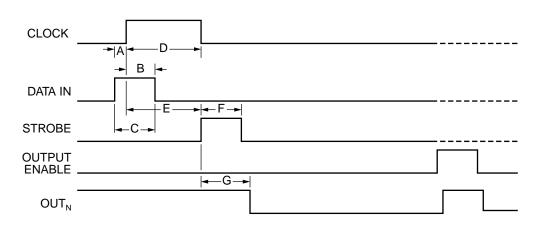

# **Timing Diagram**

# **Timing Conditions**

$(T_A = +25^{\circ}C, \text{ Logic Levels are } V_{DD} \text{ and } V_{SS})$

#### $V_{DD} = 5.0V$

| A. Minimum Data Active Time Before Clock Pulse (Data Set-Up Time) | 75 ns  |

|-------------------------------------------------------------------|--------|

| B. Minimum Data Active Time After Clock Pulse (Data Hold Time)    |        |

| C. Minimum Data Pulse Width                                       | 150 ns |

| D. Minimum Clock Pulse Width                                      | 150 ns |

| E. Minimum Time Between Clock Activation and Strobe               |        |

| F. Minimum Strobe Pulse Width                                     | 100 ns |

| G. Typical Time Between Strobe Activation and Output Transition   | 500 ns |

SERIAL DATA present at the input is transferred to the shift register on the logic "0" to logic "1" transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.

Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the ENABLE input be high during serial entry.

When the ENABLE input is high, all of the output buffers are disabled (OFF) without affecting the information stored in the latches or shift register. With the ENABLE input low, the outputs are controlled by the state of the latches.

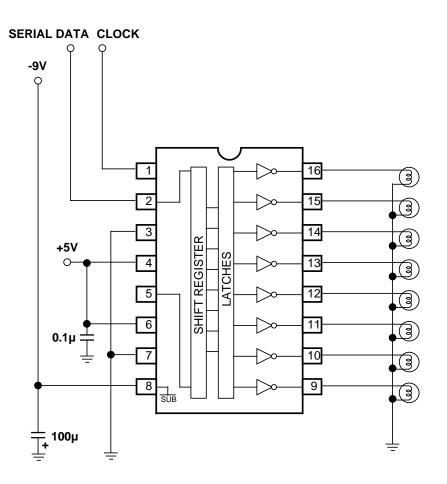

## **Typical Applications**

### MIC5822 Level Shifting Lamp Driver with Darlington Emitters Tied to a Negative Supply

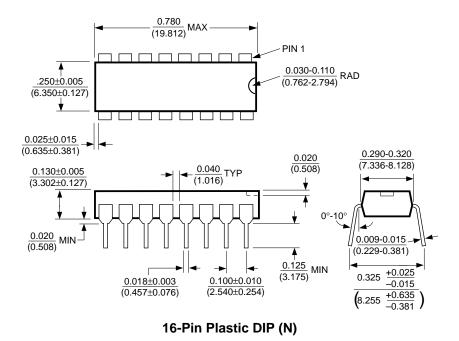

# **Package Information**

7

## MICREL INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 1998 Micrel Incorporated