# ML6429

## 75Ω Quad Video Cable Drivers and Filters with Switchable Inputs

### **GENERAL DESCRIPTION**

The ML6429 is a quad 4<sup>th</sup>-order Butterworth lowpass reconstruction filter plus quad video amplifier optimized for minimum overshoot and flat group delay. Each filter channel has a two-input multiplexer that switches between two groups of quad video signals. Applications driving SCART and EVC cables are supported for composite, component, and RGB video.

$1V_{P-P}$  input signals from DACs are AC coupled into the ML6429, where they are DC restored. Outputs are AC coupled, and drive  $2V_{P-P}$  into a 150 $\Omega$  load. The ML6429 can be used with DC coupled outputs for certain applications.

A fifth unfiltered channel is provided to support an additional analog composite video input. A swapping multiplexer between the two composite channels allows the distribution amplifiers to output from either input.

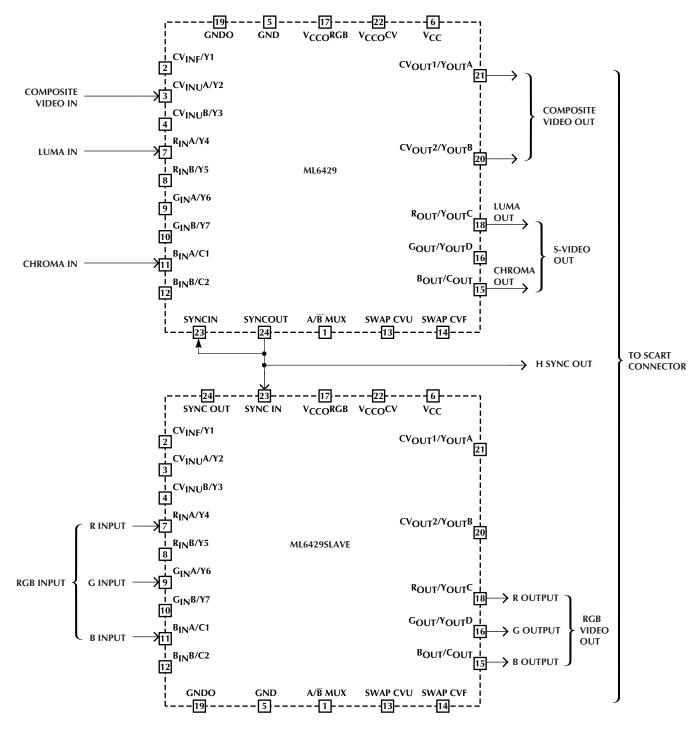

Several ML6429s can be arranged in a master-slave configuration where an external sync can be used for CV and RGB outputs.

### FEATURES

- Cable drivers for Peritel (SCART), Enhanced Video Connector (EVC), and standard video connectors, 75Ω cable drivers for CV, S-video, and RGB

- 7.1MHz cutoffs CV, RGB, and S-video, NTSC or PAL filters with mux inputs and output channel mux

- 7.1MHz to 8.4MHz cutoffs achievable with peaking capacitor

- Quad 4<sup>th</sup>-order reconstruction or dual anti-aliasing filter

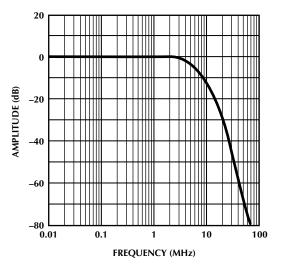

- 41dB stopband attenuation at 27MHz, 0.5dB flatness up to 4.5MHz

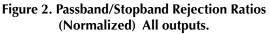

- 12ns group delay flatness up to 10MHz

- 0.4% differential gain, 0.4° differential phase on all channels, 0.4% total harmonic distortion on all channels

- 2kV ESD guaranteed

- Master-slave configuration allows up to 8 multiplexed, filtered output signals

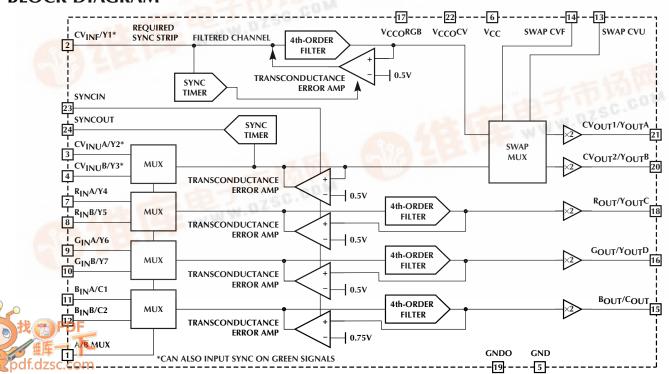

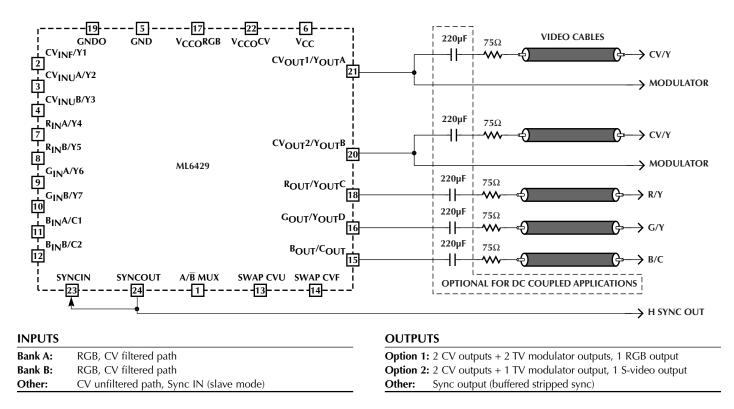

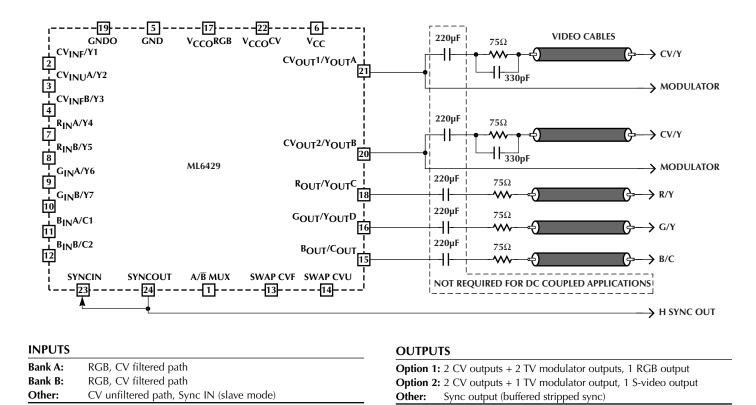

### **BLOCK DIAGRAM**

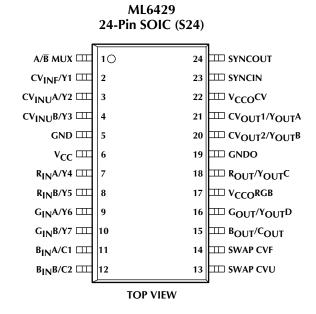

### PIN CONFIGURATION

#### PIN DESCRIPTION PIN FUNCTION

| PIN | NAME                   | FUNCTION                                                                                                                                                                                                                                                                                                      | PIN | NAME                   | FUNCTION                                                                                                                                                                                                                       |

|-----|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | A∕ <b>B</b> MU X       | Logic input pin to select between Bank<br><a> or <b> of the CV, RGB, or Y/C</b></a>                                                                                                                                                                                                                           | 5   | GND                    | Analog ground                                                                                                                                                                                                                  |

|     |                        | inputs. Internally pulled high.                                                                                                                                                                                                                                                                               | 6   | $V_{CC}$               | Analog 5V supply                                                                                                                                                                                                               |

| 2   | CV <sub>INF</sub> /Y1  | Filtered analog composite video or<br>luma video input.                                                                                                                                                                                                                                                       | 7   | R <sub>IN</sub> A/Y4   | Filtered analog RED video or luma<br>video input for Bank <a></a>                                                                                                                                                              |

| 3   | CV <sub>INU</sub> A/Y2 | Unfiltered analog composite video or<br>luma video input for Bank <a>.<br/>A composite or luma or green signal</a>                                                                                                                                                                                            | 8   | R <sub>IN</sub> B / Y5 | Filtered analog RED video or luma<br>video input for Bank <b></b>                                                                                                                                                              |

|     |                        | must be present on $CV_{INU}A/Y2$ or $CV_{INU}B/Y3$ inputs to provide necessary sync signals to other                                                                                                                                                                                                         | 9   | G <sub>IN</sub> A/Y6   | Filtered analog GREEN video or<br>luma video input for Bank <a></a>                                                                                                                                                            |

|     |                        | channels (R,G,B,Y,C). Otherwise, sync<br>must be provided at SYNCIN. For RGB<br>applications, the green channel with                                                                                                                                                                                          | 10  | G <sub>IN</sub> B/Y7   | Filtered analog GREEN video or<br>luma video input for Bank <b></b>                                                                                                                                                            |

|     |                        | sync can be used as an input to this<br>pin. (see RGB Applications section)                                                                                                                                                                                                                                   | 11  | B <sub>IN</sub> A/C1   | Filtered analog BLUE video or<br>chroma video input for Bank <a></a>                                                                                                                                                           |

| 4   | CV <sub>INU</sub> B/Y3 | Unfiltered analog composite video or<br>luma video input input for Bank <b>.<br/>A composite or luma or green signal</b>                                                                                                                                                                                      | 12  | B <sub>IN</sub> B/C2   | Filtered analog BLUE video or<br>chroma video input for Bank <b></b>                                                                                                                                                           |

|     |                        | must be present on CV <sub>INU</sub> A/Y2 or CV <sub>INU</sub> B/Y3 inputs to provide necessary sync signals to other channels (R,G,B,Y,C). Otherwise, sync must be provided at SYNCIN. For RGB applications, the green channel with sync can be used as an input to this pin. (see RGB Applications section) | 13  | SWAP CVU               | Logic input pin to select whether<br>the outputs of CV <sub>OUT</sub> 1/Y <sub>OUT</sub> A and<br>CV <sub>OUT</sub> 2/Y <sub>OUT</sub> B are from filtered<br>or unfiltered CV sources. See Table<br>1. Internally pulled low. |

|     |                        |                                                                                                                                                                                                                                                                                                               | 14  | SWAP CVF               | Logic input pin to select whether<br>the outputs of CV <sub>OUT</sub> 1/Y <sub>OUT</sub> A and<br>CV <sub>OUT</sub> 2/Y <sub>OUT</sub> B are from filtered<br>or unfiltered CV sources. See Table<br>1. Internally pulled low. |

### **PIN DESCRIPTION**

| PIN | NAME                                 | FUNCTION                                                                                                 | PIN | NAME                                   | FUNCTION                                                                                                                   |

|-----|--------------------------------------|----------------------------------------------------------------------------------------------------------|-----|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 15  | B <sub>OUT</sub> /C <sub>OUT</sub>   | Analog BLUE video output or chroma<br>output from either B <sub>IN</sub> A/C1 or B <sub>IN</sub> B/C2    | 21  | CV <sub>OUT</sub> 1/Y <sub>OUT</sub> A | Composite video output for channel 1 or luma output.                                                                       |

| 16  | G <sub>OUT</sub> /Y <sub>OUT</sub> D | Analog GREEN video output or luma<br>output from either G <sub>IN</sub> A/Y6 or G <sub>IN</sub> B/<br>Y7 | 22  | V <sub>CCO</sub> CV                    | 5V power supply for output buffers of the CV drivers.                                                                      |

| 17  | V <sub>CCO</sub> RGB                 | 5V power supply for output buffers of the RGB drivers                                                    | 23  | SYNCIN                                 | Input for an external H-sync logic<br>signal for CVU and RGB channels.<br>TTL or CMOS. For normal<br>operation, SYNCOUT is |

| 18  | R <sub>OUT</sub> /Y <sub>OUT</sub> C | Analog RED video output or luma<br>output from either R <sub>IN</sub> A/Y4 or R <sub>IN</sub> B/Y5       |     |                                        | connected to SYNCIN.                                                                                                       |

| 19  | GNDO                                 | Ground for output buffers                                                                                | 24  | SYNCOUT                                | Logic output for H-sync detect for<br>CV <sub>INU</sub> A/Y2 or CV <sub>INU</sub> B/Y3. TTL or<br>CMOS. For particip       |

| 20  | CV <sub>OUT</sub> 2/Y <sub>OUT</sub> | B Composite video output for channel 2 or luma output.                                                   |     |                                        | CMOS. For normal operation,<br>SYNCOUT is connected to<br>SYNCIN.                                                          |

### ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

| V <sub>CC</sub>      | 6V |

|----------------------|----|

| Junction Temperature |    |

| ÉSD                  |    |

### **OPERATING CONDITIONS**

| Temperature Range     |  |

|-----------------------|--|

| V <sub>CC</sub> Range |  |

### **ELECTRICAL CHARACTERISTICS**

| Unless otherwise specified, $V_{CC} = 5V \pm 10\%$ , $T_A = Operating Temperature Range (Note 1)$ |

|---------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------|

| SYMBOL             | PARAMETER                                                           | CONDITIONS                                                                                      | MIN  | <b>TYP</b><br>90 | MAX  | UNITSmA           |

|--------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------------------|------|-------------------|

| I <sub>CC</sub>    | Supply Current                                                      | No Load (V <sub>CC</sub> = 5V)                                                                  |      |                  |      |                   |

| A <sub>V</sub>     | Low Frequency Gain (All Channels)                                   | V <sub>IN</sub> = 100mV <sub>P-P</sub> at 300kHz                                                | 5.34 | 6.0              | 6.65 | dB                |

| V <sub>SYNC</sub>  | Channel Sync Output Level CV/Y, R/Y, G/Y                            | Sync Present and Clamp Settled                                                                  | 0.7  | 0.9              | 1.1  | V                 |

|                    | B/C                                                                 | Sync Present and Clamp Settled                                                                  | 1.2  | 1.4              | 1.5  | V                 |

|                    | Unfiltered                                                          | Sync Present and Clamp Settled                                                                  | 0.8  | 1.0              | 1.2  | V                 |

| t <sub>CLAMP</sub> | Clamp Response Time                                                 | Settled to Within 10mV, C <sub>IN</sub> =0.1µF                                                  |      | 10               |      | ms                |

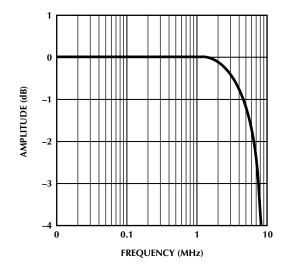

| f <sub>0.5dB</sub> | 0.5dB Bandwidth<br>(Flatness. All Filtered Channels)                | All Outputs                                                                                     |      | 4.5              |      | MHz               |

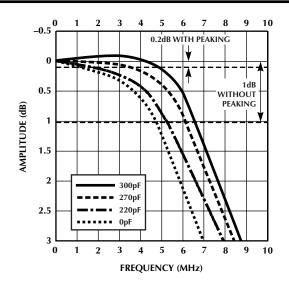

| $f_{C}$            | –3dB Bandwidth<br>(Flatness. All Filtered Channels)                 | All Outputs (with no Peaking Cap.<br>See Figures 1 and 12)                                      | 6.8  | 7.1              |      | MHz               |

| 0.8f <sub>C</sub>  | 0.8 x f <sub>C</sub> Attenuation, All Filtered Channels All Outputs |                                                                                                 |      | 1.5              |      | dB                |

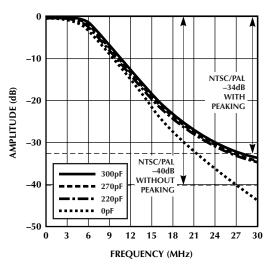

| f <sub>SB</sub>    | Stopband Rejection                                                  | All Filtered Channels<br>f <sub>IN</sub> = 27MHz to 100MHz worst case<br>(See Figures 2 and 13) | -35  | -41              |      | dB                |

| Vi                 | Input Signal Dynamic Range (All Channels)                           | AC Coupled                                                                                      | 1.25 | 1.35             |      | V <sub>P-P</sub>  |

| NOISE              | Output Noise (All Channels)                                         | Over a Frequency Band<br>of 25Hz-50MHz                                                          |      | 1                |      | mV <sub>RMS</sub> |

| OS                 | Peak Overshoot (All Channels)                                       | 2V <sub>P-P</sub> Output Pulse                                                                  |      | 4.3              |      | %                 |

| I <sub>SC</sub>    | Output Short Circuit Current (All Channels)                         | Note 2                                                                                          |      | 120              |      | mA                |

| CL                 | Output Shunt Capacitance (All Channels)                             | Load at the Output Pin                                                                          |      |                  | 35   | pF                |

| dG                 | Differential Gain (All Channels)                                    | All Outputs                                                                                     |      | 0.4              |      | %                 |

| $\mathrm{d}\Phi$   | Differential Phase (All Channels)                                   | All Outputs                                                                                     |      | 0.4              |      | 0                 |

| T <sub>HD</sub>    | Output Distortion (All Channels)                                    | V <sub>OUT</sub> = 1.8V <sub>P-P</sub> at 3.58/4.43MHz                                          |      | 0.4              |      | %                 |

| X <sub>TALK</sub>  | Crosstalk                                                           | Input of .5V <sub>P-P</sub> at 3.58/4.43MHz<br>on any channel to output of any<br>other channel |      | -55              |      | dB                |

|                    | Input A/ <del>B</del> MUX Crosstalk                                 | Input of 0.5V <sub>P-P</sub> at 3.58/4.43MHz                                                    |      | -54              |      | dB                |

|                    | Swap Mux Crosstalk                                                  | Input of 0.5V <sub>P-P</sub> at 3.58/4.43MHz                                                    |      | -52              |      | dB                |

## ELECTRICAL CHARACTERISTICS (Continued)

| SYMBOL          | PARAMETER                           | CONDITIONS                               | MIN | ТҮР | MAX | UNITS |

|-----------------|-------------------------------------|------------------------------------------|-----|-----|-----|-------|

| PSRR            | PSRR (All Channels)                 | $0.5V_{P-P}$ (100kHz) at V <sub>CC</sub> |     | -39 |     | dB    |

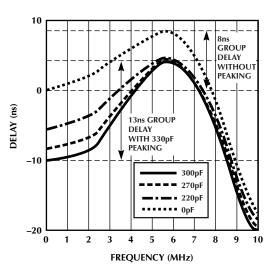

| t <sub>pd</sub> | Group Delay (All Channels)          | at 100kHz                                |     | 60  |     | ns    |

| $\Delta t_{pd}$ | Group Delay Deviation from Flatness | to 3.58MHz (NTSC)                        |     | 4   |     | ns    |

|                 | (See Figures 3 and 14)              | to 4.43MHz (PAL)                         |     | 7   |     | ns    |

|                 | (All Channels)                      | to 10MHz                                 |     | 12  |     | ns    |

| VIH             | Input Voltage Logic High            | A/B MUX, SWAP CVU, SWAP CVF              | 2.5 |     |     | V     |

| V <sub>IL</sub> | Input Voltage Logic Low             | A/B MUX, SWAP CVU, SWAP CVF              |     |     | 1   | V     |

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

**Note 2:** Sustained short circuit protection limited to 10 seconds.

### FUNCTIONAL DESCRIPTION

The ML6429 is a quad monolithic continuous time analog video filter designed for reconstructing signals from four video D/A sources. The ML6429 is intended for use in AC coupled input and output applications.

The filters approximate a 4<sup>th</sup>-order Butterworth characteristic with an optimization toward low overshoot and flat group delay. All outputs are capable of driving  $2V_{P-P}$  into AC coupled 150 $\Omega$  video loads, with up to 35pF of load capacitance at the output pin. Likewise, they are capable of driving a 75 $\Omega$  load at  $1V_{P-P}$ .

All channels are clamped during sync to establish the appropriate output voltage swing range. Thus the input coupling capacitors do not behave according to the conventional RC time constant. Clamping for all channels settles within 10ms of a change in video sources.

Input coupling capacitors of  $0.1\mu$ F are reccommended for all channels. During sync, a feedback error amplifier sources/sinks current to restore the DC level. The net result is that the average input current is zero. Any change in the input coupling capacitors value will linearly affect the clamp response times.

The RGB channels have no pulldown current sources and are essentially tilt-free. The CV channel's inputs sink less than  $1\mu$ A during active video, resulting in a tilt of less than 1mV for a 220  $\mu$ F. Up to  $1000\mu$ F recommended to reude tilt for TV applications.

### SWAP MULTIPLEXER CONTROL

Output pins CV<sub>OUT</sub>1/Y<sub>OUT</sub>A and CV<sub>OUT</sub>2/Y<sub>OUT</sub>B are each independently selectable between three input sources (CV<sub>INF</sub>, and CV<sub>INU</sub>A, CV<sub>INU</sub>B) depending on the digital inputs SWAP CVF, SWAP CVU, and A/B MUX. This allows the two outputs to remain independent and pass straight through, to remain independent but swapped, or for both outputs to have the same signal sourcing from either CV<sub>INF</sub> or CV<sub>INF</sub>A, CV<sub>INU</sub>B (See Table 1). If SWAP CVF is forced to logic low, then CV<sub>OUT2</sub>/Y<sub>OUT</sub>B sources from CV<sub>INU</sub>A/Y2, CV<sub>INU</sub>B/Y3. If SWAP CVU is logic low, CV<sub>OUT1</sub>/Y<sub>OUT</sub>A outputs video from the CV<sub>INU</sub>A, CV<sub>INU</sub>B input. If SWAP CVF is logic high, CV<sub>OUT2</sub>/YOUTB outputs from CV<sub>INF</sub>/Y1 input. If SWAP CVU is high, CV<sub>OUT1</sub>/Y<sub>OUT</sub>A outputs from CV<sub>INU</sub>A/Y2 or CV<sub>INU</sub>B/Y3. Both SWAP CVF and SWAP CVU will pull low if they are not driven.

The ML6429 is robust and stable under all stated load and input conditions. Bypassing both V<sub>CC</sub> pins directly to ground ensures this performance. Two ML6429's can be connected in a master-slave sync configuration. When using this configuration, only the "master" ML6429 is required to have a signal with embedded sync present on the CV<sub>INU</sub>A, CV<sub>INU</sub>B input. In the absence of sync on the CV<sub>INU</sub>A or CV<sub>INU</sub>B input of the "slave" ML6429, the "slave" IC will have its SYNC IN input connected to the SYNC OUT output of the "master" ML6429.

#### SYNCIN AND SYNCOUT PINS

Each ML6429 has two sync detectors which control the DC restore functions. The filtered channel has its own detector, which controls the DC restore function during the horizontal sync period of the  $CV_{INF}/Y1$  input. The other sync detector controls the DC restore functions for the filtered channels based upon the composite or luma input at the  $CV_{INU}A/Y2$  or  $CV_{INU}B/Y3$  pins.

**Required Setup:** A composite or luma or green signal must be present on  $CV_{INU}A/Y2$  or  $CV_{INU}B/Y3$  inputs to provide necessary sync signals to other channels (R,G,B,Y,C). Otherwise, sync must be provided at the SYNCIN pin. For RGB applications, the green channel with sync can be used as an input to  $CV_{INU}A/Y2$  or  $CV_{INU}B/Y3$ .

The SYNCOUT pin outputs a logic high when it detects the horizontal sync of either the  $CV_{INU}A/Y2$  or  $CV_{INU}B/Y3$  input (note that one input is selected by the A/B MUX pin).

The SYNCIN pin is an input for an external H-sync logic signal to enable or disable the internal DC restore loop for the filtered channels. When SYNCIN is logic high, the DC restore function is enabled.

For normal operation, the SYNCOUT pin is connected to the SYNCIN pin (see Figure 4). If the  $CV_{INU}$  does not have an embedded sync, an external sync can be applied on the SYNCIN pin. In master-slave configurations, the SYNCOUT of a ML6429 master can be used as the SYNCIN of a ML6429 slave.

#### **VIDEO I/O DESCRIPTION**

Each input is driven by either a low impedance source or the output of a 75 $\Omega$  terminated line. The input is required to be AC coupled via a 0.1µF coupling capacitor which gives a nominal clamping time of 10ms. All outputs are capable of driving an AC coupled 150 $\Omega$  load at 2V<sub>P-P</sub> or 1V<sub>P-P</sub> into a 75 $\Omega$  load. At the output pin, up to 35pF of load capacitance can be driven without stability or slew issues. A 220µF AC coupling capacitor is recommended at the output to reduce power consumption.

#### ANALOG MULTIPLEXER CONTROL

The four filter channels each have two input multiplexers which are paired to select between two four-channel video sources (*i.e.*, composite video plus RGB component video).

If  $A/\overline{B}$  MUX is forced to logic high, it will select Bank<A> of video inputs (CV<sub>INU</sub>A/Y2, R<sub>IN</sub>A/Y4, G<sub>IN</sub>A/Y6, B<sub>IN</sub>A/C1) to be enabled. If A/ $\overline{B}$  MUX is logic low, then Bank<B> of video inputs (CV<sub>INU</sub>B/Y3, R<sub>IN</sub>B/Y5,G<sub>IN</sub>B/Y7, B<sub>IN</sub>B/C2) will be selected. If the A/ $\overline{B}$  MUX is open, it will pull to logic high.

|         | INPUTS   |          | OUTPUTS                                |                                        |                      |                                      |                                    |  |  |

|---------|----------|----------|----------------------------------------|----------------------------------------|----------------------|--------------------------------------|------------------------------------|--|--|

| A/B MUX | SWAP CVF | SWAP CVU | CV <sub>OUT</sub> 1/Y <sub>OUT</sub> A | CV <sub>OUT</sub> 2/Y <sub>OUT</sub> B | $R_{OUT}/Y_{OUT}C$   | G <sub>OUT</sub> /Y <sub>OUT</sub> D | B <sub>OUT</sub> /C <sub>OUT</sub> |  |  |

| 0       | 0        | 0        | CV <sub>INF</sub> /Y1                  | CV <sub>INU</sub> B/Y3                 | R <sub>IN</sub> B/Y5 | G <sub>IN</sub> B/Y7                 | B <sub>IN</sub> B/C2               |  |  |

| 0       | 0        | 1        | CV <sub>INF</sub> /Y1                  | CV <sub>INF</sub> /Y1                  | R <sub>IN</sub> B/Y5 | G <sub>IN</sub> B/Y7                 | B <sub>IN</sub> B/C2               |  |  |

| 0       | 1        | 0        | CV <sub>INU</sub> B/Y3                 | CV <sub>INU</sub> B/Y3                 | R <sub>IN</sub> B/Y5 | G <sub>IN</sub> B/Y7                 | B <sub>IN</sub> B/C2               |  |  |

| 0       | 1        | 1        | CV <sub>INU</sub> B/Y3                 | CV <sub>INF</sub> /Y1                  | R <sub>IN</sub> B/Y5 | G <sub>IN</sub> B/Y7                 | B <sub>IN</sub> B/C2               |  |  |

| 1       | 0        | 0        | CV <sub>INF</sub> /Y1                  | CV <sub>INU</sub> A/Y2                 | R <sub>IN</sub> A/Y4 | G <sub>IN</sub> A/Y6                 | B <sub>IN</sub> A/C1               |  |  |

| 1       | 0        | 1        | CV <sub>INF</sub> /Y1                  | CV <sub>INF</sub> /Y1                  | R <sub>IN</sub> A/Y4 | G <sub>IN</sub> A/Y6                 | B <sub>IN</sub> A/C1               |  |  |

| 1       | 1        | 0        | CV <sub>INU</sub> A/Y2                 | CV <sub>INU</sub> A/Y2                 | R <sub>IN</sub> A/Y4 | G <sub>IN</sub> A/Y6                 | B <sub>IN</sub> A/C1               |  |  |

| 1       | 1        | 1        | CV <sub>INU</sub> A/Y2                 | CV <sub>INF</sub> /Y1                  | R <sub>IN</sub> A/Y4 | G <sub>IN</sub> A/Y6                 | B <sub>IN</sub> A/C1               |  |  |

Table 1. Selecting Composite, Luma, RGB, and Chroma Outputs

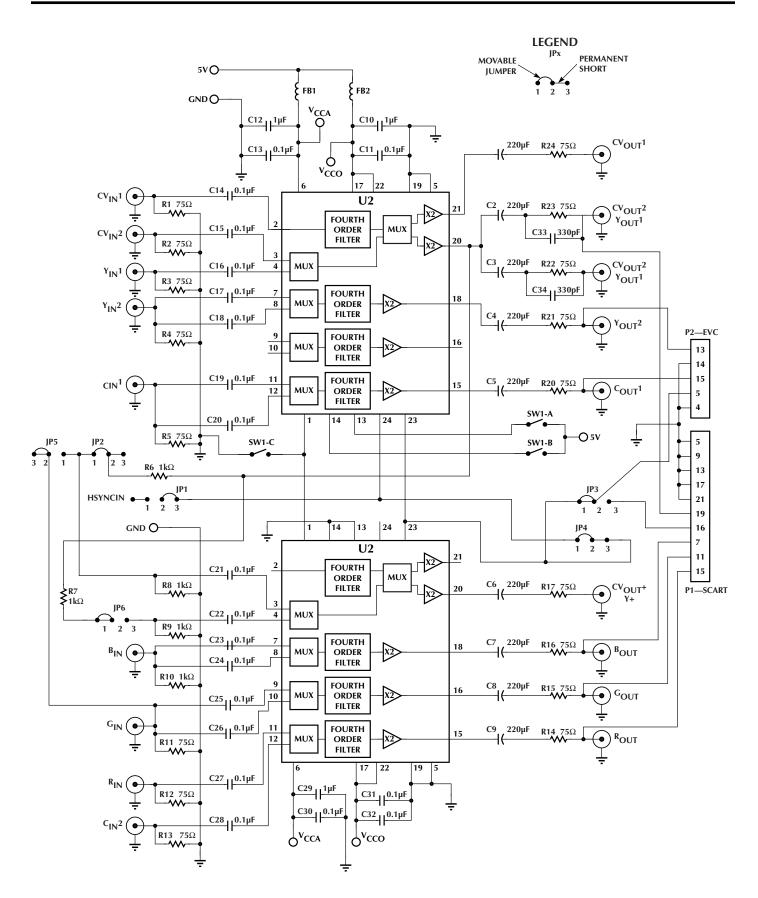

### TYPICAL APPLICATIONS

### **BASIC APPLICATIONS**

The ML6429 provides channels for two banks of inputs for RGB and composite video. The R and G channels can be used as luma inputs while the B channel can be used as a chroma input. Composite outputs and an H-sync output is also provided. There are several configurations available with the ML6429. Figure 4 includes a list of basic output options for composite, S-video, TV modulator, and RGB outputs. Note that each composite channel can drive a CV load or a channel modulator simultaneously. The ML6429 standalone can be used as an EVC or SCART cable driver with nine video sources (75 $\Omega$  or low impedance buffer) and seven video outputs. All inputs and outputs are AC coupled. When driving seven loads, power dissipation must be measured to ensure that the junction temperature doesn't exceed 120°C.

#### **EVC CABLE DRIVING**

The ML6429 can be configured to drive composite video, S-video, and horizontal sync through an EVC connector (Figure 5). Composite video and S-video inputs are filtered through 4<sup>th</sup>-order Butterworth filters and driven through internal 75 $\Omega$  cable drivers. A buffered H-sync output is also available.

### SCART CABLE DRIVING

The ML6429 can be configured either as a SCART cable driver (Figure 4) or as a SCART cable driver and S-video driver (Figure 6). A horizontal sync output is also available. Note that the ML6429 can be used in a master-slave mode where the sync-out from the master is used as the sync-in of the slave; this allows the CV, S-video, and RGB channels to operate under the same sync signals.

Note that in SCART applications, it is not always necessary to AC couple the outputs. Systems using SCART connectors for RGB and composite video can typically handle between 0 and 2V DC offset (see DC Coupled Applications section).

### **RGB APPLICATIONS**

RGB video can be filtered and driven through the ML6429. For sync suppressed RGB, the sync signal can be derived from SYNCIN PIN.

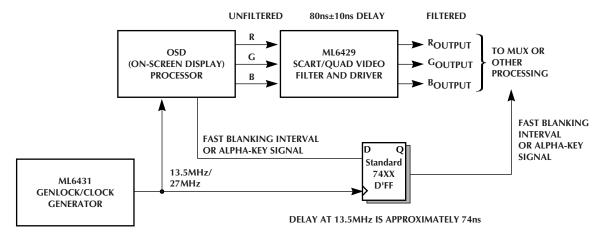

#### OSD (ON-SCREEN DISPLAY) APPLICATIONS

Unfiltered RGB video from an OSD processor needs to be filtered and then synchronized to a fast blanking interval or alpha-key signal for later video processing. With the total filter delay being  $80ns \pm 10ns$ , a D flip-flop or similar delay element can be used to delay the fast blanking interval or alpha-key signal, which synchronizes the RGB and OSD signals (Figure 9).

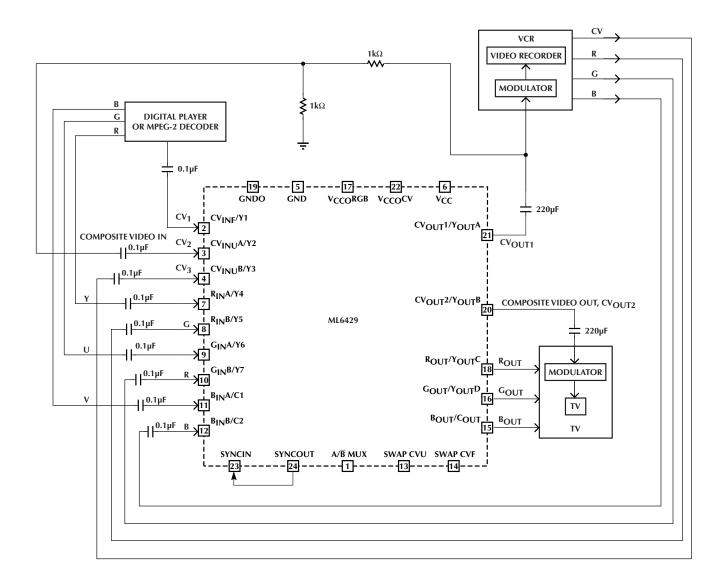

#### CHANNEL MULTIPLEXING

The ML6429 can be configured for multiple composite channel multiplexing (Figure 8). Composite and RGB sources such as VCRs, and digital MPEG 2 sources can be selected using the ML6429 swap mux controls. A/B MUX, SWAP CVU, and SWAP CVF signals can be used to select and route from various input sources.

#### DC COUPLED APPLICATIONS

The 220 $\mu$ F capacitor coupled with the 150 $\Omega$  termination forms a highpass filter which blocks the DC while passing the video frequencies and avoiding tilt. Lower values such as 10 $\mu$ F would create a problem. By AC coupling, the average DC level is zero. Thus, the output voltages of all channels will be centered around zero.

Alternately, DC coupling the output of the ML6429 is allowable. There are several tradeoffs: The average DC level on the outputs will be 2V; Each output will dissipate an additional 40mW nominally; The application will need to accommodate a 1V DC offset sync tip; And it is recommended to limit one 75 $\Omega$  load per output. However, if two loads are required to be driven at a time on the composite output while DC coupling is used, then the swap–mux and 5<sup>th</sup> line driver can be configured to enable the filtered composite signal on both the 4<sup>th</sup> and 5<sup>th</sup> line drivers. Thus, the composite load driving requirement is divided into two line drivers versus one.

**Required Setup:** A composite or luma or green signal must be present on  $CV_{INU}A/Y2$  or  $CV_{INU}B/Y3$  inputs to provide necessary sync signals to other channels (R,G,B,Y,C). Otherwise, sync must be provided at the SYNCIN pin. For RGB applications, the green channel with sync can be used as an input to  $CV_{INU}A/Y2$  or  $CV_{INU}B/Y3$ .

#### **USING THE ML6429 FOR PAL APPLICATIONS**

The ML6429 can be optimized for PAL video by adding frequency peaking to the composite and S-video outputs. Figure 10 illustrates the use of a additional external capacitor (300pF), added in parallel to the output source termination resistor. This raises the frequency response from 1.0dB down at 4.8MHz (for no peaking cap) to 0.2dB down at 4.8MHz (for 300 pF), which allows for accurate reproduction of the upper sideband of the PAL subcarrier. Figure 11 shows the frequency response of PAL video with various values of peaking capacitors (0pF, 220pF, 270pF, 300pF) between 0 and 10MHz.

For NTSC applications without the peaking capacitor, the rejection at 27MHz is 40dB (typical). For PAL applications with the peaking capacitor, the rejection at 27MHz is 34dB (typical). (Figure 12). The differential group delay is shown in Figure 13 with and without a peaking capacitor (0pF, 220pF, 270pF, and 300pF) varies slightly with capacitance; from 8ns to 13ns.

Figure 4. Basic Application for NTSC

Figure 5. EVC (Enhanced Video Connector) Application: S-Video, Composite, plus H-Sync out

Figure 6. SCART (Peritel) + S-Video Application: S-Video, RGB, Composite, plus H-Sync out

|         | INPUTS   |          | Ol                  |                     |                   |                   |                   |

|---------|----------|----------|---------------------|---------------------|-------------------|-------------------|-------------------|

| A/B MUX | SWAP CVU | SWAP CVF | CV <sub>OUT</sub> 1 | CV <sub>OUT</sub> 2 | R <sub>OUT</sub>  | G <sub>OUT</sub>  | BOUT              |

| 0       | 0        | 0        | Digital Player      | VCR                 | VCR               | VCR               | VCR               |

| 1       | 0        | 1        | Digital Player      | Digital Player      | Digital<br>Player | Digital<br>Player | Digital<br>Player |

Figure 7. Multi-Source CV and RGB Channels

Figure 8. Synchronizing the Filter Delay with Fast Blanking or Alpha-Key Signals in OSD Applications

Figure 9. Basic Application for PAL

Figure 10. NTSC/PAL Video Frequency Response With and Without Peaking Capacitor

Figure 11. Stopband Rejection at 27MHz With and Without Peaking Capacitor

Figure 12. Group Delay at 5.5MHz (PAL) With and Without Peaking Capacitor

#### Figure 13. Schematic

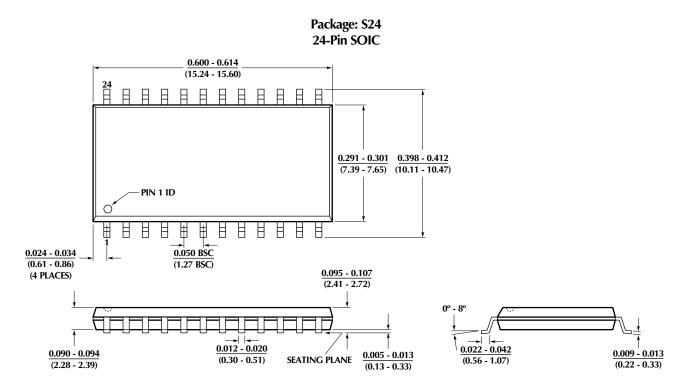

### PHYSICAL DIMENSIONS inches (millimeters)

### ORDERING INFORMATION

| PART NUMBER | TEMPERATURE RANGE | PACKAGE           |  |  |

|-------------|-------------------|-------------------|--|--|

| ML6429CS-1  | 0°C to 70°C       | 24 Pin SOIC (S24) |  |  |

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.