#### 查询MM5484供应商

| If Military/Aerospace spe | cified devices are required,    | Operating Temperature                                                | -40°C to +85°                 |  |

|---------------------------|---------------------------------|----------------------------------------------------------------------|-------------------------------|--|

|                           | ional Semiconductor Sales       | Storage Temperature                                                  | -40°C to +150°C               |  |

|                           | ilability and specifications.   | Power Dissipation at 25°C                                            |                               |  |

| Voltage at LED Outputs    | $V_{SS}-$ 0.5V to $V_{SS}+$ 12V | Molded DIP Package, board mount                                      | 21                            |  |

| Voltage at Other Pins     | $V_{SS}-$ 0.5V to $V_{SS}+$ 10V | Molded DIP Package, socket mount                                     | 1.8W*                         |  |

|                           |                                 | *Molded DIP Package, board mount,<br>derate 15.8m W/°C above 25°C.   | $\theta_{JA} = 63^{\circ}C/W$ |  |

|                           |                                 | **Molded DIP Package, socket mount,<br>derate 14.5m W/°C above 25°C. | $\theta_{JA} = 69^{\circ}C/V$ |  |

|                           |                                 | Lead Temperature (Soldering, 10 sec.)                                | 300°                          |  |

### DC Electrical Characteristics $V_{DD} = 4.5V$ to 9V, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ unless otherwise specified

| Parameter                                                                                                              | Conditions                                                                                   | Min                   | Тур | Max                   | Units         |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|---------------|

| Supply Voltage                                                                                                         |                                                                                              | 4.5                   |     | 9                     | V             |

| Supply Current                                                                                                         |                                                                                              |                       | 5   | 10                    | mA            |

| Logic One<br>Input High Level V <sub>IH</sub>                                                                          |                                                                                              | 2.4                   |     | V <sub>DD</sub> + 0.5 | v             |

| Logic Zero<br>Input Low Level V <sub>IL</sub><br>Input Current<br>Input Capacitance                                    | High or Low Level                                                                            | 0                     |     | 0.8<br>±1<br>7.5      | V<br>μA<br>pF |

| TPUTS                                                                                                                  |                                                                                              | ·                     | •   |                       |               |

| Data Output Voltage<br>High Level V <sub>OH</sub><br>Low Level V <sub>OL</sub><br>Segment Off<br>(Logic Zero on Input) | $I_{OUT} = 0.1 \text{ mA}$ $I_{OUT} = -0.1 \text{ mA}$ $V_{OUT} = 12V$ $R_{EXT} = 400\Omega$ | V <sub>DD</sub> - 0.5 |     | 0.5<br>50             | ۷<br>۷<br>μΑ  |

| Output Current Segment On<br>(Logic One on Input)<br>Output Voltage                                                    | $I_{OUT} = 15 \text{ mA}$<br>$V_{DD} \ge 6V$                                                 |                       | 0.5 | 1.0                   | v             |

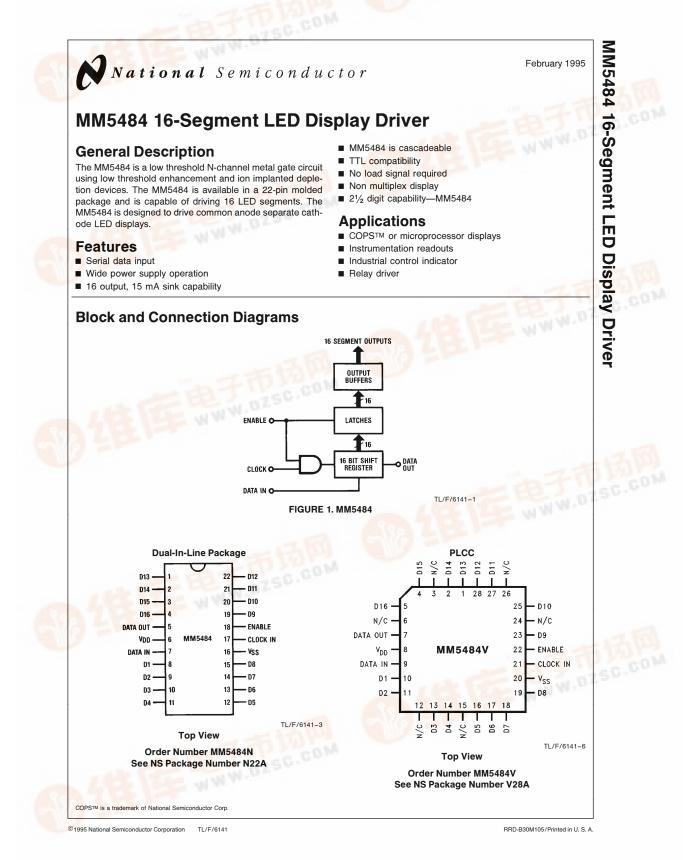

# **AC Electrical Characteristics**

(See Figure 3.)  $V_{DD}=$  4.5V to 9V,  $T_{A}=\,-40^{\circ}C$  to  $\,+\,85^{\circ}C$  unless otherwise specified

| Symbol          | Parameter         | Conditions | Min  | Тур | Max | Units |

|-----------------|-------------------|------------|------|-----|-----|-------|

| f <sub>C</sub>  | Clock Frequency   |            |      |     | 0.5 | MHz   |

| t <sub>h</sub>  | High Time         |            | 0.95 |     |     | μs    |

|                 | Low Time          |            | 0.95 |     |     | μs    |

| t <sub>S1</sub> | Data Setup Time   |            | 0.5  |     |     | μs    |

| t <sub>H1</sub> | Data Hold Time    |            | 0.5  |     |     | μs    |

| t <sub>S2</sub> | Enable Setup Time |            | 0.5  |     |     | μs    |

| t <sub>H2</sub> | Enable Hold Time  |            | 0.5  |     |     | μs    |

| t <sub>pd</sub> | Data Out Delay    |            |      |     | 0.5 | μs    |

Note 1: Under no condition should the power dissipated by the segment driver exceed 50 mW nor the entire chip power dissipation exceed 500 mW. Note 2: AC input waveform specification for test purpose:  $t_f \le 20$  ns,  $t_f \le 20$  ns, f = 500 kHz,  $50\% \pm 10\%$  duty cycle. Note 3: Clock input rise and fall times must not exceed 500 ns.

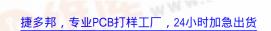

#### **Functional Description**

The MM5484 is designed to drive LED displays directly. Serial data transfer from the data source to the display driver is accomplished with 3 signals, DATA IN, CLOCK and EN-ABLE. The signal ENABLE acts as an envelope and only while this signal is at a logic '1' do the circuits recognize the clock signal.

While ENABLE is high, data on the serial data input is transferred and shifted in the internal shift register on the rising clock edge, i.e. a logic '0' to logic '1' transition. When the ENABLE signal goes to a low (logic zero state), the contents of the shift register is latched and the display will show the new data. While new data is being loaded into the SR the display will continue to show the old data.

For the MM5484, data is output from the serial DATA OUT pin on the falling edge of clock so cascading is made simple with race hazards eliminated.

When the chip first powers on, an internal power on reset signal is generated which resets the SR and latches to zero so that the display will be off.

## **Timing Diagram**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.