# MM82PC12 8-Bit Input/Output Port

# July 1987

## **General Description**

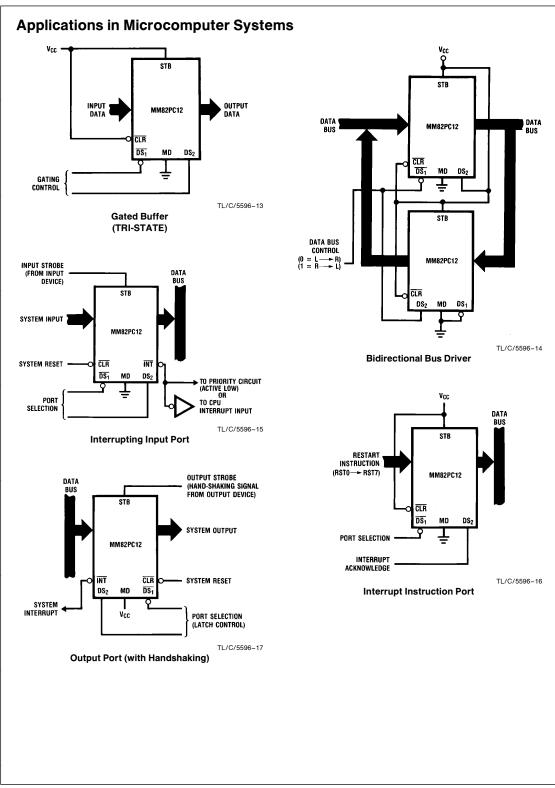

The MM82PC12 is a microCMOS 8-bit input/output port contained in a standard 24-pin dual-in-line package. The MM82PC12 can be used to implement latches, gated buffers, or multiplexers. Thus, all of the major peripheral and input/output functions of a microcomputer system can be implemented with this device.

The MM82PC12 includes an 8-bit latch with TRI-STATE® output buffers, and device selection and control logic. Also included is a service request flip-flop for the generation and control of interrupts to the microprocessor.

The MM82PC12 is pinout and function compatible with standard INS8212 and DP8212 devices.

For military applications, the MM82PC12 is available with class B screening in accordance with method 5004 of MIL-STD-883.

### **Features**

- Drive capability—150 pF load

- High noise immunity

- Low power dissipation

- Full interface to CMOS logic levels

- microCMOS technology

- $\blacksquare$  TTL drive capability when  $V_{CC} = 5V$

- 8-bit data latch and buffer

- Service request flip-flop for generation and control of interrupts

- 1 µA input load current

- Reduces system package count by replacing buffers, latches, and multiplexers in microcomputer systems

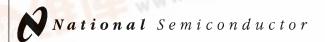

# **System Configuration**

TL/C/5596-1

TRI-STATE® is a registered trademark of National Semiconductor Corp.

©1995 National Semiconductor Corporation

RRD-B30M105/Printed in U. S. A.

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

-65°C to +150°C Storage Temperature Range

Voltage at Any Pin With Respect to Ground

-0.3 V to  $V_{\hbox{\footnotesize CC}}\,+\,0.3 V$

Lead Temperature

(Soldering, 10 seconds)

300°C

Power Dissipation 500 mW Maximum V<sub>CC</sub>

Note: Absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed. Continuous operation at these limits is not intended; operation should be limited to those conditions specified under DC Electrical Characteristics.

# Operating Range $V_{CC} = 5V \pm 10\%$

Ambient Temperature

Military  $-55^{\circ}$ C to  $+125^{\circ}$ C Industrial  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ 0°C to +70°C Commercial

# **DC Electrical Characteristics**

$V_{CC} = 5V \pm 10\%$ , GND = 0V, unless otherwise specified

| 0                | D                                 | Total Complisions                                                  |                     | <b>T</b> |                     | 11-24- |

|------------------|-----------------------------------|--------------------------------------------------------------------|---------------------|----------|---------------------|--------|

| Symbol           | Parameter                         | Test Conditions                                                    | Min                 | Тур      | Max                 | Units  |

| $V_{IH}$         | Input High Voltage                |                                                                    | 0.7 V <sub>CC</sub> |          | V <sub>CC</sub>     | V      |

| $V_{IL}$         | Input Low Voltage                 |                                                                    | 0                   |          | 0.2 V <sub>CC</sub> | V      |

| $V_{OH}$         | Output High Voltage               | $V_{CC} = 4.5V, V_{IH} = 4.5V, I_{OH} = -2 \text{ mA}$             | 2.4                 |          |                     | V      |

| $V_{OL}$         | Output Low Voltage                | $V_{CC} = 5.5V, V_{IL} = 0V, V_{IH} = 5.5V, I_{OL} = 2 \text{ mA}$ |                     |          | 0.4                 | V      |

| I <sub>IH</sub>  | Input High Current                | $V_{CC} = 5.5V, V_{IN} = 5.5V$                                     |                     |          | 10                  | μΑ     |

| I <sub>IL</sub>  | Input Low Current                 | $V_{CC} = 5.5V, V_{IN} = 0V$                                       |                     |          | -10                 | μΑ     |

| I <sub>OH</sub>  | Output High Current               | $V_{CC} = 4.5V, V_{OUT} = 2.4V, V_{IH} = 4.5V$                     | -2.0                |          |                     | mA     |

| $I_{OL}$         | Output Low Current                | $V_{CC} = 5.5V, V_{OUT} = 0.4V, V_{IL} = 0V$                       | 2.0                 |          |                     | mA     |

| Icc              | Power Supply Current              | $V_{CC} = 5.5V, V_{IH} = 5.5V, V_{IL} = 0V$                        |                     |          | 400                 | μΑ     |

| l <sub>OZL</sub> | TRI-STATE Low Leakage<br>Current  | $V_{CC} = 5.5V, V_{OUT} = 0V$                                      |                     |          | -10                 | μΑ     |

| lozh             | TRI-STATE High Leakage<br>Current | V <sub>CC</sub> = 4.5V, V <sub>OUT</sub> = 4.5V                    |                     |          | 10                  | μΑ     |

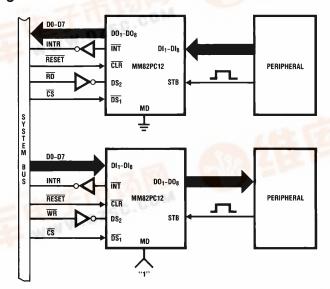

# **AC Electrical Characteristics**

$T_{A}=\,-55^{\circ}\!C$  to  $\,+\,125^{\circ}\!C,\,V_{CC}=\,5V\,\pm10\,\%,\,GND=\,0V,$  unless otherwise specified

| Symbol           | Parameter                         | Test Conditions | Min | Тур | Max | Units |

|------------------|-----------------------------------|-----------------|-----|-----|-----|-------|

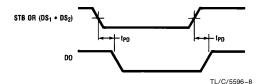

| t <sub>PW</sub>  | Pulse Width (STB, DS1 ● DS2, CLR) |                 |     | 25  | 40  | ns    |

| t <sub>PD</sub>  | Data In to Data Out               |                 |     | 45  | 60  | ns    |

| t <sub>WE</sub>  | Write Enable to Data Out          |                 |     | 55  | 75  | ns    |

| t <sub>SET</sub> | Data Setup Time                   |                 | 15  |     |     | ns    |

| t <sub>H</sub>   | Data Hold Time                    |                 | 20  |     |     | ns    |

| t <sub>R</sub>   | Reset to Data Out                 |                 |     | 50  | 65  | ns    |

| t <sub>S</sub>   | Select to Interrupt               |                 |     | 50  | 65  | ns    |

| t <sub>C</sub>   | Clear to Data Out                 |                 |     | 45  | 60  | ns    |

| t <sub>ED</sub>  | Output Enable/Disable Time        |                 |     | 50  | 65  | ns    |

# **Propagation Delays**

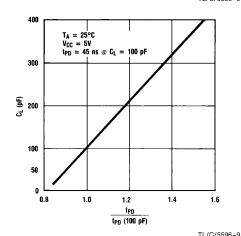

Figure 1 illustrates the calculations of a more useful propagation delay. The figure uses a 5V supply with a tolerance of  $\pm\,10\%$ , ambient temperature of  $+\,25^\circ\mathrm{C}$ , and a load capacitance of 100 pF. The AC Characteristics table depicts tpp, at 5V, 25°C, equalling 25 ns. Use the graph in Figure 1 to get the degradation multiple for 150 pF. The number shown is 1.09. The adjusted propagation delay is, therefore 25  $\times\,10.09$  or 27 ns.

\*Including jig and probe capacitance.

### Output Test Circuit for Propagation Delays

FIGURE 1. Normalized Typical Propagation Delay vs.

Load Capacitance

# **Pin Descriptions**

The following describes the function of all the MM82PC12 input/output pins. Some of these descriptions reference internal circuits.

### **INPUT SIGNALS**

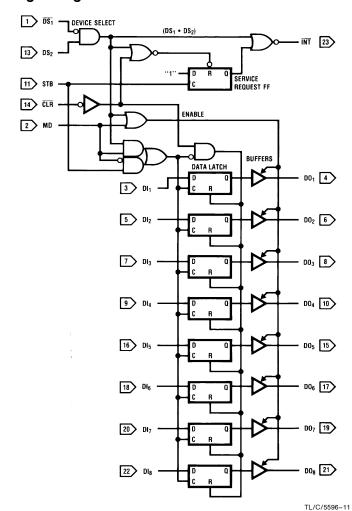

**Device Select (\overline{DS}\_1, DS\_2:** When  $\overline{DS}_1$  is low and  $DS_2$  is high, the device is selected. The output buffers are enabled and the service request flip-flop is asynchronously reset (cleared) when the device is selected.

**Mode (MD):** When MD is high (output mode), the output buffers are enabled and the source of the data latch clock input is the device selection logic (DS $_1 \bullet$  DS $_2). When MD is low (input mode), the state of the output buffers is determined by the device selection logic (DS<math display="inline">_1 \bullet$  DS $_2)$  and the source of the data latch clock input is the strobe (STB) input.

**Strobe (STB):** STB is used as the data latch clock input when the mode (MD) input is low (input mode). STB is also used to synchronously set the service request flip-flop, which is negative edge triggered.

Data In (DI<sub>1</sub>-DI<sub>8</sub>): Data In is the 8-bit data input to the data latch, which consists of eight D-type flip-flops incorporating a level sensitive clock. While the data latch clock input is high, the Q output of each flip-flop follows the data input. When the clock input returns low, the data latch stores the data input. Clear (CLR) is only effective when the clock is low (latch in the latched state).

Clear ( $\overline{\text{CLR}}$ ): When  $\overline{\text{CLR}}$  is low, the data latch is reset (cleared) if the clock is also low. The clock input high overrides the clear ( $\overline{\text{CLR}}$ ) input data latch reset.  $\overline{\text{CLR}}$  being low also resets the service request flip-flop. The service request flip-flop is in the non-interrupting state when reset.

### **OUTPUT SIGNALS**

Interrupt (INT): The interrupt pin goes low (interrupting state) when either the service request flip-flop is synchronously set by the strobe (STB) input or the device is selected.

**Data Out (DO<sub>1</sub>-DO<sub>8</sub>):** Data Out is the 8-bit data output of data buffers, which are TRI-STATE, non-inverting stages. These buffers have a common control line that either enables the buffers to transmit the data from the data latch outputs or disables the buffers by placing them in the high-impedance state.

# **Reliability Information**

Gate Count 108 Transistor Count 248

# **Connection Diagrams**

#

Top View

TL/C/5596-10

Order Number MM82PC12J or N See NS Package Number J24A or N24A

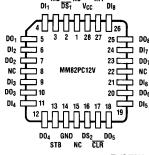

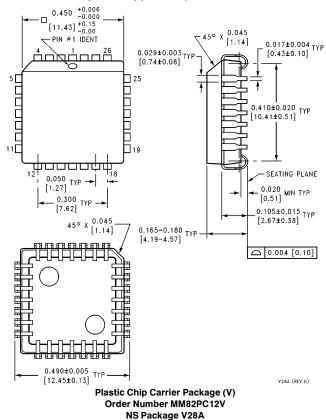

# Plastic Chip Carrier MD\_\_\_NC INT

TL/C/5596-12 **Top View**

Order Number MM82PC12V See NS Package Number V28A

### Logic Table A

| STB | MD | DS <sub>1</sub> • DS <sub>2</sub> | Data Out<br>Equals |  |

|-----|----|-----------------------------------|--------------------|--|

| 0   | 0  | 0                                 | TRI-STATE          |  |

| 1   | 0  | 0                                 | TRI-STATE          |  |

| 0   | 1  | 0                                 | Data Latch         |  |

| 1   | 1  | 0                                 | Data Latch         |  |

| 0   | 0  | 1                                 | Data Latch         |  |

| 1   | 0  | 1                                 | Data In            |  |

| 0   | 1  | 1                                 | Data In            |  |

| 1   | 1  | 1                                 | Data In            |  |

Note:  $\overline{\text{CLR}}$   $\sim$  resets data latch to the output low state. The data latch clock is level sensitive, a low level clock latches the data.

# **Logic Diagram**

Logic Table B

| CLR     | DS <sub>1</sub> • DS <sub>2</sub> | STB    | Q* | ĪNT |

|---------|-----------------------------------|--------|----|-----|

| 0 RESET | 0                                 | 0      | 0  | 1   |

| 1       | 0                                 | 0      | 0  | 1   |

| 1       | 0                                 | $\sim$ | 1  | 0   |

| 1       | 1 RESET                           | 0      | 0  | 0   |

| 1       | 0                                 | 0      | 0  | 1   |

<sup>\*</sup>Internal Service Request flip-flop.

# **Ordering Information**

# MM82PC12XXX | /A + = A + Reliability Screening | | /883 = MIL-STD-883B Screening (Note 1) | | I = Industrial Temperature (-40°C to +85°C) | | M = Military Temperature (-55°C to +125°C) | | No Designation = Commercial Temperature (0°C to +70°C) | | N = Plastic Package | | J = Cerdip Package | | V = Plastic Leaded Chip Carrier (PCC) (Availability to be announced)

TL/C/5596-18

Note 1: Do not specify a temperature option; all parts are screened to military temperature.

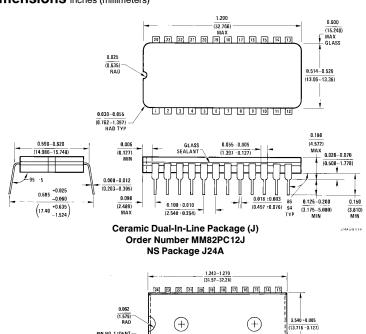

# Physical Dimensions inches (millimeters)

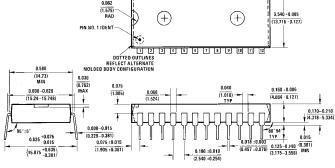

Molded Dual-In-Line Package (N) Order Number MM82PC12N NS Package N24A

# Physical Dimensions inches (millimeters) (Continued)

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86

Email: cnjwge@tevm2.nsc.com

Deutsch Tel: (+49) 0-180-530 85 85

English Tel: (+49) 0-180-532 78 32

Français Tel: (+49) 0-180-532 78 61

Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408