查询MN6732741供应商 Video Camera LSIs

#### 捷多邦,专业PCB打样工 sonic

# MN6732741

Signal-processing IC for surveillance cameras and cameras for PC input

#### Overview

The MN6732741 is camera signal-processing IC appropriate for a wide variety of applications, including surveillance cameras and cameras used for input to personal computers. In addition to the basic functions of luminance and chrominance signal processing, it also integrates the ALC, AWB, and AGC functions that were previously implemented using microcontroller signal processing. Furthermore, it also integrates on a single chip, including SSG, CG, and I<sup>2</sup>C-bus functions.

#### Features

- Input: Analog signal (A/D converter input) Digital output

- Outputs:

8-bit YUV signal

Analog outputs Luminance signal

Chrominance signal

Composite video signal output

- **RGB** output

- Operating supply voltage:  $3.3 V \pm 0.3 V$

- Operating clock frequency: 9.5 MHz to 28.7 MHz

- Main functions

- 10-bit A/D converter

- Single-channel 10-bit D/A converter

- Two-channel 8-bit D/A converter

- Supports analog AGC (NN2038 or NN2039)

- · CG and SSG circuits

- Supports 510 and 768 horizontal lines (NTSC and PAL)

- Supports VGA progressive scan readout CCDs (complementary color filters)

- Also supports black-and-white CCD signal processing

- CCD white defect/black defect correction circuit

- Digital AGC gain: up to 24 dB

- · Left/right reversing function

- Variable gamma correction ( $\gamma = 0.3$  to 1)

- ZV port standard mode, BT656 standard mode

- Modes: LL, SYNC, VD2, and HD/VD external synchronization support

- Built-in I<sup>2</sup>C-bus circuit

- ALC and AGC (Also supports external AGC)

- Two white balance modes (manual and ATW) with ATW lock function

- Automatic OB correction function

#### Applications

• Surveillance cameras, PC input cameras, multimedia cameras

## MN6732741

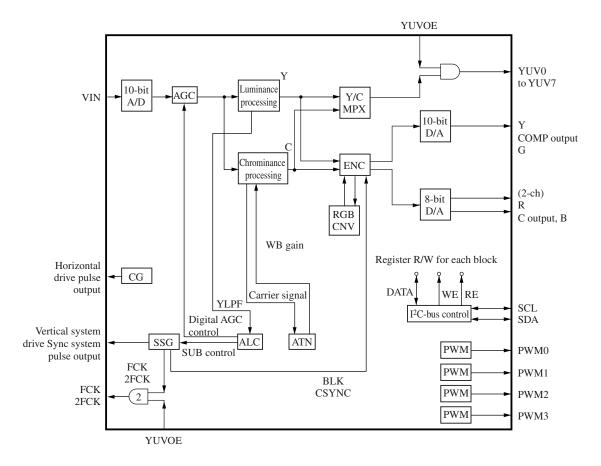

### Block Diagram

#### Function Descriptions (by circuit block)

#### 1. ADC

Converts the post-CDS CCD signal to a 10-bit digital signal.

#### 2. PATGEN

Generates test pattern signals. This circuit generates horizontal and vertical patterns with a color bar (3 colors) format. Since it simulates the output of the CCD 4-color complementary color filters, it conveniently allows problems in the analog block, from the CCD to the A/D converter, and IC internal problems, to be isolated. It can also be used to temporarily halt CCD image output and generate a blue background signal.

#### 3. AGC (AGC, pixel mixing, mirror reversal, and OB clamping functions)

Performs AGC control (up to +24 dB) digitally by linking with the ALC. Since the IC also provides an interface output to an external analog AGC (NN2038 or NN2039), over 24 dB of gain can be provided.

When a VGA CCD is used, since progressive scan is used, the photodiode mixing operation used with earlier interlaced CCDs is not required. The AGC circuit includes an internal pixel mixing circuit, and is designed for both progressive and interlaced scan at the circuit level.

In the mirror mode provided by 510 H and 768 H CCDs, it is possible to generate a reversed video signal by controlling RAM. OB correction is also performed in this block, and this function has both a digital mode, in which processing is performed internally to the IC, and an analog mode that controls the external CDS and AGC IC clamp voltage.

#### Function Descriptions (by circuit block) (continued)

#### 4. ALC

The ALC block controls the exposure electronically by inputting the luminance signal, taking an averaged but center weighted exposure reading over the whole image, and comparing that to the target value. That result is used to control the CCD's electronic shutter.

In ELC mode, since the step size of the electronic shutter accumulation time is discrete, the AGC system is used in conjunction with the ALC function to create a smoothly operating control system. This block also performs a 3field averaging flicker correction operation as well.

#### 5. Luminance system

After generating the luminance signal from the complementary color filter CCD output using a low-pass filter, this block generates the horizontal and vertical aperture signals and performs coring/low-luminance suppression, gamma correction, and blanking processing.

This block includes a defect correction circuit that corrects for defective pixels in the CCD. One of two outline correction levels can be selected with the APGAIN pin.

The IC also includes a defect correction circuit that corrects for missing pixels in the CCD. The gamma correction is continuously variable from  $\gamma = 0.3$  to 1. The luminance signal low-pass filter can be bypassed to allow this device to handle black-and-white CCDs.

#### 6. Chrominance system

This block performs white balance processing, carrier balance, color temperature correction, and low-luminance/ high-luminance chrominance suppression processing.

#### 7. AWB

This block generates the auto white balance control signal. This white balance function operates so that the state of the immediately prior and proper illumination level will be held in case of low illumination levels.

#### 8. ENC

This block converts between NTSC and PAL. A digital technique in which  $4f_{SC}$  is created from FSC is adopted, and the clock system is unified into a single system. To create the composite video signal, clock rate conversion is also applied to the Y signal and the signals are mixed digitally. The sync signal can also be mixed digitally.

#### 9. RGBCNV

The YUV signal generated from the luminance and chrominance signals is converted to RGB using a matrix. However, since the band of the UV signal is dropped to around 800 kHz at a relatively early stage relative to the chrominance signal, this is not a signal in which all three channels have the same wide band as the Y signal, such as the signals used in 3-CCD video cameras.

#### 10. YCMPX

This block takes the FCK rate luminance and UV signals and outputs them as an 8-bit time-division multiplexed signal with a 2FCK rate.

In BT656 standard mode, SAV and EAV are embedded in the signal.

#### 11. D/A converters

One D/A converter block converts the digital input to analog output. There are three channels, and one channel with a 10-bit resolution is provided for each of the composite, Y, and G signals. The circuit is designed so that the sync can be mixed digitally.

The remaining D/A converter is a two-channel 8-bit device used for the chrominance, R, and B signals.

#### 12. PWM

Provides an independently controllable 4-channel PWM output circuit that can be used to control analog circuits peripheral to the IC. These outputs can be used, for example, for VREF adjustment of D/A converter.

#### 13. CG

This circuit generates the high-speed pulse signals (H1, H2, DS1, and DS2) used by the CCD. This block's logic system power supply is isolated from the other IC internal logic circuits to minimize noise.

#### Function Descriptions (by circuit block) (continued)

#### 14. SSG

This block generates both low-speed pulse signals used by the CCD and various kinds of pulse signals used for signal processing. (However, note that VBSGEN locking is not supported.)

#### 15. I<sup>2</sup>C-bus

When power is first applied, the contents of an external EEPROM are read out and used to set the IC internal registers.

Since this circuit does not support multi-master operation, no external devices will have become bus master when power is first applied. This I<sup>2</sup>C-bus also can be used by external devices to read or write the IC internal registers. (Note that certain limitations apply.)

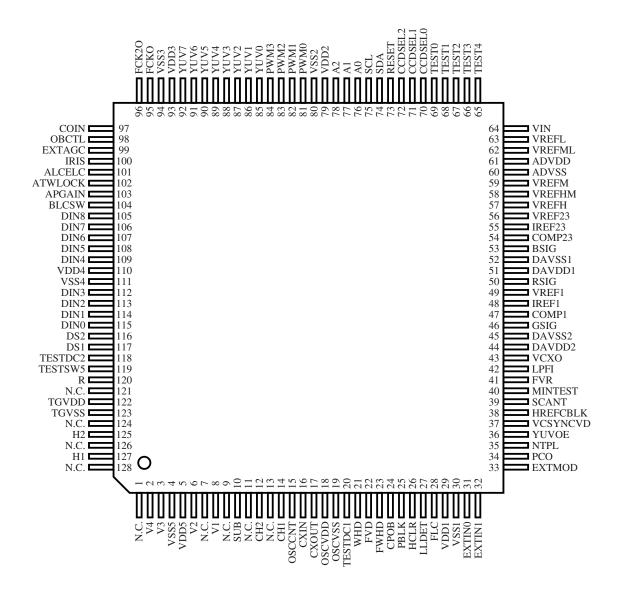

#### Pin Arrangement

# Pin Descriptions

| Pin No. | Pin     | I/O | Description                                                                                          |

|---------|---------|-----|------------------------------------------------------------------------------------------------------|

| 1       | N.C.    | _   | _                                                                                                    |

| 2       | V4      | 0   | φV4 charge pulse                                                                                     |

| 3       | V3      | 0   | φV3 charge pulse                                                                                     |

| 4       | VSS5    | VSS | Digital system ground                                                                                |

| 5       | VDD5    | VDD | Digital system power supply (3.3 V)                                                                  |

| 6       | V2      | 0   | φV2 charge pulse                                                                                     |

| 7       | N.C.    | _   | _                                                                                                    |

| 8       | V1      | 0   | φV1 charge pulse                                                                                     |

| 9       | N.C.    | _   | _                                                                                                    |

| 10      | SUB     | 0   | Vertical removal pulse                                                                               |

| 11      | N.C.    | _   | _                                                                                                    |

| 12      | CH2     | 0   | V3 charge pulse                                                                                      |

| 13      | N.C.    | _   | _                                                                                                    |

| 14      | CH1     | 0   | V1 charge pulse                                                                                      |

| 15      | OSCCNT  | 0   | Oscillator control test                                                                              |

| 16      | CXIN    | Ι   | Synchronization oscillator (crystal oscillator)                                                      |

| 17      | CXOUT   | 0   | Synchronization oscillator (crystal oscillator)                                                      |

| 18      | OSCVDD  | VDD | Oscillator cell power supply                                                                         |

| 19      | OSCVSS  | VSS | Oscillator cell ground                                                                               |

| 20      | TESTDC1 | Ι   | Test input (Normally connect to low.)                                                                |

| 21      | WHD     | 0   | WHD signal that is in proper phase relative to the sync signal                                       |

| 22      | FVD     | 0   | VD signal that is in proper phase relative to the sync signal                                        |

| 23      | FWHD    | 0   | WHD for TG drive                                                                                     |

| 24      | CPOB    | 0   | A/D converter input signal clamp pulse, or D/A converter output clamp pulse                          |

| 25      | PBLK    | 0   | Pre-blanking pulse                                                                                   |

| 26      | HCLR    | 0   | Horizontal reference signal                                                                          |

| 27      | LLDET   | Ι   | Power supply synchronization switching signal                                                        |

|         |         |     | Low: internal synchronization, High: LL synchronization                                              |

| 28      | FLC     | Ι   | Flicker correction (pulled up). High: Flicker correction on                                          |

| 29      | VDD1    | VDD | Digital system power supply (3.3 V)                                                                  |

| 30      | VSS1    | VSS | Digital system ground                                                                                |

| 31      | EXTIN0  | Ι   | External sync signal input 1                                                                         |

| 32      | EXTIN1  | Ι   | External sync signal input 2                                                                         |

| 33      | EXTMOD  | Ι   | Monitor/automotive mode switch (pulled up)<br>High: Automotive mode (HDVD/SYNC synchronization mode) |

| 34      | РСО     | 0   | Phase comparator output                                                                              |

| 35      | NTPL    | I   | NTSC/PAL switching. Low: NTSC, High: PAL (pulled down)                                               |

# ■ Pin Descriptions (continued)

| Pin No. | Pin      | I/O | Description                                                                                      |

|---------|----------|-----|--------------------------------------------------------------------------------------------------|

| 36      | YUVOE    | Ι   | Digital output system output enable                                                              |

| 37      | VCSYNCVD | 0   | VCSYNC output/VD output (VGA mode CSYNC/IT mode register switching)                              |

| 38      | HREFCBLK | 0   | HREF output/CBLK output (VGA mode HREF/IT mode register switching)                               |

| 39      | SCANT    | Ι   | Test input (Normally connect to low.)                                                            |

| 40      | MINTEST  | Ι   | Test input (Normally connect to low.)                                                            |

| 41      | FVR      | Ι   | Frequency control DC input                                                                       |

| 42      | LPFI     | Ι   | Low-pass filter analog switch input                                                              |

| 43      | VCXO     | 0   | Analog switch output. LC oscillator                                                              |

| 44      | DAVDD2   | VDD | D/A converter power supply                                                                       |

| 45      | DAVSS2   | VSS | D/A converter ground                                                                             |

| 46      | GSIG     | 0   | Video signal output (composite/luminance signal/G signal)                                        |

|         |          |     | (Connect R <sub>L</sub> between this pin and DAVSS2.)                                            |

| 47      | COMP1    | Ι   | Phase compensation (Connect a 1 µF capacitor between this pin and DAVSS2.)                       |

| 48      | IREF1    | Ι   | Bias current setting resistor connection (Connect R <sub>IREF</sub> between this pin and DAVSS2. |

| 49      | VREF1    | Ι   | Reference voltage input                                                                          |

| 50      | RSIG     | 0   | Video signal output (R signal)                                                                   |

| 51      | DAVDD1   | VDD | D/A converter power supply                                                                       |

| 52      | DAVSS1   | VSS | D/A converter ground                                                                             |

| 53      | BSIG     | 0   | Video signal output (Chrominance signal/B signal)                                                |

| 54      | COMP23   | Ι   | Phase compensation (Connect a 1 µF capacitor between this pin and DAVSS1.)                       |

| 55      | IREF23   | Ι   | Bias current setting resistor connection (Connect RIREF between this pin and DAVSS1.             |

| 56      | VREF23   | Ι   | Reference voltage input                                                                          |

| 57      | VREFH    | Ι   | High-level reference voltage input                                                               |

| 58      | VREFHM   | Ι   | Mid-level reference voltage (Connect this pin to ADVSS through a capacitor.)                     |

| 59      | VREFM    | Ι   | Mid-level reference voltage (Connect this pin to ADVSS through a capacitor.)                     |

| 60      | ADVSS    | VSS | A/D converter ground                                                                             |

| 61      | ADVDD    | VDD | A/D converter power supply                                                                       |

| 62      | VREFML   | Ι   | Mid-level reference voltage (Connect this pin to ADVSS through a capacitor.)                     |

| 63      | VREFL    | Ι   | Low-level reference voltage input                                                                |

| 64      | VIN      | Ι   | Analog signal input                                                                              |

| 65      | TEST4    | Ι   | Test input (Normally connect to low.)                                                            |

| 66      | TEST3    | Ι   | Test input (Normally connect to low.)                                                            |

| 67      | TEST2    | Ι   | Test input (Normally connect to low.)                                                            |

| 68      | TEST1    | Ι   | Test input (Normally connect to low.)                                                            |

| 69      | TEST0    | Ι   | Test input (Normally connect to low.)                                                            |

| 70      | CCDSEL0  | Ι   | CCD switching                                                                                    |

| 71      | CCDSEL1  | Ι   | CCD switching                                                                                    |

# ■ Pin Descriptions (continued)

| Pin No. | Pin     | I/O | Description                                                                       |

|---------|---------|-----|-----------------------------------------------------------------------------------|

| 72      | CCDSEL2 | Ι   | CCD switching                                                                     |

| 73      | RESET   | Ι   | Logic system initial reset                                                        |

| 74      | SDA     | I/O | I <sup>2</sup> C-bus (data)                                                       |

| 75      | SCL     | I/O | I <sup>2</sup> C-bus (clock)                                                      |

| 76      | A0      | Ι   | EEPROM address setting (pulled down)                                              |

| 77      | A1      | Ι   | EEPROM address setting (pulled down)                                              |

| 78      | A2      | Ι   | EEPROM address setting (pulled down)                                              |

| 79      | VDD2    | VDD | Digital system power supply (3.3 V)                                               |

| 80      | VSS2    | VSS | Digital system ground                                                             |

| 81      | PWM0    | 0   | PWM signal output                                                                 |

| 82      | PWM1    | 0   | PWM signal output                                                                 |

| 83      | PWM2    | 0   | PWM signal output                                                                 |

| 84      | PWM3    | 0   | PWM signal output                                                                 |

| 85      | YUV0    | 0   | Digital Y/UV output (LSB)                                                         |

| 86      | YUV1    | 0   | Digital Y/UV output                                                               |

| 87      | YUV2    | 0   | Digital Y/UV output                                                               |

| 88      | YUV3    | 0   | Digital Y/UV output                                                               |

| 89      | YUV4    | 0   | Digital Y/UV output                                                               |

| 90      | YUV5    | 0   | Digital Y/UV output                                                               |

| 91      | YUV6    | 0   | Digital Y/UV output                                                               |

| 92      | YUV7    | 0   | Digital Y/UV output (MSB)                                                         |

| 93      | VDD3    | VDD | Digital system power supply (3.3 V)                                               |

| 94      | VSS3    | VSS | Digital system ground                                                             |

| 95      | FCKO    | 0   | FCK output                                                                        |

| 96      | FCK2O   | 0   | 2FCK output                                                                       |

| 97      | COIN    | Ι   | Synchronization oscillator cell (LC oscillator)                                   |

| 98      | OBCTL   | 0   | OB automatic correction output                                                    |

| 99      | EXTAGC  | 0   | External AGC control                                                              |

| 100     | IRIS    | 0   | Mechanical iris fixation (PWM output)                                             |

| 101     | ALCELC  | Ι   | Fixed/ELC switching. Low: ELC, High: Fixed                                        |

| 102     | ATWLOCK | Ι   | ATW/Stop. Low: Normal, High: ATWLOCK                                              |

| 103     | APGAIN  | Ι   | Aperture gain switching. Low: Register value High: One half of the register value |

| 104     | BLCSW   | Ι   | Backlighting correction. Low: Normal, High: ATWLOCK                               |

| 105     | DIN8    | Ι   | Digital signal input (MSB)                                                        |

| 106     | DIN7    | Ι   | Digital signal input                                                              |

| 107     | DIN6    | Ι   | Digital signal input                                                              |

| 108     | DIN5    | Ι   | Digital signal input                                                              |

#### Pin Descriptions (continued)

| Pin No. | Pin     | I/O | Description                           |

|---------|---------|-----|---------------------------------------|

| 109     | DIN4    | Ι   | Digital signal input                  |

| 110     | VDD4    | VDD | Digital system power supply (3.3 V)   |

| 111     | VSS4    | VSS | Digital system ground                 |

| 112     | DIN3    | Ι   | Digital signal input                  |

| 113     | DIN2    | Ι   | Digital signal input                  |

| 114     | DIN1    | Ι   | Digital signal input                  |

| 115     | DIN0    | Ι   | Digital signal input (LSB)            |

| 116     | DS2     | 0   | CDS pulse 1                           |

| 117     | DS1     | 0   | CDS pulse 2                           |

| 118     | TESTDC2 | Ι   | Test input (Normally connect to low.) |

| 119     | TESTSW5 | Ι   | Test input (Normally connect to low.) |

| 120     | R       | 0   | \$\$ pulse                            |

| 121     | N.C.    | _   | _                                     |

| 122     | TGVDD   | VDD | TG power supply                       |

| 123     | TGVSS   | VSS | TG ground                             |

| 124     | N.C.    |     | —                                     |

| 125     | H2      | 0   | φH1 transfer pulse                    |

| 126     | N.C.    | _   | —                                     |

| 127     | H1      | 0   | φH2 transfer pulse                    |

| 128     | N.C.    | _   | —                                     |

#### Electrical Characteristics

#### 1. Absolute Maximum Ratings

| Parameter                | Symbol           | Rating                        | Unit |

|--------------------------|------------------|-------------------------------|------|

| Supply voltage (digital) | V <sub>DD</sub>  | - 0.3 to +4.6                 | v    |

| Supply voltage (analog)  | AV <sub>DD</sub> | - 0.3 to +4.6                 | V    |

| Input voltage            | VI               | - 0.3 to V <sub>DD</sub> +0.3 | v    |

| Output voltage           | Vo               | - 0.3 to V <sub>DD</sub> +0.3 | v    |

| Output current           | I <sub>O</sub>   | ±48                           | mA   |

| Power dissipation        | P <sub>D</sub>   | 750                           | mW   |

| Operating temperature    | T <sub>opr</sub> | -20 to +70                    | °C   |

| Storage temperature      | T <sub>stg</sub> | -55 to +150                   | °C   |

Note) 1. The absolute maximum ratings are limit values for stresses applied to the chip so that the chip will not be destroyed. Operation is not guaranteed within these ranges.

2. Always apply the identical potential to the following pins: VDD1, VDD2, VDD3, VDD4, VDD5, VDDTG, ADVDD, DAVDD1, and DAVDD2.

Always apply the identical potential to the following pins: VSS1, VSS2, VSS3, VSS4, VSS5, VSSTG, ADVSS, DAVSS1, and DAVSS2.

### Electrical Characteristics (continued)

2. Recommended Operating Conditions at  $V_{SS} = TGV_{SS} = OSCV_{SS} = ADV_{SS} = DAV_{SS} = 0 V$

| Parameter                | Symbol             | Condition                   | Min | Тур | Max  | Unit |

|--------------------------|--------------------|-----------------------------|-----|-----|------|------|

| Supply voltage (digital) | V <sub>DD</sub>    | Digital system power supply | 3.0 | 3.3 | 3.6  | V    |

|                          | TGV <sub>DD</sub>  | TG power supply             | 3.0 | 3.3 | 3.6  |      |

|                          | OSCV <sub>DD</sub> | Oscillator power supply     | 3.0 | 3.3 | 3.6  |      |

| Supply voltage (analog)  | ADV <sub>DD</sub>  | A/D converter power supply  |     | 3.3 |      | V    |

|                          | DAV <sub>DD</sub>  | D/A converter power supply  |     | 3.3 |      |      |

| Operating frequency      | f <sub>osc</sub>   | duty 50%                    | 9.5 |     | 28.7 | MHz  |

# 3. DC Characteristics at $V_{DD} = TGV_{DD} = OSCV_{DD} = 3.0 \text{ V}$ to 3.6 V, $ADV_{DD} = DAV_{DD} = 3.0 \text{ V}$ to 3.6 V, $V_{SS} = TGV_{SS} = OSCV_{SS} = ADV_{SS} = DAV_{SS} = 0 \text{ V}$ , $T_a = -20^{\circ}C$ to $+70^{\circ}C$

| Parameter                | Symbol            | Condition                                              | Min | Тур | Max | Unit |

|--------------------------|-------------------|--------------------------------------------------------|-----|-----|-----|------|

| Operating supply current | I <sub>DD</sub>   | $V_{DD} = TGV_{DD} = OSCV_{DD} = 3.6 V,$               | —   | 80  | 120 | mA   |

|                          | DAI <sub>DD</sub> | $ADV_{DD} = DAV_{DD} = 3.6 V,$                         | —   | 23  | 33  |      |

|                          | ADI <sub>DD</sub> | $f_{CLK} = 28.7 \text{ MHz}, T_a = 25^{\circ}\text{C}$ |     | 20  | 40  |      |

#### Input pins 1-1: Standard input pins LLDET, EXTINO, EXTIN1, YUVOE, CCDSEL0 to CCDSEL2, RESET, COIN, ALCELC, ATWLOCK, APGAIN, BLCSW, DIN8 to DIN0, TESTDC2, TESTSW5

|                   | ,                           | ,                 |                                          |                     |          |                     |          |

|-------------------|-----------------------------|-------------------|------------------------------------------|---------------------|----------|---------------------|----------|

| Input voltage     | High level                  | V <sub>IH</sub>   |                                          | $V_{DD} \times 0.8$ |          | V <sub>DD</sub>     | V        |

|                   | Low level                   | V <sub>IL</sub>   |                                          | 0                   |          | $V_{DD} \times 0.2$ |          |

| Input leakage cu  | irrent                      | I <sub>LIPD</sub> | $V_I = V_{DD}$ or $V_{SS}$               | -5                  |          | 5                   | μΑ       |

| 2) Input pins 1   | -2: Pulled-up ir            | nput pins         | FLC, EXTMOD                              |                     |          |                     |          |

| Input voltage     | High level                  | V <sub>IH</sub>   |                                          | $V_{DD} \times 0.8$ |          | V <sub>DD</sub>     | V        |

|                   | Low level                   | V <sub>IL</sub>   |                                          | 0                   |          | $V_{DD} \times 0.2$ |          |

| Input leakage cu  | irrent                      | I <sub>LIPD</sub> | $V_I = V_{DD}$                           | -10                 |          | 10                  | μA       |

| Pull-up resistant | ce                          | R <sub>PU1</sub>  | $V_{DD} = 3.3 \text{ V}, V_{I} = V_{SS}$ | 10                  | 30       | 90                  | kΩ       |

| 3) Input pins 1   | -3: Pulled-down             | input pir         | ns TESTDC1, NTPL, SCAN                   | NT, A0 to A         | 2, MINTE | ST, TEST4           | to TEST0 |

| Input voltage     | High level                  | V <sub>IH</sub>   |                                          | $V_{DD} \times 0.8$ |          | V <sub>DD</sub>     | V        |

|                   | Low level                   | V <sub>IL</sub>   |                                          | 0                   |          | $V_{DD} \times 0.2$ |          |

| Input leakage cu  | irrent                      | I <sub>LIPD</sub> | $V_I = V_{SS}$                           | -10                 |          | 10                  | μΑ       |

| Pull-down resist  | ance                        | R <sub>PD1</sub>  | $V_I = V_{DD}$                           | 10                  | 30       | 90                  | kΩ       |

| 4) Output pins    | 5 1-1 V4 to V1,<br>OBCTL, I |                   | 12, CH1, OSCCNT, WHD, CPC<br>, IRIS      | OB, PBLK, I         | HCLR, PC | O, PWM0 to          | o PWM3,  |

| Output voltage    | High level                  | V <sub>OH</sub>   | $I_0 = -1 \text{ mA}$                    | $V_{DD} - 0.6$      | _        | —                   | V        |

|                   | Low level                   | V <sub>OL</sub>   | $I_0 = 1 \text{ mA}$                     | _                   |          | 0.4                 |          |

| 5) Output pins    | 1-2 YUV0                    | to YUV            | 7                                        |                     |          |                     |          |

| Output voltage    | High level                  | V <sub>OH</sub>   | $I_0 = -2 \text{ mA}$                    | $V_{DD} - 0.6$      |          | _                   | V        |

|                   | Low level                   | V <sub>OL</sub>   | $I_0 = 2 \text{ mA}$                     | _                   |          | 0.4                 |          |

## Electrical Characteristics (continued)

3. DC Characteristics at  $V_{DD} = TGV_{DD} = OSCV_{DD} = 3.0 \text{ V}$  to 3.6 V,  $ADV_{DD} = DAV_{DD} = 3.0 \text{ V}$  to 3.6 V,  $V_{SS} = TGV_{SS} = OSCV_{SS} = ADV_{SS} = DAV_{SS} = 0 \text{ V}$ .  $T_{a} = -20^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  (continued)

| $V_{SS} = TGV_{SS}$ | $_{\rm S} = {\rm OSCV}_{\rm SS} = \lambda$ | ADV <sub>SS</sub> = | $DAV_{SS} = 0 V$ , $T_a = -20^{\circ}C$ to          | +70°C (cor     | ntinued) |      |      |

|---------------------|--------------------------------------------|---------------------|-----------------------------------------------------|----------------|----------|------|------|

| Parameter           |                                            | Symbol              | Condition                                           | Min            | Тур      | Max  | Unit |

| 6) Output pins      | 1-3 VCSY                                   | NCVD, F             | IREFCBLK                                            |                |          |      |      |

| Output voltage      | High level                                 | V <sub>OH</sub>     | $I_0 = -4 \text{ mA}$                               | $V_{DD} - 0.6$ |          | —    | V    |

|                     | Low level                                  | V <sub>OL</sub>     | $I_0 = 4 \text{ mA}$                                |                | _        | 0.4  |      |

| 7) Output pins      | 1-4 FVD,                                   | FWHD, F             | CKO, FCK2O                                          |                |          |      |      |

| Output voltage      | High level                                 | V <sub>OH</sub>     | $I_0 = -8 \text{ mA}$                               | $V_{DD} - 0.6$ |          |      | V    |

|                     | Low level                                  | V <sub>OL</sub>     | $I_0 = 8 \text{ mA}$                                |                |          | 0.4  |      |

| 8) Output pins      | 1-5 DS2, I                                 | DS1, R, H           | 2, H1                                               | L              |          |      |      |

| Output voltage      | High level                                 | V <sub>OH</sub>     | $I_0 = -16 \text{ mA}$                              | $V_{DD} - 0.6$ |          |      | V    |

|                     | Low level                                  | V <sub>OL</sub>     | $I_0 = 16 \text{ mA}$                               |                |          | 0.4  |      |

| 9) I/O pins 1       | SDA, SCL                                   |                     |                                                     |                |          |      |      |

| TTL                 | Input                                      | V <sub>T+</sub>     | $V_{DD} = 3.0 \text{ V}$ to 3.6 V                   |                | 1.6      | 2.2  | V    |

| Schmitt trigger     | threshold                                  |                     | $V_{ref5} = 4.75 V$ to 5.25 V                       |                |          |      |      |

| input voltage       | voltage                                    | V <sub>T</sub> -    | $(V_{ref5}$ is an external reference voltage.)      | 0.6            | 1.2      |      |      |

| Output voltage      | Low level                                  | V <sub>OL</sub>     | $I_0 = 4 \text{ mA}$                                |                |          | 0.4  | V    |

| Output leakage      | current                                    | ILO                 | $V_0 = V_{DD}$ or $V_{SS}$                          | -10            |          | 10   | μΑ   |

| 10) Oscillator p    | oins 1 CXII                                | N, CXOU             | Т                                                   |                |          |      |      |

| Standard oscilla    | tor frequency                              | f <sub>OSC</sub>    | $V_{DD} = 3.3 \text{ V}$ , with an external crystal | 15             |          | 30   | MHz  |

| Internal feedbac    | k resistance                               | R <sub>FB</sub>     | $V_{DD} = 3.3 V$                                    | 0.73           | 2.2      | 6.6  | kΩ   |

|                     | 1                                          |                     | $V_{I}(X_{I}) = V_{DD} \text{ or } V_{SS}$          |                |          |      |      |

| Output current      | High level                                 | I <sub>OH</sub>     | $V_{DD} = 3.3 V$                                    | -57.5          | -23      | -9.2 | mA   |

|                     |                                            |                     | $V_I = V_{SS}$ , $V_O = V_{SS}$                     |                |          |      |      |

|                     | Low level                                  | I <sub>OL</sub>     | $V_{DD} = 3.3 V$ $V_{DD} = V_{DD} = V_{DD}$         | 9.6            | 24       | 60   |      |

|                     |                                            |                     | $V_{I} = V_{DD}, V_{O} = V_{DD}$                    |                |          |      |      |

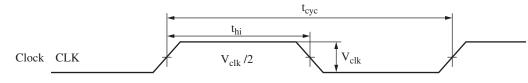

#### 4. AC Characteristics

| Parameter      |            | Symbol           | Condition                                    | Min  | Тур | Max   | Unit |

|----------------|------------|------------------|----------------------------------------------|------|-----|-------|------|

| Input pins 2-1 | CXIN       |                  |                                              |      |     |       |      |

| Clock waveform | Period     | t <sub>cyc</sub> | See figure 1                                 | 34.8 |     | 105.3 | ns   |

|                | Clock duty | d <sub>clk</sub> | See figure 1<br>$d_{clk} = t_{hi} / t_{cyc}$ |      | 50  |       | %    |

Figure 1. Clock waveform

| Electrical Characteristics | (continued) |

|----------------------------|-------------|

|----------------------------|-------------|

5. A/D converter at  $V_{DD} = TGV_{DD} = OSCV_{DD} = 3.3 V$ ,  $ADV_{DD} = DAV_{DD} = 3.3 V$ ,

$V_{SS} = TGV_{SS} = OSCV_{SS} = ADV_{SS} = DAV_{SS} = 0 V, T_a = 25^{\circ}C$

Pins: VIN, VREFH, VREFL, VREFM, VREFHM

| Parameter                             | Symbol                                            | Condition                     | Min   | Тур  | Max   | Unit |  |  |  |

|---------------------------------------|---------------------------------------------------|-------------------------------|-------|------|-------|------|--|--|--|

| 1) A/D converter recommend            | 1) A/D converter recommended operating conditions |                               |       |      |       |      |  |  |  |

| Analog input voltage                  | V <sub>AIN</sub>                                  | VIN                           | VREFL | _    | VREFH | v    |  |  |  |

| Analog input pin capacitance          | C <sub>AI</sub>                                   | VIN                           | _     | 330  |       | pF   |  |  |  |

| High-level reference voltage          | V <sub>REFH</sub>                                 | VREFH                         | —     | 2.5  | —     | V    |  |  |  |

| Low-level reference voltage           | V <sub>REFL</sub>                                 | VREFL                         | —     | 0.5  | _     | v    |  |  |  |

| Reference resistance (VREFL to VREFH) | R <sub>REF</sub>                                  |                               | —     | 440  |       | Ω    |  |  |  |

| 2) A/D converter characteristics      |                                                   |                               |       |      |       |      |  |  |  |

| Resolution                            | R <sub>ES</sub>                                   |                               |       |      | 10    | bit  |  |  |  |

| Nonlinearity error                    | INL                                               | $f_{ADCK} = 14.3 \text{ MHz}$ |       | ±5.0 | ±7.5  | LSB  |  |  |  |

| Nonlinearity error              | INL              | $f_{ADCK} = 14.3 \text{ MHz}$     |   | ±5.0 | ±7.5                | LSB    |

|---------------------------------|------------------|-----------------------------------|---|------|---------------------|--------|

| Differential nonlinearity error | DNL              | $V_{\text{REFH}} = 2.5 \text{ V}$ |   | ±2.0 | ±6.5                | LSB    |

|                                 |                  | $V_{REFL} = 0.5 V$                |   |      |                     |        |

| Analog input dynamic range      | V <sub>AIN</sub> |                                   | _ |      | V <sub>REFH</sub> – | V[p-p] |

|                                 |                  |                                   |   |      | V <sub>REFL</sub>   |        |

6. D/A converter at  $V_{DD} = TGV_{DD} = OSCV_{DD} = 3.3 \text{ V}$ ,  $ADV_{DD} = DAV_{DD} = 3.3 \text{ V}$ ,  $V_{SS} = TGV_{SS} = OSCV_{SS} = ADV_{SS} = DAV_{SS} = 0 \text{ V}$ ,  $T_a = 25^{\circ}C$

1) Pins: VREF23, IREF23, COMP23, BSIG, RSIG

| Parameter                              | Symbol            | Condition                                                                                    | Min | Тур  | Max  | Unit |

|----------------------------------------|-------------------|----------------------------------------------------------------------------------------------|-----|------|------|------|

| (1) D/A converter recomme              | ended op          | erating conditions                                                                           |     |      |      |      |

| Reference voltage                      | VREF              | $R_{L} = 75 \Omega$<br>RIREF23 = 820 $\Omega$                                                |     | 1.37 | _    | V    |

| External phase compensation capacitor  | C <sub>COMP</sub> | Connected between COMP23 and $AV_{DD}$ .                                                     |     | 1.0  | _    | μF   |

| External output resistors              | R <sub>L</sub>    | Connect output resistors<br>between each of the BSIG<br>and RSIG pins and AV <sub>SS</sub> . | _   | 75   |      | Ω    |

| External bias current setting resistor | R <sub>IREF</sub> | Connect this resistor between IREF23 and $AV_{SS}$ .                                         |     | 820  | _    | Ω    |

| (2) D/A converter characte             | ristics           |                                                                                              |     |      |      |      |

| Resolution                             | R <sub>ES</sub>   |                                                                                              |     |      | 8    | bit  |

| Nonlinearity error                     | INL               | $R_L = 75 \Omega$                                                                            | _   |      | ±2.5 | LSB  |

| Differential nonlinearity error        | DNL               | VREF23 = 1.37 V<br>RIREF23 = 820 Ω                                                           | _   |      | ±2.5 | LSB  |

| Full-scale voltage                     | V <sub>OFS</sub>  |                                                                                              |     | 1.0  |      | V    |

| Zero-scale voltage                     | V <sub>OZS</sub>  |                                                                                              | _   | 0    | _    | V    |

### MN6732741

### Electrical Characteristics (continued)

6. D/A converter at  $V_{DD} = TGV_{DD} = OSCV_{DD} = 3.3 \text{ V}$ ,  $ADV_{DD} = DAV_{DD} = 3.3 \text{ V}$ ,

$V_{SS} = TGV_{SS} = OSCV_{SS} = ADV_{SS} = DAV_{SS} = 0 V$ ,  $T_a = 25^{\circ}C$  (continued)

2) Pins: VREF1, IREF1, COMP1, GSIG

| Parameter                                          | Symbol            | Condition                                                                      | Min | Тур  | Мах  | Unit |  |

|----------------------------------------------------|-------------------|--------------------------------------------------------------------------------|-----|------|------|------|--|

| (1) D/A converter recommended operating conditions |                   |                                                                                |     |      |      |      |  |

| Reference voltage                                  | VREF              | $\begin{aligned} R_L &= 75 \ \Omega \\ RIREF1 &= 1.13 \ k\Omega \end{aligned}$ |     | 1.5  |      | V    |  |

| External phase compensation capacitor              | C <sub>COMP</sub> | Connect between COMP1 and $AV_{DD}$ .                                          |     | 1.0  |      | μF   |  |

| External output resistor                           | R <sub>L</sub>    | Connect an output resistor between GSIG and $AV_{SS}$ .                        |     | 75   |      | Ω    |  |

| External bias current setting resistor             | R <sub>IREF</sub> | Connect this resistor between IREF1 and $AV_{SS}$ .                            |     | 1.13 |      | kΩ   |  |

| (2) D/A converter characteristics                  |                   |                                                                                |     |      |      |      |  |

| Resolution                                         | R <sub>ES</sub>   |                                                                                |     |      | 10   | bit  |  |

| Nonlinearity error                                 | INL               | $R_L = 75 \Omega$                                                              | _   |      | ±2.5 | LSB  |  |

| Differential nonlinearity error                    | DNL               | VREF1 = 1.5 V<br>RIREF1 = 1.13 k $\Omega$                                      |     |      | ±2.5 | LSB  |  |

| Full-scale voltage                                 | V <sub>OFS</sub>  |                                                                                |     | 1.0  |      | V    |  |

| Zero-scale voltage                                 | V <sub>OZS</sub>  |                                                                                |     | 0    |      | V    |  |

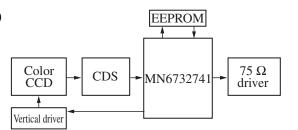

#### Application System Examples

- 1. Example A (Minimum configuration)

- Internal synchronization

- Composite video output

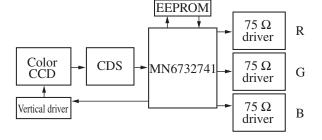

- 2. Example B

- Internal synchronization

- RGB output

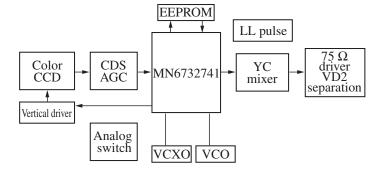

- 3. Example C (Surveillance camera)

- External synchronization

- YC output

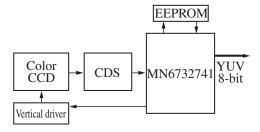

- 4. Example D (PC camera)

- Internal synchronization

- Digital output

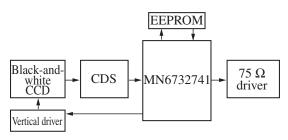

- 5. Example E

- Internal synchronization

- Y output

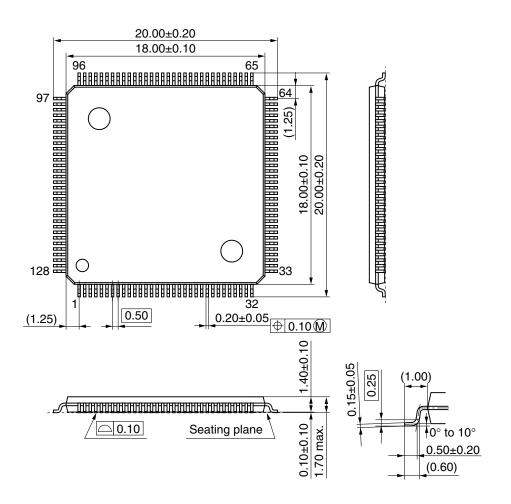

- Package Dimensions (Units: mm)

- LQFP128-P-1818C

## Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this material are subject to change without notice for reasons of modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.

- (6) When using products for which dry packing is required, observe the conditions (including shelf life and after-unpacking standby time) agreed upon when specification sheets are individually exchanged.

- (7) No part of this material may be reprinted or reproduced by any means without written permission from our company.

### Please read the following notes before using the datasheets

A. These materials are intended as a reference to assist customers with the selection of Panasonic semiconductor products best suited to their applications.

Due to modification or other reasons, any information contained in this material, such as available product types, technical data, and so on, is subject to change without notice.

Customers are advised to contact our semiconductor sales office and obtain the latest information before starting precise technical research and/or purchasing activities.

- B. Panasonic is endeavoring to continually improve the quality and reliability of these materials but there is always the possibility that further rectifications will be required in the future. Therefore, Panasonic will not assume any liability for any damages arising from any errors etc. that may appear in this material.

- C. These materials are solely intended for a customer's individual use. Therefore, without the prior written approval of Panasonic, any other use such as reproducing, selling, or distributing this material to a third party, via the Internet or in any other way, is prohibited.