# MN8390-C

## LCD Panel Source Driver

### ■ Overview

The MN8390-C is for displaying an analog video signal on a TFT color liquid crystal display panel in such applications as LCD television sets and video cameras.

### ■ Features

- Lower power consumption and reduced EMI emissions owing to digital 3.0 volt power supply and analog 5.0 volt power supply

- Broad dynamic range of 4.6 V (for power supply voltage of 5.0 V)

- Low discrepancies between output pins:  $\pm 20$  mV (typ.)

- 240 output channels

- Support for striped and delta panel layouts by switching analog (R, G, B) signals

- Support for sequential sampling mode (with CLK1 to CLK3 inputs)

- Support for serial cascade connections

- Automatic clock suspension after reading specified amount of data

- Choice of shift register shift directions (right/left)

### ■ Applications

- LCD television sets and video cameras

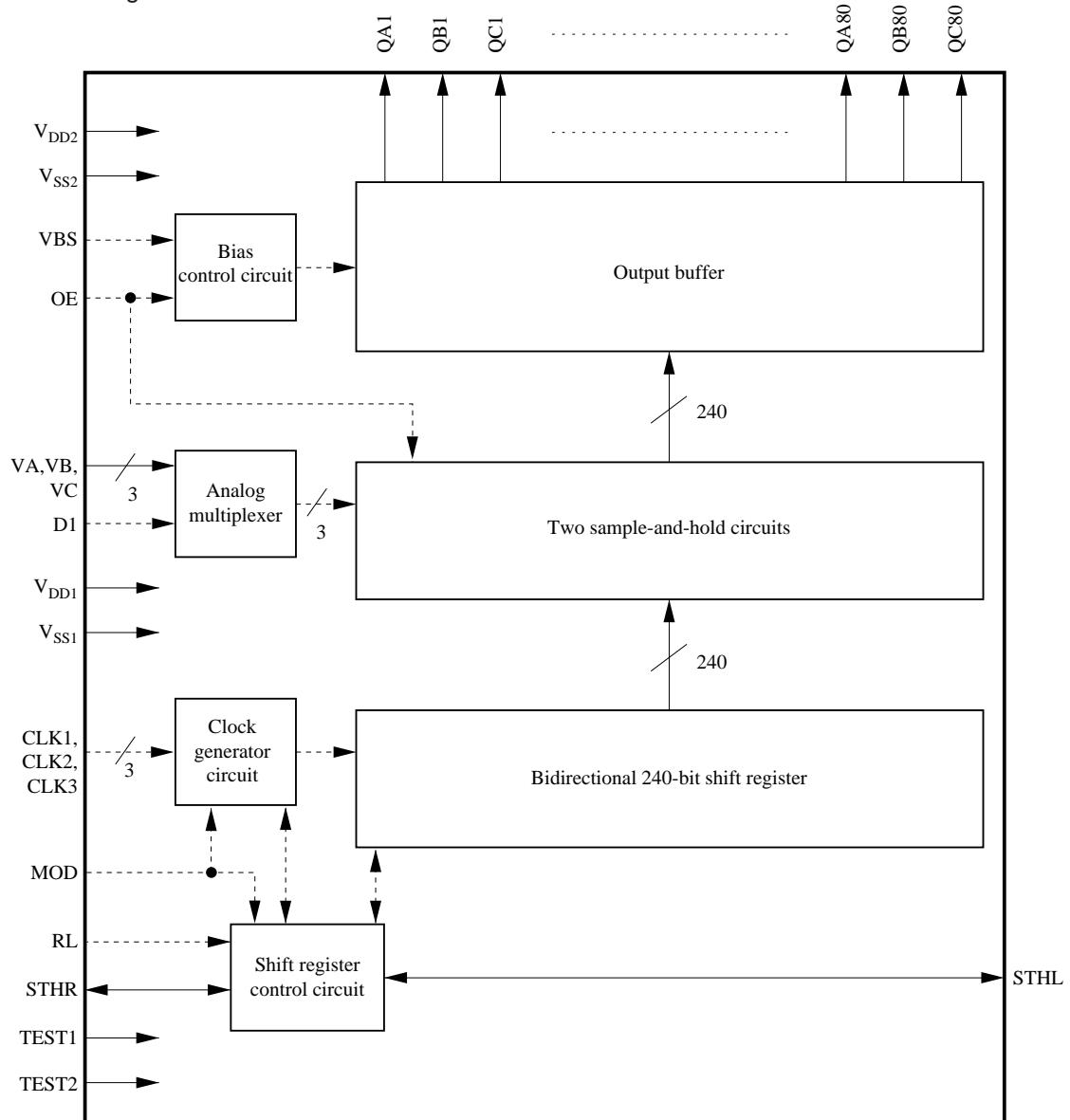

## ■ Block Diagram

## ■ Pin Descriptions

| Pin No.                          | Symbol       | Pin Name                | I/O | Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

|----------------------------------|--------------|-------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|--------|---|-------|-------------|----|-------------|-------|-------------|---|----|-------------|----|-------------|----|-------------|

| 99 to 102<br>21 to 24            | STHR<br>STHL | Shift data I/O          | I/O | <p>These are I/O pins for the bidirectional shift register. The RL pin controls their I/O directions.</p> <table border="1"> <tr> <td>RL</td><td>STHR</td><td>STHL</td></tr> <tr> <td>H</td><td>Input</td><td>Output</td></tr> <tr> <td>L</td><td>Output</td><td>Input</td></tr> </table> <p>(1) Input<br/>The pins provide input data to the shift register's first stage. The shift register reads in this data at the rising edge of the CLK1 signal.</p> <p>(2) Output<br/>In a cascade connection, the pins provide the data for the synchronizing output stage synchronized with the rising edge of the CLK1 signal.</p> | RL | STHR  | STHL   | H | Input | Output      | L  | Output      | Input |             |   |    |             |    |             |    |             |

| RL                               | STHR         | STHL                    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

| H                                | Input        | Output                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

| L                                | Output       | Input                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

| 27 to 30                         | RL           | Shift direction control | I   | <p>This pin controls the shift direction for the bidirectional shift register.</p> <p>RL="H" : QA1→QB1→QC1→→QC80<br/>RL="L" : QC80→QB80→QA80→→QA1</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

| 42 to 45<br>37 to 40<br>32 to 35 | CLK1 to 3    | Clock input             | I   | <p>These pins provide the shift clock signals that the sample-and-hold circuits use to generate the data for the LCD drive output pins (QA1-QC80).</p> <p>The following lists the relationships between these clock signals and the output pins.</p> <p>CLK1 RL="H": QA1 to QA80<br/>RL="L": QC1 to QC80<br/>CLK2: QB1 to QB80<br/>CLK3 RL="H": QC1 to QC80<br/>RL="L": QA1 to QA80</p>                                                                                                                                                                                                                                        |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

| 70 to 73                         | OE           | Output enable           | I   | <p>At each rising edge of this signal, the MN8390-C switches between its two sample-and-hold circuits and initiates output of new data. When the outputs reach the drive potential, the MN8390-C automatically reduces the drive power, but maintains the outputs at the drive potential.</p>                                                                                                                                                                                                                                                                                                                                  |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

| 47 to 50                         | D1           | Analog signal switching | I   | <p>This pin controls the mapping between the three analog inputs (VA, VB, and VC) and the drive outputs (QA, QB, and QC).</p> <table border="1"> <tr> <td>D1</td><td>Input</td><td>Output</td></tr> <tr> <td rowspan="3">L</td><td>VA</td><td>QA1 to QA80</td></tr> <tr> <td>VB</td><td>QB1 to QB80</td></tr> <tr> <td>VC</td><td>QC1 to QC80</td></tr> <tr> <td rowspan="3">H</td><td>VA</td><td>QB1 to QB80</td></tr> <tr> <td>VB</td><td>QC1 to QC80</td></tr> <tr> <td>VC</td><td>QA1 to QA80</td></tr> </table>                                                                                                           | D1 | Input | Output | L | VA    | QA1 to QA80 | VB | QB1 to QB80 | VC    | QC1 to QC80 | H | VA | QB1 to QB80 | VB | QC1 to QC80 | VC | QA1 to QA80 |

| D1                               | Input        | Output                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

| L                                | VA           | QA1 to QA80             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

|                                  | VB           | QB1 to QB80             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

|                                  | VC           | QC1 to QC80             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

| H                                | VA           | QB1 to QB80             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

|                                  | VB           | QC1 to QC80             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

|                                  | VC           | QA1 to QA80             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |        |   |       |             |    |             |       |             |   |    |             |    |             |    |             |

## ■ Pin Descriptions

| Pin No.    | Symbol           | Pin Name                          | I/O | Function Description                                                                                                 |

|------------|------------------|-----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------|

| 93 to 97   | VBS              | Bias adjustment                   | I   | The voltage applied to this pin adjusts the output buffer bias and thus the drive capacity of the LCD drive outputs. |

| 87 to 91   | VA               | Analog signal                     | I   | These pins accept the analog signal inputs for routing to the LCD drive outputs.                                     |

| 81 to 85   | VB               | input                             |     |                                                                                                                      |

| 75 to 79   | VC               |                                   |     |                                                                                                                      |

| 147, 149   | QA1 to 80        | LCD drive                         | O   | These pins yield the levels obtained by applying the sample-and-hold circuits to the analog inputs (VA, VB, and VC). |

| 151 to 385 | QB1 to 80        | output                            |     |                                                                                                                      |

| 387, 389   | QC1 to 80        |                                   |     |                                                                                                                      |

| 391        |                  |                                   |     |                                                                                                                      |

| 52         | MOD              | Mode selection signal input       | I   | Connect this pin to V <sub>SS1</sub> for sequential sampling mode.                                                   |

| 62         | TEST1            | Test input                        | I   | Connect this pin to V <sub>DD1</sub> .                                                                               |

| 61         | TEST2            | Test input                        | I   | Connect this pin to V <sub>DD1</sub> .                                                                               |

| 63 to 68   | V <sub>DD1</sub> | Power supply for digital circuits | —   | These pins supply the driving potential for the logic and other digital circuits.                                    |

| 9 to 18    | V <sub>DD2</sub> | Power supply for analog circuits  | —   | These pins supply the driving potential for the sample-and-hold and other analog circuits.                           |

| 105 to 114 |                  |                                   |     |                                                                                                                      |

| 53 to 58   | V <sub>SS1</sub> | Ground for digital circuits       | —   | These pins supply the ground potential for the logic and other digital circuits.                                     |

| 127 to 142 | V <sub>SS2</sub> | Ground for analog circuits        | —   | These pins supply the ground potential for the sample-and-hold and other analog circuits.                            |

| 396 to 409 |                  |                                   |     |                                                                                                                      |