# MP03XXX360

## Dual Thyristor, Thyristor/Diode Module

Replaces January 2000 version, DS4484-5.0

DS4484-6.1 June 2001

### FEATURES

- Dual Device Module

- Electrically Isolated Package

- Pressure Contact Construction

- International Standard Footprint

- Alumina (Non Toxic) Isolation Medium

### APPLICATIONS

- Motor Control

- Controlled Rectifier Bridges

- Heater Control

- AC Phase Control

### VOLTAGE RATINGS

| Type Number   | Repetitive Peak Voltages<br>$V_{DRM}$ $V_{RRM}$<br>V | Conditions                                  |

|---------------|------------------------------------------------------|---------------------------------------------|

| MP03XXX360-18 | 1800                                                 | $T_{vj} = 0^\circ$ to $125^\circ\text{C}$ , |

| MP03XXX360-16 | 1600                                                 | $I_{DRM} = I_{RRM} = 30\text{mA}$           |

| MP03XXX360-14 | 1400                                                 | $V_{DSM} = V_{RSM} =$                       |

| MP03XXX360-12 | 1200                                                 | $V_{DSM} = V_{RSM} + 100\text{V}$           |

| MP03XXX360-10 | 1000                                                 | respectively                                |

| MP03XXX360-08 | 800                                                  |                                             |

Lower voltage grades available.

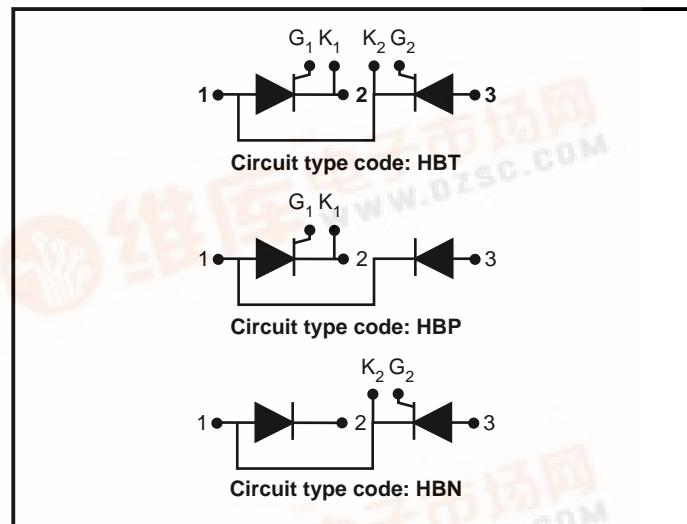

XXX shown in the part number above represents the circuit configuration required.

### ORDERING INFORMATION

Order As:

**MP03HBT360-XX**

**MP03HBN360-XX**

**MP03HBP360-XX**

XX shown in the part number above represents the  $V_{RRM}/100$  selection required, e.g. MP03HBT360-17

Note: When ordering, please use the complete part number.

### KEY PARAMETERS

|                           |       |

|---------------------------|-------|

| $V_{DRM}$                 | 1800V |

| $I_{T(AV)}$               | 355A  |

| $I_{TSM}(\text{per arm})$ | 8100A |

| $V_{isol}$                | 3000V |

Fig. 1 Circuit diagrams

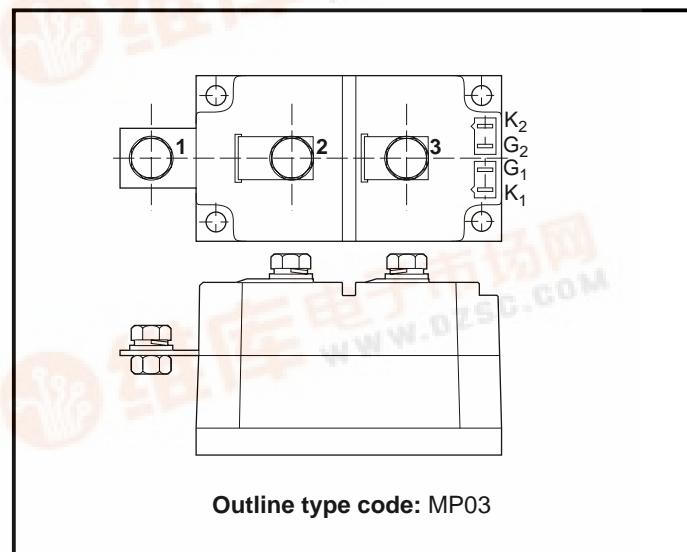

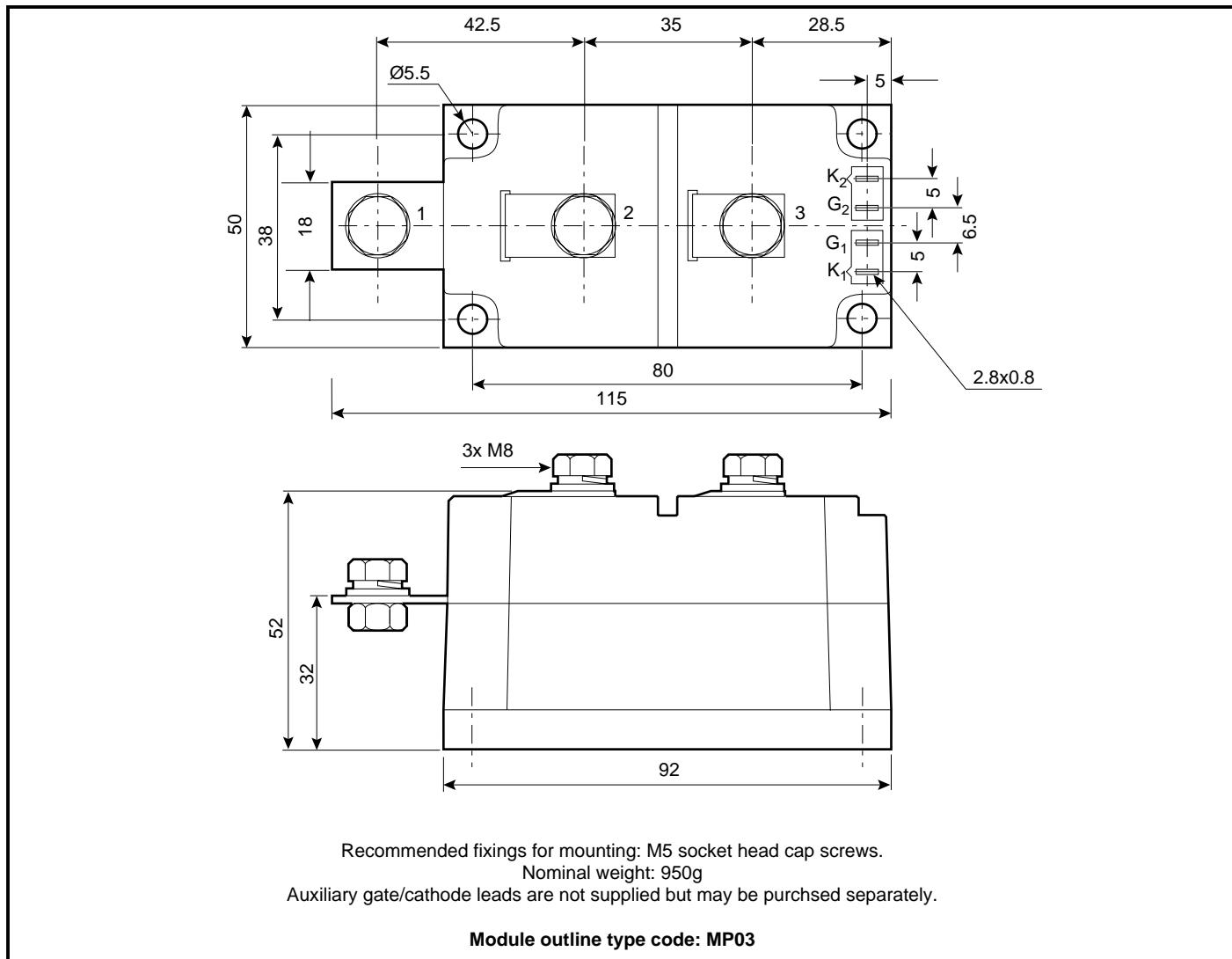

Outline type code: MP03

Fig. 2 Electrical connections - (not to scale)

**ABSOLUTE MAXIMUM RATINGS - PER ARM**

Stresses above those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. In extreme conditions, as with all semiconductors, this may include potentially hazardous rupture of the package. Appropriate safety precautions should always be followed. Exposure to Absolute Maximum Ratings may affect device reliability.

| Symbol       | Parameter                         | Test Conditions                                             | Max.                        | Units            |   |

|--------------|-----------------------------------|-------------------------------------------------------------|-----------------------------|------------------|---|

| $I_{T(AV)}$  | Mean on-state current             | Half wave resistive load                                    | $T_{case} = 75^\circ C$     | 355              | A |

|              |                                   |                                                             | $T_{case} = 85^\circ C$     | 312              | A |

|              |                                   |                                                             | $T_{heatsink} = 75^\circ C$ | 276              | A |

|              |                                   |                                                             | $T_{heatsink} = 85^\circ C$ | 242              | A |

| $I_{T(RMS)}$ | RMS value                         | $T_{case} = 75^\circ C$                                     | 560                         | A                |   |

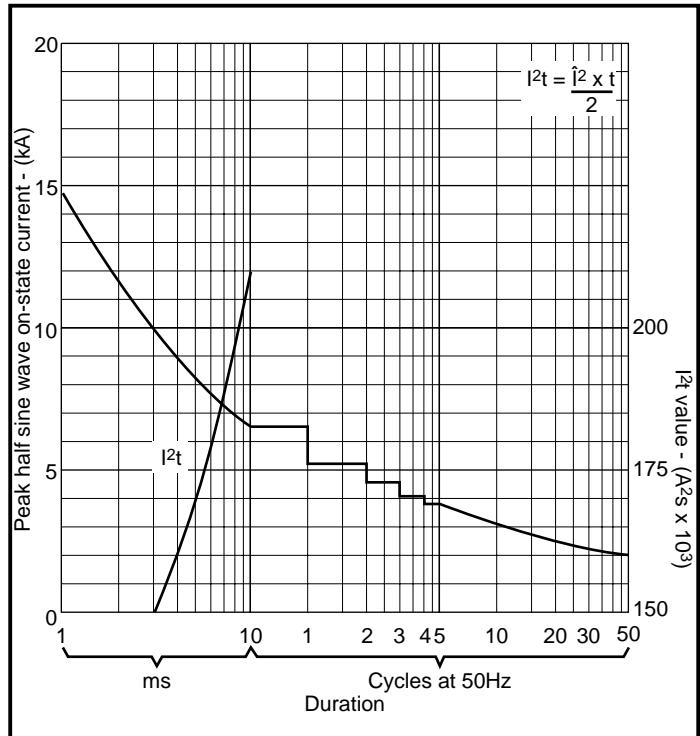

| $I_{TSM}$    | Surge (non-repetitive) on-current | 10ms half sine, $T_j = 130^\circ C$<br>$V_R = 0$            | 8.1                         | kA               |   |

| $I^2t$       | $I^2t$ for fusing                 |                                                             | 0.33x10 <sup>6</sup>        | A <sup>2</sup> s |   |

| $I_{TSM}$    | Surge (non-repetitive) on-current | 10ms half sine, $T_j = 130^\circ C$<br>$V_R = 50\% V_{DRM}$ | 6.5                         | kA               |   |

| $I^2t$       | $I^2t$ for fusing                 |                                                             | 0.21x10 <sup>6</sup>        | A <sup>2</sup> s |   |

| $V_{isol}$   | Isolation voltage                 | Commoned terminals to base plate.<br>AC RMS, 1 min, 50Hz    | 3000                        | V                |   |

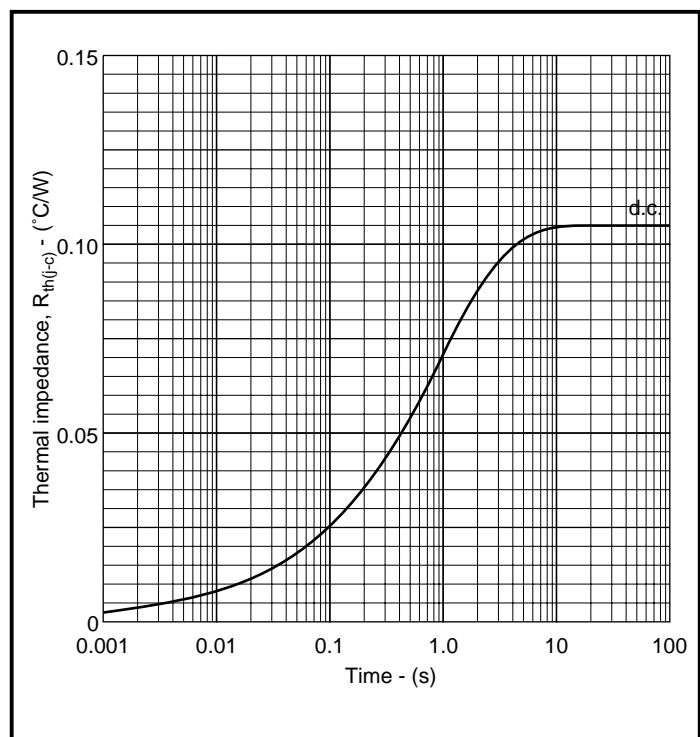

**THERMAL AND MECHANICAL RATINGS**

| Symbol         | Parameter                                                         | Test Conditions                                 | Min. | Max.  | Units       |

|----------------|-------------------------------------------------------------------|-------------------------------------------------|------|-------|-------------|

| $R_{th(j-c)}$  | Thermal resistance - junction to case<br>(per thyristor or diode) | dc                                              | -    | 0.105 | °C/kW       |

|                |                                                                   | Half wave                                       | -    | 0.115 | °C/kW       |

|                |                                                                   | 3 Phase                                         | -    | 0.12  | °C/kW       |

| $R_{th(c-hs)}$ | Thermal resistance - case to heatsink<br>(per thyristor or diode) | Mounting torque = 5Nm<br>with mounting compound | -    | 0.05  | °C/kW       |

| $T_{vj}$       | Virtual junction temperature                                      | Reverse (blocking)                              | -    | 135   | °C          |

| $T_{stg}$      | Storage temperature range                                         | -                                               | -40  | 135   | °C          |

| -              | Screw torque                                                      | Mounting - M5                                   | -    | 5(44) | Nm (lb.ins) |

|                |                                                                   | Electrical connections - M8                     | -    | 9(80) | Nm (lb.ins) |

| -              | Weight (nominal)                                                  | -                                               | -    | 950   | g           |

**DYNAMIC CHARACTERISTICS - THYRISTOR**

| Symbol            | Parameter                                | Test Conditions                                                                                  | Min. | Max. | Units      |

|-------------------|------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------------|

| $I_{RRM}/I_{DRM}$ | Peak reverse and off-state current       | At $V_{RRM}/V_{DRM}$ , $T_j = 130^\circ C$                                                       | -    | 50   | mA         |

| $dV/dt$           | Linear rate of rise of off-state voltage | To 67% $V_{DRM}$ , $T_j = 130^\circ C$                                                           | -    | 1000 | V/ $\mu$ s |

| $dl/dt$           | Rate of rise of on-state current         | From 67% $V_{DRM}$ to 600A, gate source 10V, 5 $\Omega$<br>$t_r = 0.5\mu$ s, $T_j = 130^\circ C$ | -    | 500  | A/ $\mu$ s |

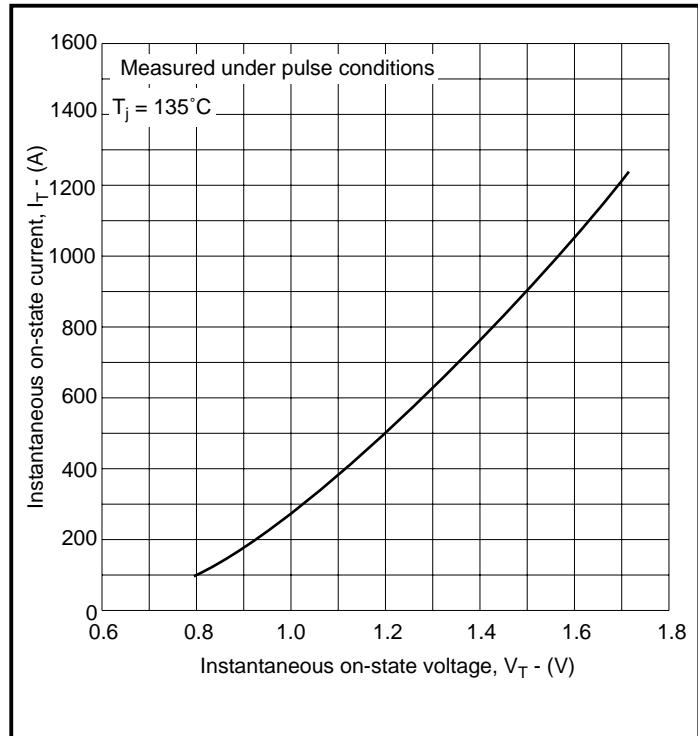

| $V_{T(TO)}$       | Threshold voltage                        | At $T_{vj} = 135^\circ C$ . See note 1                                                           | -    | 0.78 | V          |

| $r_T$             | On-state slope resistance                | At $T_{vj} = 135^\circ C$ . See note 1                                                           | -    | 0.79 | m $\Omega$ |

**Note 1:** The data given in this datasheet with regard to forward voltage drop is for calculation of the power dissipation in the semiconductor elements only. Forward voltage drops measured at the power terminals of the module will be in excess of these figures due to the impedance of the busbar from the terminal to the semiconductor.

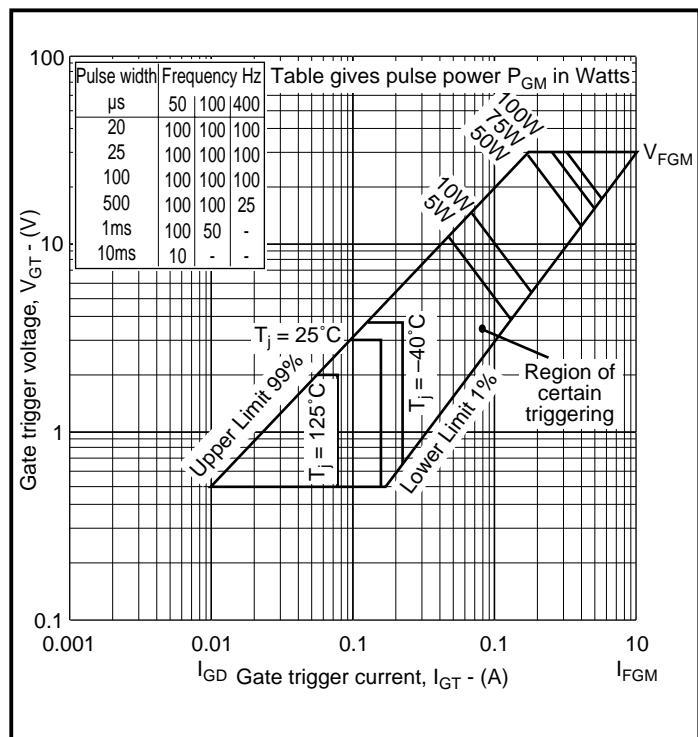

**GATE TRIGGER CHARACTERISTICS AND RATINGS**

| Symbol      | Parameter                 | Test Conditions                          | Max. | Units |

|-------------|---------------------------|------------------------------------------|------|-------|

| $V_{GT}$    | Gate trigger voltage      | $V_{DRM} = 5V$ , $T_{case} = 25^\circ C$ | 3    | V     |

| $I_{GT}$    | Gate trigger current      | $V_{DRM} = 5V$ , $T_{case} = 25^\circ C$ | 150  | mA    |

| $V_{GD}$    | Gate non-trigger voltage  | At $V_{DRM}$ $T_{case} = 125^\circ C$    | 0.25 | V     |

| $V_{FGM}$   | Peak forward gate voltage | Anode positive with respect to cathode   | 30   | V     |

| $V_{FGN}$   | Peak forward gate voltage | Anode negative with respect to cathode   | 0.25 | V     |

| $V_{RGM}$   | Peak reverse gate voltage | -                                        | 5    | V     |

| $I_{FGM}$   | Peak forward gate current | Anode positive with respect to cathode   | 10   | A     |

| $P_{GM}$    | Peak gate power           | See table fig. 5                         | 100  | W     |

| $P_{G(AV)}$ | Mean gate power           | -                                        | 5    | W     |

Fig. 3 Maximum (limit) on-state characteristics

Fig. 4 Surge (non-repetitive) on-state current vs time

(with 50%  $V_{RSM}$  at  $T_{case} = 130^\circ\text{C}$ )

Fig. 5 Gate characteristics

Fig. 6 Transient thermal impedance - dc

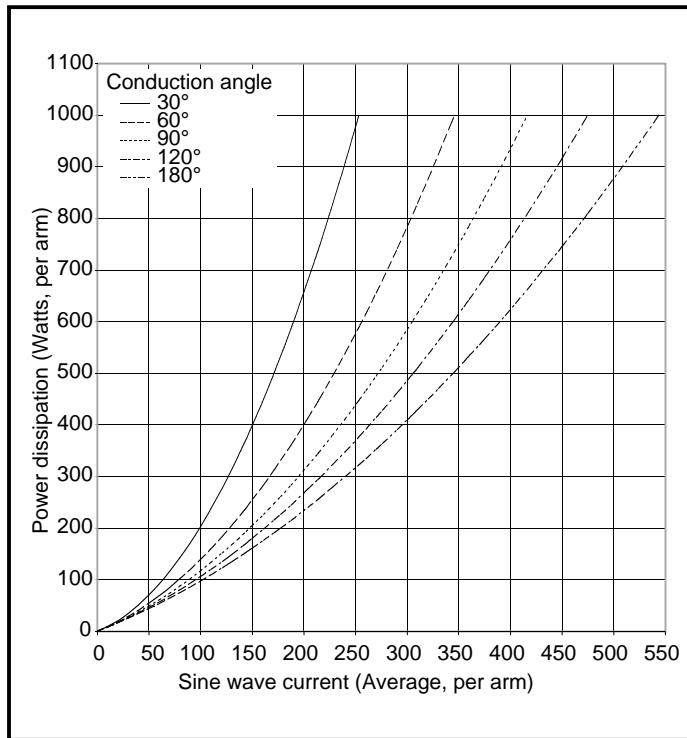

Fig. 7 On-state power loss per arm vs on-state current at specified conduction angles, sine wave 50/60Hz

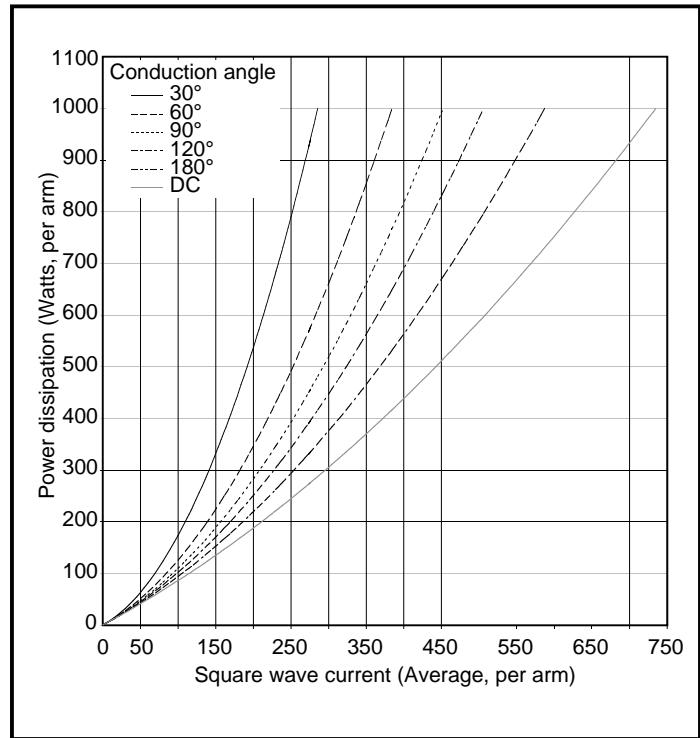

Fig. 8 On-state power loss per arm vs on-state current at specified conduction angles, square wave 50/60Hz

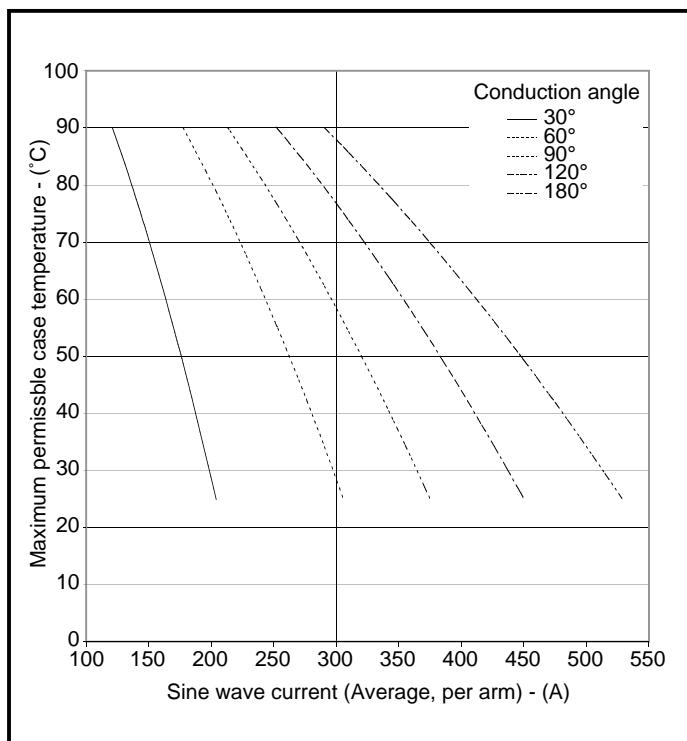

Fig. 9 Maximum permissible case temperature vs on-state current at specified conduction angles, sine wave 50/60Hz

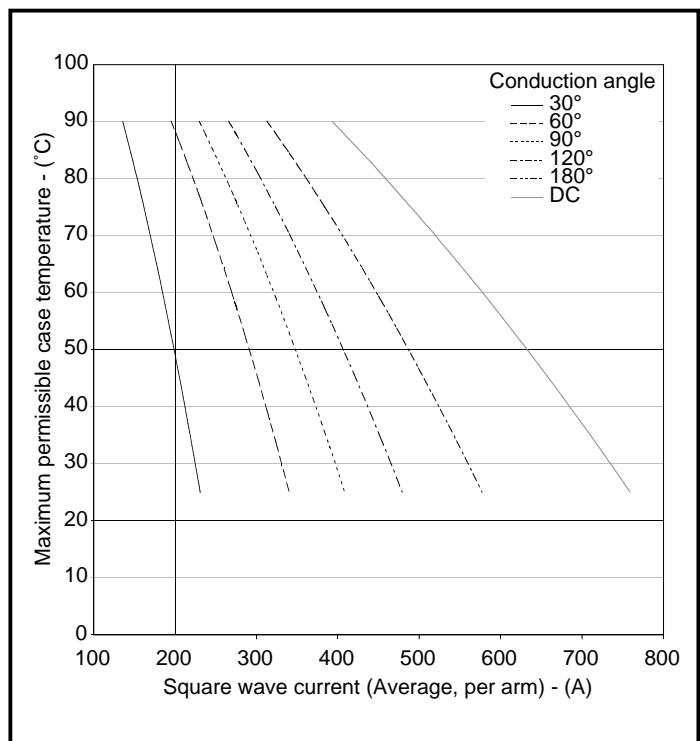

Fig. 10 Maximum permissible case temperature vs on-state current at specified conduction angles, square wave 50/60Hz

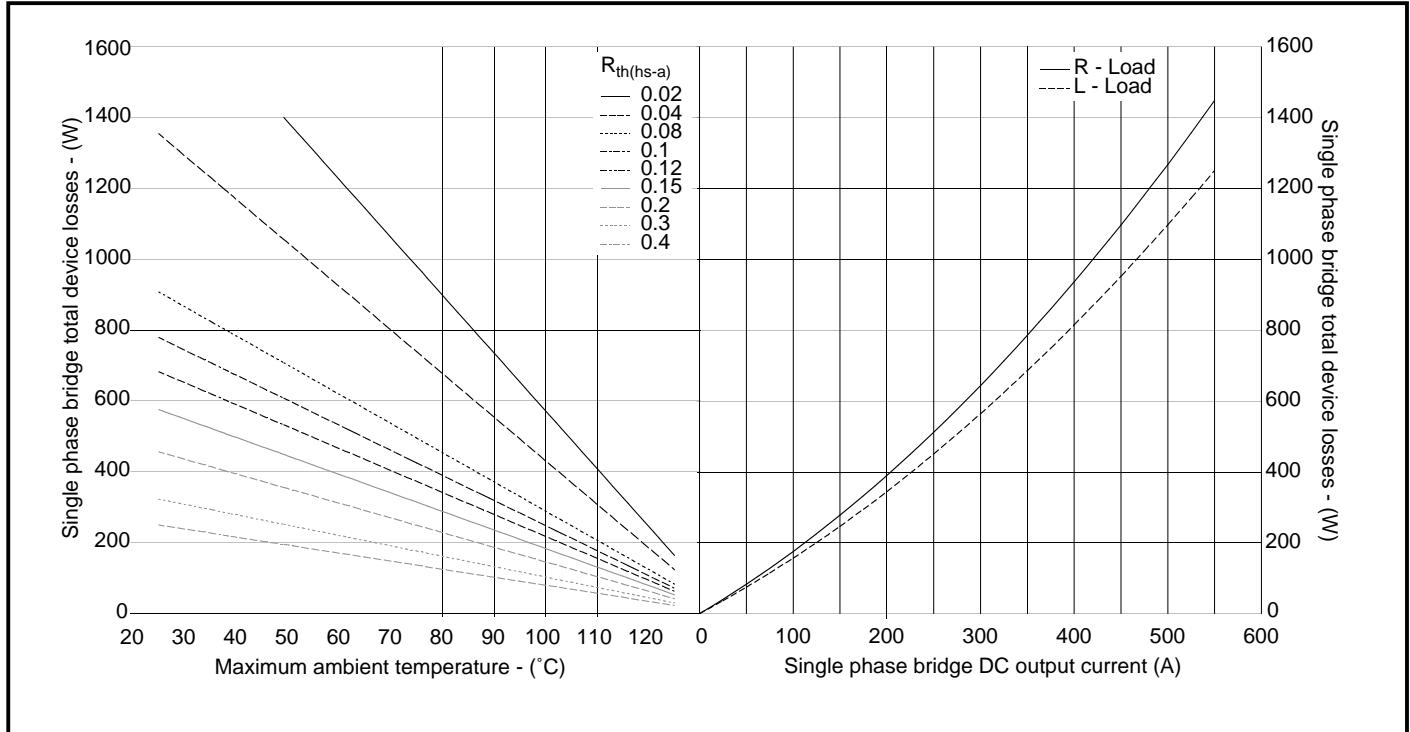

Fig. 11 50/60Hz single phase bridge DC output current vs power loss and maximum permissible case temperature for specified values of heatsink thermal resistance

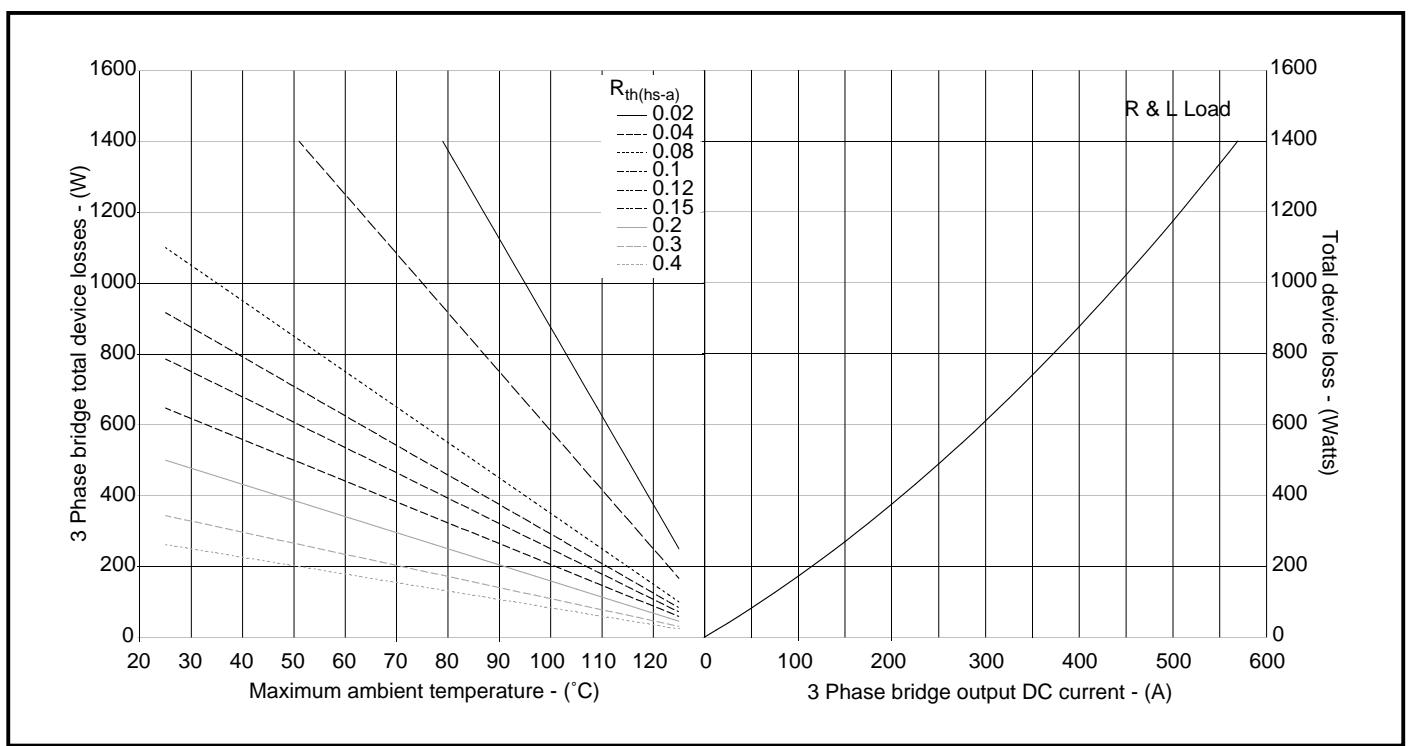

Fig. 12 Fig. 11 50/60Hz Three phase bridge DC output current vs power loss and maximum permissible case temperature for specified values of heatsink thermal resistance

## PACKAGE DETAILS

For further package information, please visit our website or contact your nearest Customer Service Centre. All dimensions in mm, unless stated otherwise. DO NOT SCALE.

## MOUNTING RECOMMENDATIONS

Adequate heatsinking is required to maintain the base temperature at 75°C if full rated current is to be achieved. Power dissipation may be calculated by use of  $V_{T(TO)}$  and  $r_T$  information in accordance with standard formulae. We can provide assistance with calculations or choice of heatsink if required.

The heatsink surface must be smooth and flat; a surface finish of N6 (32 $\mu$ in) and a flatness within 0.05mm (0.002") are recommended.

*Immediately prior to mounting, the heatsink surface should be lightly scrubbed with fine emery, Scotch Brite or a mild chemical etchant and then cleaned with a solvent to remove oxide build up and foreign material. Care should be taken to ensure no foreign particles remain.*

An even coating of thermal compound (eg. Unial) should be applied to both the heatsink and module mounting surfaces. This should ideally be 0.05mm (0.002") per surface to ensure optimum thermal performance.

After application of thermal compound, place the module squarely over the mounting holes, (or 'T' slots) in the heatsink. Using a torque wrench, slowly a torque wrench, slowly tighten the recommended fixing bolts at each end, rotating each in turn no more than 1/4 of a revolution at a time. Continue until the required torque of 6Nm (55lb.ins) is reached at both ends.

It is not acceptable to fully tighten one fixing bolt before starting to tighten the others. Such action may DAMAGE the module.

## POWER ASSEMBLY CAPABILITY

The Power Assembly group provides support for those customers requiring more than the basic semiconductor switch. Using CAD design tools the group has developed a flexible range of heatsink / clamping systems in line with advances in device types and the voltage and current capability of Dynex semiconductors.

An extensive range of air and liquid cooled assemblies is available covering the range of circuit designs in general use today.

## HEATSINKS

The Power Assembly group has a proprietary range of extruded aluminium heatsinks. These were designed to optimise the performance of Dynex semiconductors. Data with respect to air natural, forced air and liquid cooling (with flow rates) is available on request.

For further information on device clamps, heatsinks and assemblies, please contact your nearest sales representative or customer service office.

<http://www.dynexsemi.com>e-mail: [power\\_solutions@dynexsemi.com](mailto:power_solutions@dynexsemi.com)**HEADQUARTERS OPERATIONS****DYNEX SEMICONDUCTOR LTD**

Doddington Road, Lincoln.

Lincolnshire. LN6 3LF. United Kingdom.

Tel: 00-44-(0)1522-500500

Fax: 00-44-(0)1522-500550

**DYNEX POWER INC.**

99 Bank Street, Suite 410,

Ottawa, Ontario, Canada, K1P 6B9

Tel: 613.723.7035

Fax: 613.723.1518

Toll Free: 1.888.33.DYNEX (39639)

**CUSTOMER SERVICE CENTRES****Mainland Europe** Tel: +33 (0)1 58 04 91 00. Fax: +33 (0)1 46 38 51 33**North America** Tel: 011-800-5554-5554. Fax: 011-800-5444-5444**UK, Scandinavia & Rest Of World** Tel: +44 (0)1522 500500. Fax: +44 (0)1522 500020**SALES OFFICES****Mainland Europe** Tel: +33 (0)1 58 04 91 00. Fax: +33 (0)1 46 38 51 33**North America** Tel: (613) 723-7035. Fax: (613) 723-1518. Toll Free: 1.888.33.DYNEX (39639) /

Tel: (949) 733-3005. Fax: (949) 733-2986.**UK, Scandinavia & Rest Of World** Tel: +44 (0)1522 500500. Fax: +44 (0)1522 500020

These offices are supported by Representatives and Distributors in many countries world-wide.

© Dynex Semiconductor 2001 Publication No. DS4484-6 Issue No. 6.1 June 2001

**TECHNICAL DOCUMENTATION – NOT FOR RESALE. PRINTED IN UNITED KINGDOM****Datasheet Annotations:**

Dynex Semiconductor annotate datasheets in the top right hard corner of the front page, to indicate product status. The annotations are as follows:-

**Target Information:** This is the most tentative form of information and represents a very preliminary specification. No actual design work on the product has been started.

**Preliminary Information:** The product is in design and development. The datasheet represents the product as it is understood but details may change.

**Advance Information:** The product design is complete and final characterisation for volume production is well in hand.

**No Annotation:** The product parameters are fixed and the product is available to datasheet specification.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior notice the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

All brand names and product names used in this publication are trademarks, registered trademarks or trade names of their respective owners.