## CMOS, 6-Bit High-Speed Analog-to-Digital Converter

March 1998-3

### FEATURES

- Sampling Rates from 0.001 to 25 MHz (MSPS)

- Interface to any Input Range between GND and  $V_{DD}$

- Pipeline Mode (Pin Compatible Upgrade of MP7682)

- One Shot Mode

- Monotonic; No Missing Codes

- Single Power Supply (4 to 6 volt)

- Low Power CMOS (135 mW typ.)

- ESD Protection: 4000 Volts Minimum

- Latch-Up Free

### BENEFITS

- Highest Conversion Speed at Low Power

- Most Flexible Input Range of any A/D Available

- No Sample/Hold Needed

- Easy Ping-Ponging for 40 MSPS System

### GENERAL DESCRIPTION

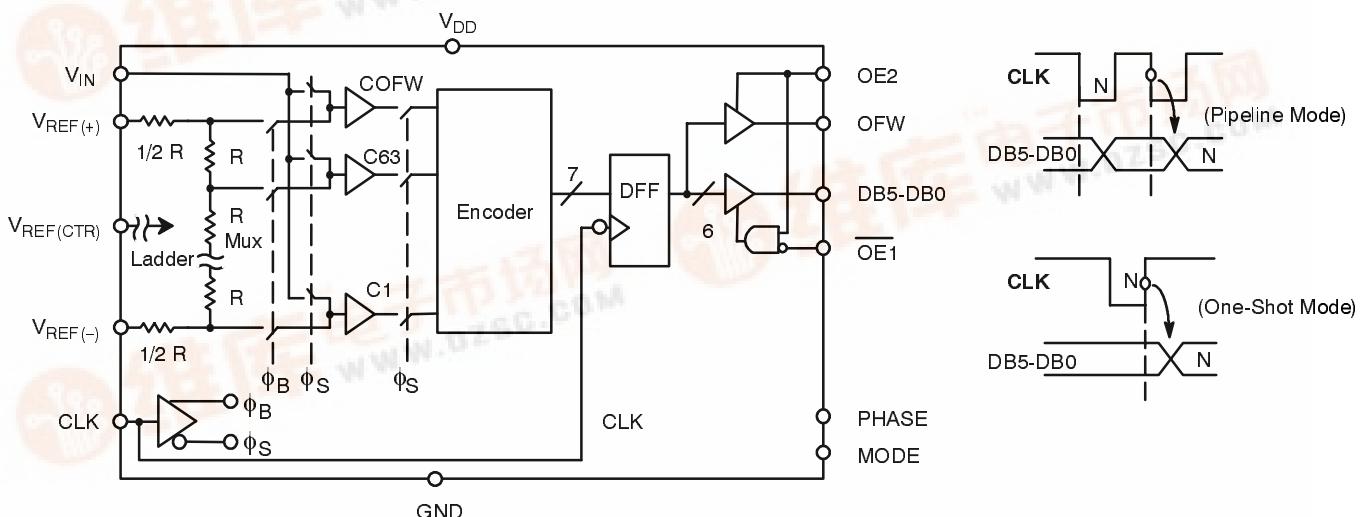

The MP7686 is a 6-bit monolithic CMOS single step high speed Analog-to-Digital Converter designed for precision 6-bit applications in video, scanning and data acquisition requiring conversion rates to 25 MHz. Differential Linearity error is less than 1/2 LSB at 20 MHz, and power consumption is 135 mW typical. A unique feature of this converter is its ability to do a complete conversion with just two clock edges (one clock pulse), by setting MODE low. When MODE is set high, the device behaves like a standard pipelined converter, requiring 3 clock edges (two clock pulses) to complete the conversion, compatible with the MP7682.

Another feature of MP7686 is its unique input architecture which eliminates the need for an input track and hold and allows full scale input ranges from about 1 to 5 volts peak-to-peak, referred to ground or offset. The user simply sets  $V_{REF(-)}$  and  $V_{REF(+)}$  to encompass the desired input range.

MP7686 includes 64 auto-balanced clocked comparators, an encoder, 3-state output buffers, a reference resistor ladder, and associated timing circuitry. An overflow bit (or flag) has been provided to make it possible to achieve 7-bit resolution by connecting two devices in series. In normal operation, this flag has no effect on the data bits.

### SIMPLIFIED BLOCK AND TIMING DIAGRAM

## ORDERING INFORMATION

| Package Type | Temperature Range | Part No. | DNL (LSB) | INL (LSB) |

|--------------|-------------------|----------|-----------|-----------|

| Plastic Dip  | -40 to +85°C      | MP7686JN | ±1 1/4    | 2         |

| Plastic Dip  | -40 to +85°C      | MP7686KN | ±1        | 1 1/4     |

| SOIC         | -40 to +85°C      | MP7686JS | ±1 1/4    | 2         |

| SOIC         | -40 to +85°C      | MP7686KS | ±1        | 1 1/4     |

| Ceramic Dip  | -40 to +85°C      | MP7686JD | ±1 1/4    | 2         |

| Ceramic Dip  | -40 to +85°C      | MP7686KD | ±1        | 1 1/4     |

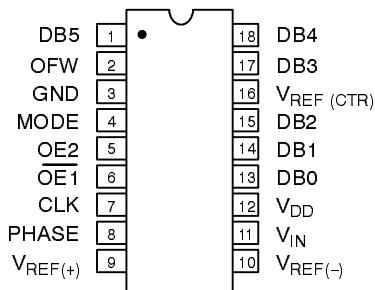

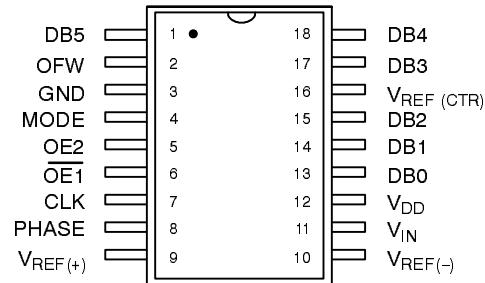

## PIN CONFIGURATIONS

See Packaging Section for Package Dimensions

18 Pin CDIP, PDIP (0.300")

18 Pin SOIC (Jedec, 0.300")

## PIN OUT DEFINITIONS

| PIN NO. | NAME                 | DESCRIPTION                    |

|---------|----------------------|--------------------------------|

| 1       | DB5                  | Data Output Bit 5 (MSB)        |

| 2       | OFW                  | Digital Output Overflow        |

| 3       | GND                  | Ground                         |

| 4       | MODE                 | Mode Select                    |

| 5       | OE2                  | Output Enable Control          |

| 6       | OE1                  | Output Enable Control          |

| 7       | CLK                  | Clock Input                    |

| 8       | PHASE                | Sampling Clock Phase Control   |

| 9       | V <sub>REF</sub> (+) | Positive Reference Voltage Pin |

| PIN NO. | NAME                   | DESCRIPTION                    |

|---------|------------------------|--------------------------------|

| 10      | V <sub>REF</sub> (-)   | Negative Reference Voltage Pin |

| 11      | V <sub>IN</sub>        | Analog Input                   |

| 12      | V <sub>DD</sub>        | Power Supply                   |

| 13      | DB0                    | Data Output Bit 0 (LSB)        |

| 14      | DB1                    | Data Output Bit 1              |

| 15      | DB2                    | Data Output Bit 2              |

| 16      | V <sub>REF</sub> (CTR) | R Ladder Mid Point             |

| 17      | DB3                    | Data Output Bit 3              |

| 18      | DB4                    | Data Output Bit 4              |

## ELECTRICAL CHARACTERISTICS TABLE

Unless Otherwise Specified:  $V_{DD} = 5$  V,  $F_S = 20$  MHz (Duty Cycle: 1/3 Sample, 2/3 Balance),

$V_{REF(+)} = 4.6$ ,  $V_{REF(-)} = GND$ ,  $T_A = 25^\circ C$

|                                                                                                                                                                                                                                                                                |                                                                 | $25^\circ C$                                                                |                                      | Tmin to Tmax                                                    |                                                |                                                                             |                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------|----------------------------|--|

| <b>KEY FEATURES</b>                                                                                                                                                                                                                                                            |                                                                 |                                                                             |                                      |                                                                 |                                                |                                                                             |                            |  |

| Resolution<br>Maximum Sampling Rate<br>Minimum Sampling Rate                                                                                                                                                                                                                   | $F_S$<br>$F_S$                                                  | 6<br>20<br>0.001                                                            |                                      | 6<br>15<br>0.001                                                | Bits<br>MHz<br>MHz                             | For specified accuracy                                                      |                            |  |

| <b>ACCURACY (J, S Grades)<sup>1</sup></b>                                                                                                                                                                                                                                      |                                                                 | DNL<br>INL                                                                  | $\pm 3/4$<br>$1 1/2$                 | $\pm 1 1/4$<br>2                                                | LSB<br>LSB                                     | Best Fit Line<br>(Max INL – Min INL) / 2                                    |                            |  |

| Zero Scale Error<br>Full Scale Error                                                                                                                                                                                                                                           | EZS<br>EFS                                                      | $\pm 2$<br>$\pm 2$                                                          |                                      |                                                                 | LSB<br>LSB                                     |                                                                             |                            |  |

| <b>ACCURACY (K, T Grades)<sup>1</sup></b>                                                                                                                                                                                                                                      |                                                                 | DNL<br>INL<br>EZS<br>EFS                                                    | $\pm 1/2$<br>1<br>$\pm 2$<br>$\pm 2$ | $\pm 1$<br>1 1/4                                                | LSB<br>LSB<br>LSB<br>LSB                       | Best Fit Line                                                               |                            |  |

| Positive Ref. Voltage<br>Negative Ref. Voltage<br>Differential Ref. Voltage <sup>3</sup><br>Ladder Resistance<br>Ladder Temp. Coefficient <sup>2</sup>                                                                                                                         | $V_{REF(+)}$<br>$V_{REF(-)}$<br>$V_{REF}$<br>$R_L$<br>$R_{TCO}$ | GND<br>1.0<br>175                                                           | $V_{DD}$<br>230<br>270               | GND<br>1.0<br>160                                               | $V_{DD}$<br>300<br>3000                        | V<br>V<br>V<br>$\Omega$<br>ppm/ $^\circ C$                                  |                            |  |

| <b>ANALOG INPUT<sup>2</sup></b>                                                                                                                                                                                                                                                | $V_{IN}$                                                        | $V_{REF(-)}$                                                                | $V_{REF(+)}$                         | $V_{REF(-)}$                                                    | $V_{REF(+)}$                                   | V p-p<br>pF<br>ns<br>ps<br>pAs                                              | <i>See Figure 5.</i>       |  |

| Input Voltage Range<br>Input Capacitance <sup>5</sup><br>Aperture Delay<br>Aperture Uncertainty (Jitter)<br>Clock Kickback Pulse                                                                                                                                               | $C_{IN}$<br>$t_{AP}$<br>$t_{AJ}$                                | 20<br>15<br>50<br>10                                                        |                                      |                                                                 |                                                |                                                                             |                            |  |

| <b>DIGITAL INPUTS</b>                                                                                                                                                                                                                                                          |                                                                 | $V_{IH}$<br>$V_{IL}$<br>$I_{IN}$                                            | 2<br>0.8                             | 2<br>0.8                                                        | V<br>V                                         |                                                                             |                            |  |

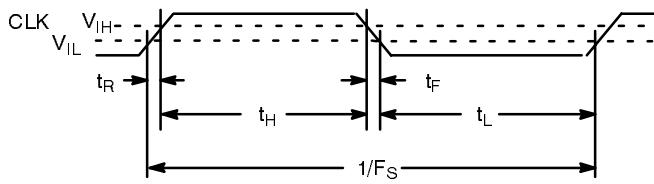

| Logical "1" Voltage<br>Logical "0" Voltage<br>Leakage Currents <sup>6</sup><br>CLK<br>OE2<br>Phase<br>Mode<br>OE1<br>Input Capacitance <sup>2</sup><br>Clock Timing (See Figure 1.)<br>Clock Period<br>Rise & Fall Time<br>"High" Time (Auto-Balance)<br>"Low" Time (Sampling) |                                                                 | -1<br>-20<br>-20<br>-20<br>-1<br>5<br>$t_S$<br>$t_R, t_F$<br>$t_H$<br>$t_L$ | 1<br>1<br>1<br>1<br>20               | -1<br>-20<br>-20<br>-20<br>-1<br>66<br>5<br>33<br>33<br>500,000 | 1<br>1<br>1<br>1<br>20<br>ns<br>ns<br>ns<br>ns | $\mu A$<br>$\mu A$<br>$\mu A$<br>$\mu A$<br>$\mu A$<br>pF<br>ns<br>ns<br>ns | $V_{IN} = GND$ to $V_{DD}$ |  |

## ELECTRICAL CHARACTERISTICS TABLE CONT'D

| Parameter                               | Symbol           | 25°C                 |     |     | Tmin to Tmax         |     | Units  | Test Conditions/Comments                  |

|-----------------------------------------|------------------|----------------------|-----|-----|----------------------|-----|--------|-------------------------------------------|

|                                         |                  | Min                  | Typ | Max | Min                  | Max |        |                                           |

| <b>DIGITAL OUTPUTS</b>                  |                  |                      |     |     |                      |     |        |                                           |

| Logical "1" Voltage                     | V <sub>OH</sub>  | V <sub>DD</sub> -0.5 |     |     | V <sub>DD</sub> -0.5 |     | V      | I <sub>LOAD</sub> = 4 mA                  |

| Logical "0" Voltage                     | V <sub>OL</sub>  |                      | 0.4 |     |                      | 0.4 | V      | I <sub>LOAD</sub> = 2.0 mA                |

| 3-state Leakage                         | I <sub>OZ</sub>  | -10                  | 10  |     | -15                  | 15  | μA     | V <sub>OUT</sub> = GND to V <sub>DD</sub> |

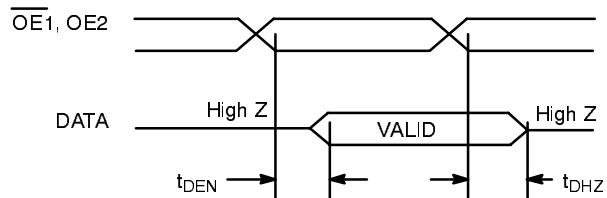

| Data Enable Delay                       | t <sub>DEN</sub> |                      | 18  | 22  |                      | 25  | ns     |                                           |

| Data 3-state Delay                      | t <sub>DHZ</sub> |                      | 18  | 22  |                      | 25  | ns     |                                           |

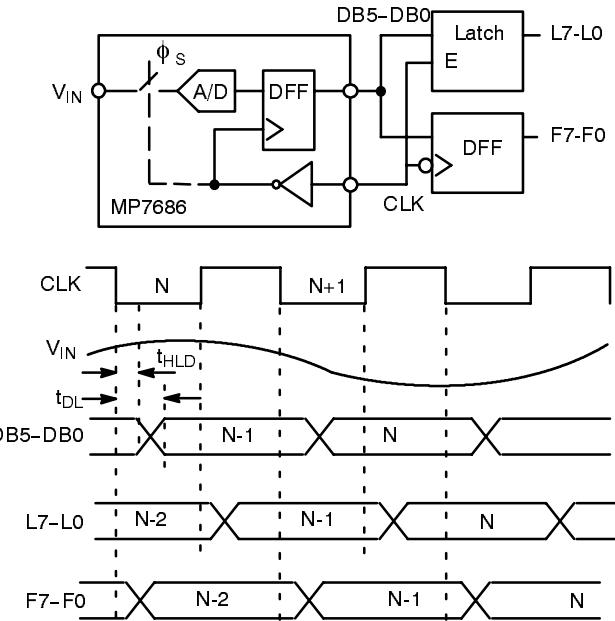

| Pipeline Mode (See Figure 6.)           |                  |                      |     |     |                      |     |        | Phase=0, Mode=1                           |

| Data Hold Time <sup>2</sup>             | t <sub>HLD</sub> | 15                   | 22  |     | 15                   |     | ns     |                                           |

| Data Valid Delay <sup>2</sup>           | t <sub>DL</sub>  |                      | 30  | 40  |                      | 40  | ns     |                                           |

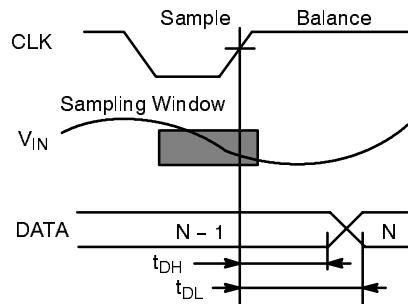

| One-Shot Mode (See Figure 7.)           |                  |                      |     |     |                      |     |        | Phase=0, Mode=0                           |

| Data Hold Time <sup>2</sup>             | t <sub>HLD</sub> | 13                   | 19  |     | 10                   |     | ns     |                                           |

| Data Valid Delay <sup>2</sup>           | t <sub>DL</sub>  |                      | 30  | 37  |                      | 40  | ns     |                                           |

| <b>POWER SUPPLIES</b>                   |                  |                      |     |     |                      |     |        |                                           |

| Operating Voltage                       | V <sub>DD</sub>  | 4                    | 6   |     | 4                    | 6   | V      |                                           |

| Current                                 | I <sub>DD</sub>  |                      | 27  | 35  |                      | 40  | mA     |                                           |

| <b>AC PARAMETERS<sup>2</sup></b>        |                  |                      |     |     |                      |     |        |                                           |

| Signal Noise Ratio <sup>10</sup>        | SNR              |                      | 36  |     |                      |     | dB     | RMS/RMS Measures                          |

| Harmonic Distortion                     |                  |                      |     |     |                      |     |        | F <sub>IN</sub> = 5 MHz                   |

| Second Harmonic                         | 2nd HD           |                      | 35  |     |                      |     | -dB    | F <sub>IN</sub> = 1 MHz                   |

| Third Harmonic                          | 3rd HD           |                      | 35  |     |                      |     | -dB    | F <sub>IN</sub> = 5 MHz                   |

| Total Harmonic Distortion <sup>12</sup> | THD              |                      | 29  |     |                      |     | -dB    | F <sub>IN</sub> = 5 MHz                   |

| Total Dynamic Error <sup>11</sup>       | TDE              |                      | 30  |     |                      |     | dB     | F <sub>IN</sub> = 5 MHz                   |

| Differential Gain Error                 | d <sub>G</sub>   |                      | 2   |     |                      |     | %      | F <sub>S</sub> = 3 x NTSC                 |

| Differential Phase Error                | d <sub>PH</sub>  |                      | 1   |     |                      |     | Degree |                                           |

**Notes:**

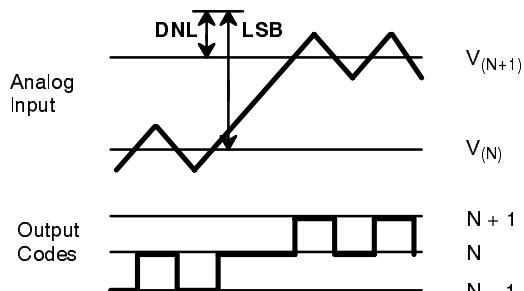

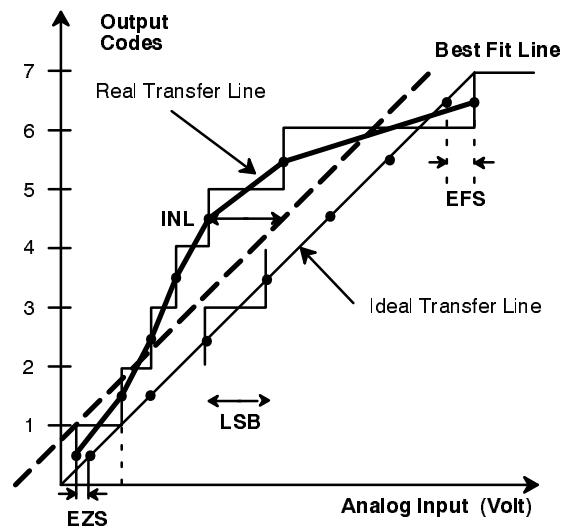

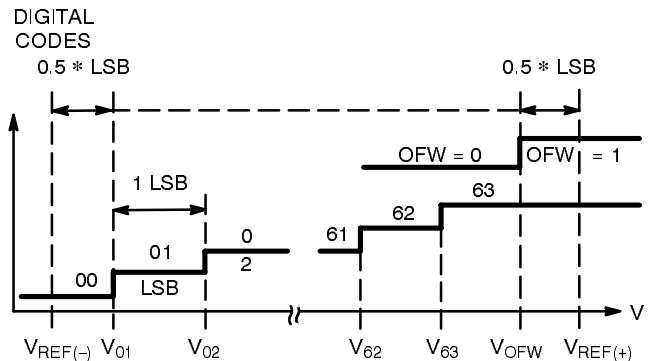

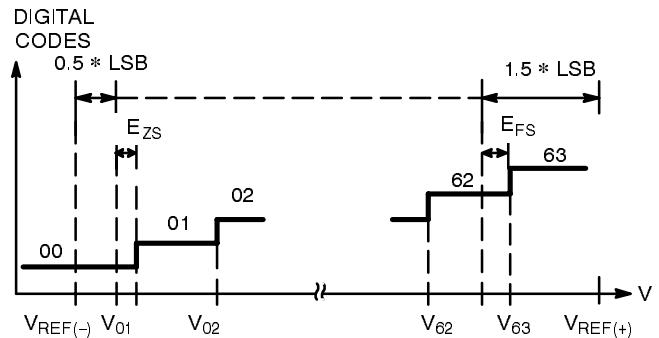

- <sup>1</sup> Tester measures code transitions by dithering the voltage of the analog input (V<sub>IN</sub>). The difference between the measured and the ideal code width (V<sub>REF</sub>/64) is the DNL error (Figure 3.). The INL error is the maximum distance (in LSBs) from the Best Fit Line to any transition voltage (Figure 4.). Accuracy is a function of the sampling rate (F<sub>S</sub>).

- <sup>2</sup> Guaranteed. Not tested.

- <sup>3</sup> Specified values guarantee functionality. Refer to other parameters for accuracy.

- <sup>4</sup> Input bandwidth is a measure of performance of the A/D input stage (S/H + amplifier). Refer to other parameters for accuracy within the specified bandwidth.

- BW calculation: BW = V<sub>OUT</sub> / V<sub>IN</sub>

- $V_{OUT} = V_{REF} * (CODE_{MAX} - CODE_{MIN}) / 64$

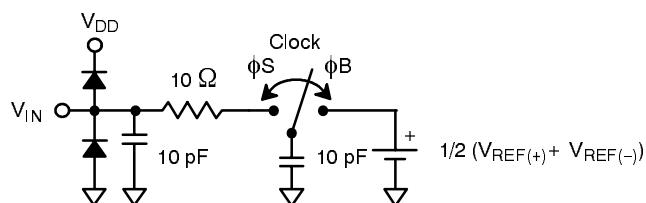

- See V<sub>IN</sub> input equivalent circuit (Figure 5.) for high sampling rates. Switched capacitor analog input requires driver with low output resistance.

- All inputs have diodes to V<sub>DD</sub> and GND. Inputs OE2, Phase, Mode have internal pull ups. Input OE1 has internal pull down. Input DC currents will not exceed specified limits for any input voltage between GND and V<sub>DD</sub>.

- Internal resistor to V<sub>DD</sub> biases unconnected input to active high logical level.

- Internal resistor to GND biases unconnected input to active low logical level.

- Condition to meet aperture delay specifications (t<sub>AP</sub>, t<sub>AJ</sub>). Actual rise/fall time can be less stringent with no loss of accuracy.

- SNR: Ratio of fundamental over noise.

- TDE: Ratio of fundamental over noise + harmonics (2nd to 9th).

- THD: Ratio of harmonics (2nd to 9th) over fundamental.

## ABSOLUTE MAXIMUM RATINGS ( $T_A = +25^\circ\text{C}$ unless otherwise noted)<sup>1, 2</sup>

|                           |       |                             |

|---------------------------|-------|-----------------------------|

| $V_{DD}$ to GND           | ..... | +7 V                        |

| $V_{REF(+)} & V_{REF(-)}$ | ..... | GND -0.5 to $V_{DD}$ +0.5 V |

| $V_{IN}$                  | ..... | GND -0.5 to $V_{DD}$ +0.5 V |

| Digital Inputs            | ..... | GND -0.5 to $V_{DD}$ +0.5 V |

| Digital Outputs           | ..... | GND -0.5 to $V_{DD}$ +0.5 V |

|                                                   |                 |

|---------------------------------------------------|-----------------|

| Storage Temperature . . . . .                     | -65°C to +150°C |

| Lead Temperature (Soldering 10 seconds) . . . . . | +300°C          |

| Package Power Dissipation Rating to 75°C          |                 |

| CDIP, PDIP, SOIC . . . . .                        | 850mW           |

| Derates above 75°C . . . . .                      | 11mW/°C         |

### **Notes:**

- <sup>1</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup> Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. All inputs have protection diodes which will protect the device from short transients outside the supplies of less than 100mA for less than 100μs.

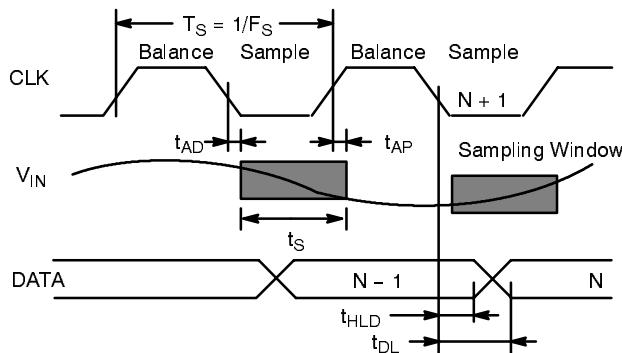

**Figure 1. Clock Timing Specification**

**Figure 2. Data Line Enable Delay**

$$\begin{aligned}

(N) \text{ Code Width} &= V_{(N+1)} - V_{(N)} \\

\text{LSB} &= [V_{\text{REF}(+)} - V_{\text{REF}(-)}] / 64 \\

\text{DNL}_{(N)} &= [V_{(N+1)} - V_{(N)}] - \text{LSB}

\end{aligned}$$

**Figure 3. DNL Measurement**

**Figure 4. INL Error Calculation**

**Figure 5. Analog Input Equivalent Circuit**

## THEORY OF OPERATION

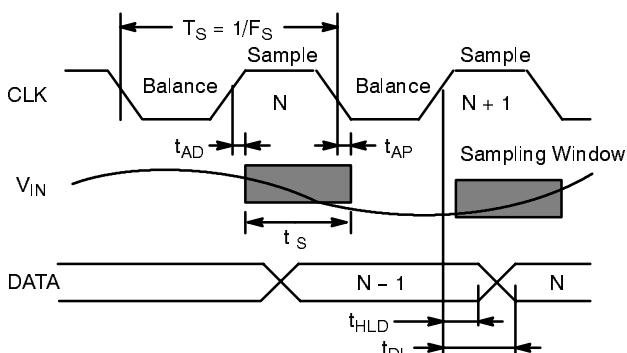

The MP7686 has three operating modes. It has two pipelined modes (MP7682 compatible) and a one shot mode. The voltages applied to the Phase and Mode pins determine the operating mode. Figures 1 through 7 show the timing specifications. Timing parameters are measured to and from valid logic levels (i.e.  $t_{DH}$  is the time from  $CLK = 0.8$  V to  $DATA = 0.4$  or  $2.4$  V).

### Pipeline Modes (Mode = High)

In this configuration, the MP7686 works in a continuous fashion (MP7682 compatible). Figure 6. shows the timing with the Phase pin high and low. When Phase is low, "sampling" occurs during the low period of the clock and "balancing" during the high period. When Phase is high, operation is reversed (see Figure 7.), "sampling" occurs during the high period and "balancing" during the low period. The actual time when the internal comparators are connected to  $V_{IN}$  is called the Acquisition Time. This time is equal to the sample phase of the external clock delayed by  $t_{AD}$  and  $t_{AP}$ .

Figure 6. Pipeline Mode Timing (7682 compatible)

(Phase = 0, Mode = 1)

Figure 7. Pipeline Mode Timing (MP7682 compatible)

(Phase = 1, Mode = 1)

The MP7686 converts analog voltages into 64 digital codes by encoding the outputs of comparators. A comparator is used to generate the overflow bit. The conversion is synchronous with the sample clock. A complete conversion cycle is accomplished in 1.5 cycles. Data is transferred from the comparator latches to the output register each cycle and at the same time the input is sampled.

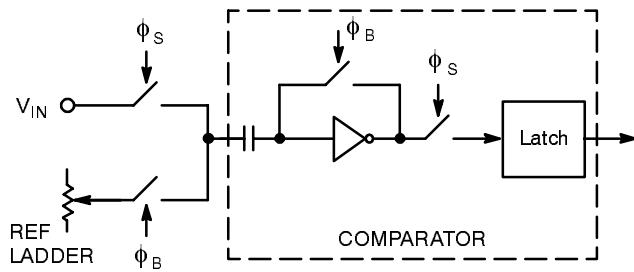

The clock signal generates the two internal phases,  $\phi B$  (CLK high = balance) and  $\phi S$  (CLK low = sample). Phase B connects the comparators to the reference tap points. Phase S connects the comparators to the analog input voltage.

The reference resistance ladder is a series of 65 resistors. The first and the last resistors of the ladder are half the value of the others so that the following relations apply:

$$R_{REF} = R * 64 \quad V_{REF} = V_{REF(+)} - V_{REF(-)} = 64 * LSB$$

Figure 8. Ideal A/D Transfer Function

Figure 9. Real A/D Transfer Curve

For MP7686 the overflow flag is ideally set at

$$V_{OFW} = V_{REF(+)} - 0.5 * LSB$$

Thus the first and last transition of the data bits take place at

$$V_{IN} = V_{01} = V_{REF(-)} + 0.5 * LSB$$

$$V_{IN} = V_{63} = V_{REF(+)} - 1.5 * LSB$$

$$LSB = (V_{63} - V_{01}) / 62$$

MP7686 also has zero scale and full scale errors which indicate the deviations from the ideal initial and final transitions, thus the

various error relationships for Differential Non-Linearity (DNL), Integral Non-Linearity (INL) and the zero and full scale errors (E<sub>ZS</sub> and E<sub>FS</sub>) can be described as follows:

$$\text{DNL (01)} = V_{02} - V_{01} - \text{LSB}$$

⋮ ⋮ ⋮

$$\text{DNL (62)} = V_{63} - V_{62} - \text{LSB}$$

$$E_{FS} (\text{full scale error}) = V_{63} - [V_{REF(+)} - 1.5 * \text{LSB}]$$

$$E_{ZS} (\text{zero scale error}) = V_{01} - [V_{REF(-)} + 0.5 * \text{LSB}]$$

$$\text{INL} (\text{I}) = \sum \text{DNL} (\text{I})$$

Systems that adjust the  $V_{REF}$  voltages only increase the DNL accuracy at the two extreme points. In the MP7686, such adjustments have little impact at frequencies lower than 15 MHz.

Figure 10. MP7686 Comparator

The MP7686 uses the balance phase ( $\phi_B$ ) to charge one plate of the capacitors to the reference ladder tap point and the other to the inverter/comparator trigger point (Figure 10.). During the sample phase ( $\phi_S$ ), one plate of the capacitors switches to  $V_{IN}$ . The change in voltage ( $V_{IN} - V_{TAP}$ ) transfers across the capacitor and forces the inverter into one of the two possible logic states. A latch (connected to the comparator during  $\phi_S$ ) restores and propagates the digital level to the decode logic.

The rising edge of the CLK input marks the end of the sampling phase ( $\phi_S$ ). Internal delay of the clock circuitry will delay the actual instant when  $\phi_S$  disconnects the latch from the comparator. This delay is called aperture delay ( $t_{AP}$ ).

The aperture delay is not constant but changes from one cycle to the next. Internal thermal noise and slow input clock edges are major contributors to this variation. The aperture jitter ( $t_{AJ}$ ) is the variation of the aperture delay distribution.

This uncertainty shows as digital code errors if the input slew rate multiplied by  $t_{AJ}$  is of the same order of magnitude as the LSB. That is, if  $(dv/dt) * t_{AJ} \approx V_{REF}/64$ , an internal 1 LSB of error results.

The logic encodes the 64 bits into a binary code and latches the data into a D-type flip-flop for output. The inputs  $\overline{OE1}$  and  $OE2$  control the output buffers in an asynchronous mode.

| $\overline{OE1}$ | $OE2$ | OFW    | DB5 - DB0 |

|------------------|-------|--------|-----------|

| X                | 0     | High Z | High Z    |

| 1                | 1     | Valid  | High Z    |

| 0                | 1     | Valid  | Valid     |

Table 1. Output Enable Logic

Figure 11. MP7686 Functional Equivalent Circuit and Interface Timing (Pipeline Mode)

The MP7686 functional equivalent circuit is shown to help the designer to correctly design the system timing. The MP7686 is equivalent to an A/D converter followed by a D-type flip-flop (DFF) with the hold and delay times specified in the electrical characteristics.

If another DFF is to follow the ADC, we recommend that the system latches the data at the negative going edge of the clock. If a latch follows the ADC, the positive half of the clock used as enable signal should guarantee stable output at the end of the enable pulse. At high sampling frequencies ( $F_S > 20$  MHz) the user should verify in the system that the MP7686 digital outputs do not change when the digital logic is trying to latch the data. If this problem occurs it may be necessary to invert the logic state of the input PHASE or to change the edge that latches the data into the external circuitry.

**Figure 12. One Shot Mode Timing**

(Phase = 0, Mode = 0)

While the pipeline mode requires three clock edges (two clock pulses) to accomplish one A/D conversion, the One Shot mode (see Figure 12.) requires only two edges (one clock pulse) to complete a conversion.

### Reserved (Mode = Low, Phase = High)

This mode is not a valid operational mode.

### Reference Voltages

If the input bandwidth is limited to the Nyquist region ( $F_{IN} < FS/2$ ) then the two reference voltages can be set at any two values between the supplies.  $V_{REF}$  (their difference) can be reduced down to 1.5 volts with minor change in accuracy. If the input bandwidth exceeds FS/2, then it is recommended that  $V_{REF}$  be lower than  $V_{DD}/2$ .

### One Shot Mode (Mode = Low, Phase = Low)

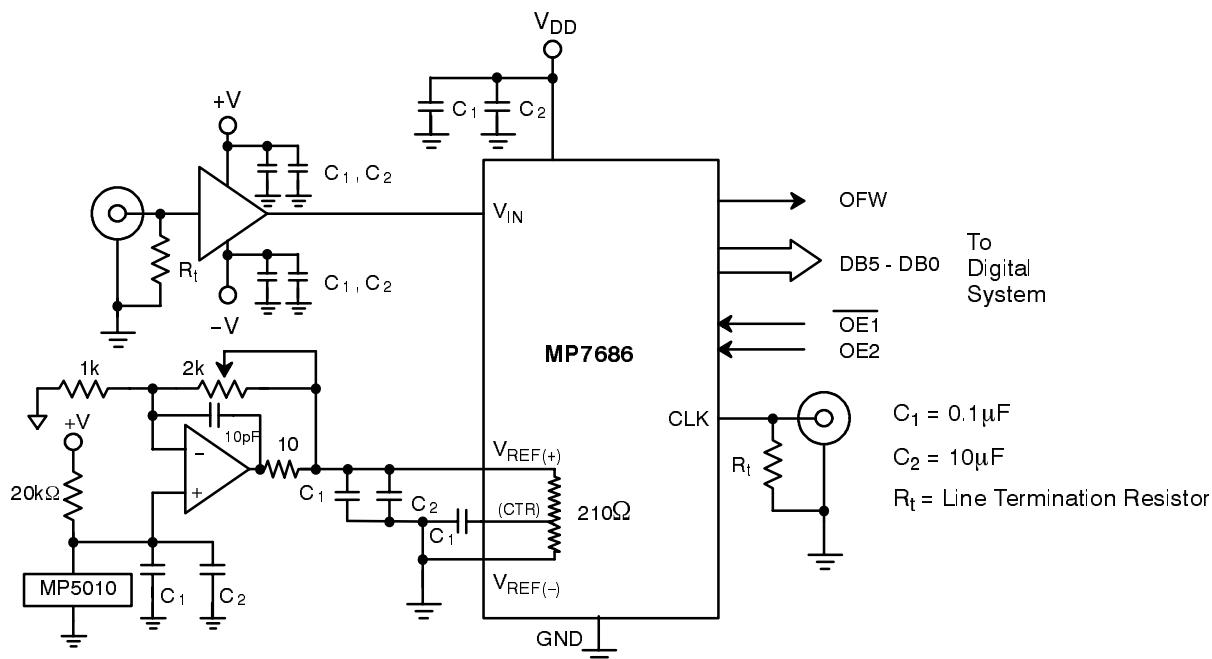

**Figure 13. Typical Circuit Connections**

1. All signals should not exceed  $V_{DD} + 0.5$  V or  $GND - 0.5$  V.

2. Any input pin which can see a value outside the absolute maximum ratings ( $V_{DD} + 0.5$  V or  $GND - 0.5$  V) should be protected by diode clamps (HP5082-2835) from input pin to the supplies. All MP7686 inputs have input protection diodes

which will protect the device from short transients outside the supplies range.

3. The PC board design will affect the MP7686 accuracy. Use of wire wrap is not recommended.

- 4. The analog input signal ( $V_{IN}$ ) is quite sensitive and should be properly routed and terminated. It should be shielded from the clock and digital outputs so as to minimize cross coupling and noise pickup.

- 5. The analog input should be driven by a buffer op amp with as low an output impedance as possible. The impedance should be less than  $25\Omega$  for clock frequencies above 15 MHz

- 6. Ground plane should be substantial. The ground plane should act as a shield for parasitics and not a return path for signals. Separate low impedance ground paths will reduce noise levels.

- 7. The power supplies and reference voltages should be decoupled with a ceramic ( $0.1\mu F$ ) and a tantalum ( $10\mu F$ ) capacitor as close to the device as possible.

- 8. The digital output should not be driving long wires as the capacitive coupling and reflection will contribute noise to the conversion. When driving distant loads, buffers should be used.