MSC8101 Rev. 18, 8/2005

## **MSC8101**

#### Network Digital Signal Processor

The Freescale MSC8101 16-bit DSP is the first member of the family of DSPs based on the StarCore SC140 DSP core. The MSC8101 is available in three core speed levels: 250, 275, and 300 MHz.

#### What's New?

Rev. 18 includes the following changes:

- The features list on page iii updates the package description.

- Table 2-3 updates junctionto-case value.

- Section 3.1 adds a note to include the lead-free packaging.

- Ordering Information on the back cover adds the leadfree part numbers.

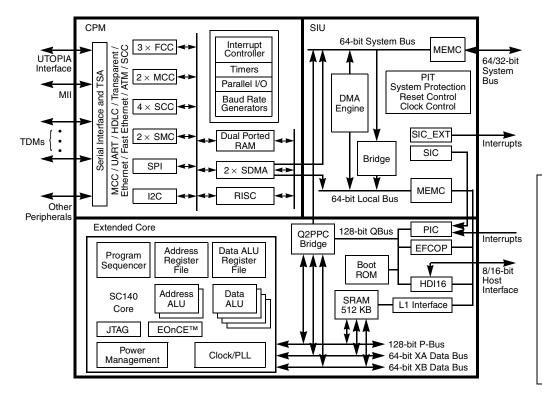

Figure 1. MSC8101 Block Diagram

The Freescale MSC8101 DSP is a very versatile device that integrates the high-performance SC140 four-ALU (arithmetic logic unit) DSP core along with 512 KB of internal memory, a communications processor module (CPM), a 64-bit bus, a very flexible System Integration Unit (SIU), and a 16-channel DMA engine on a single device. With its four-ALU core, the MSC8101 can execute up to four multiply-accumulate (MAC) operations in a single clock cycle. The MSC8101 CPM is a 32-bit RISC-based communications protocol engine that can network to time-division multiplexed (TDM) highways, Ethernet, and asynchronous transfer mode (ATM) backbones. The MSC8101 60x-compatible bus interface facilitates its connection to multi-master system architectures. The very large internal memory, 512 KB, reduces the need for external program and data memories. The MSC8101 offers 1500 DSP MMACS (1200 core and 300 EFCOP) performance using an internal 300 MHz clock with a 1.6 V core and independent 3.3 V input/output (I/O).

## **Table of Contents**

|              | MSC8                                   | 101 Features                                  | ii         |  |  |  |

|--------------|----------------------------------------|-----------------------------------------------|------------|--|--|--|

|              |                                        | Applications                                  |            |  |  |  |

|              | _                                      | ct Documentation                              |            |  |  |  |

| Chapter 1    | Signa                                  | als/Connections                               |            |  |  |  |

| -            | 1.1                                    | Power Signals                                 | 1-4        |  |  |  |

|              | 1.2                                    | Clock Signals                                 |            |  |  |  |

|              | 1.3                                    | Reset, Configuration, and EOnCE Event Signals |            |  |  |  |

|              | 1.4                                    | System Bus, HDI16, and Interrupt Signals      | 1-6        |  |  |  |

|              | 1.5                                    | Memory Controller Signals                     | 1-13       |  |  |  |

|              | 1.6                                    | CPM Ports                                     | 1-15       |  |  |  |

|              | 1.7                                    | JTAG Test Access Port Signals                 | 1-36       |  |  |  |

|              | 1.8                                    | Reserved Signals                              | 1-36       |  |  |  |

| Chapter 2    | Physical and Electrical Specifications |                                               |            |  |  |  |

| -            | 2.1                                    | Absolute Maximum Ratings                      | 2-1        |  |  |  |

|              | 2.2                                    | Recommended Operating Conditions              | 2-2        |  |  |  |

|              | 2.3                                    | Thermal Characteristics                       | 2-2        |  |  |  |

|              | 2.4                                    | DC Electrical Characteristics                 | 2-3        |  |  |  |

|              | 2.5                                    | Clock Configuration                           | 2-4        |  |  |  |

|              | 2.6                                    | AC Timings                                    | 2-7        |  |  |  |

| Chapter 3    | Pack                                   | aging                                         |            |  |  |  |

| -            | 3.1                                    | FC-PBGA Package Description                   |            |  |  |  |

|              | 3.2                                    | Lidded FC-PBGA Package Mechanical Drawing     |            |  |  |  |

| Chapter 4    | Desig                                  | gn Considerations                             |            |  |  |  |

| -            | 4.1                                    | Thermal Design Considerations                 | 4-1        |  |  |  |

|              | 4.2                                    | Electrical Design Considerations              | 4-1        |  |  |  |

|              | 4.3                                    | Power Considerations                          | 4-2        |  |  |  |

|              | 4.4                                    | Layout Practices                              | 4-3        |  |  |  |

| Ordering and | Contact I                              | nformation                                    | Back Cover |  |  |  |

### **Data Sheet Conventions**

| pin and pin-<br>out<br>OVERBAR | Although the device package does not have pins, the term pins and pin-out are used for convenience and indicate specific signal locations within the ball-grid array.  Used to indicate a signal that is active when pulled low (For example, the RESET pin is active |                                                                                                   |                              |                      |  |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------|----------------------|--|--|--|

|                                | when low.)                                                                                                                                                                                                                                                            |                                                                                                   |                              |                      |  |  |  |

| "asserted"                     | Means that a high true (a                                                                                                                                                                                                                                             | active high) signal is hig                                                                        | gh or that a low true (activ | e low) signal is low |  |  |  |

| "deasserted"                   | Means that a high true (a                                                                                                                                                                                                                                             | Means that a high true (active high) signal is low or that a low true (active low) signal is high |                              |                      |  |  |  |

| Examples:                      | Signal/Symbol                                                                                                                                                                                                                                                         | Logic State                                                                                       | Signal State                 | Voltage              |  |  |  |

|                                | PIN                                                                                                                                                                                                                                                                   | True                                                                                              | Asserted                     | $V_{IL}/V_{OL}$      |  |  |  |

|                                | PIN                                                                                                                                                                                                                                                                   | False                                                                                             | Deasserted                   | $V_{IH}/V_{OH}$      |  |  |  |

|                                | PIN                                                                                                                                                                                                                                                                   | True                                                                                              | Asserted                     | $V_{IH}/V_{OH}$      |  |  |  |

Note: Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

False

Deasserted

$V_{IL}/V_{OL}$

#### **MSC8101 Features**

- SC140 core

- Architecture optimized for efficient C/C++ code compilation

- Four 16-bit ALUs and two 32-bit AGUs

- 1200 DSP MMACS running at 300 MHz

- Very low power dissipation

- Variable-length execution set (VLES) execution model

- JTAG/Enhanced OnCE debug port

- Communications processor module (CPM)

- Programmable protocol machine using a 32-bit RISC engine

- 155 Mbps ATM interface (including AAL 0/1/2/5)

- 10/100 Mbit Ethernet interface

- Up to four E1/T1 interfaces or one E3/T3 interface and one E1/T1 interface

- HDLC support up to T3 rates, or 256 channels

- 64- or 32-bit wide bus interface

- Support for bursts for high efficiency

- Glueless interface to 60x-compatible bus systems

- Multi-master support

- Enhanced filter coprocessor (EFCOP)

- Independently and concurrently executes long filters (such as echo cancellation)

- Runs at 250/275/300 MHz and provides 250/275/300 MMACS performance

- Programmable memory controller

- Control for up to eight banks of external memory

- User-programmable machines (UPM) allowing glueless interface to various memory types (SRAM, DRAM, EPROM, and Flash memory) and other user-definable peripherals

- Dedicated pipelined SDRAM memory interface

- Large internal SRAM

- 256K 16-bit words (512 KB)

- Unified program and data space configurable by the application

- Word and byte addressable

- DMA controller

- 16 DMA channels, FIFO based, with burst capabilities

- Sophisticated addressing capabilities

- Small foot print package

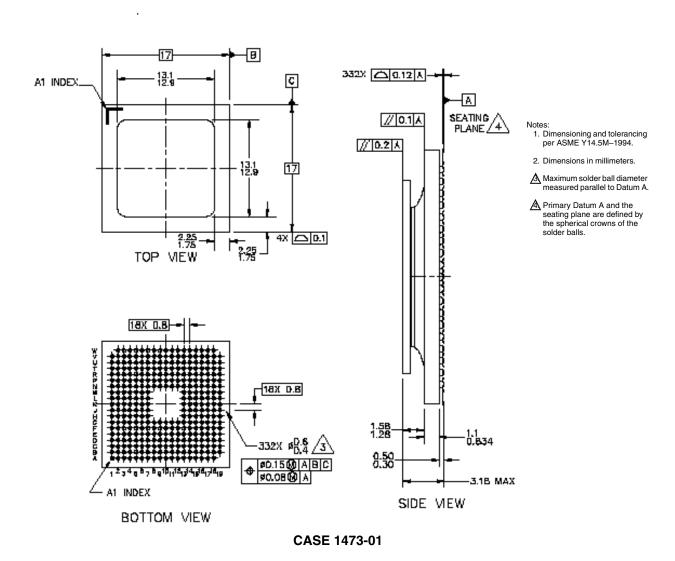

- 17 mm × 17 mm lidded FC-PBGA lead-bearing or lead-free package

- Very low power consumption

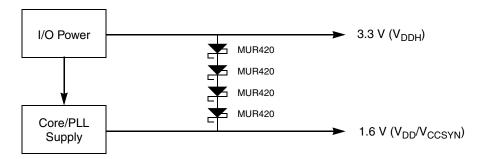

- Separate power supply for internal logic (1.6 V) and for I/O (3.3 V)

- Enhanced 16-bit parallel host interface (HDI16)

- Supports a variety of microcontroller, microprocessor, and DSP bus interfaces

- Phase-lock loops (PLLs)

- System PLL

- CPM DPLLs (SCC and SCM)

- Process technology

- 0.13 micron copper interconnect process technology

## **Target Applications**

The MSC8101 targets applications requiring very high performance, very large amounts of internal memory, and such networking capabilities as:

- Third-generation wideband wireless infrastructure systems

- Packet Telephony systems

- Multi-channel modem banks

- Multi-channel xDSL

#### **Product Documentation**

The documents listed in **Table 1** are required for a complete description of the MSC8101 and are necessary to design properly with the part. Documentation is available from the following sources (see back cover for details):

- A local Freescale distributor

- A Freescale Semiconductor sales office

- A Freescale Semiconductor Literature Distribution Center

- The world wide web (WWW)

Table 1. MSC8101 Documentation

| Name                            | Description                                                                                              | Order Number                    |

|---------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------|

| MSC8101<br>Technical Data       | MSC8101 features list and physical, electrical, timing, and package specifications                       | MSC8101/D                       |

| MSC8101 User's Guide            | Detailed functional description of the MSC8101 memory configuration, operation, and register programming | MSC8101UG/D                     |

| MSC8101 Pocket Guide            | Quick reference information for application development.                                                 | MSC8101PG/D                     |

| MSC8101 Reference Manual        | Detailed description of the MSC8101 processor core and instruction set                                   | MSC8101RM/D                     |

| SC140 DSP Core Reference Manual | Detailed description of the SC140 family processor core and instruction set                              | MNSC140CORE/D                   |

| Application Notes               | Documents describing specific applications or optimized device operation including code examples         | See the MSC8101 product website |

iv Freescale Semiconductor

# Signals/Connections

1

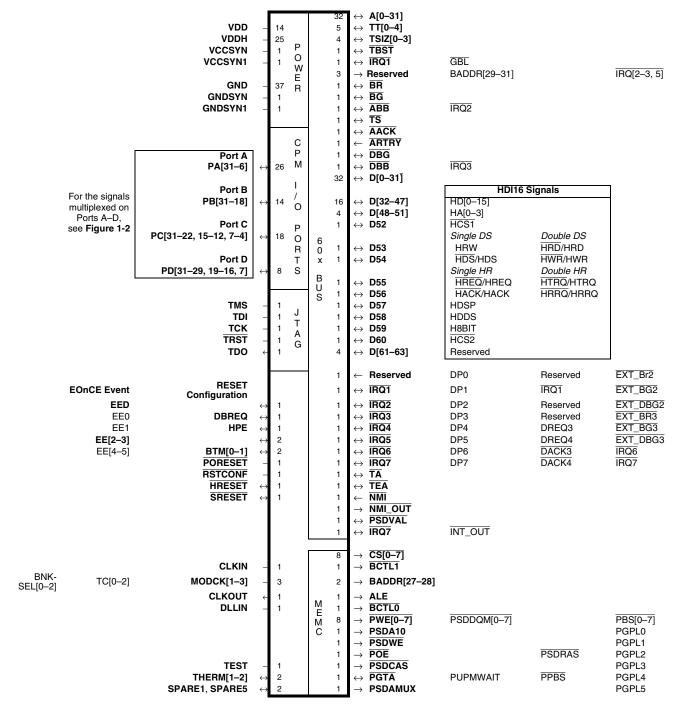

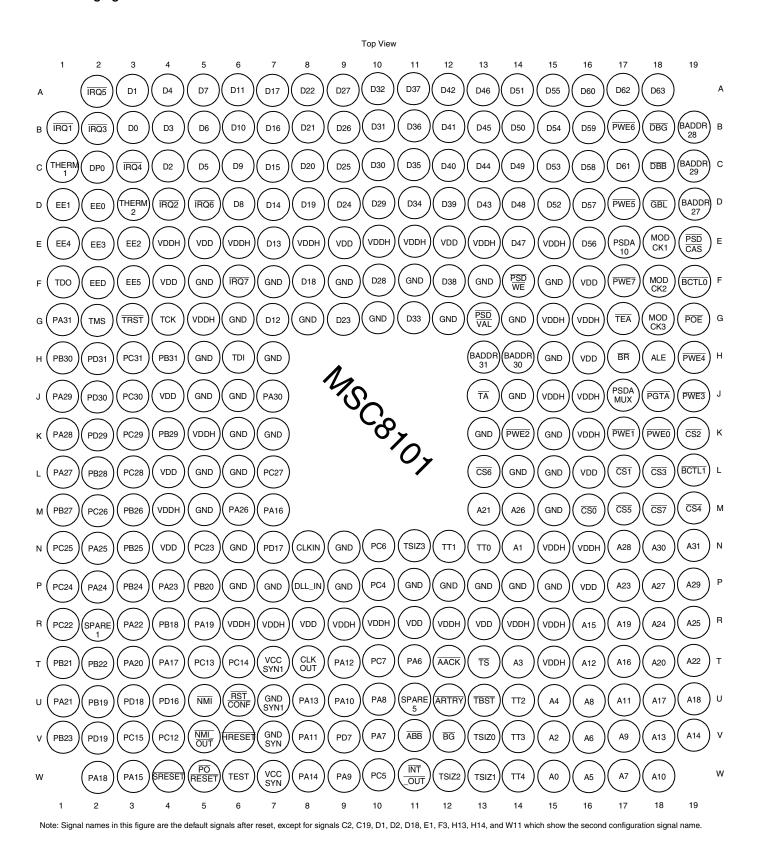

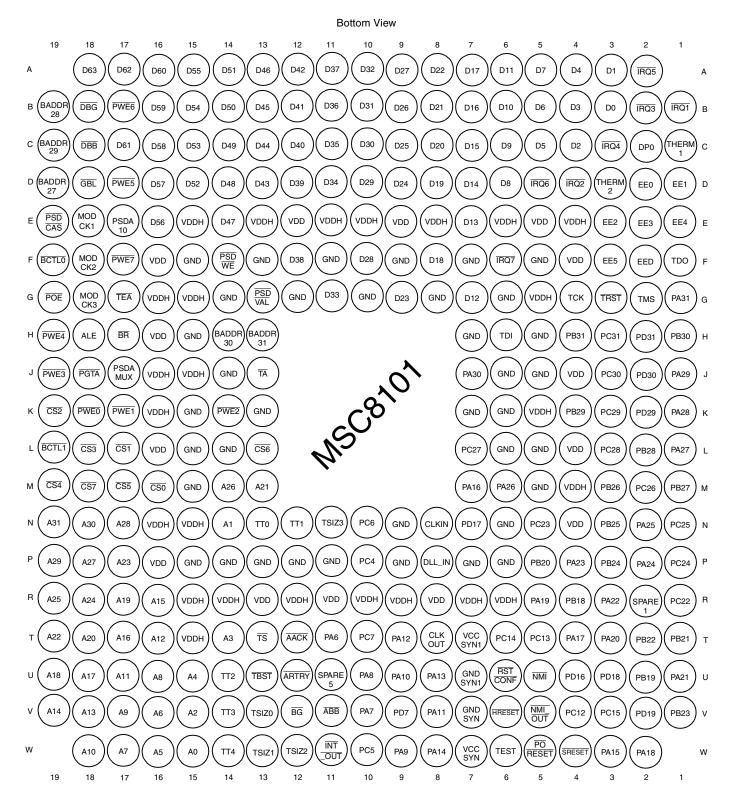

The MSC8101 external signals are organized into functional groups, as shown in **Table 1-1**, **Figure 1-1**, and **Figure 1-2**. **Table 1-1** lists the functional groups, states the number of signal connections in each group, and references the table that gives details on multiplexed signals within each group. **Figure 1-1** shows MSC8101 external signals organized by function. **Figure 1-2** indicates how the parallel input/output (I/O) ports signals are multiplexed. Because the parallel I/O design supported by the MSC8101 communications processor module (CPM) is a subset of the parallel I/O signals supported by the MPC8260 device, port pins are not numbered sequentially.

Table 1-1. MSC8101 Functional Signal Groupings

| Functional Group                                        | Number of Signal<br>Connections | Detailed Description           |                                |

|---------------------------------------------------------|---------------------------------|--------------------------------|--------------------------------|

| Power (V <sub>CC</sub> , V <sub>DD</sub> , and GND)     | 80                              | <b>Table 1-2</b> on page 1-4   |                                |

| Clock                                                   |                                 | 6                              | <b>Table 1-3</b> on page 1-4   |

| Reset, configuration, and EOnCE                         |                                 | 11                             | <b>Table 1-4</b> on page 1-5   |

| System bus, HDI16, and interrupts                       |                                 | 133                            | <b>Table 1-5</b> on page 1-7   |

| Memory Controller                                       |                                 | 27                             | <b>Table 1-6</b> on page 1-13  |

| CPM Input/Output Parallel Ports                         | Port A                          | 26                             | <b>Table 1-7</b> on page 1-16  |

|                                                         | Port B                          | 14                             | <b>Table 1-8</b> on page 1-21  |

|                                                         | Port C                          | 18                             | <b>Table 1-9</b> on page 1-24  |

|                                                         | Port D                          | 8                              | <b>Table 1-10</b> on page 1-33 |

| JTAG Test Access Port                                   | 5                               | <b>Table 1-11</b> on page 1-36 |                                |

| Reserved (denotes connections that are always reserved) |                                 | 5                              | <b>Table 1-12</b> on page 1-36 |

Note: Refer to the System Interface Unit (SIU) chapter in the MSC8101 Reference Manual for details on how to configure these pins.

Figure 1-1. MSC8101 External Signals

1-2 Freescale Semiconductor

|                    | CC1                 |                 |                  |              |                  |                     |               |                 |                  |                    |                           |               |                |                  |              |

|--------------------|---------------------|-----------------|------------------|--------------|------------------|---------------------|---------------|-----------------|------------------|--------------------|---------------------------|---------------|----------------|------------------|--------------|

| ATM/U<br>MPHY      | JTOPIA              |                 | FCC1             |              | 1                |                     |               |                 |                  |                    |                           |               |                |                  |              |

| Master<br>mux poll | MPHY<br>Master      | Ethernet        | HDLC/<br>transp. | HDLC         | 1                |                     |               |                 |                  |                    |                           |               |                |                  |              |

| or Slave           | dir. poll           | MII             | Serial           | Nibble       |                  |                     |               |                 |                  |                    |                           |               |                |                  | GPIC         |

|                    | ENB                 | COL             |                  |              |                  |                     |               |                 |                  |                    |                           |               |                |                  | PA31         |

|                    | TXCLAV0<br>(master) | CRS<br>TX_ER    | RI               | S            |                  |                     |               |                 |                  |                    |                           |               |                |                  | PA30         |

| RX                 | ENB                 | TX_EN           |                  |              |                  |                     |               |                 |                  |                    |                           |               |                |                  | PA28         |

| RXSOC<br>(slave)   |                     | RX_DV           |                  |              |                  |                     |               |                 |                  |                    |                           |               |                |                  | PA27         |

| RXCLAV             |                     | RX_ER           |                  |              |                  |                     |               |                 |                  |                    | SDMA                      |               |                |                  | PA26         |

|                    | XD0<br>XD1          |                 |                  |              |                  |                     |               |                 |                  |                    | MSNUM0<br>MSNUM1          |               |                |                  | PA25         |

|                    | XD2                 |                 |                  |              |                  |                     |               |                 |                  |                    |                           |               |                |                  | PA23         |

|                    | XD3<br>XD4          | TXD3            |                  | TXD3         |                  |                     |               |                 |                  |                    | -                         |               |                |                  | PA22<br>PA21 |

|                    | XD5                 | TXD2            |                  | TXD2         |                  |                     |               |                 |                  |                    |                           |               |                |                  | PA20         |

|                    | XD6<br>XD7          | TXD1<br>TXD0    | TXD              | TXD1<br>TXD0 |                  |                     |               |                 |                  |                    | -                         |               |                |                  | PA18         |

|                    | XD7                 | RXD0            | RXD              | RXD0         |                  |                     |               |                 |                  |                    |                           |               |                |                  | PA17         |

|                    | XD6<br>XD5          | RXD1<br>RXD2    |                  | RXD1<br>RXD2 |                  |                     |               |                 |                  |                    | -                         |               |                |                  | PA16         |

| R                  | XD4                 | RXD3            |                  | RXD3         |                  |                     |               |                 |                  |                    | MON!!!!                   |               |                |                  | PA14         |

|                    | XD3<br>XD2          |                 |                  |              |                  |                     |               | S               | l1               |                    | MSNUM2<br>MSNUM3          | -             |                |                  | PA13         |

| R                  | XD1                 |                 |                  |              |                  |                     | 0116          | TDI             | VIA1             |                    | MSNUM4                    |               |                |                  | PA11         |

| R)                 | XD0                 |                 |                  |              |                  |                     | SMC2<br>SMTXD | Serial<br>L1TXD | Nibble<br>L1TXD0 |                    | MSNUM5                    |               |                |                  | PA10<br>PA9  |

|                    |                     |                 | FCC2             | 1            |                  |                     | SMRXD         | L1RXD           | L1RXD0           |                    | 7                         |               |                |                  | PA8          |

|                    |                     | Ethernet<br>MII | HDLC/<br>transp. | HDLC         | <u> </u>         |                     | SMSYN         |                 | SYNC             | SI2                |                           |               |                |                  | PA7          |

|                    |                     | TX_ER           | Serial           | Nibble       |                  | SCC2<br>RXD         |               | L1RS            | SYNC             | TDMB2<br>L1TXD     |                           |               |                |                  | PA6<br>PB31  |

|                    |                     | RX_DV           |                  |              |                  | TXD                 |               |                 |                  | L1RXD              |                           |               |                |                  | PB30         |

|                    |                     | TX_EN           |                  | <u> </u>     |                  | RTS/TENA            |               |                 |                  | L1RSYNC<br>L1TSYNC |                           |               |                |                  | PB29<br>PB28 |

|                    |                     | RX_ER<br>COL    | R                | 5            |                  | HIS/IENA            |               |                 |                  | TDMC2              |                           |               |                |                  | PB27         |

|                    |                     | CRS             |                  |              |                  |                     |               |                 |                  | L1TXD<br>L1RXD     |                           |               |                |                  | PB27         |

|                    |                     | TXD3            |                  | TXD3         |                  |                     |               |                 | L1TXD3           | L1TSYNC            |                           |               |                |                  | PB25         |

|                    |                     | TXD2            |                  | TXD2         |                  |                     |               |                 | L1RXD3           | L1RSYNC<br>TDMD2   |                           |               |                |                  | PB24         |

|                    |                     | TXD1            |                  | TXD1         |                  |                     |               |                 | L1RXD2           | L1TXD              |                           |               |                |                  | PB23         |

|                    |                     | TXD0<br>RXD0    | TXD<br>RXD       | TXD0<br>RXD0 |                  |                     |               |                 | L1RXD1<br>L1TXD2 | L1RXD<br>L1TSYNC   |                           |               |                |                  | PB22<br>PB21 |

|                    |                     | RXD1            | TIXD             | RXD1         |                  |                     |               |                 | L1TXD1           | L1RSYNC            | I <sup>2</sup> C          | I             |                |                  | PB20         |

|                    |                     | RXD2            |                  | RXD2         |                  |                     |               |                 |                  |                    | SDA                       |               |                |                  | PB19         |

|                    |                     | RXD3            |                  | RXD3         | Ext. Req.        | <u> </u>            |               |                 |                  |                    | SCL                       | BRGs<br>BRG10 | Clocks<br>CLK1 | Timers<br>TGATE1 | PB18<br>PC31 |

|                    |                     |                 |                  |              | EXT1             |                     |               |                 |                  |                    |                           | BRG2O         |                | TOUT1            | PC30         |

|                    |                     |                 |                  |              | SCC1<br>CTS/CLSN |                     |               |                 |                  |                    |                           | BRG3O         | CLK3           | TIN2             | PC29         |

|                    |                     |                 |                  |              |                  | CTS/CLSN            |               |                 |                  |                    | SIU Timer Input           | BRG40         | CLK4           | TIN1/<br>TOUT2   | PC28         |

|                    |                     |                 |                  |              |                  |                     |               |                 |                  |                    | CLK5                      | BRG5O         | CLK5           | TGATE2           | PC27         |

|                    |                     |                 |                  |              | I                |                     |               |                 |                  |                    | TMCLK                     | BRG6O         |                | TOUT3            |              |

|                    |                     |                 |                  |              |                  |                     |               |                 |                  |                    | DMA<br>DACK2              | BRG7O         | CLK7           | TIN4             | PC25         |

|                    |                     |                 |                  |              | Ext. Req.        |                     |               |                 |                  |                    | DREQ2                     | BRG8O         | CLK8           | TIN3/<br>TOUT4   | PC24         |

|                    |                     |                 |                  |              | EXT2             | Į                   |               |                 |                  |                    | DACK1                     |               | CLK9           |                  | PC23         |

| TXA                | DDR0                |                 |                  |              | SCC1<br>CTS/CLSN |                     | SMTXD         | LIS             | ST1              |                    | DREQ1                     |               | CLK10          | <b>.</b>         | PC22<br>PC15 |

| RXA                | DDR0                |                 |                  |              | CD/RENA          |                     |               |                 | ST2              |                    |                           |               |                |                  | PC14         |

|                    | DDR1<br>DDR1        |                 | FC               | C1           | 1                | CTS/CLSN<br>CD/RENA |               |                 | ST4<br>ST3       |                    |                           |               |                |                  | PC13<br>PC12 |

| TXADDR2            | TXADDR2/            |                 | CT               |              |                  | J.J. ILIVA          |               |                 |                  | LIST1              |                           |               |                |                  | PC7          |

|                    | TXCLAV1<br>RXADDR2/ |                 |                  |              |                  |                     |               |                 |                  |                    |                           |               |                |                  |              |

| RXADDR2            | RXCLAV1             |                 | C                |              | Į                |                     | CMC4          |                 |                  | LIST2              |                           |               |                |                  | PC6          |

|                    |                     |                 | FC<br>C1         |              |                  |                     | SMC1<br>SMTXD |                 |                  | LIST3              |                           |               |                |                  | PC5          |

|                    |                     |                 | C                |              | D. (2            |                     | SMRXD         |                 |                  | LIST4              | DD 101/1/25 23 25         |               |                |                  | PC4          |

|                    |                     |                 |                  |              | RXD<br>TXD       |                     |               |                 |                  |                    | DRACK1/DONE1 DRACK2/DONE2 |               |                |                  | PD31         |

|                    | RXCLAV2             |                 |                  |              | RTS/TENA         |                     |               |                 |                  |                    | SPI                       |               |                |                  | PD29         |

|                    | TXCLAV3<br>RXCLAV3  |                 |                  |              |                  |                     |               |                 |                  |                    | SPISEL<br>SPICLK          | BRG10         |                |                  | PD19         |

| RXF                | PRTY                |                 |                  |              |                  |                     |               |                 |                  |                    | SPIMOSI                   | BRG2O         |                |                  | PD17         |

|                    | PRTY<br>TXCLAV2     |                 |                  |              |                  |                     | SMSYN         |                 |                  |                    | SPIMISO                   |               |                |                  | PD16<br>PD7  |

| ארוטטרא            | INOLAVZ             |                 |                  |              |                  |                     |               | <u> </u>        |                  | ved Functio        |                           |               |                |                  | 101          |

Figure 1-2. CPM Port A–D Pin Multiplexed Functionality

# 1.1 Power Signals

Table 1-2. Power and Ground Signal Inputs

| Power Name          | Description                                                                                                                                                                                                                                                     |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>     | Internal Logic Power  V <sub>DD</sub> dedicated for use with the device core. The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the V <sub>DD</sub> power rail.                                     |

| V <sub>DDH</sub>    | Input/Output Power This source supplies power for the I/O buffers. The user must provide adequate external decoupling capacitors.                                                                                                                               |

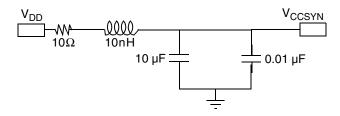

| V <sub>CCSYN</sub>  | System PLL Power  V <sub>CC</sub> dedicated for use with the system Phase Lock Loop (PLL). The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the V <sub>CC</sub> power rail.                        |

| V <sub>CCSYN1</sub> | SC140 PLL Power  V <sub>CC</sub> dedicated for use with the SC140 core PLL. The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the V <sub>CC</sub> power rail.                                       |

| GND                 | System Ground  An isolated ground for the internal processing logic. This connection must be tied externally to all chip ground connections, except GND <sub>SYN</sub> and GND <sub>SYN1</sub> . The user must provide adequate external decoupling capacitors. |

| GND <sub>SYN</sub>  | System PLL Ground Ground dedicated for system PLL use. The connection should be provided with an extremely low-impedance path to ground.                                                                                                                        |

| GND <sub>SYN1</sub> | SC140 PLL Ground 1 Ground dedicated for SC140 core PLL use. The connection should be provided with an extremely low-impedance path to ground.                                                                                                                   |

# 1.2 Clock Signals

Table 1-3. Clock Signals

| Signal Name | Туре   | Signal Description                                                                                               |

|-------------|--------|------------------------------------------------------------------------------------------------------------------|

| CLKIN       | Input  | Clock In Primary clock input to the MSC8101 PLL.                                                                 |

| MODCK1      | Input  | Clock Mode Input 1 Defines the operating mode of internal clock circuits.                                        |

| TC0         | Output | Transfer Code 0 Supplies information that can be useful for debugging bus transactions initiated by the MSC8101. |

| BNKSEL0     | Output | Bank Select 0 Selects the SDRAM bank when the MSC8101 is in 60x-compatible bus mode.                             |

| MODCK2      | Input  | Clock Mode Input 2 Defines the operating mode of internal clock circuits.                                        |

| TC1         | Output | Transfer Code 1 Supplies information that can be useful for debugging bus transactions initiated by the MSC8101. |

| BNKSEL1     | Output | Bank Select 1 Selects the SDRAM bank when the MSC8101 is in 60x-compatible bus mode.                             |

| MODCK3      | Input  | Clock Mode Input 3 Defines the operating mode of internal clock circuits.                                        |

| TC2         | Output | Transfer Code 2 Supplies information that can be useful for debugging bus transactions initiated by the MSC8101. |

| BNKSEL2     | Output | Bank Select 2 Selects the SDRAM bank when the MSC8101 is in 60x-compatible bus mode.                             |

1-4 Freescale Semiconductor

Table 1-3. Clock Signals (Continued)

| Signal Name | Туре   | Signal Description                                                                                      |

|-------------|--------|---------------------------------------------------------------------------------------------------------|

| CLKOUT      | Output | Clock Out The system bus clock.                                                                         |

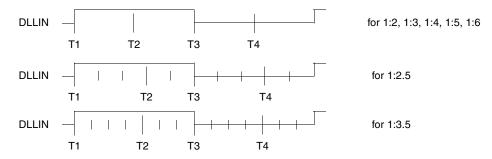

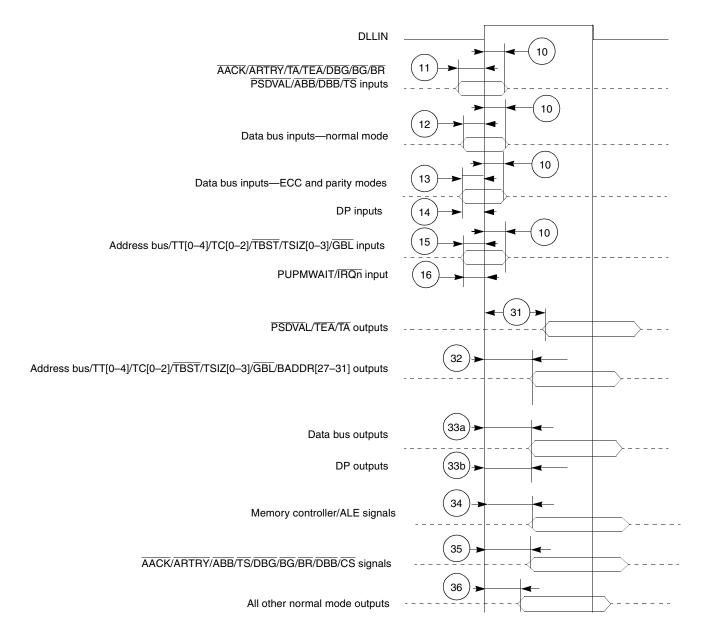

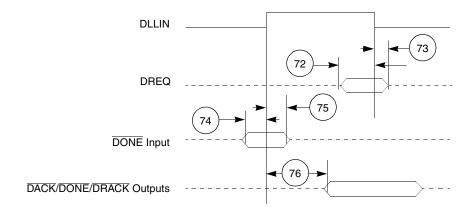

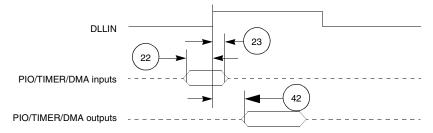

| DLLIN       | Input  | DLLIN Synchronizes with an external device. Note: When the DLL is disabled, connect this signal to GND. |

# 1.3 Reset, Configuration, and EOnCE Event Signals

Table 1-4. Reset, Configuration, and EOnCE Event Signals

| Signal Name      | Туре   | Signal Description                                                                                                                                                                                                 |

|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBREQ            | Input  | Debug Request Determines whether to go into SC140 Debug mode when PORESET is deasserted.                                                                                                                           |

| EE0 <sup>1</sup> |        | Enhanced OnCE (EOnCE) Event 0 After PORESET is deasserted, you can configure EE0 as an input (default) or an output.                                                                                               |

|                  | Input  | Debug request, enable Address Event Detection Channel 0, or generate an EOnCE event.                                                                                                                               |

|                  | Output | Detection by Address Event Detection Channel 0. Used to trigger external debugging equipment.                                                                                                                      |

| HPE              | Input  | Host Port Enable When this pin is asserted during PORESET, the Host port is enabled, the system data bus is 32 bits wide, and the Host must program the reset configuration word.                                  |

| EE1 <sup>1</sup> |        | EOnCE Event 1 After PORESET is deasserted, you can configure EE1 as an input (default) or an output.                                                                                                               |

|                  | Input  | Enable Address Event Detection Channel 1 or generate an EOnCE event.                                                                                                                                               |

|                  | Output | Debug Acknowledge or detection by Address Event Detection Channel 1. Used to trigger external debugging equipment.                                                                                                 |

| EE2 <sup>1</sup> |        | EOnCE Event 2 After PORESET is deasserted, you can configure EE2 as an input (default) or an output.                                                                                                               |

|                  | Input  | Enable Address Event Detection Channel 2 or generate an EOnCE event or enable the Event Counter.                                                                                                                   |

|                  | Output | Detection by Address Event Detection Channel 2. Used to trigger external debugging equipment.                                                                                                                      |

| EE3 <sup>1</sup> |        | EOnCE Event 3  After PORESET is deasserted, you can configure EE3 as an input (default) or an output. See the emulation and debug chapter in the SC140 DSP Core Reference Manual for details on the ERCV Register. |

|                  | Input  | Enable Address Event Detection Channel 3 or generate one of the EOnCE events.                                                                                                                                      |

|                  | Output | The DSP has read the EOnCE Receive Register (ERCV). Triggers external debugging equipment.                                                                                                                         |

**Table 1-4.** Reset, Configuration, and EOnCE Event Signals (Continued)

| Signal Name      | Туре              | Signal Description                                                                                                                                                                                                                     |

|------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BTM[0-1]         | Input             | Boot Mode 0–1  Determines the MSC8101 boot mode when PORESET is deasserted. See the emulation and debug chapter in the SC140 DSP Core Reference Manual for details on how to set these pins.                                           |

| EE4 <sup>1</sup> |                   | EOnCE Event 4  After PORESET is deasserted, you can configure EE4 as an input (default) or an output. See the emulation and debug chapter in the SC140 DSP Core Reference Manual for details on the ETRSMT Register.                   |

|                  | Input             | Enable Address Event Detection Channel 4 or generate an EOnCE event.                                                                                                                                                                   |

|                  | Output            | The DSP wrote the EOnCE Transmit Register (ETRSMT). Triggers external debugging equipment.                                                                                                                                             |

| EE5 <sup>1</sup> |                   | EOnCE Event 5 After PORESET is deasserted, you can configure EE5 as an input (default) or an output.                                                                                                                                   |

|                  | Input             | Enable Address Event Detection Channel 5.                                                                                                                                                                                              |

|                  | Output            | Detection by Address Event Detection Channel 5. Triggers external debugging equipment.                                                                                                                                                 |

| EED <sup>1</sup> |                   | Enhanced OnCE (EOnCE) Event Detection  After PORESET is deasserted, you can configure EED as an input (default) or output:                                                                                                             |

|                  | Input             | Enable the Data Event Detection Channel.                                                                                                                                                                                               |

|                  | Output            | Detection by the Data Event Detection Channel. Triggers external debugging equipment.                                                                                                                                                  |

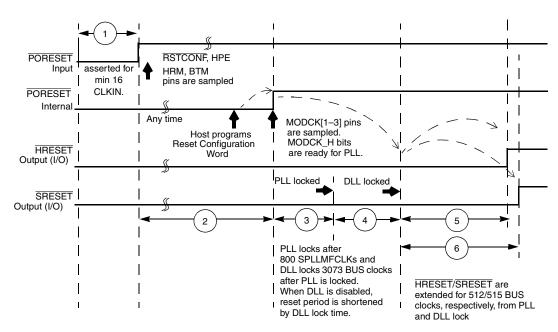

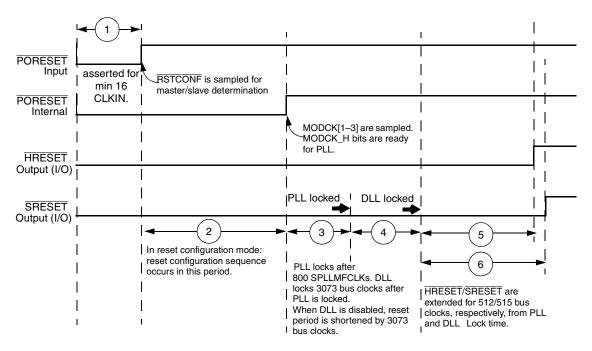

| PORESET          | Input             | Power-On Reset When asserted, this line causes the MSC8101 to enter power-on reset state.                                                                                                                                              |

| RSTCONF          | Input             | Reset Configuration Used during reset configuration sequence of the chip. A detailed explanation of its function is provided in the "Power-On Reset Flow" and "Hardware Reset Configuration" sections of the MSC8101 Reference Manual. |

| HRESET           | Input             | Hard Reset When asserted, this open-drain line causes the MSC8101 to enter the hard reset state.                                                                                                                                       |

| SRESET           | Input             | Soft Reset When asserted, this open-drain line causes the MSC8101 to enter the soft reset state.                                                                                                                                       |

| Note: See the e  | emulation and deb | ug chapter in the SC140 DSP Core Reference Manual for details on how to configure these pins.                                                                                                                                          |

### 1.4 System Bus, HDI16, and Interrupt Signals

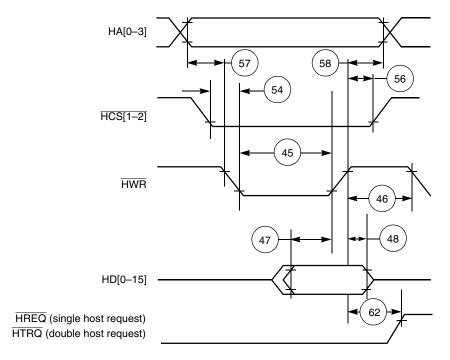

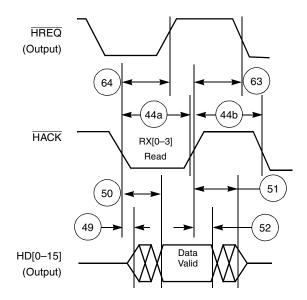

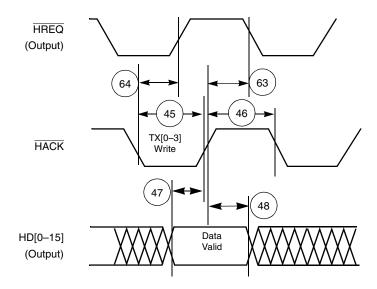

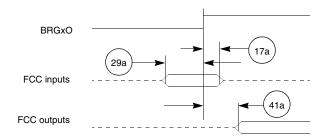

The system bus, HDI16, and interrupt signals are grouped together because they use a common set of signal lines. Individual assignment of a signal to a specific signal line is configured through registers in the System Interface Unit (SIU) and the Host Interface (HDI16). 1-5 describes the signals in this group.

Note: To boot from the host interface, the HDI16 must be enabled by pulling up the HPE signal line during PORESET. The configuration word must then be loaded from the host. The configuration word must set the Internal Space Port Size bit in the Bus Control Register (BCR[ISPS]) to change the system data bus width from 64 bits to 32 bits and reassign the upper 32 bits to their HDI16 functions. Never set the Host Port Enable (HEN) bit in the Host Port Control Register (HPCR) to enable the HDI16, unless the bus size is first changed from 64 bits to 32 bits. Otherwise, unpredictable operation may occur.

1-6 Freescale Semiconductor

MSC8101 Technical Data, Rev. 18

Although there are eight interrupt request  $(\overline{IRQ})$  connections to the core processor, there are multiple external lines that can connect to these internal signal lines. After reset, the default configuration includes two  $\overline{IRQ1}$  and two  $\overline{IRQ7}$  input lines. The designer must select one line for each required interrupt and reconfigure the other external signal line or lines for alternate functions.

Table 1-5. System Bus, HDI16, and Interrupt Signals

| Signal    | Data Flow    | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[0-31]   | Input/Output | Address Bus  When the MSC8101 is in external master bus mode, these pins function as the address bus. The MSC8101 drives the address of its internal bus masters and responds to addresses generated by external bus masters. When the MSC8101 is in Internal Master Bus mode, these pins are used as address lines connected to memory devices and are controlled by the MSC8101 memory controller |

| TT[0-4]   | Input/Output | Bus Transfer Type The bus master drives these pins during the address tenure to specify the type of transaction.                                                                                                                                                                                                                                                                                    |

| TSIZ[0-3] | Input/Output | Transfer Size  The bus master drives these pins with a value indicating the number of bytes transferred in the current transaction.                                                                                                                                                                                                                                                                 |

| TBST      | Input/Output | Bus Transfer Burst The bus master asserts this pin to indicate that the current transaction is a burst transaction (transfers four quad words).                                                                                                                                                                                                                                                     |

| IRQ1      | Input        | Interrupt Request 1 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                        |

| GBL       | Input/Output | Global <sup>1</sup> When a master within the chip initiates a bus transaction, it drives this pin. When an external master initiates a bus transaction, it should drive this pin. Assertion of this pin indicates that the transfer is global and it should be snooped by caches in the system.                                                                                                     |

| Reserved  | Output       | The primary configuration is reserved.                                                                                                                                                                                                                                                                                                                                                              |

| BADDR29   | Output       | Burst Address 29 <sup>1</sup> One of five outputs of the memory controller. These pins connect directly to memory devices controlled by the MSC8101 memory controller.                                                                                                                                                                                                                              |

| ĪRQ2      | Input        | Interrupt Request 2 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                        |

| Reserved  | Output       | The primary configuration is reserved.                                                                                                                                                                                                                                                                                                                                                              |

| BADDR30   | Output       | Burst Address 30 <sup>1</sup> One of five outputs of the memory controller. These pins connect directly to memory devices controlled by the MSC8101 memory controller.                                                                                                                                                                                                                              |

| ĪRQ3      | Input        | Interrupt Request 3 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                        |

| Reserved  | Output       | The primary configuration is reserved.                                                                                                                                                                                                                                                                                                                                                              |

| BADDR31   | Output       | Burst Address 31 <sup>1</sup> One of five outputs of the memory controller. These pins connect directly to memory devices controlled by the MSC8101 memory controller.                                                                                                                                                                                                                              |

| ĪRQ5      | Input        | Interrupt Request 5 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                        |

Table 1-5.

System Bus, HDI16, and Interrupt Signals (Continued)

| Signal  | Data Flow              | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR      | Input/Output<br>Output | Bus Request <sup>2</sup> An output when an external arbiter is used. The MSC8101 asserts this pin to request ownership of the bus.                                                                                                                                                                                                                                                                                 |

|         | Input                  | An input when an internal arbiter is used. An external master should assert this pin to request bus ownership from the internal arbiter.                                                                                                                                                                                                                                                                           |

| BG      | Input/Output<br>Output | Bus Grant <sup>2</sup> An output when an internal arbiter is used. The MSC8101 asserts this pin to grant bus ownership to an external bus master.                                                                                                                                                                                                                                                                  |

|         | Input                  | An input when an external arbiter is used. The external arbiter should assert this pin to grant bus ownership to the MSC8101.                                                                                                                                                                                                                                                                                      |

| ĀBB     | Input/Output<br>Output | Address Bus Busy <sup>1</sup> The MSC8101 asserts this pin for the duration of the address bus tenure. Following an address acknowledge (AACK) signal, which terminates the address bus tenure, the MSC8101 deasserts ABB for a fraction of a bus cycle and then stops driving this pin.                                                                                                                           |

|         | Input                  | The MSC8101 does not assume bus ownership while it this pin is asserted by an external bus master.                                                                                                                                                                                                                                                                                                                 |

| ĪRQ2    | Input                  | Interrupt Request 2 <sup>1</sup> One of the eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                   |

| TS      | Input/Output           | Bus Transfer Start Signals the beginning of a new address bus tenure. The MSC8101 asserts this signal when one of its internal bus masters (SC140 core or DMA controller) begins an address tenure. When the MSC8101 senses this pin being asserted by an external bus master, it responds to the address bus tenure as required (snoop if enabled, access internal MSC8101 resources, memory controller support). |

| AACK    | Input/Output           | Address Acknowledge A bus slave asserts this signal to indicate that it identified the address tenure. Assertion of this signal terminates the address tenure.                                                                                                                                                                                                                                                     |

| ARTRY   | Input                  | Address Retry Assertion of this signal indicates that the bus transaction should be retried by the bus master. The MSC8101 asserts this signal to enforce data coherency with its internal cache and to prevent deadlock situations.                                                                                                                                                                               |

| DBG     | Input/Output<br>Output | Data Bus Grant <sup>2</sup> An output when an internal arbiter is used. The MSC8101 asserts this pin as an output to grant data bus ownership to an external bus master.                                                                                                                                                                                                                                           |

|         | Input                  | An input when an external arbiter is used. The external arbiter should assert this pin as an input to grant data bus ownership to the MSC8101.                                                                                                                                                                                                                                                                     |

| DBB     | Input/Output<br>Output | Data Bus Busy <sup>1</sup> The MSC8101 asserts this pin as an output for the duration of the data bus tenure. Following a TA, which terminates the data bus tenure, the MSC8101 deasserts DBB for a fraction of a bus cycle and then stops driving this pin.                                                                                                                                                       |

|         | Input                  | The MSC8101 does not assume data bus ownership while $\overline{\text{DBB}}$ is asserted by an external bus master.                                                                                                                                                                                                                                                                                                |

| ĪRQ3    | Input                  | Interrupt Request 3 <sup>1</sup> One of the eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                   |

| D[0-31] | Input/Output           | Data Bus Most Significant Word In write transactions the bus master drives the valid data on this bus. In read transactions the slave drives the valid data on this bus. In Host Port Disabled mode, these 32 bits are part of the 64-bit data bus. In Host Port Enabled mode, these bits are used as the bus in 32-bit mode.                                                                                      |

MSC8101 Technical Data, Rev. 18

1-8 Freescale Semiconductor

Table 1-5.

System Bus, HDI16, and Interrupt Signals (Continued)

| Signal    | Data Flow    | Description                                                                                                                                                                                                                                                                         |  |  |

|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D[32–47]  | Input/Output | Data Bus Bits 32–47 In write transactions the bus master drives the valid data on this bus. In read transactions the slave drives the valid data on this bus.                                                                                                                       |  |  |

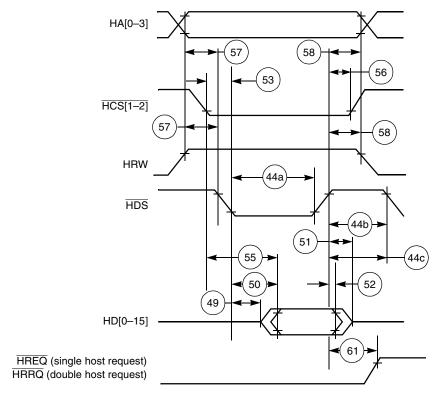

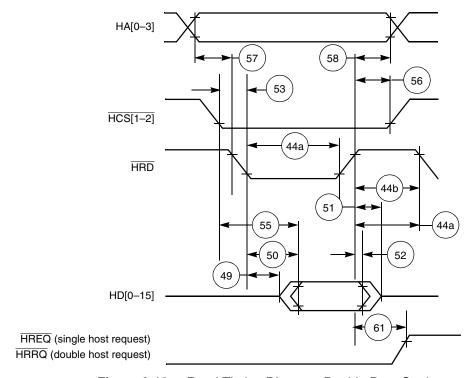

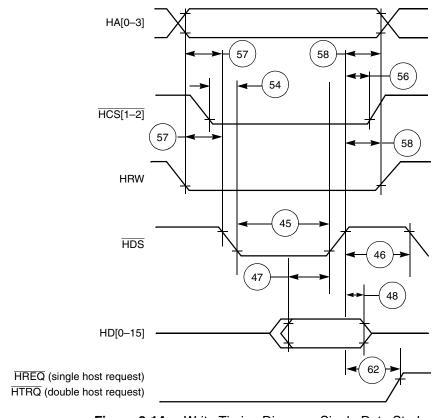

| HD[0-15]  | Input/Output | Host Data <sup>2</sup> When the HDI16 interface is enabled, these signals are lines 0-15 of the bidirectional tri-state data bus.                                                                                                                                                   |  |  |

| D[48–51]  | Input/Output | Data Bus Bits 48–51 In write transactions the bus master drives the valid data on these pins. In read transactions the slave drives the valid data on these pins.                                                                                                                   |  |  |

| HA[0-3]   | Input        | Host Address Line 0–3 <sup>3</sup> When the HDI16 interface bus is enabled, these lines address internal host registers.                                                                                                                                                            |  |  |

| D52       | Input/Output | Data Bus Bit 52 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                           |  |  |

| HCS1      | Input        | Host Chip Select <sup>3</sup> When the HDI16 interface is enabled, this is one of the two chip-select pins. The HDI16 chip select is a logical OR of HCS1 and HCS2.                                                                                                                 |  |  |

| D53       | Input/Output | Data Bus Bit 53 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                           |  |  |

| HRW       | Input        | Host Read Write Select <sup>3</sup> When the HDI16 interface is enabled in Single Strobe mode, this is the read/write input (HRW).                                                                                                                                                  |  |  |

| HRD/HRD   | Input        | Host Read Strobe <sup>3</sup> When the HDI16 is programmed to interface with a double data strobe host bus, this pin is the read data strobe Schmitt trigger input (HRD/HRD). The polarity of the data strobe is programmable.                                                      |  |  |

| D54       | Input/Output | Data Bus Bit 54 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                           |  |  |

| HDS/HDS   | Input        | Host Data Strobe <sup>3</sup> When the HDI16 is programmed to interface with a single data strobe host bus, this pin is the data strobe Schmitt trigger input (HDS/HDS). The polarity of the data strobe is programmable.                                                           |  |  |

| HWR/HWR   | Input        | Host Write Data Strobe <sup>3</sup> When the HDI16 is programmed to interface with a double data strobe host bus, this pin is the write data strobe Schmitt trigger input (HWR/HWR). The polarity of the data strobe is programmable.                                               |  |  |

| D55       | Input/Output | Data Bus Bit 55 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                           |  |  |

| HREQ/HREQ | Output       | Host Request <sup>3</sup> When the HDI16 is programmed to interface with a single host request host bus, this pin is the host request output (HREQ/HREQ). The polarity of the host request is programmable. The host request may be programmed as a driven or open-drain output.    |  |  |

| HTRQ/HTRQ | Output       | Transmit Host Request <sup>3</sup> When the HDI16 is programmed to interface with a double host request host bus, this pin is the transmit host request output (HTRQ/HTRQ). The signal can be programmed as driven or open drain. The polarity of the host request is programmable. |  |  |

#### Signals/Connections

Table 1-5.

System Bus, HDI16, and Interrupt Signals (Continued)

| Signal    | Data Flow    | Description                                                                                                                                                                                                                                                                       |  |  |  |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D56       | Input/Output | Data Bus Bit 56 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |  |

| HACK/HACK | Output       | Host Acknowledge <sup>3</sup> When the HDI16 is programmed to interface with a single host request host bus, this pin is the host acknowledge Schmitt trigger input (HACK). The polarity of the host acknowledge is programmable.                                                 |  |  |  |

| HRRQ/HRRQ | Output       | Receive Host Request <sup>3</sup> When the HDI16 is programmed to interface with a double host request host bus, this pin is the receive host request output (HRRQ/HRRQ). The signal can be programmed as driven or open drain. The polarity of the host request is programmable. |  |  |  |

| D57       | Input/Output | Data Bus Bit 57 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |  |

| HDSP      | Input        | Host Data Strobe Polarity <sup>3</sup> When the HDI16 interface is enabled, this pin is the host data strobe polarity (HDSP).                                                                                                                                                     |  |  |  |

| D58       | Input/Output | Data Bus Bit 58 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |  |

| HDDS      | Input        | Host Dual Data Strobe <sup>3</sup> When the HDI16 interface is enabled, this pin is the host dual data strobe (HDDS).                                                                                                                                                             |  |  |  |

| D59       | Input/Output | Data Bus Bit 59 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |  |

| H8BIT     | Input        | H8BIT <sup>3</sup> When the HDI16 interface is enabled, this bit determines if the interface is in 8-bit or 16-bit mode.                                                                                                                                                          |  |  |  |

| D60       | Input/Output | Data Bus Bit 60 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |  |

| HCS2      | Input        | Host Chip Select <sup>3</sup> When the HDI16 interface is enabled, this is one of the two chip-select pins. The HDI16 chip select is a logical OR of HCS1 and HCS2.                                                                                                               |  |  |  |

| D[61–63]  | Input/Output | Data Bus Bits 61–63 Used only in 60x-mode-only mode. In write transactions the bus master drives the valid data on this bus. In read transactions the slave drives the valid data on this bus.                                                                                    |  |  |  |

| Reserved  |              | These dedicated signals are reserved when the HDI16 is enabled. <sup>3</sup>                                                                                                                                                                                                      |  |  |  |

| Reserved  | Input        | The primary configuration is reserved.                                                                                                                                                                                                                                            |  |  |  |

| DP0       | Input/Output | Data Parity 0 <sup>1</sup> The agent that drives the data bus also drives the data parity signals. The value driven on the data parity zero pin should give odd parity (odd number of ones) on the group of signals that includes data parity 0 and D[0–7].                       |  |  |  |

| EXT_BR2   | Input        | External Bus Request 2 <sup>1,2</sup> An external master asserts this pin to request bus ownership from the internal arbiter.                                                                                                                                                     |  |  |  |

1-10 Freescale Semiconductor

Table 1-5.

System Bus, HDI16, and Interrupt Signals (Continued)

| Signal   | Data Flow    | Description                                                                                                                                                                                                                                                          |  |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IRQ1     | Input        | Interrupt Request 1 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                         |  |

| DP1      | Input/Output | Data Parity 1 <sup>1</sup> The agent that drives the data bus also drives the data parity signals. The value driven on the data parity one pin should give odd parity (odd number of ones) on the group of signals that includes data parity 1 and D[8–15].          |  |

| EXT_BG2  | Output       | External Bus Grant 2 <sup>1,2</sup> The MSC8101 asserts this pin to grant bus ownership to an external bus master.                                                                                                                                                   |  |

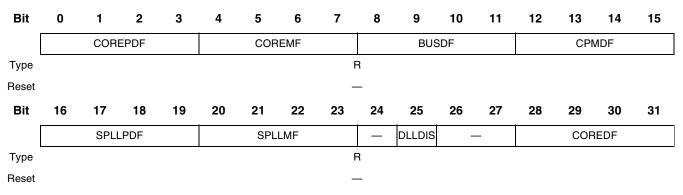

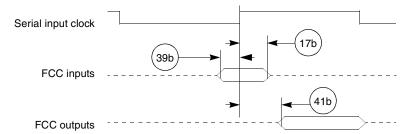

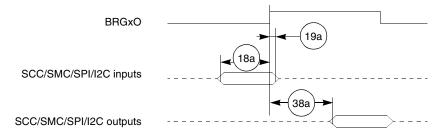

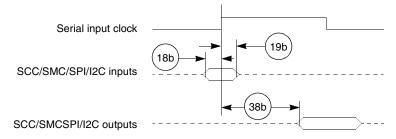

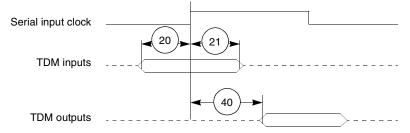

| ĪRQ2     | Input        | Interrupt Request 2 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                         |  |