# 捷多邦,专业PCB打样工厂,24小时加急出**懶SP430x11x** MIXED SIGNAL MICROCONTROLLERS

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

- Low Supply Voltage Range 2.5 V to 5.5 V

- **Ultralow-Power Consumption:**

- Active Mode: 330 μA at 1 MHz, 3 V

- Standby Mode: 1.5 μA

- Off Mode (RAM Retention): 0.1 μA

- Wake-up From Standby Mode in less than 6 us

- 16-Bit RISC Architecture, 200 ns Instruction **Cycle Time**

- **Basic Clock Module Configurations:**

- Various Internal Resistors

- Single External Resistor

- 32 kHz Crystal

- High Frequency Crystal

- Resonator

- External Clock Source

- 16-Bit Timer A With Three Capture/Compare Registers

- **Serial Onboard Programming**

- **Program Code Protection by Security Fuse**

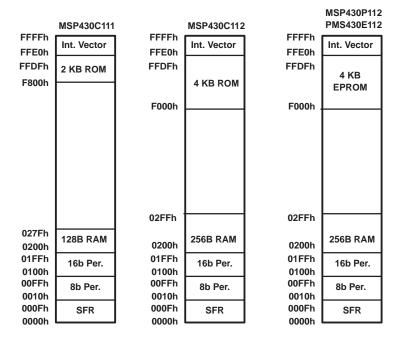

- Family Members Include: MSP430C111: 2k Byte ROM, 128 Byte RAM MSP430C112: 4k Byte ROM, 256 Byte RAM MSP430P112: 4k Byte OTP, 256 Byte RAM

- **EPROM Version Available for Prototyping:**  PMS430E112: 4k Byte EPROM, 256 Byte **RAM**

- Available in a 20-Pin Plastic Small-Outline Wide Body (SOWB) Package, 20-Pin Ceramic Dual-In-Line (CDIP) Package (EPROM Only)

- For Complete Module Descriptions, Refer to the MSP430x1xx Family User's Guide, Literature Number SLAU049

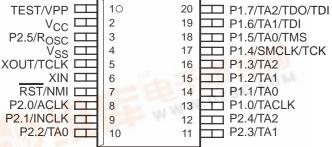

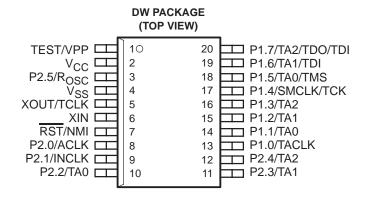

DW PACKAGE

#### description

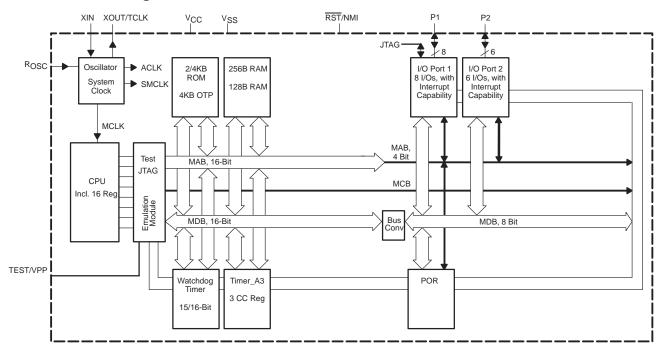

The Texas Instruments MSP430 family of ultralow power microcontrollers consist of several devices featuring different sets of peripherals targeted for various applications. The architecture, combined with five low power modes is optimized to achieve extended battery life in portable measurement applications. The device features a powerful 16-bit RISC CPU, 16-bit registers, and constant generators that attribute to maximum code efficiency. The digitally controlled oscillator (DCO) allows wake-up from low-power modes to active mode in less than 6µs.

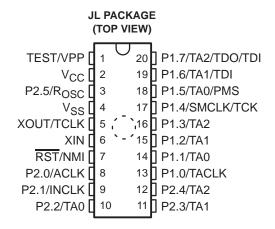

(TOP VIEW) 10

The MSP430x11x series is an ultra low-power mixed signal microcontroller with a built in 16-bit timer and fourteen I/O pins.

Typical applications include sensor systems that capture analog signals, convert them to digital values, and then process the data and display them or transmit them to a host system. Stand alone RF sensor front-end is another area of application.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### **AVAILABLE OPTIONS**

|               | PACKAGED DEVICES                                |                        |  |  |  |

|---------------|-------------------------------------------------|------------------------|--|--|--|

| TA            | SOWB<br>20-Pin<br>(DW)                          | CDIP<br>20-Pin<br>(JL) |  |  |  |

| -40°C to 85°C | MSP430C111IDW<br>MSP430C112IDW<br>MSP430P112IDW |                        |  |  |  |

| 25°C          | _                                               | PMS430E112JL           |  |  |  |

# functional block diagram

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

# **Terminal Functions**

| TERMINAL              |     | 1/0 | DESCRIPTION                                                                                                                     |

|-----------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | NO. |     |                                                                                                                                 |

| P1.0/TACLK            | 13  | I/O | General-purpose digital I/O pin/Timer_A, clock signal TACLK input                                                               |

| P1.1/TA0              | 14  | I/O | General-purpose digital I/O pin/Timer_A, Capture: CCI0A input, Compare: Out0 output                                             |

| P1.2/TA1              | 15  | I/O | General-purpose digital I/O pin/Timer_A, Capture: CCI1A input, Compare: Out1 output                                             |

| P1.3/TA2              | 16  | I/O | General-purpose digital I/O pin/Timer_A, Capture: CCI2A input, Compare: Out2 output                                             |

| P1.4/SMCLK/TCK        | 17  | I/O | General-purpose digital I/O pin/SMCLK signal output/Test clock, input terminal for device programming and test                  |

| P1.5/TA0/TMS          | 18  | I/O | General-purpose digital I/O pin/Timer_A, Compare: Out0 output/test mode select, input terminal for device programming and test. |

| P1.6/TA1/TDI          | 19  | I/O | General-purpose digital I/O pin/Timer_A, Compare: Out1 output/test data input terminal.                                         |

| P1.7/TA2/TDO/TDI      | 20  | I/O | General-purpose digital I/O pin/Timer_A, Compare: Out2 output/test data output terminal or data input during programming.       |

| P2.0/ACLK             | 8   | I/O | General-purpose digital I/O pin/ACLK output                                                                                     |

| P2.1/INCLK            | 9   | I/O | General-purpose digital I/O pin/Timer_A, clock signal at INCLK                                                                  |

| P2.2/TA0              | 10  | I/O | General-purpose digital I/O pin/Timer_A, Capture: CCI0B input, Compare: Out0 output                                             |

| P2.3/TA1              | 11  | I/O | General-purpose digital I/O pin/Timer_A, Capture: CCI1B input, Compare: Out1 output                                             |

| P2.4/TA2              | 12  | I/O | General-purpose digital I/O pin/Timer_A, Compare: Out2 output                                                                   |

| P2.5/R <sub>OSC</sub> | 3   | I/O | General-purpose digital I/O pin/Input for external resistor that defines the DCO nominal frequency                              |

| RST/NMI               | 7   | I   | Reset or nonmaskable interrupt input                                                                                            |

| TEST/VPP              | 1   | I   | Selects test mode for JTAG pins on Port1/programming voltage input during EPROM programming                                     |

| VCC                   | 2   |     | Supply voltage                                                                                                                  |

| Vss                   | 4   |     | Ground reference                                                                                                                |

| XIN                   | 6   | I   | Input terminal of crystal oscillator                                                                                            |

| XOUT/TCLK             | 5   | I/O | Output terminal of crystal oscillator or test clock input                                                                       |

#### short-form description

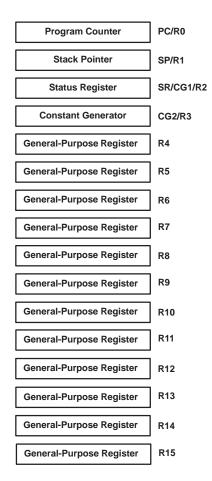

#### **CPU**

The MSP430 CPU has a 16-bit RISC architecture that is highly transparent to the application. All operations, other than program-flow instructions, are performed as register operations in conjunction with seven addressing modes for source operand and four addressing modes for destination operand.

The CPU is integrated with 16 registers that provide reduced instruction execution time. The register-to-register operation execution time is one cycle of the CPU clock.

Four of the registers, R0 to R3, are dedicated as program counter, stack pointer, status register, and constant generator respectively. The remaining registers are general-purpose registers.

Peripherals are connected to the CPU using data, address, and control buses, and can be handled with all instructions.

#### instruction set

The instruction set consists of 51 instructions with three formats and seven address modes. Each instruction can operate on word and byte data. Table 1 shows examples of the three types of instruction formats; the address modes are listed in Table 2.

**Table 1. Instruction Word Formats**

| Dual operands, source-destination | e.g. ADD R4,R5 | R4 + R5> R5           |

|-----------------------------------|----------------|-----------------------|

| Single operands, destination only | e.g. CALL R8   | PC>(TOS), R8> PC      |

| Relative jump, un/conditional     | e.g. JNE       | Jump-on-equal bit = 0 |

**Table 2. Address Mode Descriptions**

| ADDRESS MODE           | s | D | SYNTAX          | EXAMPLE          | OPERATION                   |

|------------------------|---|---|-----------------|------------------|-----------------------------|

| Register               | • | • | MOV Rs,Rd       | MOV R10,R11      | R10> R11                    |

| Indexed                | • | • | MOV X(Rn),Y(Rm) | MOV 2(R5),6(R6)  | M(2+R5)> M(6+R6)            |

| Symbolic (PC relative) | • | • | MOV EDE,TONI    |                  | M(EDE)> M(TONI)             |

| Absolute               | • | • | MOV &MEM,&TCDAT |                  | M(MEM)> M(TCDAT)            |

| Indirect               | • |   | MOV @Rn,Y(Rm)   | MOV @R10,Tab(R6) | M(R10)> M(Tab+R6)           |

| Indirect autoincrement | • |   | MOV @Rn+,Rm     | MOV @R10+,R11    | M(R10)> R11<br>R10 + 2> R10 |

| Immediate              | • |   | MOV #X,TONI     | MOV #45,TONI     | #45> M(TONI)                |

NOTE: S = source D = destination

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

#### operating modes

The MSP430 has one active mode and five software selectable low-power modes of operation. An interrupt event can wake up the device from any of the five low-power modes, service the request and restore back to the low-power mode on return from the interrupt program.

The following six operating modes can be configured by software:

- Active mode AM:

- All clocks are active

- Low-power mode 0 (LPM0);

- CPU is disabled ACLK and SMCLK remain active. MCLK is disabled

- Low-power mode 1 (LPM1);

- CPU is disabled

ACLK and SMCLK remain active. MCLK is disabled

DCO's dc-generator is disabled if DCO not used in active mode

- Low-power mode 2 (LPM2);

- CPU is disabled

MCLK and SMCLK are disabled

DCO's dc-generator remains enabled

ACLK remains active

- Low-power mode 3 (LPM3);

- CPU is disabled MCLK and SMCLK are disabled DCO's dc-generator is disabled ACLK remains active

- Low-power mode 4 (LPM4);

- CPU is disabled

ACLK is disabled

MCLK and SMCLK are disabled

DCO's dc-generator is disabled

Crystal oscillator is stopped

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

#### interrupt vector addresses

The interrupt vectors and the power-up starting address are located in the ROM with an address range of 0FFFFh-0FFE0h. The vector contains the 16-bit address of the appropriate interrupt handler instruction sequence.

| INTERRUPT SOURCE                       | INTERRUPT FLAG                                            | SYSTEM INTERRUPT                  | WORD ADDRESS | PRIORITY    |

|----------------------------------------|-----------------------------------------------------------|-----------------------------------|--------------|-------------|

| Power-up, external reset, watchdog     | WDTIFG (see Note1)                                        | Reset                             | 0FFFEh       | 15, highest |

| NMI, oscillator fault                  | NMIIFG, OFIFG (see Note 1)                                | (non)-maskable,<br>(non)-maskable | 0FFFCh       | 14          |

|                                        |                                                           |                                   | 0FFFAh       | 13          |

|                                        |                                                           |                                   | 0FFF8h       | 12          |

|                                        |                                                           |                                   | 0FFF6h       | 11          |

| Watchdog Timer                         | WDTIFG                                                    | maskable                          | 0FFF4h       | 10          |

| Timer_A3                               | TACCR0 CCIFG (see Note 2)                                 | maskable                          | 0FFF2h       | 9           |

| Timer_A3                               | TACCR1 and TACCR2<br>CCIFGs, TAIFG<br>(see Notes 1 and 2) | FGs, TAIFG maskable               |              | 8           |

|                                        |                                                           |                                   | 0FFEEh       | 7           |

|                                        |                                                           |                                   | 0FFECh       | 6           |

|                                        |                                                           |                                   | 0FFEAh       | 5           |

|                                        |                                                           |                                   | 0FFE8h       | 4           |

| I/O Port P2 (eight flags – see Note 3) | P2IFG.0 to P2IFG.7<br>(see Notes 1 and 2)                 | maskable                          | 0FFE6h       | 3           |

| I/O Port P1 (eight flags)              | P1IFG.0 to P1IFG.7<br>(see Notes 1 and 2)                 | maskable                          | 0FFE4h       | 2           |

|                                        |                                                           |                                   | 0FFE2h       | 1           |

|                                        |                                                           |                                   | 0FFE0h       | 0, lowest   |

NOTES: 1. Multiple source flags

- 2. Interrupt flags are located in the module

- 3. There are eight Port P2 interrupt flags, but only six Port P2 I/O pins (P2.0-5) are implemented on the '11x devices.

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

#### special function registers

Most interrupt and module enable bits are collected into the lowest address space. Special function register bits that are not allocated to a functional purpose are not physically present in the device. Simple software access is provided with this arrangement.

#### interrupt enable 1

| Address | 7 | 6 | 5 | 4     | 3 | 2 | 1    | 0     |

|---------|---|---|---|-------|---|---|------|-------|

| 0h      |   |   |   | NMIIE |   |   | OFIE | WDTIE |

|         |   |   |   | rw-0  |   |   | rw-0 | rw-0  |

WDTIE: Watchdog Timer interrupt enable. Inactive if watchdog mode is selected. Active if Watchdog Timer

is configured in interval timer mode.

OFIE: Oscillator fault enable

NMIIE: (Non)maskable interrupt enable

#### interrupt flag register 1

| Address | 7 | 6 | 5 | 4      | 3 | 2 | 1     | 0      |

|---------|---|---|---|--------|---|---|-------|--------|

| 02h     |   |   |   | NMIIFG |   |   | OFIFG | WDTIFG |

|         |   |   |   | rw-0   |   |   | rw-1  | rw-(0) |

WDTIFG: Set on Watchdog Timer overflow (in watchdog mode) or security key violation.

Reset on V<sub>CC</sub> power-up or a reset condition at RST/NMI pin in reset mode.

OFIFG: Flag set on oscillator fault NMIIFG: Set via RST/NMI-pin

**Legend rw:** Bit can be read and written.

rw-0,1: Bit can be read and written. It is Reset or Set by PUCrw-(0,1): Bit can be read and written. It is Reset or Set by POR

SFR bit is not present in device.

#### memory organization

#### peripherals

Peripherals are connected to the CPU through data, address, and control busses and can be handled using all instructions. For complete module descriptions, refer to the MSP430x1xx Family User's Guide, literature number SLAU049.

#### oscillator and system clock

The clock system is supported by the basic clock module that includes support for a 32768-Hz watch crystal oscillator, an internal digitally-controlled oscillator (DCO) and a high frequency crystal oscillator. The basic clock module is designed to meet the requirements of both low system cost and low-power consumption. The internal DCO provides a fast turn-on clock source and stabilizes in less than 6  $\mu$ s. The basic clock module provides the following clock signals:

- Auxiliary clock (ACLK), sourced from a 32768-Hz watch crystal or a high frequency crystal.

- Main clock (MCLK), the system clock used by the CPU.

- Sub-Main clock (SMCLK), the sub-system clock used by the peripheral modules.

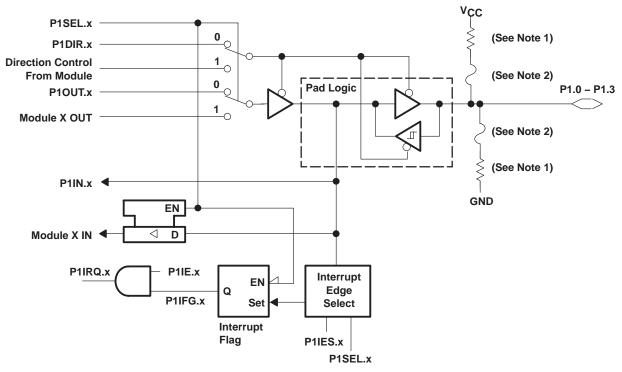

#### digital I/O

There are two 8-bit I/O ports implemented—ports P1 and P2 (only six P2 I/O signals are available on external pins):

- All individual I/O bits are independently programmable.

- Any combination of input, output, and interrupt conditions is possible.

- Edge-selectable interrupt input capability for all the eight bits of port P1 and six bits of port P2.

- Read/write access to port-control registers is supported by all instructions.

#### NOTE:

Six bits of Port P2, P2.0 to P2.5, are available on external pins – but all control and data bits for Port P2 are implemented.

## watchdog timer

The primary function of the watchdog timer (WDT) module is to perform a controlled system restart after a software problem occurs. If the selected time interval expires, a system reset is generated. If the watchdog function is not needed in an application, the module can be configured as an interval timer and can generate interrupts at selected time intervals.

#### timer\_A3

Timer\_A3 is a 16-bit timer/counter with three capture/compare registers. Timer\_A3 can support multiple capture/compares, PWM outputs, and interval timing. Timer\_A3 also has extensive interrupt capabilities. Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers.

|                  | Timer_A3 Signal Connections |                   |              |                      |                   |  |  |  |  |  |

|------------------|-----------------------------|-------------------|--------------|----------------------|-------------------|--|--|--|--|--|

| Input Pin Number | Device Input Signal         | Module Input Name | Module Block | Module Output Signal | Output Pin Number |  |  |  |  |  |

| 13 - P1.0        | TACLK                       | TACLK             |              |                      |                   |  |  |  |  |  |

|                  | ACLK                        | ACLK              | _            | NA                   |                   |  |  |  |  |  |

|                  | SMCLK                       | SMCLK             | Timer        | NA                   |                   |  |  |  |  |  |

| 9 - P2.1         | INCLK                       | INCLK             |              |                      |                   |  |  |  |  |  |

| 14 - P1.1        | TA0                         | CCI0A             |              |                      | 14 - P1.1         |  |  |  |  |  |

| 10 - P2.2        | TA0                         | CCI0B             | 0000         | T4.0                 | 18 - P1.5         |  |  |  |  |  |

|                  | DVSS                        | GND               | CCR0         | TA0                  | 10 - P2.2         |  |  |  |  |  |

|                  | DVCC                        | VCC               |              |                      |                   |  |  |  |  |  |

| 15 - P1.2        | TA1                         | CCI1A             |              |                      | 15 - P1.2         |  |  |  |  |  |

| 11 - P2.3        | TA1                         | CCI1B             | 005/         |                      | 19 - P1.6         |  |  |  |  |  |

|                  | DV <sub>SS</sub>            | GND               | CCR1         | TA1                  | 11 - P2.3         |  |  |  |  |  |

|                  | DV <sub>CC</sub>            | Vcc               |              |                      |                   |  |  |  |  |  |

| 16 - P1.3        | TA2                         | CCI2A             |              |                      | 16 - P1.3         |  |  |  |  |  |

|                  | ACLK (internal)             | CCI2B             | 0000         | T4.0                 | 20 - P1.7         |  |  |  |  |  |

|                  | DVSS                        | GND               | CCR2         | TA2                  | 12 - P2.4         |  |  |  |  |  |

|                  | DVCC                        | Vcc               |              |                      |                   |  |  |  |  |  |

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

# peripheral file map

| PERIPHERALS WITH WORD ACCESS |                                                                                                                                                                                                                                                                                            |                                                              |                                                                                                                                              |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Watchdog                     | Watchdog/Timer Control                                                                                                                                                                                                                                                                     | WDTCTL                                                       | 0120h                                                                                                                                        |  |  |  |

| Timer_A                      | Timer_A Interrupt Vector Timer_A Control Cap/Com Control Cap/Com Control Cap/Com Control Reserved Reserved Reserved Reserved Timer_A Register Cap/Com Register Cap/Com Register Cap/Com Register Reserved | TAIV TACTL TACCTL0 TACCTL1 TACCTL2  TAR TACCR0 TACCR1 TACCR2 | 012Eh<br>0160h<br>0162h<br>0164h<br>0166h<br>0168h<br>016Ch<br>016Ch<br>0170h<br>0172h<br>0174h<br>0176h<br>0178h<br>017Ah<br>017Ch<br>017Eh |  |  |  |

| PER                          | PIPHERALS WITH BYTE ACCESS                                                                                                                                                                                                                                                                 | S                                                            |                                                                                                                                              |  |  |  |

| Basic Clock                  | Basic Clock Sys. Control2<br>Basic Clock Sys. Control1<br>DCO Clock Freq. Control                                                                                                                                                                                                          | BCSCTL2<br>BCSCTL1<br>DCOCTL                                 | 058h<br>057h<br>056h                                                                                                                         |  |  |  |

| EPROM                        | EPROM Control                                                                                                                                                                                                                                                                              | EPCTL                                                        | 054h                                                                                                                                         |  |  |  |

| Port P2                      | Port P2 Selection Port P2 Interrupt Enable Port P2 Interrupt Edge Select Port P2 Interrupt Flag Port P2 Direction Port P2 Output Port P2 Input                                                                                                                                             | P2SEL<br>P2IE<br>P2IES<br>P2IFG<br>P2DIR<br>P2OUT<br>P2IN    | 02Eh<br>02Dh<br>02Ch<br>02Bh<br>02Ah<br>029h<br>028h                                                                                         |  |  |  |

| Port P1                      | Port P1 Selection Port P1 Interrupt Enable Port P1 Interrupt Edge Select Port P1 Interrupt Flag Port P1 Direction Port P1 Output Port P1 Input                                                                                                                                             | P1SEL<br>P1IE<br>P1IES<br>P1IFG<br>P1DIR<br>P1OUT<br>P1IN    | 026h<br>025h<br>024h<br>023h<br>022h<br>021h<br>020h                                                                                         |  |  |  |

| Special Function             | SFR Interrupt Flag1<br>SFR Interrupt Enable1                                                                                                                                                                                                                                               | IFG1<br>IE1                                                  | 002h<br>000h                                                                                                                                 |  |  |  |

## absolute maximum ratings†

| Voltage applied at V <sub>CC</sub> to V <sub>SS</sub>       | 0.3 V to 6 V   |

|-------------------------------------------------------------|----------------|

| Voltage applied to any pin (see Note)                       |                |

| Diode current at any device terminal                        | ±2 mA          |

| Storage temperature, T <sub>stq</sub> (unprogrammed device) | –55°C to 150°C |

| Storage temperature, T <sub>sto</sub> (programmed device)   |                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|                                                                        |                       | MIN | NOM   | MAX  | UNITS   |

|------------------------------------------------------------------------|-----------------------|-----|-------|------|---------|

|                                                                        | MSP430C11x            | 2.5 |       | 5.5  | .,      |

| Supply voltage, VCC                                                    | MSP430P112            | 2.7 |       | 5.5  | V       |

|                                                                        | PMS430E112            | 2.7 |       | 5.5  | V       |

|                                                                        | MSP430P112            | 4.5 | 5     | 5.5  | V       |

| Supply voltage during programming, V <sub>CC</sub>                     | MSP430E112            | 4.5 | 5     | 5.5  | V       |

|                                                                        | MSP430C11x            | 40  |       | 0.5  |         |

| Operating free-air temperature range, TA                               | MSP430P112            | -40 |       | 85   | °C      |

|                                                                        | PMS430E112            |     | 25    |      |         |

| XTAL frequency, f <sub>(XTAL)</sub> ,(ACLK signal)                     |                       |     | 32768 |      | Hz      |

| (PMC420P/E440) (MCLIV eignel)                                          | V <sub>CC</sub> = 3 V | dc  |       | 2    |         |

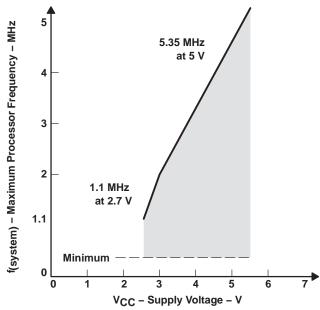

| Processor frequency f <sub>(system)</sub> (PMS430P/E112) (MCLK signal) | V <sub>CC</sub> = 5 V | dc  |       | 5.35 | MHz     |

| (MOLIV et al.) (MORAGOOMA)                                             | VCC = 3 V             | dc  | 2.7   |      | N 41 1- |

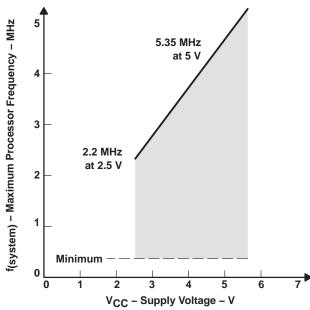

| Processor frequency f <sub>(system)</sub> (MCLK signal) (MSP430C11x)   | V <sub>CC</sub> = 5 V | dc  |       | 5.35 | MHz     |

NOTE: Minimum processor frequency is defined by system clock.

Figure 1. C Version Frequency vs Supply Voltage

NOTE: All voltages referenced to V<sub>SS</sub>. The JTAG fuse-blow voltage, V<sub>FB</sub>, is allowed to exceed the absolute maximum rating. The voltage is applied to the TEST pin when blowing the JTAG fuse.

# recommended operating conditions (continued)

NOTE: Minimum processor frequency is defined by system clock.

Figure 2. P/E Version Frequency vs Supply Voltage

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

#### supply current (into V<sub>CC</sub>) excluding external current

| PARAMETER |                    |          |                                                                                   | TEST CONDITIONS                                              |                                                | MIN | NOM        | MAX        | UNIT |

|-----------|--------------------|----------|-----------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------|-----|------------|------------|------|

|           |                    |          | $T_A = -40^{\circ}C + 8$<br>$f_{(ACLK)} = 32$                                     | $5^{\circ}$ C, $f(MCLK) = f(SMCLK) = 1$ MHz,<br>768 Hz       | V <sub>CC</sub> = 3 V<br>V <sub>CC</sub> = 5 V |     | 330<br>630 | 400<br>700 | μΑ   |

|           |                    | C11x     | $T_A = -40^{\circ}C + 8$                                                          | B5°C,<br>MCLK) = f(ACLK) = 4096 Hz                           | V <sub>CC</sub> = 3 V<br>V <sub>CC</sub> = 5 V |     | 3.4<br>7.8 | 4<br>10    | μΑ   |

| I(AM)     | Active mode        |          | $T_A = -40^{\circ}C + 8$                                                          | 35°C,                                                        | VCC = 3 V                                      |     | 400        | 500        |      |

|           |                    | P112     | f(ACLK) = 32                                                                      | ICLK) = 1 MHz,<br>768 Hz                                     | V <sub>CC</sub> = 5 V                          |     | 730        | 900        | μΑ   |

|           |                    |          | $T_A = -40^{\circ}C + 8$                                                          | 35°C,                                                        | VCC = 3 V                                      |     | 3.4        | 4          | μА   |

|           |                    |          | f(MCLK) = f(S                                                                     | MCLK) = f(ACLK) = 4096 Hz                                    | $V_{CC} = 5 V$                                 |     | 7.8        | 10         | μ    |

|           |                    | C11x     | $T_A = -40^{\circ}C + 8$                                                          | $85^{\circ}$ C, $f_{MCLK} = 0$ MHz,                          | VCC = 3 V                                      |     | 51         | 60         |      |

| ļ. i      | Low power mode,    | CIIX     | f(SMCLK) = 1 MHz, f(ACLK) = 32,768 Hz                                             |                                                              | $V_{CC} = 5 V$                                 |     | 120        | 150        | μА   |

| I(CPUOff) | (LPM0)             | P112     | $T_A = -40^{\circ}C + 85^{\circ}C$ , $f_{(MCLK)} = 0 \text{ MHz}$ ,               |                                                              | $V_{CC} = 3 V$                                 |     | 70         | 85         |      |

|           |                    |          | f(SMCLK) = 1                                                                      | MHz, $f_{(ACLK)} = 32,768 \text{ Hz}$                        | V <sub>CC</sub> = 5 V                          |     | 125        | 170        |      |

| la prac)  | Low power mode, (L | DM2)     | $T_A = -40^{\circ}\text{C} + 85^{\circ}\text{C},$<br>f(MCLK) = f(SMCLK) = 0  MHz, |                                                              | V <sub>CC</sub> = 3 V                          |     | 8          | 22         | μΑ   |

| I(LPM2)   | Low power mode, (L | -1 1012) | f(ACLK) = f(S)                                                                    | 768 Hz, SCG0 = 0, Rsel = 3                                   | V <sub>CC</sub> = 5 V                          |     | 16         | 35         | μΛ   |

|           |                    |          | $T_A = -40^{\circ}C$                                                              | f(MCLK) = f(SMCLK) = 0 MHz,                                  | V <sub>CC</sub> = 3 V                          |     | 2          | 2.6        |      |

|           |                    |          | T <sub>A</sub> = 25°C                                                             | f(ACLK) = 32,768 Hz,                                         |                                                |     | 1.5        | 2.2        | ]    |

|           | 1                  | D140)    | T <sub>A</sub> = 85°C                                                             | SCG0 = 1                                                     |                                                |     | 1.85       | 2.2        |      |

| I(LPM3)   | Low power mode, (L | -PIVI3)  | T <sub>A</sub> = −40°C                                                            |                                                              |                                                |     | 6.3        | 8          | μΑ   |

|           |                    |          | T <sub>A</sub> = 25°C                                                             | f(MCLK) = f(SMCLK) = 0 MHz,<br>f(ACLK) = 32,768 Hz, SCG0 = 1 | V <sub>C</sub> C = 5 V                         |     | 5.1        | 7          |      |

|           |                    |          | T <sub>A</sub> = 85°C                                                             | (ACLK) = 32,700 112, 3000 = 1                                |                                                |     | 5.1        | 7          |      |

|           |                    |          | $T_A = -40^{\circ}C$                                                              | f(MCLK) = f(SMCLK) = 0 MHz,                                  |                                                |     | 0.1        | 0.8        | μА   |

| I(LPM4)   | Low power mode, (L | -PM4)    | T <sub>A</sub> = 25°C                                                             | f(ACLK) = 0 Hz,                                              | V <sub>CC</sub> = 3 V/                         |     | 0.1        | 0.8        |      |

|           |                    |          | T <sub>A</sub> = 85°C                                                             | SCG0 = 1                                                     |                                                |     | 0.4        | 1          |      |

NOTE: All inputs are tied to  $V_{\mbox{SS}}$  or  $V_{\mbox{CC}}$ . Outputs do not source or sink any current.

# current consumption of active mode versus system frequency

$I_{AM} = I_{AM[1 \text{ MHz}]} \times f_{system} [MHz]$

## current consumption of active mode versus supply voltage

$$I_{AM} = I_{AM[3\ V]} + 175\ \mu A/V \times (V_{CC} - 3\ V)$$

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

## Schmitt-trigger inputs Port 1 to Port P2; P1.0 to P1.7, P2.0 to P2.5

|                     | PARAMETER                                                        | TEST CONDITIONS       | MIN | NOM MAX | UNIT |

|---------------------|------------------------------------------------------------------|-----------------------|-----|---------|------|

| V <sub>IT+</sub> Po | Desitive main a inner through and realterns                      | V <sub>CC</sub> = 3 V | 1.2 | 2.1     |      |

|                     | Positive-going input threshold voltage                           | $V_{CC} = 5 V$        | 2.3 | 3.4     | V    |

| V <sub>IT</sub> _   |                                                                  | V <sub>CC</sub> = 3 V | 0.7 | 1.5     | V    |

|                     | Negative-going input threshold voltage                           | $V_{CC} = 5 V$        | 1.4 | 2.3     |      |

| V <sub>hys</sub>    | Input voltage hysteresis, (V <sub>IT+</sub> – V <sub>IT-</sub> ) | V <sub>CC</sub> = 3 V | 0.3 | 1       | \/   |

|                     |                                                                  | V <sub>CC</sub> = 5 V | 0.6 | 1.4     | ľ    |

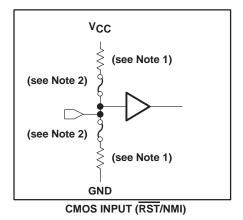

#### standard inputs RST/NMI, TCK, TMS, TDI

|                 | PARAMETER                | TEST CONDITIONS | MIN                 | NOM MAX              | UNIT                                  |

|-----------------|--------------------------|-----------------|---------------------|----------------------|---------------------------------------|

| V <sub>IL</sub> | Low-level input voltage  | Vcc = 3 V/5 V   | Vss                 | V <sub>SS</sub> +0.8 | 3                                     |

| VIH             | High-level input voltage | VCC = 2 V/2 V   | 0.7xV <sub>CC</sub> | Vcc                  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

#### inputs Px.x, TAx

|                                              | PARAMETER                                                                                  | TEST CONDITIONS                                             | VCC      | MIN | NOM | MAX | UNIT  |

|----------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------|-----|-----|-----|-------|

| t <sub>(int)</sub> External Interrupt timing |                                                                                            |                                                             | 3 V/ 5 V | 1.5 |     |     | cycle |

|                                              | Port P1, P2: P1.x to P2.x,<br>External trigger signal for the interrupt flag, (see Note 1) | 3 V                                                         | 540      |     |     |     |       |

|                                              |                                                                                            | External trigger signal for the interrupt mag, (see Note 1) | 5 V      | 270 |     |     | ns    |

|                                              |                                                                                            |                                                             | 3 V/5 V  | 1.5 |     |     | cycle |

| t(cap) Timer_A, ca                           | Timer_A, capture timing                                                                    |                                                             | 3 V      | 540 |     |     |       |

|                                              |                                                                                            |                                                             | 5 V      | 270 |     |     | ns    |

- NOTES: 1. The external signal sets the interrupt flag every time the minimum t<sub>int</sub> cycle and time parameters are met. It may be set even with trigger signals shorter than t<sub>int</sub>. Both the cycle and timing specifications must be met to ensure the flag is set.

- The external capture signal triggers the capture event every time when the minimum t<sub>cap</sub> cycles and time parameters are met. A capture may be triggered with capture signals even shorter than t<sub>cap</sub>. Both the cycle and timing specifications must be met to ensure a correct capture of the 16-bit timer value and to ensure the flag is set.

#### internal signals TAx, SMCLK at Timer\_A

|                       | PARAMETER               | TEST CONDITIONS                                         | VCC     | MIN | NOM MAX | UNIT |

|-----------------------|-------------------------|---------------------------------------------------------|---------|-----|---------|------|

| f(IN) Input frequency |                         |                                                         | 3 V     | dc  | 10      |      |

|                       |                         | Internal TA0, TA1, TA2, t <sub>H</sub> = t <sub>L</sub> | 5 V     | dc  | 15      | MHz  |

| f(TAint)              | Timer_A clock frequency | Internally, SMCLK signal applied                        | 3 V/5 V | dc  | fSvstem |      |

#### leakage current (see Note 1)

|            | ,                                    |                                             |                            |     |     |     |      |

|------------|--------------------------------------|---------------------------------------------|----------------------------|-----|-----|-----|------|

|            | PARAMETER                            | TEST COND                                   | ITIONS                     | MIN | NOM | MAX | UNIT |

|            | High the second second second second | Port P1: P1.x, $0 \le x \le 7$ (see Note 2) | V <sub>CC</sub> = 3 V/5 V, |     |     | ±50 |      |

| Ilkg(Px.x) |                                      | Port P2: P2.x, $0 \le x \le 5$ (see Note 2) | V <sub>CC</sub> = 3 V/5 V, |     |     | ±50 | nA   |

NOTES: 1. The leakage current is measured with  $V_{SS}$  or  $V_{CC}$  applied to the corresponding pin(s), unless otherwise noted.

2. The leakage of the digital port pins is measured individually. The port pin must be selected for input and there must be no optional pullup or pulldown resistor.

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

#### outputs P2x, TAx

|                     | PARAMETER                   | TEST CONDITIONS                    |                                       | VCC      | MIN | NOM | MAX     | UNIT   |

|---------------------|-----------------------------|------------------------------------|---------------------------------------|----------|-----|-----|---------|--------|

| f(P20)              | Customat from successive    | P2.0/ACLK,                         | C <sub>L</sub> = 20 pF                | 3 V/5 V  |     |     | 1.1     | N41.1- |

| f(TAx)              | Output frequency            | TA0, TA1, TA2,                     | C <sub>L</sub> = 20 pF                | 3 V/5 V  | dc  |     | fSystem | MHz    |

|                     |                             | P2.0/ACLK, C <sub>L</sub> = 20 pF  | $f_{P20} = 1.1 \text{ MHz}$           |          | 40% |     | 60%     |        |

| t(Xdc)              |                             |                                    | f <sub>P20</sub> = f <sub>XTCLK</sub> | 3 V/5 V  | 35% |     | 65%     |        |

|                     | Duty cycle of O/P frequency |                                    | fP20 = fXTCLK/n                       |          |     | 50% |         |        |

| <sup>t</sup> (TAdc) |                             | TA0, TA1, TA2,<br>Duty cycle = 50% | C <sub>L</sub> = 20 pF,               | 3 V/ 5 V |     | 0   | ±50     | ns     |

#### outputs Port 1 to P2; P1.0 to P1.7, P2.0 to P2.5

|                                           | PARAMETER TEST CONDITIONS |                               |                             | MIN        | NOM                  | MAX | UNIT                 |    |

|-------------------------------------------|---------------------------|-------------------------------|-----------------------------|------------|----------------------|-----|----------------------|----|

| V                                         | High lavel autout valtage | $I_{(OH)} = -1.5 \text{ mA},$ | $V_{CC} = 3 \text{ V/5 V},$ | See Note 1 | V <sub>CC</sub> -0.4 |     | VCC                  | V  |

| V <sub>OH</sub> High-level output voltage | High-level output voltage | $I_{(OH)} = -4.5 \text{ mA},$ | $V_{CC} = 3 \text{ V/5 V},$ | See Note 2 | VCC-0.6              |     | VCC                  | V  |

| Vai                                       | Low lovel output voltage  | $I_{(OL)} = 1.5 \text{ mA},$  | $V_{CC} = 3 \text{ V/5 V},$ | See Note 1 | VSS                  |     | V <sub>SS</sub> +0.4 | \/ |

| V <sub>OL</sub> Low-level output voltage  | Low-level output voltage  | $I_{(OL)} = 4.5 \text{ mA},$  | $V_{CC} = 3 \text{ V/5 V},$ | See Note 2 | VSS                  |     | VSS+0.6              | V  |

NOTES: 1. The maximum total current, I<sub>OH</sub> and I<sub>OL</sub>, or all outputs combined, should not exceed ±12 mA to hold the maximum voltage drop specified.

2. The maximum total current, I<sub>OH</sub> and I<sub>OL</sub>, or all outputs combined, should not exceed ±36 mA to hold the maximum voltage drop specified.

#### optional resistors, individually programmable with ROM code (see Note 1)

|                      | PARAMETER                                                          | TEST CONDITIONS           | MIN | NOM | MAX | UNIT |

|----------------------|--------------------------------------------------------------------|---------------------------|-----|-----|-----|------|

| R <sub>(opt1)</sub>  |                                                                    | V <sub>CC</sub> = 3 V/5 V | 2.1 | 4.1 | 6.2 | kΩ   |

| R <sub>(opt2)</sub>  |                                                                    | V <sub>CC</sub> = 3 V/5 V | 3.1 | 6.2 | 9.3 | kΩ   |

| R <sub>(opt3)</sub>  |                                                                    | V <sub>CC</sub> = 3 V/5 V | 6   | 12  | 18  | kΩ   |

| R <sub>(opt4)</sub>  |                                                                    | V <sub>CC</sub> = 3 V/5 V | 10  | 19  | 29  | kΩ   |

| R <sub>(opt5)</sub>  | Resistors, individually programmable with ROM code, all port pins, | V <sub>CC</sub> = 3 V/5 V | 19  | 37  | 56  | kΩ   |

| R <sub>(opt6)</sub>  | values applicable for pulldown and pullup                          | V <sub>CC</sub> = 3 V/5 V | 38  | 75  | 113 | kΩ   |

| R <sub>(opt7)</sub>  |                                                                    | V <sub>CC</sub> = 3 V/5 V | 56  | 112 | 168 | kΩ   |

| R <sub>(opt8)</sub>  |                                                                    | V <sub>CC</sub> = 3 V/5 V | 94  | 187 | 281 | kΩ   |

| R <sub>(opt9)</sub>  |                                                                    | V <sub>CC</sub> = 3 V/5 V | 131 | 261 | 392 | kΩ   |

| R <sub>(opt10)</sub> |                                                                    | V <sub>CC</sub> = 3 V/5 V | 167 | 337 | 506 | kΩ   |

NOTE 1: Optional resistors Roptx for pulldown or pullup are not programmed in standard OTP or EPROM devices MSP430P112 or PMS430E112.

electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued)

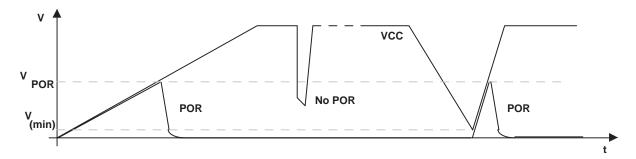

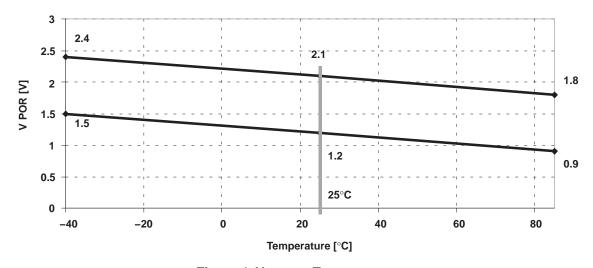

## PUC/POR

| PARAMETER           |         | TEST CONDITI                 | TEST CONDITIONS           |     | NOM | MAX | UNIT |

|---------------------|---------|------------------------------|---------------------------|-----|-----|-----|------|

| t(POR_Dela          | ay)     |                              |                           |     | 150 | 250 | μs   |

|                     |         | $T_A = -40^{\circ}C$         |                           | 1.5 |     | 2.4 | V    |

| V <sub>POR</sub> PO | POR     | T <sub>A</sub> = 25°C        | V 2 V/F V                 | 1.2 |     | 2.1 | V    |

|                     |         | T <sub>A</sub> = 85°C        | V <sub>CC</sub> = 3 V/5 V | 0.9 |     | 1.8 | V    |

| V <sub>(min)</sub>  |         |                              |                           | 0   |     | 0.4 | V    |

| t(reset)            | PUC/POR | Reset is accepted internally |                           | 2   |     |     | μs   |

Figure 3. Power-On Reset (POR) vs Supply Voltage

Figure 4. V<sub>POR</sub> vs Temperature

electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued)

## wake-up from lower power modes (LPMx)

|                     | PARAMETER  | TEST CONDITIONS                        |                           | MIN | NOM | MAX | UNIT |

|---------------------|------------|----------------------------------------|---------------------------|-----|-----|-----|------|

| t(LPM0)/<br>t(LPM2) |            |                                        | V <sub>CC</sub> = 3 V/5 V |     | 100 |     | ns   |

| t(LPM3)             | Delay time | R <sub>Sel</sub> = 4, DCO = 3, MOD = 0 | V <sub>CC</sub> = 3 V/5 V |     | 2.6 | 6   | μs   |

| t(LPM4)             |            | R <sub>Sel</sub> = 4, DCO = 3, MOD = 0 | V <sub>CC</sub> = 3 V/5 V |     | 2.8 | 6   | μs   |

#### **RAM**

|         | PARAMETER               | MIN | NOM | MAX | UNIT |

|---------|-------------------------|-----|-----|-----|------|

| V(RAMh) | CPU halted (see Note 1) | 1.8 |     |     | V    |

NOTE 1: This parameter defines the minimum supply voltage V<sub>CC</sub> when the data in the program memory RAM remains unchanged. No program execution should happen during this supply voltage condition.

#### DCO (MSP430P112)

| PARAMETER           | TEST CONDITIONS                                                                              |                              | MIN            | NOM            | MAX            | UNIT    |

|---------------------|----------------------------------------------------------------------------------------------|------------------------------|----------------|----------------|----------------|---------|

|                     | D 0 000 0 MOD 0 000D 0 T 0500                                                                | V <sub>CC</sub> = 3 V        |                | 0.12           |                | N41.1-  |

| f(DCO03)            | $R_{\text{Sel}} = 0$ , DCO = 3, MOD = 0, DCOR = 0, $T_{\text{A}} = 25^{\circ}\text{C}$       | $V_{CC} = 5 V$               |                | 0.13           |                | MHz     |

| £                   | D . 4 DCO 2 MOD 0 DCOD 0 T. 25°C                                                             | V <sub>CC</sub> = 3 V        |                | 0.19           |                | MHz     |

| f(DCO13)            | $R_{Sel} = 1$ , DCO = 3, MOD = 0, DCOR = 0, $T_A = 25$ °C                                    | $V_{CC} = 5 V$               |                | 0.21           |                | IVI□Z   |

| f(DCCCs)            | $R_{\text{Sel}} = 2$ , DCO = 3, MOD = 0, DCOR = 0, $T_{\text{A}} = 25^{\circ}\text{C}$       | VCC = 3 V                    |                | 0.31           |                | MHz     |

| f(DCO23)            | Ngg  = 2, DOO = 3, MOD = 0, DOON = 0, TA = 23 0                                              | $V_{CC} = 5 V$               |                | 0.34           |                | IVII IZ |

| f(DOOOS)            | $R_{SOI} = 3$ , DCO = 3, MOD = 0, DCOR = 0, $T_{\Delta} = 25^{\circ}$ C                      | VCC = 3 V                    |                | 0.5            |                | MHz     |

| f(DCO33)            | NSe  = 3, DCO = 3, MOD = 0, DCON = 0, TA = 23 C                                              | $V_{CC} = 5 V$               |                | 0.55           |                | IVII IZ |

| f(D0040)            | $R_{SO} = 4$ , DCO = 3, MOD = 0, DCOR = 0, $T_{\Delta} = 25^{\circ}$ C                       | $V_{CC} = 3 V$               | 0.5            | 0.8            | 1.1            | MHz     |

| f(DCO43)            | NSe  = 4, DCO = 3, MOD = 0, DCON = 0, TA = 23 C                                              | $V_{CC} = 5 V$               | 0.6            | 0.9            | 1.2            | IVII IZ |

| f(DOOSO)            | R 5 DCO - 3 MOD - 0 DCOR - 0 Ta - 25°C                                                       | V <sub>CC</sub> = 3 V        | 0.9            | 1.2            | 1.55           | MHz     |

| f(DCO53)            | $R_{Sel} = 5$ , DCO = 3, MOD = 0, DCOR = 0, $T_A = 25^{\circ}$                               | $V_{CC} = 5 V$               | 1.1            | 1.4            | 1.7            |         |

| f/DOGGS             | R <sub>Sel</sub> = 6, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                      | V <sub>CC</sub> = 3 V        | 1.7            | 2              | 2.3            | MHz     |

| f(DCO63)            | NSe  = 0, DCO = 3, MOD = 0, DCON = 0, TA = 23 C                                              | $V_{CC} = 5 V$               | 2.1            | 2.4            | 2.7            | IVITIZ  |

| f/DOOTS)            | R <sub>Sel</sub> = 7, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                      | V <sub>CC</sub> = 3 V        | 2.8            | 3.1            | 3.5            | MHz     |

| f(DCO73)            | NSe  = 1, DCO = 3, MOD = 0, DCON = 0, 1A = 23 C                                              | $V_{CC} = 5 V$               | 3.8            | 4.2            | 4.5            | IVII IZ |

| f(DCO47)            | R <sub>Sel</sub> = 4, DCO = 7, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                      | V <sub>CC</sub> = 3 V/5 V    | FDCO40<br>x1.8 | FDCO40<br>x2.2 | FDCO40<br>x2.6 | MHz     |

| S <sub>(Rsel)</sub> | S <sub>R</sub> = f <sub>Rsel+1</sub> /f <sub>Rsel</sub>                                      | V <sub>CC</sub> = 3 V/5 V    | 1.4            | 1.65           | 1.9            |         |

| S <sub>(DCO)</sub>  | S <sub>DCO</sub> = f <sub>DCO+1</sub> /f <sub>DCO</sub>                                      | V <sub>CC</sub> = 3 V/5 V    | 1.07           | 1.12           | 1.16           | ratio   |

|                     | Temperature drift, R <sub>sel</sub> = 4, DCO = 3,                                            | VCC = 3 V                    | -0.31          | -0.36          | -0.40          | 0.100   |

|                     | MOD = 0  (see Note 1)                                                                        | V <sub>CC</sub> = 5 V        | -0.33          | -0.38          | -0.43          | %/°C    |

| DV                  | Drift with V <sub>CC</sub> variation, R <sub>sel</sub> = 4, DCO = 3,<br>MOD = 0 (see Note 1) | V <sub>CC</sub> = 3 V to 5 V | 0              | 5              | 10             | %/V     |

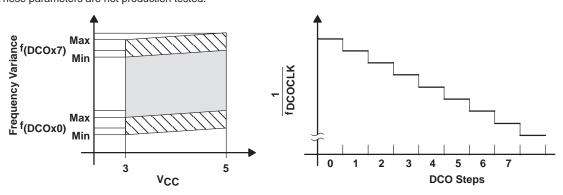

NOTE 1: These parameters are not production tested.

electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued)

#### DCO (MSP430C111, C112)

| PARAMETER           | TEST CONDITIONS                                                                              |                              | MIN                        | NOM                        | MAX                     | UNIT    |  |

|---------------------|----------------------------------------------------------------------------------------------|------------------------------|----------------------------|----------------------------|-------------------------|---------|--|

|                     | D 0 DCC 2 MOD 0 DCCD 0 T 05°C                                                                | V <sub>CC</sub> = 3 V        | 0.04                       | 0.07                       | 0.10                    | NAL I-  |  |

| f(DCO03)            | $R_{sel} = 0$ , DCO = 3, MOD = 0, DCOR = 0, $T_A = 25$ °C                                    | V <sub>CC</sub> = 5 V        | 0.04                       | 0.07                       | 0.10                    | MHz     |  |

| <b>.</b>            | D . 4 DCC 2 MOD 0 DCCD 0 T- 0500                                                             | VCC = 3 V                    | 0.08                       | 0.13                       | 0.18                    | N 41 1- |  |

| f(DCO13)            | $R_{sel} = 1$ , DCO = 3, MOD = 0, DCOR = 0, $T_A = 25$ °C                                    | V <sub>CC</sub> = 5 V        | 0.08                       | 0.13                       | 0.18                    | MHz     |  |

| f(DOOSS)            | $R_{Sel} = 2$ , DCO = 3, MOD = 0, DCOR = 0, $T_A = 25^{\circ}C$                              | V <sub>CC</sub> = 3 V        | 0.15                       | 0.22                       | 0.30                    | MHz     |  |

| f(DCO23)            | NSE  = 2, DCO = 3, WOD = 0, DCON = 0, TA = 23 C                                              | V <sub>CC</sub> = 5 V        | 0.15                       | 0.22                       | 0.30                    | IVII IZ |  |

| f(DODGS)            | $R_{Sel} = 3$ , DCO = 3, MOD = 0, DCOR = 0, $T_A = 25^{\circ}C$                              | VCC = 3 V                    | 0.26                       | 0.36                       | 0.47                    | MHz     |  |

| f(DCO33)            | R <sub>Sel</sub> = 3, DCO = 3, MOD = 0, DCOR = 0, 1 <sub>A</sub> = 23 C                      | V <sub>CC</sub> = 5 V        | 0.26                       | 0.36                       | 0.47                    | IVII IZ |  |

| <b>6</b>            | D . 4 DCO 2 MOD 0 DCOD 0 T. 25°C                                                             | VCC = 3 V                    | 0.4                        | 0.6                        | 0.8                     | MHz     |  |

| f(DCO43)            | $R_{sel} = 4$ , DCO = 3, MOD = 0, DCOR = 0, $T_A = 25$ °C                                    | V <sub>CC</sub> = 5 V        | 0.4                        | 0.6                        | 0.8                     | IVITZ   |  |

| <i>t</i> = 2 2 >    | D . F DCC 2 MOD 0 DCCD 0 T. 25°C                                                             | VCC = 3 V                    | 0.8                        | 1.1                        | 1.4                     | MHz     |  |

| f(DCO53)            | $R_{Sel} = 5$ , DCO = 3, MOD = 0, DCOR = 0, $T_A = 25$ °C                                    | V <sub>CC</sub> = 5 V        | 0.8                        | 1.1                        | 1.4                     | IVITZ   |  |

| 4                   | R <sub>Sel</sub> = 6, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                      | V <sub>CC</sub> = 3 V        | 1.3                        | 1.7                        | 2.1                     | MHz     |  |

| f(DCO63)            | $R_{Sel} = 0$ , $DCO = 3$ , $MOD = 0$ , $DCOR = 0$ , $T_A = 25^{\circ}C$                     | V <sub>CC</sub> = 5 V        | 1.5                        | 1.9                        | 2.3                     | IVITZ   |  |

| f /= ·              | $R_{Sel} = 7$ , DCO = 3, MOD = 0, DCOR = 0, $T_A = 25$ °C                                    | VCC = 3 V                    | 2.4                        | 2.9                        | 3.4                     | MHz     |  |

| f(DCO73)            | $R_{\text{Sel}} = 7$ , $DCO = 3$ , $MOD = 0$ , $DCOR = 0$ , $T_A = 23$ C                     | V <sub>CC</sub> = 5 V        | 3.1                        | 3.8                        | 4.5                     | IVITIZ  |  |

| f(DCO47)            | R <sub>Sel</sub> = 4, DCO = 7, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                      | V <sub>CC</sub> = 3 V/5 V    | F <sub>DCO40</sub><br>x1.8 | F <sub>DCO40</sub><br>x2.2 | F <sub>DCO40</sub> x2.6 | MHz     |  |

| S <sub>(Rsel)</sub> | S <sub>R</sub> = f <sub>Rsel+1</sub> /f <sub>Rsel</sub>                                      | V <sub>CC</sub> = 3 V/5 V    | 1.4                        | 1.65                       | 1.9                     |         |  |

| S <sub>(DCO)</sub>  | S <sub>DCO</sub> = f <sub>DCO+1</sub> /f <sub>DCO</sub>                                      | V <sub>CC</sub> = 3 V/5 V    | 1.07                       | 1.12                       | 1.16                    | ratio   |  |

|                     | Temperature drift, R <sub>sel</sub> = 4, DCO = 3,                                            | V <sub>CC</sub> = 3 V        | -0.31                      | -0.36                      | -0.40                   | 0, 100  |  |

| D <sub>t</sub>      | MOD = 0 (see Note 1)                                                                         | V <sub>CC</sub> = 5 V        | -0.33                      | -0.38                      | -0.43                   | %/°C    |  |

| D <sub>V</sub>      | Drift with V <sub>CC</sub> variation, R <sub>sel</sub> = 4, DCO = 3,<br>MOD = 0 (see Note 1) | V <sub>CC</sub> = 3 V to 5 V | 0                          | 5                          | 10                      | %/V     |  |

NOTE 1: These parameters are not production tested.

Figure 5. DCO Characteristics

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued)

#### main DCO characteristics

- Individual devices have a minimum and maximum operation frequency. The specified parameters for f<sub>(DCOx0)</sub> to f<sub>(DCOx7)</sub> are valid for all devices.

- All ranges selected by Rsel(n) overlap with Rsel(n+1): Rsel0 overlaps Rsel1, ... Rsel6 overlaps Rsel7.

- DCO control bits DCO0, DCO1, and DCO2 have a step size as defined by parameter S<sub>DCO</sub>.

- Modulation control bits MOD0 to MOD4 select how often f<sub>(DCO+1)</sub> is used within the period of 32 DCOCLK cycles. The frequency f<sub>(DCO)</sub> is used for the remaining cycles. The frequency is an average equal to:

$$f_{average} = \frac{32 \times f_{(DCO)} \times f_{(DCO+1)}}{MOD \times f_{(DCO)} + (32 - MOD) \times f_{(DCO+1)}}$$

#### crystal oscillator, XIN, XOUT

|                   | PARAMETER             | TEST CONDITIONS                        | MIN                 | NOM MAX             | UNIT |

|-------------------|-----------------------|----------------------------------------|---------------------|---------------------|------|

| C <sub>XIN</sub>  | Capacitance at input  | V <sub>CC</sub> = 3 V/5 V              |                     | 12                  | pF   |

| C <sub>XOUT</sub> | Capacitance at output | V <sub>CC</sub> = 3 V/5 V              |                     | 12                  | pF   |

| $V_{IL}$          | Input levels at XIN   | V = = = 2 \//E \/ (200 Noto 2)         | V <sub>SS</sub>     | 0.2×V <sub>CC</sub> | V    |

| VIH               | Input levels at AIN   | V <sub>CC</sub> = 3 V/5 V (see Note 2) | 0.8×V <sub>CC</sub> | Vcc                 | 7 °  |

NOTES: 1. The oscillator needs capacitors at both terminals, with values specified by the crystal manufacturer.

2. Applies only when using an external logic-level clock source. Not applicable when using a crystal or resonator.

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued)

#### **EPROM Memory, P- and E- versions only (see Note 1)**

|                   | PARAMETER                                                                                    | TEST<br>CONDITIONS | VCC | MIN  | NOM  | MAX | UNIT   |

|-------------------|----------------------------------------------------------------------------------------------|--------------------|-----|------|------|-----|--------|

| V <sub>(PP)</sub> | Programming voltage, applied to TEST/VPP                                                     |                    |     | 12   | 12.5 | 13  | V      |

| I <sub>(PP)</sub> | Current from programming voltage source                                                      |                    |     |      |      | 70  | mA     |

| t(pps)            | Programming time, single pulse                                                               |                    |     | 5    |      |     | ms     |

| t(ppf)            | Programming time, fast algorithm                                                             |                    |     |      | 100  |     | μs     |

| P <sub>(n)</sub>  | Number of pulses for successful programming                                                  |                    |     | 4    |      | 100 | Pulse  |

| t(erase)          | Erase time: Wave length 2537 Å at 15 Ws/cm <sup>2</sup> (UV lamp of 12 mW/ cm <sup>2</sup> ) |                    |     | 30   |      |     | min    |

| -(GIA36)          | Write/erase cycles                                                                           |                    |     | 1000 |      |     | cycles |

|                   | Data retention Tj < 55°C                                                                     |                    |     | 10   |      | _   | Year   |

NOTES: 1. Refer to the Recommended Operating Conditions for the correct V<sub>CC</sub> during programming.

#### JTAG Interface

|     | PARAMETER           | TEST<br>CONDITIONS | vcc | MIN | NOM N | АХ | UNIT  |

|-----|---------------------|--------------------|-----|-----|-------|----|-------|

|     | TOV input for many  | ana Nista 4        | 3 V | DC  |       | 5  | MI I- |

| TCK | TCK input frequency | see Note 1         | 5 V | DC  |       | 10 | MHz   |

NOTES: 1. f<sub>TCK</sub> may be restricted to meet the timing requirements of the module selected.

#### JTAG Fuse (see Note 1)

|                 | PARAMETER                                     | TEST<br>CONDITIONS | vcc      | MIN | NOM | MAX | UNIT |

|-----------------|-----------------------------------------------|--------------------|----------|-----|-----|-----|------|

| .,              | Fuse blow voltage, C versions (see Note 2)    |                    | 3 V/ 5 V | 5.5 |     | 6   | .,   |

| $V_{FB}$        | Fuse blow voltage, E/P versions (see Note 2)  |                    | 3 V/ 5 V | 11  |     | 13  | V    |

| I <sub>FB</sub> | Supply current into TEST/VPP during fuse blow |                    |          |     |     | 100 | mA   |

| t <sub>FB</sub> | Time to blow fuse                             |                    |          |     |     | 1   | ms   |

NOTES: 1. Once the fuse is blown, no further access to the MSP430 JTAG/Test and emulation features is possible. The JTAG block is switched to bypass mode.

2. The fuse blow voltage is applied to the TEST/VPP pin.

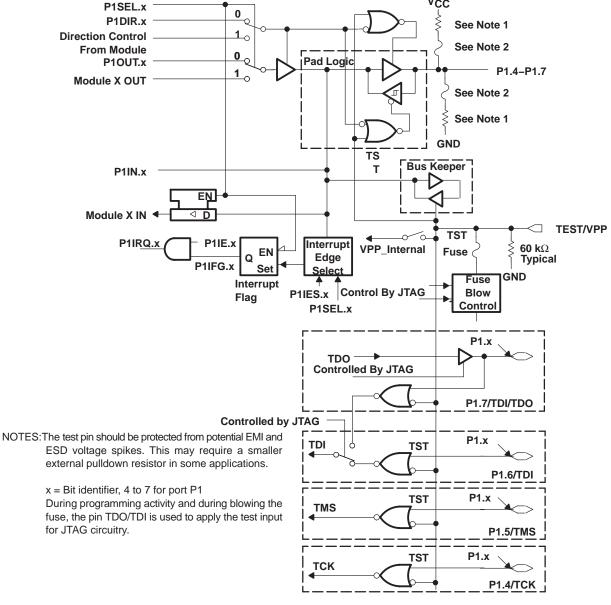

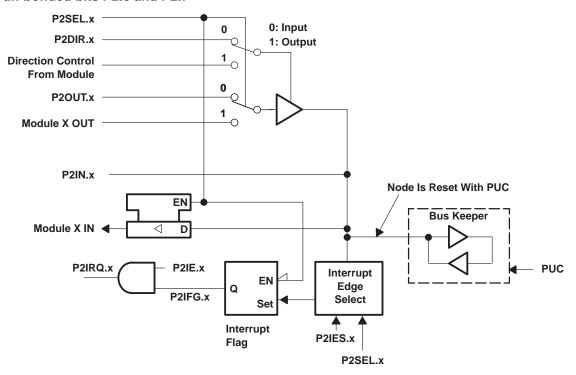

## input/output schematic

#### Port P1, P1.0 to P1.3, input/output with Schmitt-trigger

NOTE: x = Bit Identifier, 0 to 3 For Port P1

| PnSel.x | PnDIR.x | Dir. Control from module | PnOUT.x | Module X<br>OUT          | PnIN.x | Module X<br>IN     | PnIE.x | PnIFG.x | PnIES.x |

|---------|---------|--------------------------|---------|--------------------------|--------|--------------------|--------|---------|---------|

| P1Sel.0 | P1DIR.0 | P1DIR.0                  | P1OUT.0 | V <sub>SS</sub>          | P1IN.0 | TACLK <sup>†</sup> | P1IE.0 | P1IFG.0 | P1IES.0 |

| P1Sel.1 | P1DIR.1 | P1DIR.1                  | P1OUT.1 | Out0 signal†             | P1IN.1 | CCI0A†             | P1IE.1 | P1IFG.1 | P1IES.1 |

| P1Sel.2 | P1DIR.2 | P1DIR.2                  | P1OUT.2 | Out1 signal <sup>†</sup> | P1IN.2 | CCI1A <sup>†</sup> | P1IE.2 | P1IFG.2 | P1IES.2 |

| P1Sel.3 | P1DIR.3 | P1DIR.3                  | P1OUT.3 | Out2 signal <sup>†</sup> | P1IN.3 | CCI2A <sup>†</sup> | P1IE.3 | P1IFG.3 | P1IES.3 |

† Signal from or to Timer\_A

NOTES: 1. Optional selection of pullup or pulldown resistors with ROM (masked) versions.

2. Fuses for optional pullup and pulldown resistors can only be programmed at the factory.

#### input/output schematic (continued)

#### Port P1, P1.4 to P1.7, input/output with Schmitt-trigger and in-system access features

| PnSel.x | PnDIR.x | Dir. Control from module | PnOUT.x | Module X<br>OUT          | PnIN.x | Module X<br>IN | PnIE.x | PnIFG.x | PnIES.x |

|---------|---------|--------------------------|---------|--------------------------|--------|----------------|--------|---------|---------|

| P1Sel.4 | P1DIR.4 | P1DIR.4                  | P1OUT.4 | SMCLK                    | P1IN.4 | unused         | P1IE.4 | P1IFG.4 | P1IES.4 |

| P1Sel.5 | P1DIR.5 | P1DIR.5                  | P1OUT.5 | Out0 signal†             | P1IN.5 | unused         | P1IE.5 | P1IFG.5 | P1IES.5 |

| P1Sel.6 | P1DIR.6 | P1DIR.6                  | P1OUT.6 | Out1 signal <sup>†</sup> | P1IN.6 | unused         | P1IE.6 | P1IFG.6 | P1IES.6 |

| P1Sel.7 | P1DIR.7 | P1DIR.7                  | P1OUT.7 | Out2 signal†             | P1IN.7 | unused         | P1IE.7 | P1IFG.7 | P1IES.7 |

<sup>†</sup> Signal from or to Timer\_A

<sup>2.</sup> Fuses for optional pullup and pulldown resistors can only be programmed at the factory.

NOTES: 1. Optional selection of pullup or pulldown resistors with ROM (masked) versions.

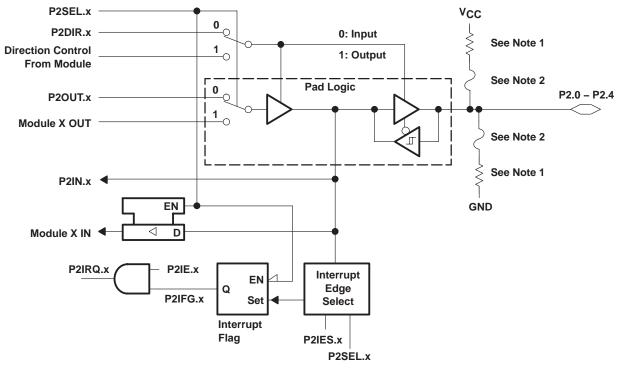

## input/output schematic (continued)

#### Port P2, P2.0 to P2.4, input/output with Schmitt-trigger

NOTE: x = Bit Identifier, 0 to 4 For Port P2

| PnSel.x | PnDIR.x | Dir. Control from module | PnOUT.x | Module X<br>OUT | PnIN.x | Module X<br>IN     | PnIE.x | PnIFG.x | PnIES.x |

|---------|---------|--------------------------|---------|-----------------|--------|--------------------|--------|---------|---------|

| P2Sel.0 | P2DIR.0 | P2DIR.0                  | P2OUT.0 | ACLK            | P2IN.0 | unused             | P2IE.0 | P2IFG.0 | P1IES.0 |

| P2Sel.1 | P2DIR.1 | P2DIR.1                  | P2OUT.1 | VSS             | P2IN.1 | INCLK†             | P2IE.1 | P2IFG.1 | P1IES.1 |

| P2Sel.2 | P2DIR.2 | P2DIR.2                  | P2OUT.2 | Out0 signal†    | P2IN.2 | CCI0B†             | P2IE.2 | P2IFG.2 | P1IES.2 |

| P2Sel.3 | P2DIR.3 | P2DIR.3                  | P2OUT.3 | Out1 signal†    | P2IN.3 | CCI1B <sup>†</sup> | P2IE.3 | P2IFG.3 | P1IES.3 |

| P2Sel.4 | P2DIR.4 | P2DIR.4                  | P2OUT.4 | Out2 signal†    | P2IN.4 | unused             | P2IE.4 | P2IFG.4 | P1IES.4 |

<sup>†</sup> Signal from or to Timer\_A

NOTES: 1. Optional selection of pullup or pulldown resistors with ROM (masked) versions.

2. Fuses for optional pullup and pulldown resistors can only be programmed at the factory.

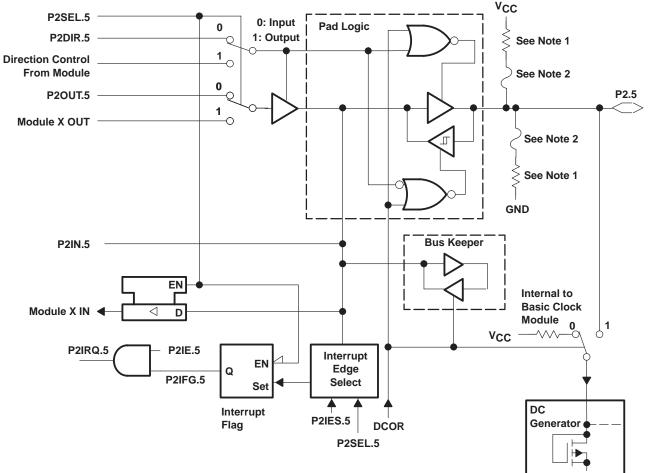

## input/output schematic (continued)

# Port P2, P2.5, input/output with Schmitt-trigger and R<sub>OSC</sub> function for the Basic Clock module

NOTE: DCOR: Control bit from basic clock module if it is set, P2.5 is disconnected from P2.5 pad

| PnSel.x | PnDIR.x | Director<br>Control from<br>module | PnOUT.x | Module X<br>OUT | PnIN.x | Module X<br>IN | PnIE.x | PnIFG.x | PnIES.x |

|---------|---------|------------------------------------|---------|-----------------|--------|----------------|--------|---------|---------|

| P2Sel.5 | P2DIR.5 | P2DIR.5                            | P2OUT.5 | $V_{SS}$        | P2IN.5 | unused         | P2IE.5 | P2IFG.5 | P2IES.5 |

NOTES: 1. Optional selection of pullup or pulldown resistors with ROM (masked) versions.

2. Fuses for optional pullup and pulldown resistors can only be programmed at the factory.

## input/output schematic (continued)

#### Port P2, un-bonded bits P2.6 and P2.7

NOTE: x = Bit identifier, 6 to 7 for Port P2 without external pins

| P2Sel.x | P2DIR.x | Dir. Control from module | P2OUT.x | Module X<br>OUT | P2IN.x | Module X<br>IN | P2IE.x | P2IFG.x | P2IES.x |

|---------|---------|--------------------------|---------|-----------------|--------|----------------|--------|---------|---------|

| P2Sel.6 | P2DIR.6 | P2DIR.6                  | P2OUT.6 | V <sub>SS</sub> | P2IN.6 | unused         | P2IE.6 | P2IFG.6 | P2IES.6 |

| P2Sel.7 | P2DIR.7 | P2DIR.7                  | P2OUT.7 | VSS             | P2IN.7 | unused         | P2IE.7 | P2IFG.7 | P2IES.7 |

NOTE: A good use of the unbonded bits 6 and 7 of port P2 is to use the interrupt flags. The interrupt flags can not be influenced from any signal other than from software. They work then as soft interrupt.

#### APPLICATION INFORMATION

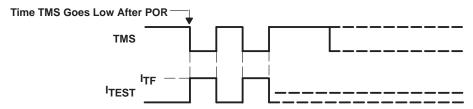

#### JTAG fuse check mode

MSP430 devices that have the fuse on the TEST terminal have a fuse check mode that tests the continuity of the fuse the first time the JTAG port is accessed after a power-on reset (POR). When activated, a fuse check current, I<sub>TF</sub>, of 1 mA at 3 V, 2.5 mA at 5 V can flow from the TEST pin to ground if the fuse is not burned. Care must be taken to avoid accidentally activating the fuse check mode and increasing overall system power consumption.

When the TEST pin is taken back low after a test or programming session, the fuse check mode and sense currents are terminated.

Activation of the fuse check mode occurs with the first negative edge on the TMS pin after power up or if TMS is being held low during power up. The second positive edge on the TMS pin deactivates the fuse check mode. After deactivation, the fuse check mode remains inactive until another POR occurs. After each POR the fuse check mode has the potential to be activated.

The fuse check current will only flow when the fuse check mode is active and the TMS pin is in a low state (see Figure 6). Therefore, the additional current flow can be prevented by holding the TMS pin high (default condition).

Figure 6. Fuse Check Mode Current, MSP430x11x

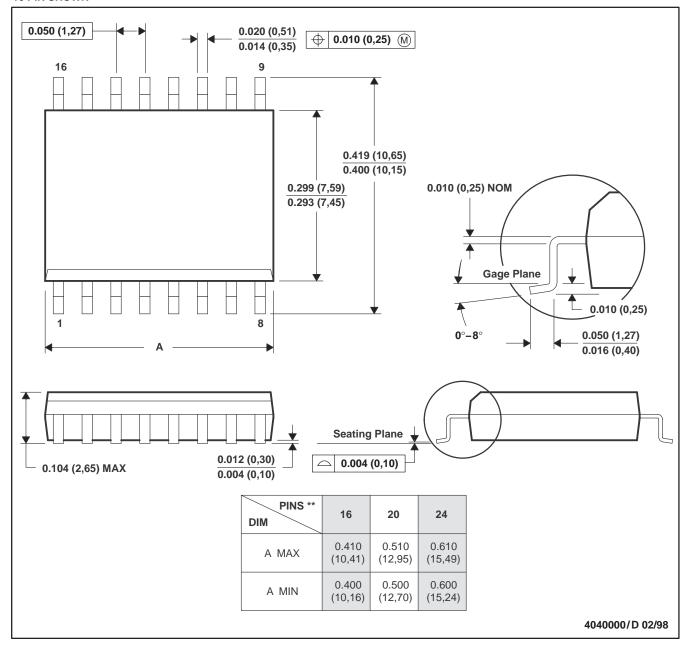

#### **MECHANICAL DATA**

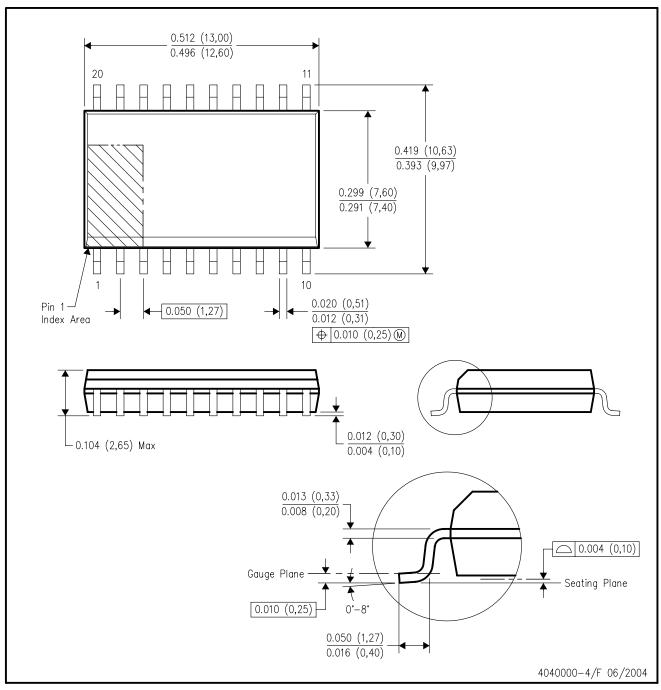

#### DW (R-PDSO-G\*\*)

#### **16 PIN SHOWN**

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013

SLAS196D- DECEMBER 1998 - REVISED SEPTEMBER 2004

#### MSP430C111IDW, MSP430C112IDW, MSP430P112IDW pin out

#### PMS430E112 pin out

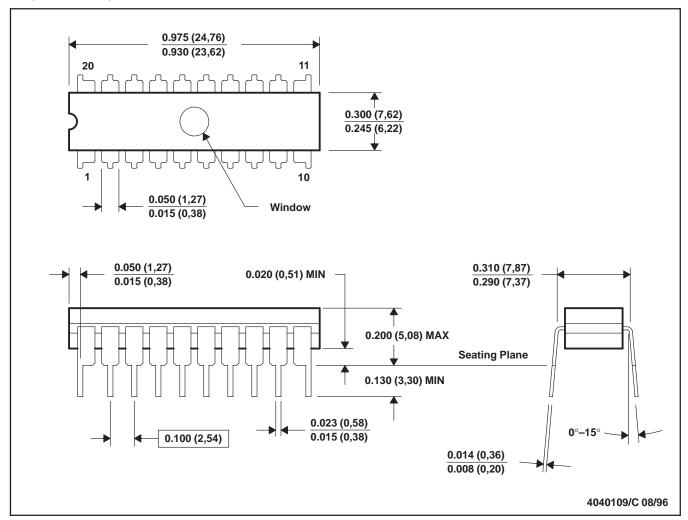

#### JL (R-GDIP-T20)

#### **CERAMIC DUAL-IN-LINE PACKAGE**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only

- E. Falls within MIL-STD-1835 GDIP1-T20

# DW (R-PDSO-G20)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AC.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.