#### MOSEL VITELIC

# **MSS1506**

#### **DECEMBER**

# **VOICE ROM**

#### **Features**

- Single power can operate at 2.4 V through 6V.

- ■Current output could drive 8 ohm speaker with a transistor, Vout could drive buzzer directly.

WWW.DZSC.COM

- ■The voice content is stored up to 15 seconds and can be separated to 64 sections.

- Duration of each section can be different.

- ■Mute is available for each section up to 48 seconds totally.

- A Forever Play function is available.

- Four addressing interface modes are provided for versatile applications: CPU, Stand alone, Ring Trigger and Table Trigger.

- Stand alone mode:

- 8 sections can be accessed by 8 trigger input pins individually.

- ■Table trigger mode:

- a. A phrase is accessed by  $\overline{TG0}$ , low active.

- b. This phrase is composed of 16 elements contiguously as the table content.

- c. These 16 elements are chosen from 8 sections.

- d. Section is located and numbered by 0 through 7. WWW.DZSG.G

- ■Ring trigger mode:

- a. A section-by-section phrase is accessed by TGO, low active.

- b. This phrase is composed of 16 element (section)s contiguously as the table content.

c. Each single trigger plays next one element (section)

- following above sequence.

- d. These 16 elements are chosen from 8 sections.

- e. Section is located and numbered by 0 through 7.

- ■CPU addressing mode:

- a. 64 sections can be accessed by 6 address bits with enable strobe trigger.

- b. Section is located and numbered by 0 through 63.

- c. The address bit is high true.

- Mask option for either retriggerable output or not.

- Mask option for either Level or Edge trigger type.

- For all four modes, retrigger action restarts playing from the beginning.

- One BUSY output signal is available.

- Automatic power down function(selected by external input, pwr).

#### **General Description**

The MSS1506 is a single-chip CMOS LSI ROM that can memorize voice up to 15 seconds using MOSEL qualified coding method (MPCM).

Four addressing interfaces are provided: CPU mode, Stand Alone mode, Ring Trigger mode and Table Trigger mode for versatile applications. The voice content can be stored separatly into 64 or 8 or 16 sections or 1 phrase with arbitary length. With minimum external components, this chip can be applied to various application. Customer voice is edited and programmed into ROM by changing one mask during fabrication.

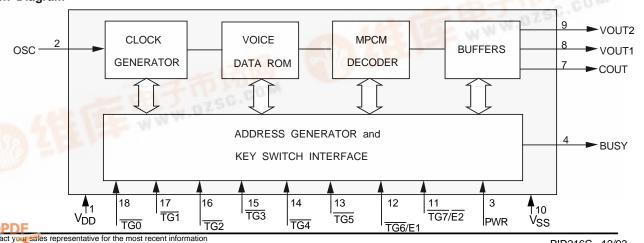

#### **Block Diagram**

dzsc.com

## **Absolute Maximum Rating**

| Symbol                                    | Rating                                                        | Unit |

|-------------------------------------------|---------------------------------------------------------------|------|

| V <sub>DD</sub> ~ V <sub>SS</sub>         | -0.5 ~ +7.0                                                   | V    |

| V <sub>IN</sub> (TG)<br>all input pins    | V <sub>SS</sub> -0.3 < V <sub>IN</sub> < V <sub>DD</sub> +0.3 | V    |

| V <sub>OUT</sub> (STS)<br>all output pins | V <sub>SS</sub> <v<sub>OUT &lt; V<sub>DD</sub></v<sub>        | V    |

| T (Operating)                             | -10 ~ +60                                                     | °C   |

| T (Storage)                               | -55 ~ +125                                                    | °C   |

## **Pad Description**

| Pad No. | Signal Name       | 1/0   | Function                                                                               |

|---------|-------------------|-------|----------------------------------------------------------------------------------------|

| 1       | V <sub>DD</sub>   | Power | Positive power supply                                                                  |

| 2       | OSC               | I     | Oscillator input                                                                       |

| 3       | PWR               | I     | Active high for non-power down, Internal pull low                                      |

| 4       | BUSY              | 0     | Busy signal output, active high                                                        |

| 5       | NC                |       |                                                                                        |

| 6       | NC                |       |                                                                                        |

| 7       | Соит              | 0     | Audio signal current output (for speaker)                                              |

| 8       | V <sub>OUT1</sub> | 0     | Audio signal voltage output (for buzzer)                                               |

| 9       | V <sub>OUT2</sub> | 0     | Audio signal voltage output (for buzzer)                                               |

| 10      | V <sub>SS</sub>   | Power | Negative power supply                                                                  |

| 11      | E2, TG7           | NC/I  | No connection (RT,TT);Trigger 7, active low( SA);<br>Enable 2, active low (CPU)        |

| 12      | E1, TG6           | NC/I  | No connection (RT,TT);Trigger 6, active low (SA);<br>Enable 1, active high (CPU)       |

| 13      | TG5               | NC/I  |                                                                                        |

| 14      | TG4               | NC/I  |                                                                                        |

| 15      | TG3               | NC/I  | No connection (RT, TT); Trigger 1 ~ 5, active low (SA); address 1 ~ 5, high true (CPU) |

| 16      | TG2               | NC/I  | (07), address 1 - 0, flight true (01 0)                                                |

| 17      | TG1               | NC/I  |                                                                                        |

| 18      | TG0               | I     | Trigger 0, active low (RT TT, SA); address 0 high true (CPU)                           |

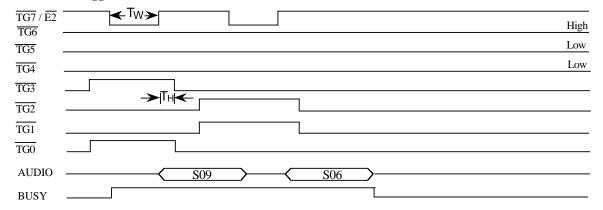

### **AC Characteristics**

| Timing         | Parameter                 | Min. | Тур. | Max. | Unit. |

|----------------|---------------------------|------|------|------|-------|

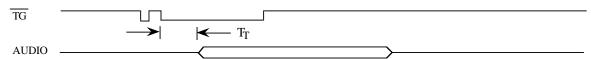

| T <sub>T</sub> | Trigger pulse width       | 10   | _    | _    | ms    |

| T <sub>W</sub> | Write Enable pulse width  | 300  | _    | _    | ns    |

| T <sub>H</sub> | Trigger address hold time | 80   | _    | _    | ns    |

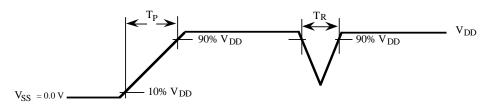

| T <sub>P</sub> | Power rise up time        | _    | _    | 1    | ms    |

| T <sub>R</sub> | Power Ripple width        | _    | _    | 1    | ms    |

#### **DC** Characteristics

| Symbol          | Parameter                            |     | Min.  | Тур. | Max. | Unit | Condition                             |                                 |  |

|-----------------|--------------------------------------|-----|-------|------|------|------|---------------------------------------|---------------------------------|--|

| I <sub>SB</sub> | Supply                               | Sta | nd by | _    | 1    | _    |                                       |                                 |  |

| I <sub>OP</sub> | Current Operating                    |     | _     | _    | 200  | μΑ   | V <sub>DD</sub> = 4.5V, I/O Open      |                                 |  |

| V <sub>IH</sub> | Input Voltage<br>(T0~T7, E1,E2, PWR) |     |       | 4    | 4.5  | 5    |                                       | V <sub>DD</sub> = 4.5V          |  |

| VIL             |                                      |     | -0.3  | 0    | 0.3  | V    | V <sub>DD</sub> = 4.5 V               |                                 |  |

| I <sub>H</sub>  | Input Current                        |     | _     | 0    | 1    | μΑ   | V <sub>DD</sub> = 4.5V                |                                 |  |

| I <sub>⊫</sub>  | ( <del>T</del> 0~ <del>T7</del> )    |     |       | _    | _    |      | -15                                   | - 00 -                          |  |

| Iн              | Input Current                        |     |       | _    | _    | 20   | μΑ                                    | V <sub>DD</sub> = 4.5V          |  |

| I <sub>L</sub>  | for PWR                              |     | -     | 0    | ı    |      |                                       |                                 |  |

| I <sub>OH</sub> | O/P Current Drive                    |     | Drive | -8   | -13  | -18  | m Λ                                   | $V_{DD} = 4.5V, V_{O/P} = 0V$   |  |

| loL             | V <sub>OUT1</sub> ,V <sub>OU</sub>   | JT2 | Sink  | 8    | 13   | 18   | mA                                    | $V_{DD} = 4.5V, V_{O/P} = 4.5V$ |  |

| I <sub>OH</sub> | Output Current (BUSY)                |     | _     | 2    | 1    | Λ    | $V_{DD} = 4.5V, V_{O/P} = 0V$         |                                 |  |

| I <sub>OL</sub> |                                      |     |       | 4    | ı    | mA   | $V_{DD} = 4.5V, V_{O/P} = 4.5V$       |                                 |  |

| lω              | Output Current (C OUT )              |     | 2.4   | 3    | 3.6  | mA   | V <sub>DD</sub> = 4.5V                |                                 |  |

| ΔF/F            | Frequency Stability                  |     |       |      | 5    | %    | [Fosc(4.5V) - Fosc(4V)]/Fosc(4.5V)    |                                 |  |

| ΔF/F            | Frequency Variation                  |     | _     | _    | 10   | %    | $V_{DD} = 4.5V$ , Rosc = $1.2M\Omega$ |                                 |  |

#### **Timing Diagram**

#### I.1. Acceptable Power On Signal & Ripple

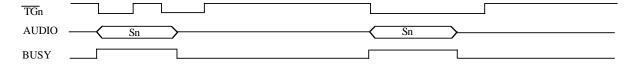

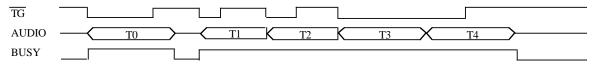

#### II.1. Stand Alone mode, No Retrigger function, Edge Trigger Mask, low active, single trigger input

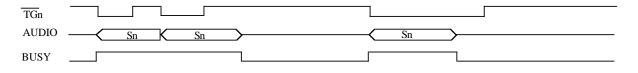

### II.2. Stand Alone mode, No Retrigger function, Level Trigger Mask, low active, single trigger input

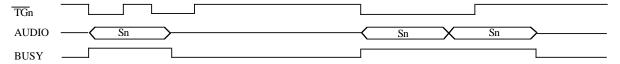

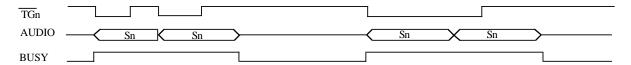

#### III.1. Stand Alone mode, Retrigger function, Edge Trigger Mask, low active, single trigger input

#### III.1. Stand Alone mode, Retrigger function, Level Trigger Mask, low active, single trigger input

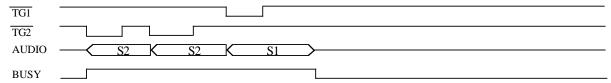

#### IV. 1. Stand Alone mode, No Retrigger function, Edge Trigger Mask, low active, two non - overlap trigger inputs

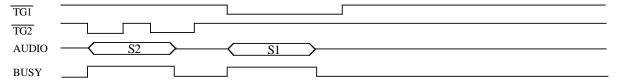

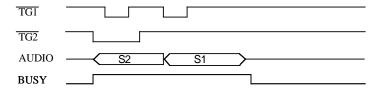

#### IV. 2. Stand Alone mode, No Retrigger function, Level Trigger Mask, low active, two non - overlap trigger inputs

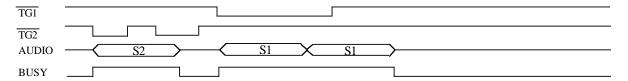

#### IV. 3. Stand Alone mode, Retrigger function, low active, two non - overlap trigger inputs

### V. 4. Retrigger function, Trigger Mask = Edge or Level, Overlap trigger inputs

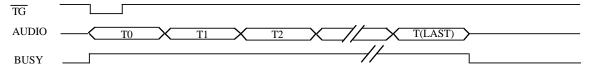

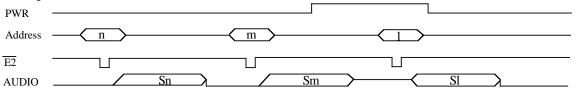

#### V. Table Trigger Mask

4

NOTE: Tn = nth element of Table content.

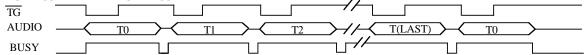

#### VII. Ring Trigger mode, Edge Trigger Mask

#### VIII. Ring Trigger mode, Level Trigger Mask

a. When trigger is shorter than a whole section output b. When trigger is longer than a whole section output

#### IX. Power keep function

#### X. Mask as Retrigger / CPU mode (6 - bit address)

#### XI. Debounce Time

Note: 1. AUDIO means cout, vout1, vout2.

- 2.  $\overline{TG0} \sim \overline{TG5}$ , E1/ $\overline{TG6}$ ,  $\overline{E2}/\overline{TG7}$  are all internal pull high.

- 3. For standalone mode,  $\overline{TG0} \sim \overline{TG7}$  are used as section trigger input (active low).

- 4. Every retrigger action will reload address and play the audio output from the beginning.

- 5. In CPU mode to avoid unwanted noise caused by abrupt change between different sections of messages, it is recommended to program PWR pin to high (V<sub>DD</sub>) during voice processing.

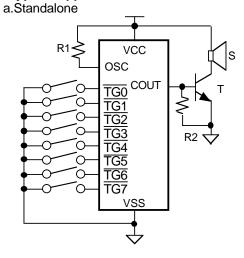

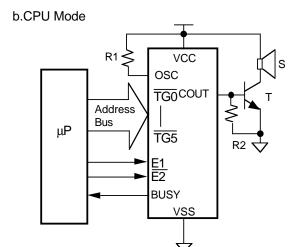

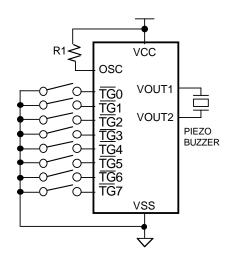

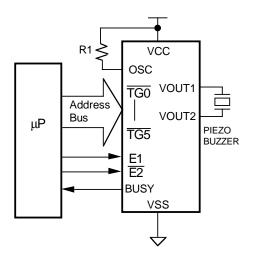

#### **Application Circuit**

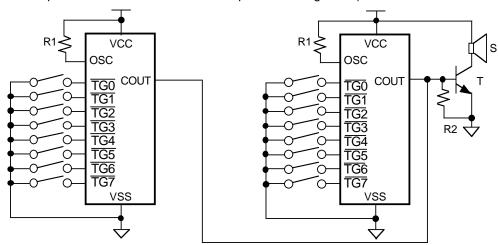

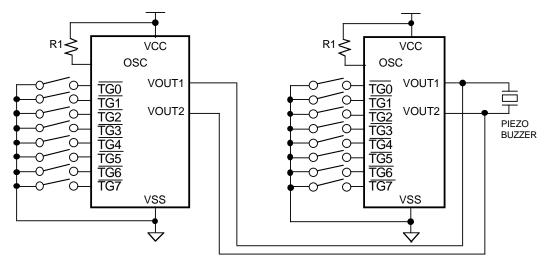

### 1. Typical Application

#### 2.Parallel Application

(Could extend depth to desired section number in parallel arrangement)

6 PID216C 12/93

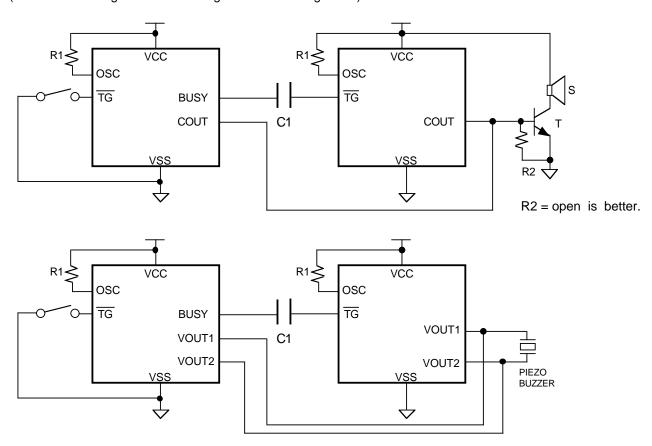

#### 3. Cascade Application

(Could extend length to desired length in serial arrangement)

Note: 1. R1 = 1.2 M  $\Omega$ , C1 = 0.1  $\mu$ f, T(transistor) =  $\beta$  > 150, R2 =open, S(speaker) = 1/4 w, 8  $\Omega$ ; all typical.

7

- 2. Piezo buzzer resonant frequency being around 1K Hz in recommended.

- 3. Input switch could be replaced by CDS.

- 4. Cout, Vout1, Vout2 are tristate during stand by state.

- 5. Both cascade and parallel application are applied in CPU mode.

PID216C 12/93

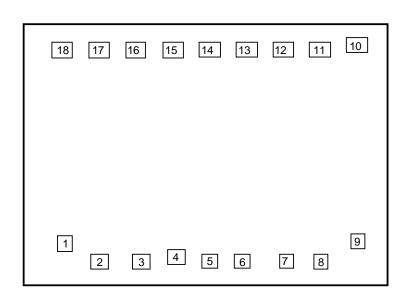

### **Bonding Diagram**

| Pad I | <u>No</u> . | Designation       |

|-------|-------------|-------------------|

| 1     |             | $V_{DD}$          |

| 2     |             | OSC               |

| 3     |             | PWR               |

| 4     |             | BUSY              |

| 5     |             | NC                |

| 6     |             | NC                |

| 7     |             | COUT              |

| 8     |             | V <sub>OUT1</sub> |

| 9     |             | V OUT2            |

| 10    |             | Vss               |

| 11    |             | TG7               |

| 12    |             | TG <sub>6</sub>   |

| 13    |             | TG5               |

| 14    |             | TG4               |

| 15    |             | TG3               |

| 16    |             | TG <sub>2</sub>   |

| 17    |             | TG <sub>1</sub>   |

| 18    |             | TG <sub>0</sub>   |

| 10    |             | 100               |

Note: Substrate is  $V_{\mbox{\scriptsize DD}}$