PRELIMINARY MX98224EC

# 24-port Dual-Speed Ethernet Switch Controller

### **FEATURES**

- Single chip 24-port 10/100M wire speed Ethernet • switching controller with all memory embedded

- Integration of 24-port dual speed, full/half duplex • capable Media Access Controllers (MACs) with RMII interfaces

- Support IEEE 802.3x compliant flow control for FDX and back-pressure flow control for HDX

- Auto-negotiation through MDC/MDIO

- Support source/destination MAC address lookup and aging within built-in storage of 8K MAC address (4K entries each entry table)

- Self address learning, forwarding, and filtering • schemes

- Store-and-Forward switching operation

- 12-group port base VLAN with port overlapping

### **GENERAL DESCRIPTION**

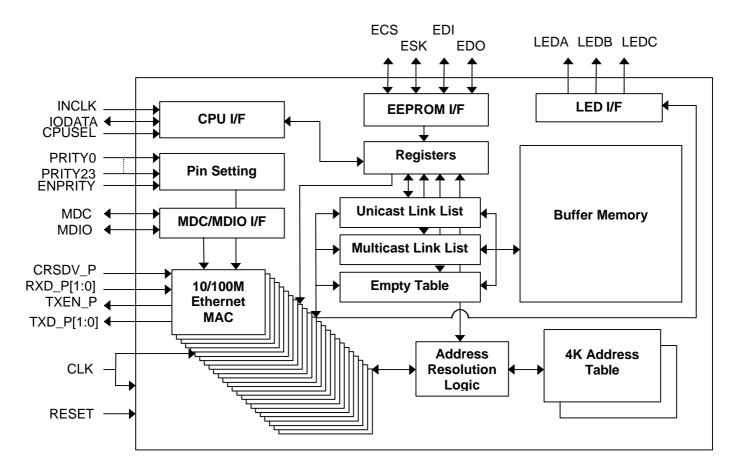

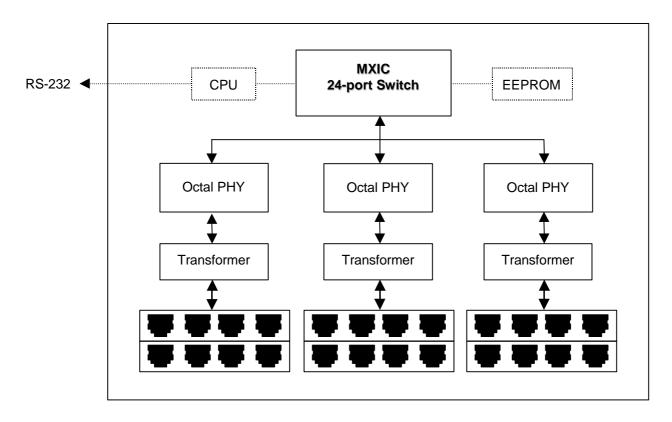

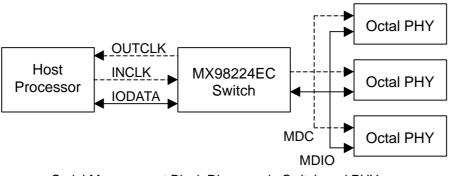

MX98224EC is a stand-alone 10/100M Ethernet switch controller with SRAM embedded which saves 2-3 extra 64KX64 SRAM cost. Any standalone desktop or enterprising Ethernet switches can be achieved by simply combining MX98224EC and quad/octal physical devices. All 24 ports are full duplex capable to provide dedicated 20/200M bandwidth connections each port. MX98224EC basically supports store-and-forward switching scheme with two address entry tables, 4K size each. The function modules integrated in controller include 24-port half/full-duplex compatible media access controller with RMII interface, address resolution logic (ARL) for address learning, filtering, recognition, priority queue manager, port base VLAN. It fully complies with IEEE Std. 802.3/802.3u/802.1q specifications and supports MDC/MDIO interface for physical layer management with industrial standard physical devices.

The switch architecture adopting dynamic buffer management shared by 24 ports can reach full-line speed of high performance application. To save system cost, single 50Mhz clock is for RMII and system requirement. MX98224EC proceeds in advanced foundry and smaller package which consumes lower power dissipation.

The smart features with low power CPU or EEPROM are for system configuration and ALR access required. Also, it emphasizes at Class of Service (CoS) which

- IEEE 802.1q CoS and two priority queues support based on port, tagging, and TOS configurations

- Address table and PHY register access allowed through CPU processor

- Dynamic buffer management

- No head-of-line blocking system support

- Power on self diagnostic .

- Serial EEPROM (93C46) interface for auto-• configuration

- Broadcast storm prevention •

- Serial CPU interface support for system configuration reauired

- Three alter/self-diagnostic LED interface WWW.DZSC.COM

- CMOS, 1.8/3.3V I/O tolerance

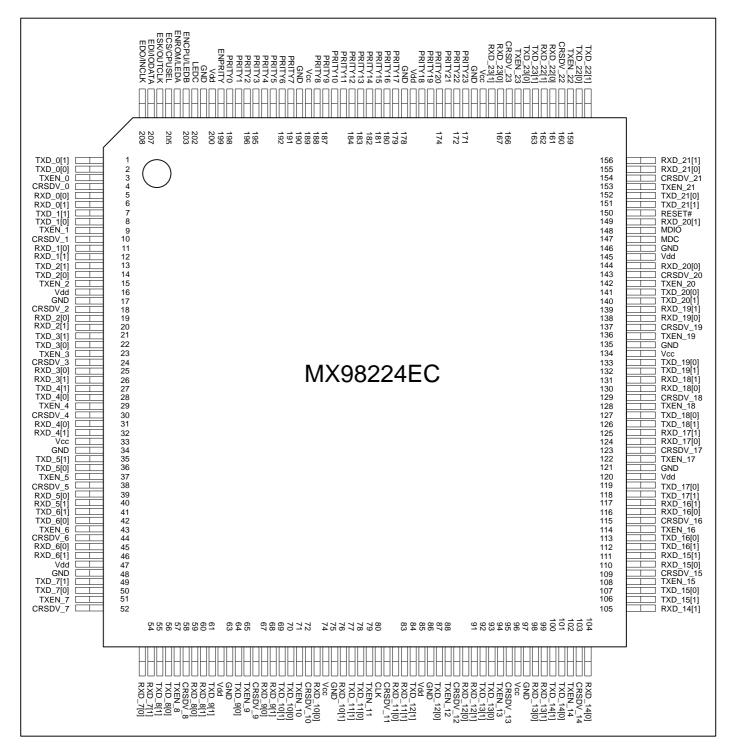

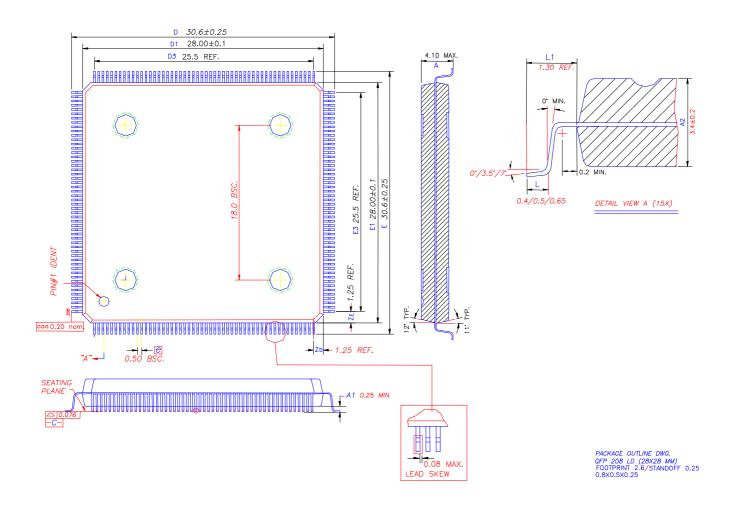

- 208 PQFP package

extracts various packet types in appropriate forwarding scheme. Now, Voice over IP (VoIP) is applied the feature for cutting voice packet latency and promise the In addition, port-base VLAN is quality of service. another valuable feature for the switches. MX98224EC offers 12 groups with port overlapping allowed. The feature can add on more security and data flow in the same switch with different groups should get connection through router. The powerful switching architecture and robust design can easily reach high performance, non-blocking data flow.

Head-of-line blocking prevents switch performance, and operation defective from other port impacts. The switch architecture provides a clean port independent It guarantees port transmission or receive operation. is not affected by other ports.

Moreover, user can discard broadcast packets regarding the threshold of system overload. This prevents potential broadcast storming from abnormal events. After buffer fullness drops in the safe margin, the switch controller jumps into flow control state to allow physical ports work as normal condition.

MX98224EC provides self on test as soon as power on or reset. It will detect all buffer memory and address table and others. If defective, LED is automatically on. Several LEDs are defined in switch controller like status of broadcast storm, packet loss, and buffer full.

Figure 1. MX98224EC Functional Block Diagram

Figure 2. MX98224EC System Block Diagram

**Optional Components**

Figure 3. MX98224EC Pin Diagram Top View

## PIN DESCRIPTION

## 10/100Mbps RMII INTERFACE

| PIN#               | PIN NAME                   | I/O | DESCRIPTION                                                                                             |

|--------------------|----------------------------|-----|---------------------------------------------------------------------------------------------------------|

| 4<br>10            | CRSDV_0<br>CRSDV_1         | Ι   | Carrier Sense/Receive Data Valid<br>Active high, indicate receive medium is non-idle. CRSDV is asserted |

| 18                 | CRSDV_2                    |     | asynchronously with respect to CLK.                                                                     |

| 24                 | CRSDV_3                    |     |                                                                                                         |

| 30                 | CRSDV_4                    |     |                                                                                                         |

| 38<br>44           | CRSDV_5<br>CRSDV 6         |     |                                                                                                         |

| 44<br>52           | CRSDV_0<br>CRSDV_7         |     |                                                                                                         |

| 58                 | CRSDV_7<br>CRSDV_8         |     |                                                                                                         |

| 66                 | CRSDV_0                    |     |                                                                                                         |

| 72                 | CRSDV_10                   |     |                                                                                                         |

| 81                 | CRSDV_11                   |     |                                                                                                         |

| 89                 | CRSDV_12                   |     |                                                                                                         |

| 95                 | CRSDV_13                   |     |                                                                                                         |

| 103                | CRSDV_14                   |     |                                                                                                         |

| 109                | CRSDV_15                   |     |                                                                                                         |

| 115                | CRSDV_16                   |     |                                                                                                         |

| 123                | CRSDV_17                   |     |                                                                                                         |

| 129                | CRSDV_18                   |     |                                                                                                         |

| 137                | CRSDV_19                   |     |                                                                                                         |

| 143                | CRSDV_20                   |     |                                                                                                         |

| 154                | CRSDV_21                   |     |                                                                                                         |

| 160                | CRSDV_22                   |     |                                                                                                         |

| 166                | CRSDV_23                   |     |                                                                                                         |

| 6, 5               | RXD_0[1:0]                 | I   | Receive Data                                                                                            |

| 12, 11             | RXD_1[1:0]                 |     | From Port 0 to Port 23, synchronous to CLK and RXD[1] is MSB.                                           |

| 20, 19             | RXD_2[1:0]                 |     | While CRSDV is deasserted, RXD[1:0] is "00".                                                            |

| 26, 25             | RXD_3[1:0]                 |     |                                                                                                         |

| 32, 31             | RXD_4[1:0]                 |     |                                                                                                         |

| 40, 39             | RXD_5[1:0]                 |     |                                                                                                         |

| 46, 45             | RXD_6[1:0]                 |     |                                                                                                         |

| 54, 53             | RXD_7[1:0]                 |     |                                                                                                         |

| 60, 59             | RXD_8[1:0]                 |     |                                                                                                         |

| 68, 67<br>76, 72   | RXD_9[1:0]                 |     |                                                                                                         |

| 76, 73             | RXD_10[1:0]                |     |                                                                                                         |

| 83, 82<br>01 00    | RXD_11[1:0]                |     |                                                                                                         |

| 91, 90<br>99, 98   | RXD_12[1:0]<br>RXD_13[1:0] |     |                                                                                                         |

| 99, 90<br>105, 104 | RXD_13[1:0]                |     |                                                                                                         |

| 111, 110           | RXD_14[1:0]                |     |                                                                                                         |

| 117, 116           | RXD_16[1:0]                |     |                                                                                                         |

| 125, 124           | RXD_17[1:0]                |     |                                                                                                         |

| 131, 130           | RXD_18[1:0]                |     |                                                                                                         |

| 139, 138           | RXD_19[1:0]                |     |                                                                                                         |

| 149, 144           | RXD_20[1:0]                |     |                                                                                                         |

| 156, 155           | RXD_21[1:0]                |     |                                                                                                         |

| 162, 161           | RXD_22[1:0]                |     |                                                                                                         |

| 102, 101           |                            |     |                                                                                                         |

| <br> |

|------|

|      |

|      |

| <br> |

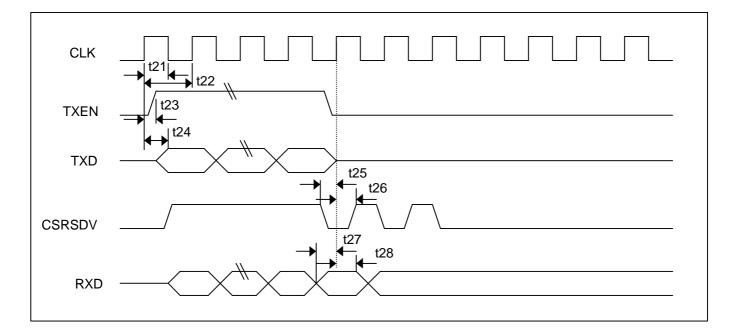

| 3<br>9<br>15<br>23<br>29<br>37<br>43<br>51<br>57<br>65<br>71<br>79<br>88<br>94<br>102<br>108<br>114<br>122<br>128<br>136<br>142<br>153<br>159<br>165                                                                                                                | TXEN_0<br>TXEN_1<br>TXEN_2<br>TXEN_3<br>TXEN_4<br>TXEN_5<br>TXEN_6<br>TXEN_7<br>TXEN_8<br>TXEN_9<br>TXEN_10<br>TXEN_10<br>TXEN_11<br>TXEN_12<br>TXEN_13<br>TXEN_14<br>TXEN_14<br>TXEN_15<br>TXEN_16<br>TXEN_17<br>TXEN_18<br>TXEN_19<br>TXEN_20<br>TXEN_21<br>TXEN_22<br>TXEN_23                                                            | O<br>4mA | Transmit Enable<br>Active high, assertion indicates the MAC is presenting di-bits on<br>TXD[1:0] for transmission. TXEN is asserted synchronously with first<br>nibble of preamable and remained asserted while all di-bits transmitted<br>are presented on RMII. TXEN is negated prior to 1 <sup>st</sup> CLK rising edge<br>following the final di-bit of frame. |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $\begin{array}{c} 1, 2\\ 7, 8\\ 13, 14\\ 21, 22\\ 27, 28\\ 35, 36\\ 41, 42\\ 49, 50\\ 55, 56\\ 61, 64\\ 69, 70\\ 77, 78\\ 84, 87\\ 92, 93\\ 100, 101\\ 106, 107\\ 112, 113\\ 118, 119\\ 126, 127\\ 132, 133\\ 140, 141\\ 151, 152\\ 157, 158\\ 163, 164\end{array}$ | TXD_0[1:0]<br>TXD_1[1:0]<br>TXD_2[1:0]<br>TXD_3[1:0]<br>TXD_4[1:0]<br>TXD_5[1:0]<br>TXD_6[1:0]<br>TXD_6[1:0]<br>TXD_7[1:0]<br>TXD_9[1:0]<br>TXD_10[1:0]<br>TXD_10[1:0]<br>TXD_11[1:0]<br>TXD_13[1:0]<br>TXD_14[1:0]<br>TXD_15[1:0]<br>TXD_15[1:0]<br>TXD_16[1:0]<br>TXD_18[1:0]<br>TXD_19[1:0]<br>TXD_20[1:0]<br>TXD_22[1:0]<br>TXD_23[1:0] | O<br>4mA | Transmit Data<br>From Port 0 to Port 23, synchronous to CLK and TXD[1] is MSB.<br>When TXEN is asserted, TXD[1:0] are accepted fro transmission.<br>TXD[1:0] is "00" when TXEN is deasserted.                                                                                                                                                                      |  |

| 80                                                                                                                                                                                                                                                                  | CLK                                                                                                                                                                                                                                                                                                                                         | I        | Reference Clock<br>For RMII and system clock use. 50MHz.                                                                                                                                                                                                                                                                                                           |  |

| Subtotal                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                             |          | 145                                                                                                                                                                                                                                                                                                                                                                |  |

#### **EEPROM INTERFACE**

| PIN#     | PIN NAME | I/O      | DESCRIPTION                                                                                                                                                                                                                             |

|----------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

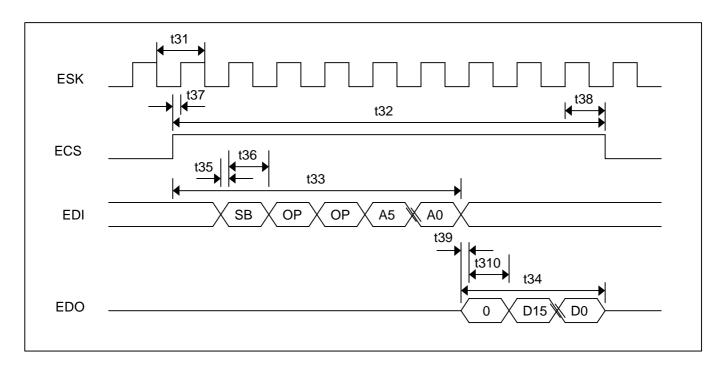

| 204      | ENROM    | I        | EEPROM Enable<br>Internally pull down. Default disable. Active high; indicated<br>configuration data is auto-loaded from EEPROM after reset. Tying<br>this pin to ground disables EEPROM interface and prevents auto-<br>configuration. |

| 205      | ECS      | O<br>4mA | EEPROM Chip Select<br>Active high.                                                                                                                                                                                                      |

| 206      | ESK      | O<br>8mA | EEPROM Clock<br>390KHz derived from system clock.                                                                                                                                                                                       |

| 207      | EDI      | O<br>4mA | EEPROM Data Input<br>Output data to the corresponding EDI pin of EEPROM.                                                                                                                                                                |

| 208      | EDO      | I        | EEPROM Data Output<br>Input data to the corresponding EDO pin of EEPROM.                                                                                                                                                                |

| Subtotal |          |          | 5                                                                                                                                                                                                                                       |

# **CoS PRIORITY SETTING**

| PIN#                          | PIN NAME                                                                                                                                                                                                                                                                                                          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                           |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 199                           | ENPRITY                                                                                                                                                                                                                                                                                                           | I   | Priority Queue Enable<br>Internally pull down. Per port base pin setting priority function enable.<br>If the pin is enabled, per port base priority settings used by EEPROM or<br>CPU is invalid. Port base priority settings controlled by EEPROM or<br>CPU will be valid when the pin is pull down. |

| 198-191<br>188-179<br>176-171 | PRITY0<br>PRITY1<br>PRITY2<br>PRITY3<br>PRITY4<br>PRITY5<br>PRITY6<br>PRITY7<br>PRITY8<br>PRITY9<br>PRITY10<br>PRITY10<br>PRITY11<br>PRITY12<br>PRITY12<br>PRITY13<br>PRITY13<br>PRITY15<br>PRITY15<br>PRITY15<br>PRITY15<br>PRITY16<br>PRITY17<br>PRITY18<br>PRITY19<br>PRITY20<br>PRITY21<br>PRITY22<br>PRITY23 | I   | Per Port Priority Enable<br>Active low. If pin pull high, the mapped port will act as high priority.                                                                                                                                                                                                  |

Subtotal

25

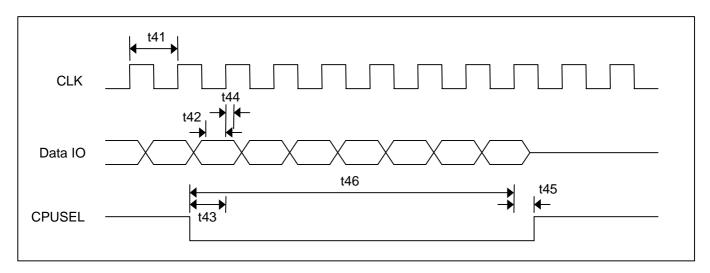

# **CPU INTERFACE**

| PIN#     | PIN NAME | I/O        | DESCRIPTION                                                                                            |

|----------|----------|------------|--------------------------------------------------------------------------------------------------------|

| 203      | ENCPU    | I          | CPU Interface Enable<br>Internally pull down. At reset, the pin is latched as CPU interface<br>enable. |

| 205      | CPUSEL   | I          | CPU Selection<br>The selected chip enable from CPU.                                                    |

| 206      | OUTCLK   | O<br>8mA   | CPU Input Clock<br>The switch generates 8.3MHz serial clock to CPU.                                    |

| 207      | IODATA   | I/O<br>4mA | CPU Data Input/Output<br>CPU read/write data & command.                                                |

| 208      | INCLK    | Ι          | CPU Output Clock<br>CPU generates 8.3MHz serial clock to Ethernet switch.                              |

| Subtotal |          |            | 5                                                                                                      |

# LED INTERFACE

| PIN#     | PIN NAME | I/O      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 204      | LEDA     | O<br>8mA | Address Table Self-test/Buffer Full LED<br>Internally pull down. Initially, after power on or reset, address table<br>will be tested and LEDC (Reset function) is keeping on until internal<br>test finished. If any error found in address table, LEDA will keep on.<br>After LEDC off, the switch is functional. If global buffer utilization is<br>full within previous 40ms intervals, LEDA will be on 40ms. It will keep<br>on if the buffer utilization keeps full within current intervals. |

| 203      | LEDB     | O<br>8mA | Buffer Memory Test/Packet Loss LED<br>Internally pull down. If power on or reset, LEDC (Reset function) is<br>keeping on and all buffer memory will be tested. If buffer memory has<br>an error found, LEDB will be on.<br>After LEDB and LEDC off, switch self-test is done. If packet loss<br>found, LEDB is keeping on 40ms within each 40ms time intervals.                                                                                                                                    |

| 202      | LEDC     | O<br>8mA | Reset/Broadcast Storm LED<br>Internally pull up. If reset, LEDC is on until all internal memory test<br>finished. Then, the pin will show the status of broadcast storm<br>packets. If the number of broadcast packets stored in switch over<br>threshold within 40ms time intervals, LEDC will be on 40ms. It will be<br>shown until broadcast storm released.                                                                                                                                    |

| Subtotal |          |          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### **MISCELLANEOUS**

| PIN#                                                                         | PIN NAME | I/O         | DESCRIPTION                                                                                                                                           |

|------------------------------------------------------------------------------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

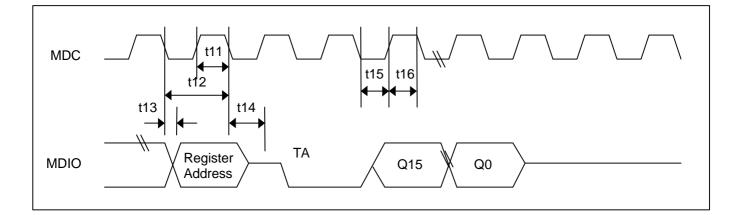

| 147                                                                          | MDC      | I/O<br>16mA | Management Data Clock<br>Internal pull down. The pin provides 2.5MHz clock for MDIO.                                                                  |

| 148                                                                          | MDIO     | I/O<br>16mA | Management Data<br>Bi-directional RMII management port data pin. MDIO is synchronous<br>with respect to MDC and is sampled on the rising edge of MDC. |

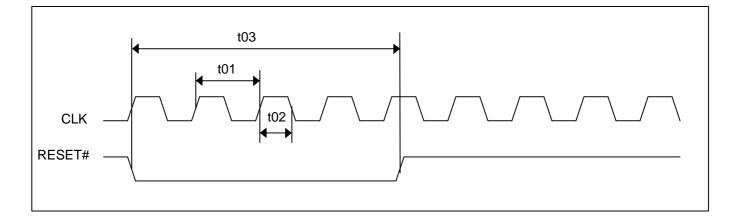

| 150                                                                          | RESET#   | I           | Chip Reset<br>Active low; be held low for some time after power-on.                                                                                   |

| 33, 74, 96,<br>134, 169,<br>189,                                             | Vcc      |             | 1.8V Core Power                                                                                                                                       |

| 16, 47, 62,<br>85, 120, 145,<br>177, 200                                     | Vdd      |             | 3.3V I/O Power                                                                                                                                        |

| 17, 34, 48,<br>63, 75, 86,<br>97, 121, 135,<br>146, 170,<br>178, 190,<br>201 | GND      |             | Ground                                                                                                                                                |

| Subtotal                                                                     |          |             | 31                                                                                                                                                    |

## **EEPROM AND CPU CONTROL REGISTERS**

| OFFSET | REGISTER                                   | OFFSET | REGISTER                               |

|--------|--------------------------------------------|--------|----------------------------------------|

| 0x00H  | Port Base VLAN Group 0 (0-11)              | 0x1BH  | Aging Timer                            |

| 0x01H  | Port Base VLAN Group 0 (12-23)             | 0x1CH  | Reserved                               |

| 0x02H  | Port Base VLAN Group 1 (0-11)              | 0x1DH  | 802.3x Pause Frame Timer               |

| 0x03H  | Port Base VLAN Group 1 (12-23)             | 0x1EH  | MAC Address 0                          |

| 0x04H  | Port Base VLAN Group 2 (0-11)              | 0x1FH  | MAC Address 1                          |

| 0x05H  | Port Base VLAN Group 2 (12-23)             | 0x20H  | MAC Address 2                          |

| 0x06H  | Port Base VLAN Group 3 (0-11)              | 0x21H  | IP/VLAN Tagging Base Priority (0-7)    |

| 0x07H  | Port Base VLAN Group 3 (12-23)             | 0x22H  | IP/VLAN Tagging Base Priority (8-15)   |

| 0x08H  | Port Base VLAN Group 4 (0-11)              | 0x23H  | IP/VLAN Tagging Base Priority (16-23)  |

| 0x09H  | Port Base VLAN Group 4 (12-23)             | 0x24H  | Reserved                               |

| 0x0AH  | Port Base VLAN Group 5 (0-11)              | 0x25H  | Reserved                               |

| 0x0BH  | Port Base VLAN Group 5 (12-23)             | 0x26H  | Reserved                               |

| 0x0CH  | Port Base VLAN Group 6 (0-11)              | 0x27H  | LED Control & VLAN Group Reset         |

| 0x0DH  | Port Base VLAN Group 6 (12-23)             | 0x28H  | CPU Access Data                        |

| 0x0EH  | Port Base VLAN Group 7 (0-11)              | 0x29H  | PHY/Address Table Operation Command    |

| 0x0FH  | Port Base VLAN Group 7 (12-23)             | 0x2AH  | Flow Control Enable (8-23)             |

| 0x10H  | Port Base VLAN Group 8 (0-11)              | 0x2BH  | Reserved                               |

| 0x11H  | Port Base VLAN Group 8 (12-23)             | 0x2CH  | Flow Control Enable (0-7)              |

| 0x12H  | Port Base VLAN Group 9 (0-11)              | 0x2DH  | Reserved                               |

| 0x13H  | Port Base VLAN Group 9 (12-23)             | 0x2EH  | Reserved                               |

| 0x14H  | Port Base VLAN Group 10 (0-11)             | 0x2FH  | Reserved                               |

| 0x15H  | Port Base VLAN Group 10 (12-23)            | 0x30H  | Auto-negotiation Disable (0-15)        |

| 0x16H  | Port Base VLAN Group 11 (0-11)             | 0x31H  | Auto-negotiation (16-23) & Force Speed |

| 0x17H  | Port Base VLAN Group 11 (12-23)            | _      | Setting (0-7)                          |

| 0x18H  | Configuration 0 & Port Base Priority (0-7) | 0x32H  | Force Speed Setting (8-23)             |

| 0x19H  | Port Base Priority (8-23)                  | 0x33H  | Force Half/Full Duplex Setting (0-15)  |

| 0x1AH  | Configuration 1                            | 0x34H  | Force Half/Full Duplex Setting (16-23) |

|        |                                            |        |                                        |

Note : 1. 93C46 EEPROM must be in 16-bit mode

2. The contents of EEPROM and CPU access registers are the same as following descriptions

3. (A-B) means port number setting from A to B

# Port Base VLAN Group 0 (0-11) (Reg00H), default = 0x0FFFH

| BIT     | DESCRIPTION                                                                                                                                                                                                                   | TYPE | DEFAULT |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 0.11-0  | Port 0-11 VLAN Group 0<br>Default 1; all ports are into single group.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 0 member | R/W  | 0xFFF   |

| 0.15-12 | N/A                                                                                                                                                                                                                           |      |         |

# Port Base VLAN Group 0 (12-23) (Reg01H), default = 0x0FFFH

| BIT     | DESCRIPTION                                                                                                                                                                                                                     | TYPE | DEFAULT |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 1.11-0  | Port 12-23 VLAN Group 0<br>Default 1; all ports are into single group.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 0 member | R/W  | 0xFFF   |

| 1.15-12 | N/A                                                                                                                                                                                                                             |      |         |

# Port Base VLAN Group 1 (0-11) (Reg02H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                  | ТҮРЕ | DEFAULT |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 2.11-0  | Port 0-11 VLAN Group 1<br>Default 0; group 1 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 1 member | R/W  | 0x000   |

| 2.15-12 | N/A                                                                                                                                                                                                                          |      |         |

## Port Base VLAN Group 1 (12-23) (Reg03H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                    | TYPE | DEFAULT |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 3.11-0  | Port 12-23 VLAN Group 1<br>Default 0; group 1 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 1 member | R/W  | 0x000   |

| 3.15-12 | N/A                                                                                                                                                                                                                            |      |         |

# Port Base VLAN Group 2 (0-11) (Reg04H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                  | ТҮРЕ | DEFAULT |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 4.11-0  | Port 0-11 VLAN Group 2<br>Default 0; group 2 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 2 member | R/W  | 0x000   |

| 4.15-12 | N/A                                                                                                                                                                                                                          |      |         |

# Port Base VLAN Group 2 (12-23) (Reg05H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                    | TYPE | DEFAULT |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 5.11-0  | Port 12-23 VLAN Group 2<br>Default 0; group 2 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 2 member | R/W  | 0x000   |

| 5.15-12 | N/A                                                                                                                                                                                                                            |      |         |

## Port Base VLAN Group 3 (0-11) (Reg06H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                  | TYPE | DEFAULT |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 6.11-0  | Port 0-11 VLAN Group 3<br>Default 0; group 3 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 3 member | R/W  | 0x000   |

| 6.15-12 | N/A                                                                                                                                                                                                                          |      |         |

## Port Base VLAN Group 3 (12-23) (Reg07H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                    | TYPE | DEFAULT |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 7.11-0  | Port 12-23 VLAN Group 3<br>Default 0; group 3 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 3 member | R/W  | 0x000   |

| 7.15-12 | N/A                                                                                                                                                                                                                            |      |         |

# Port Base VLAN Group 4 (0-11) (Reg08H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                  | TYPE | DEFAULT |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 8.11-0  | Port 0-11 VLAN Group 4<br>Default 0; group 4 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 4 member | R/W  | 0x000   |

| 8.15-12 | N/A                                                                                                                                                                                                                          |      |         |

## Port Base VLAN Group 4 (12-23) (Reg09H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                    | TYPE | DEFAULT |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 9.11-0  | Port 12-23 VLAN Group 4<br>Default 0; group 4 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 4 member | R/W  | 0x000   |

| 9.15-12 | N/A                                                                                                                                                                                                                            |      |         |

## Port Base VLAN Group 5 (0-11) (Reg0AH), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                  | ТҮРЕ | DEFAULT |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| A.11-0  | Port 0-11 VLAN Group 5<br>Default 0; group 5 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 5 member | R/W  | 0x000   |

| A.15-12 | N/A                                                                                                                                                                                                                          |      |         |

## Port Base VLAN Group 5 (12-23) (Reg0BH), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                    | TYPE | DEFAULT |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| B.11-0  | Port 12-23 VLAN Group 5<br>Default 0; group 5 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 5 member | R/W  | 0x000   |

| B.15-12 | N/A                                                                                                                                                                                                                            |      |         |

# Port Base VLAN Group 6 (0-11) (Reg0CH), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                  | TYPE | DEFAULT |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| C.11-0  | Port 0-11 VLAN Group 6<br>Default 0; group 6 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 6 member | R/W  | 0x000   |

| C.15-12 | N/A                                                                                                                                                                                                                          |      |         |

## Port Base VLAN Group 6 (12-23) (Reg0DH), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                    | TYPE | DEFAULT |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| D.11-0  | Port 12-23 VLAN Group 6<br>Default 0; group 6 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 6 member | R/W  | 0x000   |

| D.15-12 | N/A                                                                                                                                                                                                                            |      |         |

## Port Base VLAN Group 7 (0-11) (Reg0EH), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                  | TYPE | DEFAULT |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| E.11-0  | Port 0-11 VLAN Group 7<br>Default 0; group 7 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 7 member | R/W  | 0x000   |

| E.15-12 | N/A                                                                                                                                                                                                                          |      |         |

## Port Base VLAN Group 7 (12-23) (Reg0FH), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                    | TYPE | DEFAULT |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| F.11-0  | Port 12-23 VLAN Group 7<br>Default 0; group 7 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 7 member | R/W  | 0x000   |

| F.15-12 | N/A                                                                                                                                                                                                                            |      |         |

# Port Base VLAN Group 8 (0-11) (Reg10H), default = 0x0000H

| BIT      | DESCRIPTION                                                                                                                                                                                                                  | TYPE | DEFAULT |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 10.11-0  | Port 0-11 VLAN Group 8<br>Default 0; group 8 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 8 member | R/W  | 0x000   |

| 10.15-12 | N/A                                                                                                                                                                                                                          |      |         |

# Port Base VLAN Group 8 (12-23) (Reg11H), default = 0x0000H

| BIT      | DESCRIPTION                                                                                                                                                                                                                    | TYPE | DEFAULT |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 11.11-0  | Port 12-23 VLAN Group 8<br>Default 0; group 8 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 8 member | R/W  | 0x000   |

| 11.15-12 | N/A                                                                                                                                                                                                                            |      |         |

# Port Base VLAN Group 9 (0-11) (Reg12H), default = 0x0000H

| BIT      | DESCRIPTION                                                                                                                                                                                                                  | TYPE | DEFAULT |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 12.11-0  | Port 0-11 VLAN Group 9<br>Default 0; group 9 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 9 member | R/W  | 0x000   |

| 12.15-12 | N/A                                                                                                                                                                                                                          |      |         |

## Port Base VLAN Group 9 (12-23) (Reg13H), default = 0x0000H

| BIT      | DESCRIPTION                                                                                                                                                                                                                    | TYPE | DEFAULT |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 13.11-0  | Port 12-23 VLAN Group 9<br>Default 0; group 9 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 9 member | R/W  | 0x000   |

| 13.15-12 | N/A                                                                                                                                                                                                                            |      |         |

# Port Base VLAN Group 10 (0-11) (Reg14H), default = 0x0000H

| BIT      | DESCRIPTION                                                                                                                                                                                                                     | TYPE | DEFAULT |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 14.11-0  | Port 0-11 VLAN Group 10<br>Default 0; group 10 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 10 member | R/W  | 0x000   |

| 14.15-12 | N/A                                                                                                                                                                                                                             |      |         |

# Port Base VLAN Group 10 (12-23) (Reg15H), default = 0x0000H

| BIT      | DESCRIPTION                                                                                                                                                                                                                       | TYPE | DEFAULT |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 15.11-0  | Port 12-23 VLAN Group 10<br>Default 0; group 10 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 10 member | R/W  | 0x000   |

| 15.15-12 | N/A                                                                                                                                                                                                                               |      |         |

## Port Base VLAN Group 11 (0-11) (Reg16H), default = 0x0000H

| BIT      | DESCRIPTION                                                                                                                                                                                                                     | TYPE | DEFAULT |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 16.11-0  | Port 0-11 VLAN Group 11<br>Default 0; group 11 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 0 and bit 11 for port 11<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 11 member | R/W  | 0x000   |

| 16.15-12 | N/A                                                                                                                                                                                                                             |      |         |

## Port Base VLAN Group 11 (12-23) (Reg17H), default = 0x0000H

| BIT      | DESCRIPTION                                                                                                                                                                                                                       | TYPE | DEFAULT |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 17.11-0  | Port 12-23 VLAN Group 11<br>Default 0; group 11 not in use if all zero.<br>One bit per port; e.g. bit 0 for port 12 and bit 11 for port 23<br>0 : disable; to be treat as an isolated port<br>1 : enable; to be a group 11 member | R/W  | 0x000   |

| 17.15-12 | N/A                                                                                                                                                                                                                               |      |         |

# Configuration 0 and Port Base Priority (0-7) (Reg18H), default = 0x0022H

| BIT     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                            | TYPE | DEFAULT |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 18.0    | Continuous 16-time Collision Drop Disable<br>0 : packet that runs into 16 consecutive collision will be dropped<br>1 : packet that runs into 16 consecutive collision will NOT be dropped                                                                                                                                                                                                                                                              | R/W  | 0       |

| 18.1    | Timeout disable<br>0 : packet will NOT be dropped if packet has been queued over 1 second<br>1 : packet will be dropped in spite of packet being queue over 1 second                                                                                                                                                                                                                                                                                   | R/W  | 1       |

| 18.3-2  | CRC Hashing Selection<br>48-bit DA/SA address is translated separated into 12-bit entry pointer of<br>address table for address learning and recognition. The translation is by<br>aid of CRC generator within the switch controller. The index of entry<br>pointer selection is defined by:<br>00: bit [11:0] of CRC are selected<br>01: bit [16:5] of CRC are selected<br>10: bit [24:13] of CRC are selected<br>11: bit [30:19] of CRC are selected | R/W  | 00      |

| 18.4    | Direct Mapping<br>It means bit [63:52] of DA/SA address directly as an index of address<br>table.<br>0 : CRC calculation to get the hashing index of address table<br>1 : direct mapping enable                                                                                                                                                                                                                                                        | R/W  | 1       |

| 18.5    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W  | 0       |

| 18.6    | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |         |

| 18.7    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W  | 1       |

| 18.15-8 | Port 0-7 Priority<br>Port base priority settings from port 0 to port 7. If external pins of port<br>base priority are set, the content of EEPROM or CPU will be overridden.<br>One bit per port; e.g. bit 8 for port 0 and bit 15 for port 7.<br>0 : disable<br>1 : enable, the port of packets always in high priority                                                                                                                                | R/W  | 0x00H   |

# Port Base Priority (8-23) (Reg19H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                                                                                                                                                | TYPE | DEFAULT |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 19.15-0 | Port 8-23 Priority<br>Port base priority settings from port 8 to port 23. If external pins of port<br>base priority are set, the content of EEPROM or CPU will be overridden.<br>One bit per port; e.g. bit 0 for port 8 and bit 15 for port 23.<br>0 : disable<br>1 : enable, the port of packets always in high priority | R/W  | 0x0000H |

# Configuration 1 (Reg1AH), default = 0x502EH

| BIT     |                                                                             |                                                                                                                |                      |                       | DES     | CRIPT   | ON                                                                                                  | TYPE | DEFAULT |

|---------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|---------|---------|-----------------------------------------------------------------------------------------------------|------|---------|

| 1A.3-0  | Reser                                                                       | ved                                                                                                            |                      |                       |         |         |                                                                                                     | R/W  | 0xFH    |

| 1A.5-4  | In nor<br>within<br>The s<br>Etherr<br>00 : st<br>01 : fir<br>in<br>10 : pa | off Ope<br>mal b<br>2 <sup>n</sup> –1<br>witch<br>net per<br>andard<br>rst two<br>transi<br>acket r<br>acket r | R/W                  | 00                    |         |         |                                                                                                     |      |         |

| 1A.6    |                                                                             | e back<br>able                                                                                                 | ure Disa<br>a pressu |                       | alf dup | lex cor | nection for all ports                                                                               | R/W  | 0       |

| 1A.7    | N/A                                                                         |                                                                                                                |                      |                       |         |         |                                                                                                     |      |         |

| 1A.8    | Reser                                                                       | ved                                                                                                            |                      |                       |         |         |                                                                                                     | R/W  | 0       |

| 1A.14-9 | Bit 9<br>transn                                                             | to 11<br>nitted                                                                                                | wherea               | is a deo<br>is bit 12 | 2 to 1  | 4 to a  | for low priority packets to be<br>decimal value for high priority<br>of high to low priority value. | R/W  | 0x28H   |

|         |                                                                             |                                                                                                                | Value<br>Bit 12      | Low Pr<br>Bit 11      |         |         | Meaning                                                                                             |      |         |

|         | 0/1                                                                         | 0/1                                                                                                            | 0/1                  | 0                     | 0       | 0       | High priority port packets need<br>to be sent first until empty;<br>then, low priority packets      |      |         |

|         | 0                                                                           | 1                                                                                                              | 1                    | 0                     | 0       | 1       | The transmission ratio of high to low priority packets is 3 : 1                                     |      |         |

| 1A.15   | Aging<br>Enabl<br>0 : en<br>1 : dis                                         | e the f<br>able                                                                                                | R/W                  | 0                     |         |         |                                                                                                     |      |         |

# Aging Timer (Reg1BH), default = 0x0005H

| BIT     |                                                            | DESCRIPTION                                                                                                                                       | TYPE | DEFAULT |

|---------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 1B.15-0 | age out the least                                          | es for address table. The timer period is defined to<br>unused entries on address table. The formula is<br>X 65536 X 1ms. Here are some examples: | R/W  | 0x0005H |

|         | Bit 15 – Bit 0<br>0x0001H<br>0x0005H<br>0x001BH<br>0x0037H | Aging Timer<br>65.5 sec (around 1 min)<br>327.7 sec (around 5.5 min)<br>1769.5 sec (around 30 min)<br>3604.5 sec (around 1 hr)                    |      |         |

### Reserved (Reg1CH), default = 0xC350H

| BIT     | DESCRIPTION | TYPE | DEFAULT |

|---------|-------------|------|---------|

| 1C.15-0 | Reserved    | R/W  | 0xC350H |

## 802.3x Pause Frame Timer (Reg1DH), default = 0x01FFH

| BIT     | DESCRIPTION                                                                                                                                                                                                                                                 | TYPE | DEFAULT |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 1D.4-0  | Reserved                                                                                                                                                                                                                                                    | R/W  | 0x1FH   |

| 1D.15-5 | Flow Control Counter<br>The timer determines the period, namely "pause time", to inhibit packet<br>transmission from attached host for flow control. The variable pause<br>time of pause frame is equal to the decimal value times 32 plus 31 slot<br>time. | R/W  | 0x1E0H  |

### MAC Address 0 (Reg1EH), default = 0x0000H

| BIT     | DESCRIPTION                            | TYPE | DEFAULT |

|---------|----------------------------------------|------|---------|

| 1E.15-0 | Switch's MAC ID for address bit [15:0] | R/W  | 0x0000H |

### MAC Address 1 (Reg1FH), default = 0x0000H

| BIT     | DESCRIPTION                             | TYPE | DEFAULT |

|---------|-----------------------------------------|------|---------|

| 1F.15-0 | Switch's MAC ID for address bit [31:16] | R/W  | 0x0000H |

## MAC Address 2 (Reg20H), default = 0x0000H

| BIT     | DESCRIPTION                             | TYPE | DEFAULT |

|---------|-----------------------------------------|------|---------|

| 20.15-0 | Switch's MAC ID for address bit [47:32] | R/W  | 0x0000H |

### IP/VLAN Tagging Base Priority (0-7) (Reg21H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                        | TYPE | DEFAULT |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 21.7-0  | TOS (IP Base)<br>Enable for port 0-7 to recognize the TOS field of IP priority packets. One<br>bit per port; e.g. bit 0 for port 0 and bit 7 for port 7.<br>0 : disable<br>1 : enable              | R/W  | 0x00H   |

| 21.15-8 | TCI (VLAN Tagging Base)<br>Enable for port 0-7 to recognize the TCI field of VLAN priority packets.<br>One bit per port; e.g. bit 8 for port 0 and bit 15 for port 7.<br>0 : disable<br>1 : enable | R/W  | 0x00H   |

# IP/VLAN Tagging Base Priority (8-15) (Reg22H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                          | TYPE | DEFAULT |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 22.7-0  | TOS (IP Base)<br>Enable for port 8-15 to recognize the TOS field of IP priority packets.<br>One bit per port; e.g. bit 0 for port 8 and bit 7 for port 15.<br>0 : disable<br>1 : enable              | R/W  | 0x00H   |

| 22.15-8 | TCI (VLAN Tagging Base)<br>Enable for port 8-15 to recognize the TCI field of VLAN priority packets.<br>One bit per port; e.g. bit 8 for port 8 and bit 15 for port 15.<br>0 : disable<br>1 : enable | R/W  | 0x00H   |

## IP/VLAN Tagging Base Priority (16-23) (Reg23H), default = 0x0000H

| BIT     | DESCRIPTION                                                                                                                                                                                           | TYPE | DEFAULT |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 23.7-0  | TOS (IP Base)<br>Enable for port 16-23 to recognize the TOS field of IP priority packets.<br>One bit per port; e.g. bit 0 for port 16 and bit 7 for port 23.<br>0 : disable<br>1 : enable             | R/W  | 0x00H   |

| 23.15-8 | TCI (VLAN Tagging Base)<br>Enable for port 8-15 to recognize the TCI field of VLAN priority packets.<br>One bit per port; e.g. bit 8 for port 16 and bit 15 for port 23.<br>0 : disable<br>1 : enable | R/W  | 0x00H   |

### Reserved (Reg24H), default = 0xB081H

| BIT     | DESCRIPTION | TYPE | DEFAULT |

|---------|-------------|------|---------|

| 24.15-0 | Reserved    | R/W  | 0xB081H |

## Reserved (Reg25H), default = 0x0040H

| BIT     | DESCRIPTION | TYPE | DEFAULT |

|---------|-------------|------|---------|

| 25.15-0 | Reserved    | R/W  | 0x0040H |

### Reserved (Reg26H), default = 0x0082H

| BIT     | DESCRIPTION | TYPE | DEFAULT |

|---------|-------------|------|---------|

| 26.15-0 | Reserved    | R/W  | 0x0082H |

# LED Control and VLAN Group Reset (Reg27H), default = 0x0200H

| BIT     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                | TYPE | DEFAULT |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 27.0    | Port Grouping Command<br>When, initially, the execution of default values of the VLAN registers<br>(Reg00H-17H) or VLAN grouping settings required via CPU/EEPROM,<br>VLAN grouping contents need to write into the registers; then, grouping<br>command is put into action. After grouping command is done, the bit will<br>be self-clean to 0.<br>0 : Idle<br>1 : Port regrouping enable | R/W  | 0       |

| 27.2-1  | Reserved                                                                                                                                                                                                                                                                                                                                                                                   | R/W  | 00      |

| 27.3    | Broadcast Storm LED<br>0 : LED displays the broadcast storm symptom in high priority packets<br>1 : LED displays the broadcast storm symptom of all packets                                                                                                                                                                                                                                | R/W  | 1       |

| 27.4    | Packet Loss LED<br>0 : LED displays the high priority packet loss<br>1 : LED displays all packet loss                                                                                                                                                                                                                                                                                      | R/W  | 1       |

| 27.15-5 | N/A                                                                                                                                                                                                                                                                                                                                                                                        |      | 0x010H  |

# CPU Access Data (Reg28H), default = 0x0000H