# MN1959041

# Commercial MPEG-4 Video Codec IC for W-CDMA Mobile Visual Terminals

# Overview

MN1959041 is an image-processing DSP that adopts a vector pipelined architecture. It provides an extensive set of features that allow it to implement the high-efficiency image and video encoding and decoding required for image communication, recording, and playback. It implements encoding and decoding that conform to the H.263 and MPEG-4 Simple@L1 video encoding standards, and decoding that conforms to the MPEG-4 Simple@L3 video encoding standard. It includes dedicated special-purpose circuits for high-speed decoding of the MPEG-4 core profile.

### Features

- General-purpose DSP core (MP: Main Processor) that can implement complex processing flexibly

- Provides an instruction set of 43 instructions, including both scalar and vector instructions.

- Provides interrupt control and task management functions that issue VCE/VIF/MIF (described later) start/stop instructions and DMA transfer instructions.

- Special-purpose arithmetic circuit (VCE: Video Codec Engine) that implements a high-speed video codec

- Integer precision and half-pel precision motion detection circuit (MEF/MEH)

- Discrete cosine transformation/inverse discrete cosine transformation circuits (DCT/IDCT)

- Variable-length encoding and decoding circuits (VLC/VLD)

- Blocking noise elimination circuit (PNR)

- Shape information decoding circuit (CAD)

- Pixel supplementing circuit (PADDING)

- Image synthesis circuit (COMPOSITE)

- Full complement of image signal input and output functions

- Video interface circuit (VIF) that supports both portrait and landscape orientation LCDs

- Support for CIF and QCIF 4:2:2 format video input from CMOS cameras

- P in P function that displays a subscreen in the lower right of the main screen

- Cursor and blue background display functions.

- Mosquito noise elimination filter

- Functions for picture quality adjustment and for combining video and graphics

- IIC (Inter IC) interface (Conforms to Version 2.0, standard and fast mode)

- Video signal format conversion function (YCbCr 4:2:2  $\rightarrow$  RGB; can be stopped when not needed.)

- Graphics overlay function (Either post RGB conversion or post dithering can be selected.)

- Video signal adjustment functions: outline enhancement, tint, color gain, brightness, contrast, and gamma adjustment

- Dithering function for pseudo 24-bit color  $(2 \times 2 \text{ matrix})$

- Monochrome conversion function (Either monochrome or sepia can be specified.)

- Allows moving the display area (a 176-pixel × 220-line area placed anywhere within a 352-pixel × 288-line image)

- YCbCr 4:2:2 test image generation function (75% color bar, horizontal/vertical stripe, arbitrary brightness/color difference)

- · Camera reset control function

- Large on-chip DRAM capacity

- On-chip 20 Mbit DRAM provided to reduce parts counts and achieve overall system cost reductions

# Features (continued)

- Built-in multifunction memory interface

- Memory interface circuit (MIF) for batch centralized management of DMA transfers between internal DRAM and the following internal circuit blocks: main processor (MP) block, host interface (HIF) block, and video interface block (VIF).

- 16-bit internal DRAM bus width for high-speed data transfers

- Adopts a DMA transfer reservation and reservation unit prioritization method for efficient data transfers.

- Ring buffer structure and matrix address access structure

- Extensive set of peripheral functions

- · One nonmaskable and two maskable interrupt systems

- Parallel I/O functions

- Timer functions

- Microcode downloading function

- Program debugging mode

- Provides a dedicated debugging mode that can access all memory spaces in the IC for easy program debugging during microcode development.

- Supply voltage: 3.3 V external (2.9 V) and 1.8 V internal

PLL block: 3.3 V (2.9 V)

DRAM block: 3.3 V and 1.8 V

- Internal operating frequency: 54 MHz (External input frequency: 76.8 kHz)

- Package: 239-pin CSP

- Applications

- Cell phones, PDAs, and other communication equipment

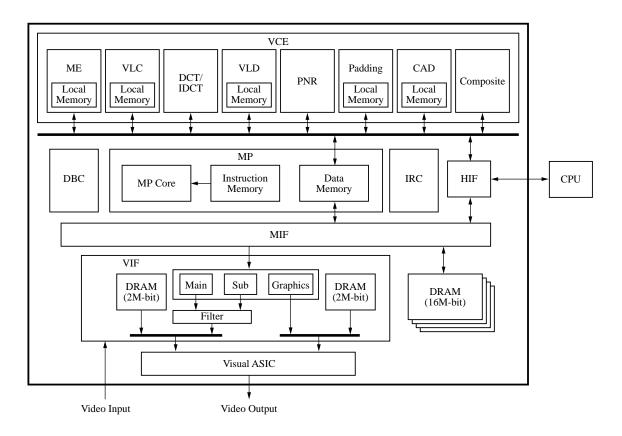

# Block Diagram

MN1959041 consists of the following hardware blocks.

- MP (Main Processor)

- HIF (Host Interface)

- MIF (Memory Interface)

- Visual ASIC

- IRC (Interrupt Controller)

- VCE (Video Codec Engine)

- VIF (Video Interface)

- DBC (Debug Controller)

# Functional Description

1. MP (Main Processor) Block

The MP block is a processor core that can interpret and execute programs. It has the following features.

- 16-bit fixed-point DSP core

- Instruction cycle: 18.6 ns (53.76 MHz)

- Most instructions execute in a single machine cycle.

- Instruction length: 32 bits, data length: 16 bits

- Program memory: 16K words, boot memory: 1K words

- On-chip data memory: total of 21K words in three areas

- Data path functions: 16-bit extended arithmetic and logic unit (EALU)

- Multiplier: 16-bit × 16-bit

- Arithmetic unit: 32 bits

- Shifter: 32 bits

- General-purpose registers: sixteen 16-bit registers

- Double bank data memory structure that supports parallel execution of DMA transfers and MP internal calculations

- Each data memory has its own matrix addressing generator for accessing matrices in a memory space.

- Provides vector pipelined arithmetic instructions that allow a single engine block to be embedded in a vector pipeline for execution.

- · Conditional vector pipeline instructions

- Loop control with four independent loop counters

- Subroutine control with up to 16 levels of nesting

- Dedicated interrupt program counter stack

#### 2. IRC (Interrupt Controller) Block

MN1959041 can temporarily halt an executing program when an interrupt request occurs, transfer control to an interrupt handler, and then continue the interrupted program when the interrupt handling completes.

This interrupt function does not interrupt instruction execution itself, but occurs between instructions. Note that this means that when an instruction that requires multiple clock cycles, such as a vector instruction, is executing, there are periods when interrupts cannot be accepted. Also note that there are cases where the occurrence of an interrupt can result in an MP or VCE state transition.

There are two types of interrupt: internal interrupts that occur within the MP, and external interrupts that occur outside the MP.

Interrupts also are classified into the following two classes:

Maskable interrupts: interrupts that can be enabled or disabled under program control, and

Nonmaskable interrupts: Interrupts that cannot be disabled.

Interrupts are assigned priority levels, and when multiple interrupts occur at the same time, the interrupt with the highest priority is accepted first. When multiple interrupts with the same priority level occur at the same time, either the software must determine the priority level or the priority must be controlled in software using the interrupt mask register.

Table 1 shows the interrupt types.

- Functional Description (continued)

- 2. IRC (Interrupt Controller) Block (continued)

Table 1. Interrupt Types

| Priorit | y level          | Masking     | Interrupt                          |

|---------|------------------|-------------|------------------------------------|

| 1       | High Nonmaskable |             | Watchdog timer interrupt           |

| 2       |                  | Nonmaskable | External pin nonmaskable interrupt |

| 3       |                  | Maskable    | Stack exception (stack overflow)   |

|         |                  | Maskable    | Stack exception (stack underflow)  |

|         |                  | Maskable    | Software interrupt                 |

|         |                  | Maskable    | Interrupt request No. 0            |

|         |                  |             |                                    |

|         | Low              |             | Interrupt request No. 12           |

#### 3. HIF (Host Interface) Block

The HIF block performs the data transfers between MN1959041 and an external CPU. The IC and the CPU are connected by a 16-bit data bus. During these transfers, the CPU must set, in advance, the bus mode, which determines the physical usage of the data bus. The CPU must set up 16-bit bus mode for transfers with the IC, but can use 8-bit or 16-bit access for other purposes. For example, the CPU can use 8-bit access for bit stream data, and use 16-bit access for all other data transfers.

A total of 32 signal lines are required for to the host memory (HM), and for write operations, the IC uses two write enable lines to distinguish between 8-bit and 16-bit access. For read access, the IC always operates in 16-bit output mode in response to the read enable signal. (The CPU must distinguish between the 16 bits of valid data and 8 bits of valid data cases.)

#### 4. VCE (Video Coded Engine) Block

MN1959041 includes a built-in VCE that executes video codec operations at high speeds. In particular, it includes the following circuits.

- Motion detection circuits (MEF, MEH)

- Discrete cosine transformation/inverse discrete cosine transformation circuits (DCT/IDCT)

- Variable-length encoding and decoding circuits (VLC/VLD)

- Blocking noise elimination circuit (PNR)

- Shape information decoding circuit (CAD)

- Pixel supplementing circuit (PADDING)

- Image synthesis circuit (COMPOSITE)

The tables below shows the special-purpose circuits (engines) that form the VCE classified as encoder engine or decoder engine.

| Engine   | Function                             | Туре |  |  |  |  |  |

|----------|--------------------------------------|------|--|--|--|--|--|

| MEF      | Full pel motion detection            | Α    |  |  |  |  |  |

| MEH      | Half pel motion detection            | А    |  |  |  |  |  |

| VLC      | Variable-length coding               | А    |  |  |  |  |  |

| DCT/IDCT | One-dimensional DCT/IDCT calculation | В    |  |  |  |  |  |

#### Table 2. Encoder Engines

- Functional Description (continued)

- 4. VCE (Video Coded Engine) Block (continued)

| Table 3. Decoder Engines |  |

|--------------------------|--|

|--------------------------|--|

| Engine    | Function                                               | Туре |

|-----------|--------------------------------------------------------|------|

| MEH       | Half pel generation                                    | А    |

| IDCT      | One-dimensional IDCT calculation                       | В    |

| VLD       | Variable-length decoding                               | Α    |

| PNR       | Blocking noise elimination                             | В    |

| PADDING   | Horizontal/vertical, expanded, and fixed-value padding | А    |

| CAD       | Shape information decoding                             | Α    |

| COMPOSITE | Image composition                                      | В    |

| THROUGH   | Data through (Data is output without processing)       | В    |

The CAD, PADDING, and COMPOSITE items in the above table are core profile engines.

The engines in the VCE block are classified into type A and type B engines. Type A engines operate independently of the MP block, and type B engines operate in conjunction with the MP block.

#### 5. MIF (Memory Interface) Block

The MIF block arbitrates and controls DMA transfers between the MP, HIF, and VIF functional blocks. The following are the main types of DMA transfers provided.

- Data transfers with the MP DM (Data Memory). These are used for functions such as motion detection and compensation.

- Data transfers with the HIF HM (HIF Memory). These are used for bit stream data.

- Image data I/O transfers with VIF performed at fixed periods.

Requests for DMA transfers other than video I/O are issued with priorities assigned from the MP. Although VIF DMA transfers are performed with the highest priority (level 0), the transfer priority for other DMA transfers can be specified. Table 4 lists the types of priority level.

| Level   | Priority | Usage                   |  |  |  |  |  |  |  |  |

|---------|----------|-------------------------|--|--|--|--|--|--|--|--|

| Level 0 | High     | Only used for image I/O |  |  |  |  |  |  |  |  |

| Level 1 | <b> </b> | Programmable            |  |  |  |  |  |  |  |  |

| Level 2 | ] ↓      |                         |  |  |  |  |  |  |  |  |

| Level 3 | Low      |                         |  |  |  |  |  |  |  |  |

| Table 4. | Priority Lo | evel Types |

|----------|-------------|------------|

|----------|-------------|------------|

The MIF supports the four addressing modes listed below.

- 1) P+ : Consecutive access

- 2) Sag+ : Matrix access

- 3) RP+ : Ring buffer access

- 4) RP+DF : Ring buffer access with start address offset (every transfer)

MN1959041 provides two large-capacity DRAMs; working memory and frame memory. Working memory is mainly used for image compression and expansion, and frame memory is mainly used as the frame buffer used for VIF image output. Working memory is 16 Mbits of DRAM formed from four 4 Mbit DRAMs. Frame memory consists of a video buffer and a graphics buffer, each of which formed from a single 2 Mbit DRAM for a total of 2 DRAM chip. The operation frequency used is 53.76 MHz. Table 5 lists the internal DRAM structures and details of these memories.

#### Functional Description (continued)

5. MIF (Memory Interface) Block (continued)

Table 5. Internal DRAM Structure

|                | Work Memory          | Frame Memory                            |

|----------------|----------------------|-----------------------------------------|

| Capacity       | 16M-bit (4M-bit × 4) | 2 M-bit × 2                             |

| Bus width      | 16-bit               | 64-bit                                  |

| Transfer speed | 53.76 MHz            | 53.76 MHz                               |

| Use            | Used by the MP.      | Used by the VIF for video and graphics. |

#### 6. VIF (Video Interface) Block

MN1959041 includes the VIF block as the interface that passes image data between the IC and the image sensor and the LCD display.

The VIF input system provides functions for acquiring, at the stipulated frame rate, CIF or QCIF images sent from an external image sensor at 15 fps, and storing those images in working memory (internal DRAM) as object images for encoding.

The VIF output system provides functions for output of images encoded internally in the IC for LCD display at 60 fps. It also provides image size conversion from QCIF to CIF, mosquito noise elimination filter execution as required for QCIF images, functions for subscreen generation and display at lower right of the main screen, and a cursor display function.

In the VIF block, video images are processed in YCbCr format, and graphics images are processed in RGB format.

The VIF block supports two screen display modes. The first is a full-screen mode that displays all of the image data in the CIF size on the LCD, and the other is a window display mode in which an arbitrary part  $(176 \times 220)$  of the CIF size output from the VIF is displayed on the LCD. Actual output to the LCD is performed through the Visual ASIC block.

#### 7. Visual ASIC Block

The Visual ASIC block takes the video and graphics data output from the VIF block as input, synthesizes the final images, and adjusts the image. The features of the Visual ASIC block are listed below.

- IIC (Inter IC) interface (Conforms to Version 2.0, standard and fast mode)

- Video signal format conversion function (YCbCr 4:2:2  $\rightarrow$  RGB, can be stopped when not needed.)

- Graphics overlay function (Either post RGB conversion or post dithering can be selected.)

- Video signal adjustment functions: outline enhancement, tint, color gain, brightness, contrast, and gamma adjustment

- Dithering function for pseudo 24-bit color  $(2 \times 2 \text{ matrix})$

- Monochrome conversion function (Either monochrome or sepia can be specified.)

- Allows moving the display area (a 176-pixel × 220-line area placed anywhere within a 352-pixel × 288-line image)

- Provides a 4-format LCD connection interface.

- YCbCr 4:2:2 test image generation function (75% color bar, horizontal/vertical stripe, arbitrary brightness/color difference)

- Camera reset control function

# Functional Description (continued)

#### 8. DBC (Debug Controller) Block

MN1959041 provides its own debugging mode functions, and, when it is in HOLD mode, provides functions for reading and writing internal registers and memory, setting MP breakpoints, and other debugging operations. These functions can contribute to improved efficiency when debugging actual end products, and improved efficiency in system debugging.

The IC provides the following functions in debug mode.

- · Read and write operation to internal registers

- Read and write operation to internal memory spaces

- Read and write operation to internal DRAM

- Breakpoint setting functions

- PC value break

- DM1 address break

- DM2 address break

- GM address break

- CM address break

- PC trace function

- 1-bit trace

- 7-bit trace

- 9. Operating States and State Transition Control

MN1959041 has 4 operating states: RUN, HOLD, SLEEP, and WAIT.

RUN mode is the state where the program is executing, and HOLD mode is the state where program execution is stopped. SLEEP mode and WAIT mode are both program stopped states, but WAIT mode is a state that waits for the completion of specific processing (specified by the program) and switches to RUN mode automatically at the point completion is verified.

Of these four modes, HOLD mode can be used for program debugging, and allows the IC internal memory (instruction memory and data memory) to be read and written from external circuits.

The IC is started externally by clearing a reset applied with an external pin (the NVRST pin). After startup, the IC can be stopped and restarted with an external pin (the VHOLD pin).

The IC operating state can be observed from the VST[2:0] pins. Table 6 lists the processor states as indicated by these pins.

Always set the IC to HOLD mode before accessing internal resources when debugging. Operation is not guaranteed if resources are accessed in other modes.

|            |                                  | VST[2] | VST[1] | VST[0] |

|------------|----------------------------------|--------|--------|--------|

| RUN mode   |                                  | Low    | Low    | Low    |

| HOLD mode  | For the RUN to HOLD transition   | High   | Low    | Low    |

|            | For the SLEEP to HOLD transition | High   | High   | Low    |

|            | For the WAIT to HOLD transition  | High   | Low    | High   |

| SLEEP mode |                                  | Low    | High   | Low    |

| WAIT mode  |                                  | Low    | Low    | High   |

Table 6. Internal Operating States

# Pin Arrangement

|     | 16         | 15         | 14        | 13      | 12     | 11    | 10      | 9       | 8      | 7      | 6      | 5      | 4        | 3        | 2        | 1        |

|-----|------------|------------|-----------|---------|--------|-------|---------|---------|--------|--------|--------|--------|----------|----------|----------|----------|

| Т   |            |            | IN        | IN      | IN     | IN    | IN      | IN      | OUT    | OUT    | OUT    | OUT    | OUT      | OUT      |          |          |

| 1   | NC         | NC         | YD12      | YD15    | CD10   | CD13  | CD16    | NHDI    | CAMCK  | LRDO2  | LRDO5  | LGDO2  | LGDO5    | LBDO0    | NC       | NC       |

| D   |            |            | IN        | IN      | IN     | IN    | IN      | IN      | OUT    | OUT    | OUT    | OUT    | OUT      | OUT      |          |          |

| R   | NC         | NC         | YD11      | YD14    | YD17   | CD12  | CD15    | NVDI    | CIFRQ  | LRDO1  | LRDO4  | LGD01  | LGDO4    | LBDO1    | NC       | NC       |

| Р   | OUT        | OUT        | IN        | IN      | IN     | IN    | IN      | IN      | IN     | OUT    | OUT    | OUT    | OUT      | OUT      | OUT      | OUT      |

| r   | TEST7      | TEST8      | YD10      | YD13    | YD16   | CD11  | CD14    | CD17    | VCKI   | LRDO0  | LRDO3  | LGDO0  | LGDO3    | LBDO2    | LBDO3    | LBDO4    |

| Ν   | OUT        | OUT        | OUT       | GND     | GND    | GND   | GND     | GND     | 2.9 V    | OUT      | OUT      | OUT      |

| 14  | TEST6      | TEST5      | TEST4     | VSSDRAM | VSS    | VSS   | VSSDRAM | VSSDRAM | VDDH   | VDDH   | VDDH   | VDDH   | VDDH     | LBDO5    | LVCKO    | VFLG     |

| М   | OUT        | OUT        | OUT       | GND     | GND    |       |         |         |        |        |        | 2.9 V  | 2.9 V    | OUT      | OUT      | OUT      |

| 141 | TEST3      | TEST2      | TEST1     | VSS     | VSS    | NC    | NC      | NC      | NC     | NC     | NC     | VDDH   | VDDH     | NLVSYNCO | NLHSYNCO | LVVALIDO |

| L   | IN         | IN         | IN        | GND     |        |       |         |         |        |        |        |        | 2.9 V    | 2.9 V    | OUT      | OUT      |

| L   | TESTMODE3  | TESTMODE2  | TESTMODE1 | VSS     | NC     | NC    | NC      | NC      | NC     | NC     | NC     | NC     | VDDH     | VDDH     | LHVALIDO | NYRESETO |

| К   | IN         | IN         | GND       | GND     |        |       |         |         |        |        |        |        | 2.9 V    | 2.9 V    | OUT      | OUT      |

| ĸ   | TESTMODE0  | TESTER     | VSS       | VSSDRAM | NC     | NC    | NC      | NC      | NC     | NC     | NC     | NC     | VDDH     | VDDH     | PO0      | PO1      |

| J   | IN         | IN         | GND       | GND     |        |       |         |         |        |        |        |        | 2.9 V    | 2.9 V    | IN/OUT   | IN       |

| 5   | NTDRAM     | PTESTDRAMI | VSS       | VSS     | NC     | NC    | NC      | NC      | NC     | NC     | NC     | NC     | VDDH     | VDDH     | I2CSD    | I2CSCKI  |

| н   | IN         | IN         | 2.9 V     | GND     |        |       |         |         |        |        |        |        | 3.3 V    | 3.3 V    | IN       | IN       |

|     | PTESTDRAMO | PSCMR      | AVDD      | AVSS    | NC     | NC    | NC      | NC      | NC     | NC     | NC     | NC     | VDDDRAMH | VDDDRAMH | PI0      | PI1      |

| G   | IN         | IN         | GND       | GND     |        |       |         |         |        |        |        |        | 3.3 V    | 1.8 V    | IN       | IN       |

| 0   | VCOI       | MINTEST    | VSS       | VSS     | NC     | NC    | NC      | NC      | NC     | NC     | NC     | NC     | VDDDRAMH | VDDDRAM  | NVCS     | VA0      |

| F   | IN         | IN         | GND       | GND     |        |       |         |         |        |        |        |        | 1.8 V    | 1.8 V    | IN       | IN       |

|     | CFO        | VMCK       | VSS       | VSS     | NC     | NC    | NC      | NC      | NC     | NC     | NC     | NC     | VDDDRAM  | VDDDRAM  | VA1      | VA2      |

| Е   | IN         | IN         | IN        | GND     | GND    |       |         |         |        |        |        | 1.8 V  | 1.8 V    | IN       | IN       | IN       |

| _   | NPLLRST    | PLLEN      | NPLLEN    | VSS     | VSS    | NC    | NC      | NC      | NC     | NC     | NC     | VDD    | VDDDRAM  | VA3      | VA4      | VA5      |

| D   | IN         | IN         | OUT       | GND     | GND    | GND   | GND     | GND     | 1.8 V    | IN       | IN       | IN       |

| _   | NYGCMD     | VTSTMD     | VTDO      | VSS     | VSS    | VSS   | VSS     | VSS     | VDD    | VDD    | VDD    | VDD    | VDD      | VA6      | VA7      | VA8      |

| С   | IN/OUT     | IN/OUT     | IN/OUT    | IN      | IN     | IN    | IN/OUT  | IN/OUT  | IN/OUT | IN/OUT | IN/OUT | IN/OUT | IN/OUT   | IN       | IN       |          |

| 0   | VTRWEN     | VTDI       | VTCK      | NVBTRO  | NVIRQ0 | NVWE1 | VPIO3   | VPIO0   | VD13   | VD10   | VD7    | VD4    | VD1      | VA10     | VA9      | NC       |

| В   |            |            | OUT       | IN      | IN     | IN    | OUT     | IN/OUT  | IN/OUT | IN/OUT | IN/OUT | IN/OUT | IN/OUT   | IN       |          |          |

| 5   | NC         | NC         | VST2      | VHOLD   | NVIRQ1 | NVRE  | TEST0   | VPIO1   | VD14   | VD11   | VD8    | VD5    | VD2      | VA11     | NC       | NC       |

| А   |            |            | OUT       | OUT     | IN     | IN    | IN      | IN/OUT  | IN/OUT | IN/OUT | IN/OUT | IN/OUT | IN/OUT   | IN/OUT   |          |          |

|     | NC         | NC         | VST1      | VST0    | NVNMI  | NVRST | NVWE0   | VPIO2   | VD15   | VD12   | VD9    | VD6    | VD3      | VDO      | NC       | NC       |

# Pin Descriptions

| Pin        | I/O   |                | Description                                                                         | Normal<br>usage |

|------------|-------|----------------|-------------------------------------------------------------------------------------|-----------------|

| YDI[7:0]   | Ι     | Video input    | Luminance data input                                                                |                 |

| CDI[7:0]   | Ι     |                | Color difference input                                                              |                 |

| NVDI       | Ι     |                | Vertical sync signal                                                                |                 |

| NHDI       | Ι     |                | Horizontal sync signal                                                              |                 |

| VCKI       | Ι     |                | Input system video clock (2.250 MHz)                                                |                 |

| CIFRQ      | 0     |                | CIF size request signal                                                             |                 |

| CAMCK      | 0     |                | Camera block operating clock (9.000 MHz)                                            |                 |

| VFLG       | 0     | Video output   | MMP1 output frame update flag                                                       |                 |

| I2CSCKI    | Ι     |                | I2C interface serial clock input                                                    |                 |

| I2CSD      | I/O/Z |                | I2C interface serial data I/O                                                       |                 |

| LRDO[5:0]  | 0     |                | Red data<br>(Outputs the MMP1 YDO[7:2] bits in V-ASIC through mode.)                |                 |

| LGDO[5:0]  | 0     |                | Green data<br>(Outputs the MMP1 YDO[1:0] and CDO[7:4] bits in V-ASIC through mode.) |                 |

| LBDO[5:0]  | 0     |                | Blue data<br>(Outputs the MMP1 CDO[3:0] and 2'b00 bits in V-ASIC through mode.)     |                 |

| NLVSYNCO   | 0     |                | Vertical sync signal                                                                |                 |

| NLHSYNCO   | 0     |                | Horizontal sync signal                                                              |                 |

| LVVALIDO   | 0     |                | Vertical data valid flag                                                            |                 |

| LHVALIDO   | 0     |                | Horizontal data valid flag                                                          |                 |

| LVCKO      | 0     |                | Output system video clock (9.000 MHz)                                               |                 |

| PI[1:0]    | Ι     |                | General-purpose input port                                                          |                 |

| PO[1:0]    | 0     |                | General-purpose output port                                                         |                 |

| NVRESETO   | 0     |                | Camera vertical sync and horizontal sync output reset signal                        |                 |

| NVCS       | Ι     | Host interface | Chip enable from the MMP-C                                                          |                 |

| VA[11:0]   | Ι     |                | Input address bus from the MMP-C                                                    |                 |

| VD[15:0]   | I/O/Z |                | I/O data bus from the MMP-C                                                         | Pull Up         |

| NVWE[1:0]  | Ι     |                | Write enable from the MMP-C                                                         |                 |

| NVRE       | Ι     |                | Read enable from the MMP-C                                                          |                 |

| VPIO[3:0]  | I/O   |                | Parallel I/O with the MMP-C                                                         | Pull Up         |

| TEST0      | 0     |                | Contention access signal between the MP and the MMP-C to the HM.                    | NC              |

| NVIRQ[1:0] | Ι     | Misc           | Maskable interrupt request signal from the MMP-C                                    | Pull Up         |

| NVNMI      | Ι     |                | Nonmaskable interrupt request from the MMP-C                                        | Pull Up         |

| NVRST      | Ι     |                | MMP-V reset request signal from the MMP-C                                           |                 |

| NVBTRQ     | Ι     |                | Boot request at MMP-V reset clear                                                   |                 |

| VHOLD      | Ι     |                | MMP-V hold signal from the MMP-C                                                    |                 |

| VST[2:0]   | 0     |                | MMP-V operating state signals to the MMP-C                                          |                 |

# ■ Pin Descriptions (continued)

| Pin        | I/O   |                     | Description                                                                                     | Normal<br>usage |

|------------|-------|---------------------|-------------------------------------------------------------------------------------------------|-----------------|

| VTCK       | I/O/Z | Debugging interface | Debugging clock<br>PC value serial output clock (VTCK pin shared function)                      | Low             |

| VTDI       | I/O/Z |                     | Serial debugging data input<br>PC value serial output start bit flag (VTDI pin shared function) | Low             |

| VTDO       | 0     |                     | Serial debugging data output<br>PC value serial output                                          |                 |

| VTRWEN     | I/O/Z |                     | Serial debugging data I/O enable<br>PC value increment flag (VTRWEN pin shared function)        | Low             |

| NVGCMD     | Ι     |                     | MMP-V internal 54 MHz clock gated mode setting                                                  | Low             |

| VTSTMD     | Ι     |                     | TEST pin output mode setting                                                                    | Low             |

| TEST1      | 0     |                     | MMP-V internal VIF signal debugging output or<br>PC value [1] output                            | NC              |

| TEST2      | 0     |                     | MMP-V internal VIF signal debugging output or<br>PC value [2] output                            | NC              |

| TEST3      | 0     |                     | MMP-V internal VIF signal debugging output or<br>PC value [3] output                            | NC              |

| TEST4      | 0     |                     | MMP-V internal VIF signal debugging output or<br>PC value [4] output                            | NC              |

| TEST5      | 0     |                     | MMP-V internal VIF signal debugging output or<br>PC value [5] output                            | NC              |

| TEST6      | 0     |                     | MMP-V internal VIF signal debugging output or<br>PC value [6] output                            | NC              |

| TEST7      | 0     |                     | MMP-V internal MIF signal debugging output                                                      | NC              |

| TEST8      | 0     |                     | MMP-V internal MIF signal debugging output                                                      | NC              |

| MINTEST    | Ι     | Test mode           | Buffer test control input                                                                       | Low             |

| TESTER     | Ι     |                     | Normal mode/test mode switching                                                                 | Low             |

| TESTMODE0  | Ι     |                     | Test mode setting                                                                               | Low             |

| TESTMODE1  | Ι     |                     | Test mode setting                                                                               | Low             |

| TESTMODE2  | Ι     |                     | Test mode setting                                                                               | Low             |

| TESTMODE3  | Ι     |                     | Test mode setting                                                                               | Low             |

| PTESTDRAM0 | Ι     |                     | DRAM test mode setting 0                                                                        | Low             |

| PTESTDRAM1 | Ι     |                     | DRAM test mode setting 1                                                                        | Low             |

| NTDRAM     | Ι     |                     | Normal mode/shift mode switching during DRAM scan testing                                       | Low             |

#### Pin Descriptions (continued)

| Pin      | I/O |              | Description                                                          | Normal<br>usage |

|----------|-----|--------------|----------------------------------------------------------------------|-----------------|

| VMCK     | Ι   | PLL          | MMP-V operation reference clock (input to the PLL)                   | 76.8 KHz        |

| NPLLEN   | Ι   |              | MMP1 internal operating clock selection                              | Low             |

| PLLEN    | Ι   |              | Selection of the clock input the MMP1 internal divide-by-two circuit | High            |

| NPLLRST  | Ι   |              | MMP-V internal PLL reset                                             | High            |

| VCOI     | Ι   |              | VCO analog voltage input                                             |                 |

| AVDD     |     |              | PLL power supply: +2.9 V                                             | 2.9 V           |

| AVSS     |     |              | PLL ground                                                           | AVSS            |

| CFO      |     | Power supply | Test pin                                                             | High            |

| PSCMR    | Ι   |              | Test pin                                                             | High            |

| VDDH     |     |              | Power supply: +2.9 V                                                 | 2.9 V           |

| VDD      |     |              | Power supply: +1.8 V                                                 | 1.8 V           |

| VSS      |     |              | Ground                                                               | DGND            |

| VDDDRAMH |     |              | DRAM power supply: +3.3 V                                            | 3.3 V           |

| VDDDRAM  |     |              | DRAM power supply: +1.8 V                                            | 1.8 V           |

| VSSDRAM  |     |              | DRAM ground                                                          | GND             |

| PVBBDRAM |     |              | P detection substrate power supply monitor output                    |                 |

| PVBPDRAM |     |              | P detection test bit line precharge power supply monitor output      |                 |

#### Electrical Characteristics

#### 1. Absolute Maximum Ratings at $V_{SS} = 0 V$

| Parameter                      | Symbol           | Rating                                           | Unit |

|--------------------------------|------------------|--------------------------------------------------|------|

| External supply voltage *      | V <sub>DD</sub>  | – 0.3 to +4.6                                    | V    |

| Internal supply voltage *      | V <sub>DDI</sub> | - 0.3 to +2.5                                    | V    |

| Input pin voltage              | VI               | -0.3 to V <sub>DD</sub> + 0.3 (Upper limit: 4.6) | V    |

| Output pin voltage             | Vo               | -0.3 to V <sub>DD</sub> + 0.3 (Upper limit: 4.6) | V    |

| Output current (Type HL4 pins) | I <sub>O</sub>   | ±20                                              | mA   |

| Power supply input current     | I <sub>V</sub>   | ±70 (Per pin)                                    | mA   |

| Power dissipation              | P <sub>D</sub>   | 1.77                                             | mW   |

| Operating temperature          | T <sub>opr</sub> | -20 to +70                                       | °C   |

| Storage temperature            | T <sub>stg</sub> | -55 to +150                                      | °C   |

Note) 1. \*: When one of VDD and VDDI is off and the other on, through currents flow and the outputs will be undefined. There are no stipulation on the power on and power off sequences. The power supply levels should be applied as close to simultaneously as possible. However, this does no apply when CFO is controlled.

- 2. Type HL4 pins: CIFRQ, CAMCK, VFLG, I2CSD, LRDO[0] to LRDO[5], LGDO[0] to LGDO[5], LBDO[0] to LBDO[5], NLVSYNCO, NLHSYNCO, LVVALIDO, LHVALIDO, LVCKO, PO[0], PO[1], NVRESRTO, VD[0] to VD[15], VPIO[0] to VPIO[3], VST[0] to VST[2], VTCK, VTDI, VTDO, VTRWEN, TEST[0] to TEST[8]

- 3. The absolute maximum ratings are limit values for stresses applied to the chip so that the chip will not be destroyed. Functional operation is not guaranteed over the complete span of these ranges.

- 4. All of the VDD and VSS pins must be connected directly to their corresponding power supply and ground levels.

# 2. Recommended Operating Conditions at $V_{SS} = 0 V$

| Parameter                   | Symbol             | Conditions | Min  | Тур | Max  | Unit |

|-----------------------------|--------------------|------------|------|-----|------|------|

| External supply voltage     | V <sub>DD</sub>    |            | 2.7  | 2.9 | 3.1  | V    |

| Internal supply voltage     | V <sub>DDI</sub>   |            | 1.65 | 1.8 | 1.95 | V    |

| DRAM supply voltage         | V <sub>DD18D</sub> |            | 1.65 | 1.8 | 1.95 | V    |

| DRAM step-up supply voltage | V <sub>DD33D</sub> |            | 3.0  | 3.3 | 3.6  | V    |

| Analog supply voltage       | AV <sub>DD</sub>   |            | 2.7  | 2.9 | 3.1  | V    |

| Ambient temperature         | Ta                 |            | -20  | _   | 70   | °C   |

#### 3. I/O Capacitances

| Parameter   | Symbol           | Conditions                       | Min | Тур | Max | Unit |

|-------------|------------------|----------------------------------|-----|-----|-----|------|

| Input pins  | C <sub>IN</sub>  | $V_{DD} = V_{DDI} = V_I = 0 V$   | —   | 7   | 8   | pF   |

| Output pins | C <sub>OUT</sub> | $f = 1$ MHz, $T_a = 25^{\circ}C$ | _   | 7   | 8   | pF   |

| I/O pins    | C <sub>IO</sub>  |                                  | _   | 7   | 8   | pF   |

# 4. DC Characteristics at V<sub>DD</sub> = 2.7 V to 3.1 V, V<sub>DDI</sub> = 1.65 V to 1.95 V, V<sub>SS</sub> = 0 V, $f_{TEST}$ = 54 MHz, $T_a$ = -20°C to +70°C

| Parameter                                                                     | Symbol            | Conditions                                                                                                                                                                                                                              | Min | Тур | Max  | Unit |

|-------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I/O power supply operating supply current                                     | I <sub>DDO</sub>  | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 54 \text{ MHz}, V_{DD} = 2.9 \text{ V}, \\ V_{DDI} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                              |     | 4   | 12.0 | mA   |

| Internal power supply operation supply current                                | I <sub>ddio</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 54 \text{ MHz}, V_{DD} = 2.9 \text{ V}, \\ V_{DDI} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                              |     | 50  | 85.0 | mA   |

| DRAM 3.3 V power supply<br>operating supply<br>current (Normal mode) *        | I <sub>DDDO</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 54 \text{ MHz}, V_{DD} = 2.9 \text{ V}, \\ V_{DDI} &= 1.8 \text{ V}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$ |     | 0.3 | 2.0  | mA   |

| DRAM 3.3 V power supply<br>operating supply current<br>(Standby test mode)    | I <sub>DDDO</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 30 \text{ MHz}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                      | —   | 0.3 | 4.1  | mA   |

| DRAM 3.3 V power supply<br>operating supply current<br>(Dynamaic test mode)   | I <sub>DDDO</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 30 \text{ MHz}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                      | —   | 1.3 | 5.7  | mA   |

| DRAM 3.3 V power supply<br>operating supply current<br>(Page mode test mode)  | I <sub>DDDO</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 30 \text{ MHz}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                      |     | 0.1 | 5.0  | mA   |

| DRAM 3.3 V power supply<br>operating supply current<br>(Self refre test mode) | I <sub>DDDO</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 30 \text{ MHz}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                      |     | 0.3 | 4.4  | mA   |

Note) \*: Design value

4. DC Characteristics at  $V_{DD}$  = 2.7 V to 3.1 V,  $V_{DDI}$  = 1.65 V to 1.95 V,  $V_{SS}$  = 0 V,  $f_{TEST}$  = 54 MHz,  $T_a$  = -20°C to +70°C (continued)

| Parameter                                                                        | Symbol             | Conditions                                                                                                                                                                                                                              | Min | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| DRAM internal power supply<br>operating supply current<br>(Normal mode) *        | I <sub>dddio</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 54 \text{ MHz}, V_{DD} = 2.9 \text{ V}, \\ V_{DDI} &= 1.8 \text{ V}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$ |     | 6.0  | 12.0 | mA   |

| DRAM internal power supply<br>operating supply current<br>(Standby test mode)    | I <sub>dddio</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 30 \text{ MHz}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                      |     | 3.0  | 10.0 | mA   |

| DRAM internal power supply<br>operating supply current<br>(Dynamaic test mode)   | I <sub>dddio</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 30 \text{ MHz}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                      | —   | 25.0 | 50.0 | mA   |

| DRAM internal power supply<br>operating supply current<br>(Page mode test mode)  | I <sub>dddio</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 30 \text{ MHz}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                      |     | 25.0 | 50.0 | mA   |

| DRAM internal power supply<br>operating supply current<br>(Self refre test mode) | I <sub>dddio</sub> | $\begin{split} V_I &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 30 \text{ MHz}, V_{DDDRAMH} = 3.3 \text{ V}, \\ V_{DDDRAM} &= 1.8 \text{ V}, \text{ outputs open} \end{split}$                                                        | _   | 3.0  | 15.0 | mA   |

| Analog power supply operating supply current                                     | I <sub>DDAO</sub>  | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} ,\\ \text{fin} &= 76.8 \text{ kHz}, V_{DD} = 2.9 \text{ V},\\ V_{DDI} &= 1.8 \text{ V}, \text{ AV}_{DD} = 2.9 \text{ V},\\ \text{outputs open} \end{split}$                           |     | 0.5  | 1.0  | mA   |

| I/O power supply quiescent supply current                                        | I <sub>DDQO</sub>  | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} , \\ f &= 0 \text{ MHz}, V_{DD} = 2.9 \text{ V}, \\ V_{DDI} &= 1.8 \text{ V}, \text{ AV}_{DD} = 2.9 \text{ V}, \\ \text{outputs open} \end{split}$                                    |     | 1    | 20.0 | μΑ   |

| Analog power supply quiescent supply current                                     | I <sub>ddqao</sub> | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ \text{fin} &= 0 \text{ kHz},  V_{DD} = 2.9 \text{ V}, \\ V_{DDI} &= 1.8 \text{ V},  \text{AV}_{DD} = 2.9 \text{ V}, \\ \text{outputs open} \end{split}$                  |     | 1    | 20.0 | μΑ   |

Note) \*: Design value.

Output leakage current

PLL oscillator frequency

# Electrical Characteristics (continued)

| 4. DC Characteristics at $v_{DD} = 2.7 v$                                                                         | 10 3.1 V, V         | $DDI = 1.05 \text{ v}$ to 1.95 v, $v_{SS} = 0 \text{ v}$ , 1                        | TEST = 34 IVI       | $12, 1_a = -20$ |                     | continueu) |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------|---------------------|-----------------|---------------------|------------|--|--|--|--|

| Parameter                                                                                                         | Symbol              | Conditions                                                                          | Min                 | Тур             | Max                 | Unit       |  |  |  |  |

|                                                                                                                   | VNMI, N<br>MODE[3], | )], PI[1], NVCS, VA[0] to VA<br>VRST, NVBTRQ, VHOLD, N<br>, PTESTDRAM[0], PTESTDR   | VGCMD, V            | TSTMD,          | TESTER,             |            |  |  |  |  |

| High-level input voltage                                                                                          | V <sub>IH</sub>     |                                                                                     | $V_{DD} \times 0.7$ |                 | V <sub>DD</sub>     | V          |  |  |  |  |

| Low-level input voltage                                                                                           | V <sub>IL</sub>     |                                                                                     | 0                   |                 | $V_{DD} \times 0.3$ | V          |  |  |  |  |

| Input leakage current                                                                                             | I <sub>LI</sub>     | $V_{I} = V_{DD}$ or $V_{SS}$                                                        | —                   | —               | ±10                 | μΑ         |  |  |  |  |

| 2) LVCMOS level inputs with pull-down resistors:<br>YDI[0] to YDI[7], CDI[0] to CDI[7], NVDI, NHDI, VCKI, MINTEST |                     |                                                                                     |                     |                 |                     |            |  |  |  |  |

| High-level input voltage                                                                                          | V <sub>IH</sub>     |                                                                                     | $V_{DD} 	imes 0.7$  |                 | V <sub>DD</sub>     | V          |  |  |  |  |

| Low-level input voltage                                                                                           | V <sub>IL</sub>     |                                                                                     | 0                   |                 | $V_{DD} \times 0.3$ | V          |  |  |  |  |

| Pull-down resistance                                                                                              | R <sub>IL</sub>     | $V_I = V_{DD}$                                                                      | 10                  | 30              | 90                  | kΩ         |  |  |  |  |

| Output leakage current                                                                                            | I <sub>LIL</sub>    | $V_I = V_{SS}$                                                                      | —                   | —               | ±10                 | μΑ         |  |  |  |  |

|                                                                                                                   | LVSYNC              | MCK, VFLG, I2CSD, LRDO[(<br>D, NLHSYNCO, LVVALIDO,<br>IO[0] to VPIO[3], VST[0] to V | LHVALID             | O, LVCK         | O, PO[0], P         | O[1],      |  |  |  |  |

| High-level input voltage                                                                                          | V <sub>IH</sub>     |                                                                                     | $V_{DD} \times 0.7$ |                 | V <sub>DD</sub>     | V          |  |  |  |  |

| Low-level input voltage                                                                                           | V <sub>IL</sub>     |                                                                                     | 0                   |                 | $V_{DD} \times 0.3$ | V          |  |  |  |  |

| High-level output voltage                                                                                         | V <sub>OH</sub>     | $I_{OH} = 4.0 \text{ mA},$<br>$V_I = V_{DD} \text{ or } V_{SS}$                     | $V_{DD} \times 0.8$ | _               | V <sub>DD</sub>     | V          |  |  |  |  |

| Low-level output voltage                                                                                          | V <sub>OL</sub>     | $I_{OL} = 4.0 \text{ mA},$<br>V <sub>I</sub> = V <sub>DD</sub> or V <sub>SS</sub>   | 0                   |                 | $V_{DD} \times 0.2$ | V          |  |  |  |  |

|                                                                                                                   |                     |                                                                                     |                     |                 |                     |            |  |  |  |  |

$V_0$  = High-impedance state,

$$\begin{split} V_{DD} &= 2.9 \ V, \ V_{DDI} = 1.8 \ V, \\ AV_{DD} &= 2.9 \ V, \ R_2 = 390 \ \Omega, \\ C_1 &= 1.0 \ \mu F, \ C_2 = 0.047 \ \mu F \end{split}$$

$V_{I} = V_{DD} \text{ or } V_{SS}$  $V_{D} = V_{DD} \text{ or } V_{SS}$  $F_{IN} = 76.8 \text{ kHz},$

$I_{\text{LO}}$

Fosc

$\pm 10$

\_\_\_\_

53.76

μΑ

MHz

#### 5. AC Characteristics

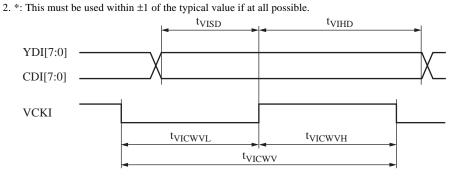

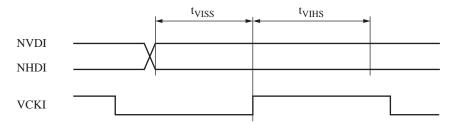

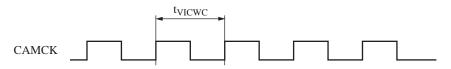

### 1) Video input interface timing

| Parameter                                      | Symbol              | Conditions                                          | Min | Тур | Max | Unit  |

|------------------------------------------------|---------------------|-----------------------------------------------------|-----|-----|-----|-------|

| Video Input Timing                             |                     |                                                     |     |     |     |       |

| YC data setup time from the VCKI rising edge * | t <sub>VISD</sub>   | $V_{I} = V_{DD} \text{ or } V_{SS},$<br>f = 54 MHz, | 1   | 12  |     | cycle |

| YC data hold time from the VCKI rising edge *  | t <sub>VIHD</sub>   | $V_{DD} = 2.9 V,$<br>$V_{DDI} = 1.8 V$              | 5   | 12  |     | cycle |

| VCKI low-level period                          | t <sub>VICWVL</sub> |                                                     | —   | 12  | —   | cycle |

| VCKI high-level period                         | t <sub>VICWVH</sub> |                                                     | —   | 12  | —   | cycle |

| VCKI frequency                                 | t <sub>VICWV</sub>  |                                                     | —   | 24  | —   | cycle |

| Sync setup time from the VCKI rising edge *    | t <sub>VISS</sub>   |                                                     | 2   | 12  |     | cycle |

| Sync hold time from the VCKI rising edge *     | t <sub>VIHS</sub>   |                                                     | 3   | 12  |     | cycle |

| CAMCK output frequency                         | t <sub>VICWC</sub>  |                                                     | _   | 6   |     | cycle |

Note) 1. The stipulated values that follow are all design values. Note that the unit "cycle" in the table refers to one clock period of internal operating frequency.

#### Figure 1. YC data input timing

Figure 2. Vsync and Hsync input timing

Figure 3. CAMCK output timing

- 5. AC Characteristics (continued)

- 2) Video output interface timing

| Parameter                                                                 | Symbol              | Conditions                            | Min   | Тур   | Max   | Unit |

|---------------------------------------------------------------------------|---------------------|---------------------------------------|-------|-------|-------|------|

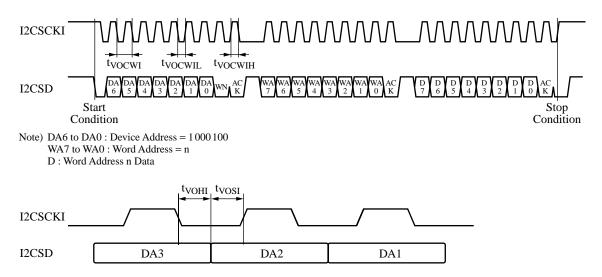

| Video Output Timing                                                       |                     |                                       |       |       |       |      |

| I2CSCKI cycle time                                                        | t <sub>VOCWI</sub>  | $V_{I} = V_{DD} \text{ or } V_{SS}$ , | 2.5   | 10    | _     | μs   |

| I2CSCKI high-level pulse width                                            | t <sub>VOCWIH</sub> | f = 54 MHz,                           | 0.6   | 4.0   | —     | μs   |

| I2CSCKI low-level pulse width                                             | t <sub>VOCWIL</sub> | $V_{DD} = 2.9 V,$                     | 1.3   | 4.7   | —     | μs   |

| I2CSD setup time                                                          | t <sub>VOSI</sub>   | V <sub>DDI</sub> = 1.8 V              | 250   |       | _     | ns   |

| I2CSD hold time                                                           | t <sub>VOHI</sub>   |                                       | 300   |       | —     | ns   |

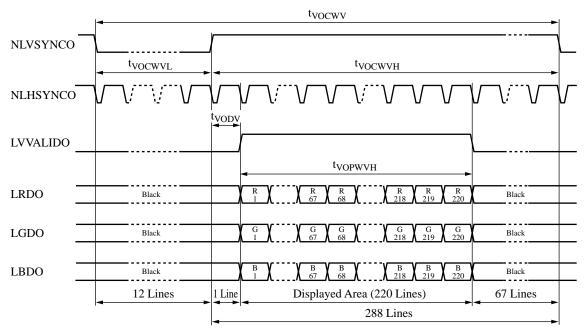

| NLVSYNCO cycle time                                                       | t <sub>VOCWV</sub>  |                                       | 16.7  | 16.7  | 16.7  | ms   |

| NLVSYNCO high-level pulse width                                           | t <sub>VOCWVH</sub> |                                       | 16    | 16    | 16    | ms   |

| NLVSYNCO low-level pulse width                                            | t <sub>VOCWVL</sub> |                                       | 665.7 | 666.7 | 667.7 | μs   |

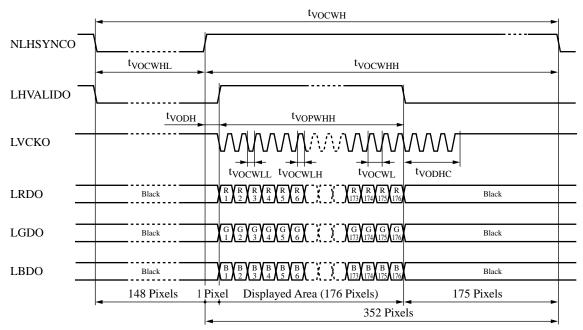

| NLHSYNCO cycle time                                                       | t <sub>VOCWH</sub>  |                                       | 54.6  | 55.6  | 56.6  | μs   |

| NLHSYNCO high-level pulse width                                           | t <sub>VOCWHH</sub> |                                       | 38.1  | 39.1  | 40.1  | μs   |

| NLHSYNCO low-level pulse width                                            | t <sub>VOCWHL</sub> |                                       | 15.4  | 16.4  | 17.4  | μs   |

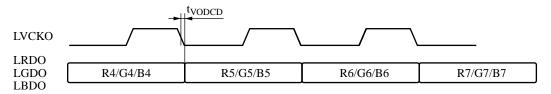

| LVCKO cycle time                                                          | t <sub>VOCWL</sub>  |                                       | 80    | 111   | 140   | ns   |

| LVCKO high-level pulse width                                              | t <sub>VOCWLH</sub> |                                       | 40    | 55    | 70    | ns   |

| LVCKO low-level pulse width                                               | t <sub>VOCWLL</sub> |                                       | 40    | 55    | 70    | ns   |

| Delay time from the NLVSYNCO rising edge to the LVVALIDO rising edge      | t <sub>VODV</sub>   |                                       | 0     | —     | 3.78  | ms   |

| LVVALIDO high-level pulse width                                           | t <sub>VOPWVH</sub> |                                       | 12.2  | 12.2  | 12.2  | ms   |

| Delay time from the NLHSYNCO rising edge to the LHVALIDO rising edge      | t <sub>VODH</sub>   |                                       | 0     | _     | 19.6  | μs   |

| LHVALIDO high-level pulse width                                           | t <sub>VOPWHH</sub> |                                       | 19.54 | 19.65 | 19.76 | μs   |

| Delay time from the LHVALIDO falling<br>edge to the point the LVCKO stops | t <sub>VODHC</sub>  |                                       | 1.67  | 1.78  | 1.89  | μs   |

| Delay time from the LVCKO falling<br>edge to LRDO, LGDO, and LBDO         | t <sub>VODCD</sub>  |                                       | 0     |       | 9.25  | ns   |

- 5. AC Characteristics (continued)

- 2) Video output interface timing (continued)

Figure 4. Random write timing

Note) When V\_POS = 1, line 0 and lines 221 to 287 will be filled with black in the LCD RGB, and only lines 1 to 220 will be output.

Figure 5. Vertical timing (When  $V_{POS} = 1$ )

- Electrical Characteristics (continued)

- 5. AC Characteristics (continued)

- 2) Video output interface timing (continued)

Note) When H\_POS = 1, pixel 0 and pixels 177 to 351 will be filled with black in the LCD RGB, and only pixels 1 to 176 will be output.

Figure 6. Horizontal timing (When  $V_{POS} = 1$ )

# 5. AC Characteristics (continued)

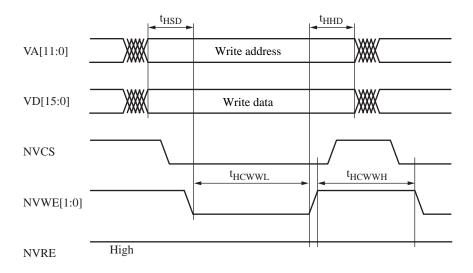

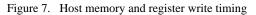

# 3) Host interface timing

| Parameter                                                         | Symbol             | Conditions                                                                                                                                   | Min | Тур | Max | Unit  |

|-------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Host Memory and Register Access T                                 | iming              |                                                                                                                                              |     |     |     |       |

| Address and data setup time<br>after NVCS and NVWE[1:0]<br>go low | t <sub>HSD</sub>   | $\begin{split} V_{I} &= V_{DD} \text{ or } V_{SS} \text{ ,} \\ f &= 54 \text{ MHz} \text{,} \\ V_{DD} &= 2.9 \text{ V} \text{,} \end{split}$ | 0   |     |     | cycle |

| Period that NVCS and NVWE[1:0] are both low                       | t <sub>HCWWL</sub> | $V_{DDI} = 1.8 V$                                                                                                                            | 4   | 5   |     | cycle |

| Address and data hold time after<br>NVCS and NVWE[1:0] go low     | t <sub>HHD</sub>   |                                                                                                                                              | 0   |     |     | cycle |

| Period that NVCS and NVWE[1:0] are both high                      | t <sub>HCWWH</sub> |                                                                                                                                              | 1   | 2   |     | cycle |

| Address setup time after NVCS<br>and NVRE are both low            | t <sub>HSR</sub>   |                                                                                                                                              | 0   |     |     | cycle |

| Period that NVCS and NVRE go low                                  | t <sub>HCWRL</sub> |                                                                                                                                              | 5   | 5.5 |     | cycle |

| Address hold time after NVCS and NVRE go low                      | t <sub>HHA</sub>   |                                                                                                                                              | 0   |     |     | cycle |

| Period that NVCS and NVRE are both high                           | t <sub>HCWRH</sub> |                                                                                                                                              | 1   | 1.5 |     | cycle |

| Data output delay time after NVCS<br>and NVRE go low              | t <sub>HDD</sub>   |                                                                                                                                              | _   |     | 4   | cycle |

| Data hold time after NVCS and NVRE go high                        | t <sub>HHD</sub>   |                                                                                                                                              | _   |     | 1   | cycle |

- Electrical Characteristics (continued)

- 5. AC Characteristics (continued)

- 3) Host interface timing (continued)

Figure 8. Host memory and register read timing

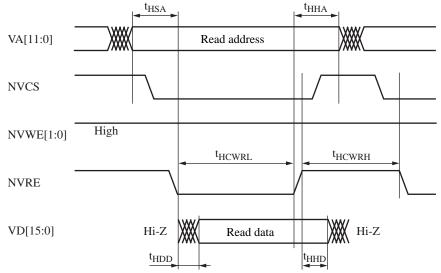

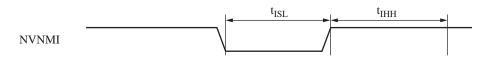

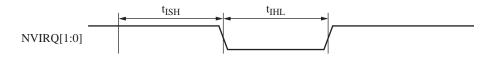

#### 4) Interrupt input timing

| Parameter                                         | Symbol           | Conditions                                          | Min | Тур | Max | Unit  |

|---------------------------------------------------|------------------|-----------------------------------------------------|-----|-----|-----|-------|

| Interrupt Input Timing                            |                  |                                                     |     |     |     |       |

| Low-level setup time after an NVNMI rising edge   | t <sub>ISL</sub> | $V_{I} = V_{DD} \text{ or } V_{SS},$<br>f = 54 MHz, | 3   | 6   |     | cycle |

| High-level hold time after an NVNMI rising edge   | t <sub>IHH</sub> | $V_{DD} = 2.9 V,$<br>$V_{DDI} = 1.8 V$              | 3   | 6   |     | cycle |

| High-level setup time after an NVIRQ falling edge | t <sub>ISH</sub> |                                                     | 3   | 6   |     | cycle |

| Low-level hold time after an NVIRQ falling edge   | t <sub>IHL</sub> |                                                     | 3   | 6   |     | cycle |

Figure 9. NVNMI interrupt input timing

Figure 10. NVNMI interrupt input timing

- 5. AC Characteristics (continued)

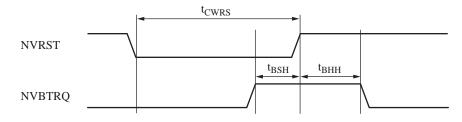

- 5) Reset and boot timing

| Parameter                                                            | Symbol            | Conditions                                                                | Min  | Тур   | Max | Unit  |

|----------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------|------|-------|-----|-------|

| Reset and Boot Timing                                                |                   |                                                                           |      |       |     |       |

| Reset low-level period                                               | t <sub>CWRS</sub> | $V_{I} = V_{DD} \text{ or } V_{SS}$ ,                                     | 6000 | 6000< |     | cycle |

| Boot request high-level<br>setup time after<br>the reset rising edge | t <sub>BSH</sub>  | $f = 54 \text{ MHz},$ $V_{DD} = 2.9 \text{ V},$ $V_{DDI} = 1.8 \text{ V}$ | 3    | 3<    |     | cycle |

| Boot request high-level<br>hold time after<br>the reset rising edge  | t <sub>BHH</sub>  |                                                                           | 3    | 3<    |     | cycle |

Figure 11. Reset and boot timing

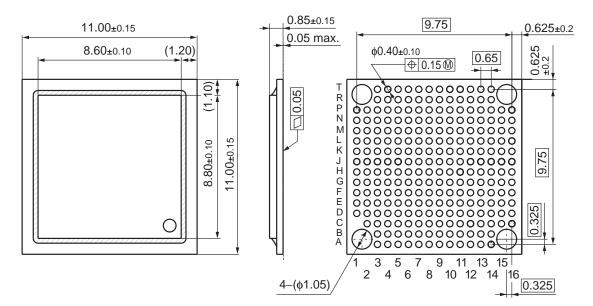

- Package Dimensions (Units: mm)

- MLGA239-C-1111 (lead free)

# Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this material are subject to change without notice for reasons of modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.

- (6) When using products for which dry packing is required, observe the conditions (including shelf life and after-unpacking standby time) agreed upon when specification sheets are individually exchanged.

- (7) No part of this material may be reprinted or reproduced by any means without written permission from our company.

# Please read the following notes before using the datasheets

- A. These materials are intended as a reference to assist customers with the selection of Panasonic semiconductor products best suited to their applications.

Due to modification or other reasons, any information contained in this material, such as available product types, technical data, and so on, is subject to change without notice.

Customers are advised to contact our semiconductor sales office and obtain the latest information before starting precise technical research and/or purchasing activities.

- B. Panasonic is endeavoring to continually improve the quality and reliability of these materials but there is always the possibility that further rectifications will be required in the future. Therefore, Panasonic will not assume any liability for any damages arising from any errors etc. that may appear in this material.

- C. These materials are solely intended for a customer's individual use. Therefore, without the prior written approval of Panasonic, any other use such as reproducing, selling, or distributing this material to a third party, via the Internet or in any other way, is prohibited.