# Low-power coaxial Ethernet transceiver

### NE83C92

### DESCRIPTION

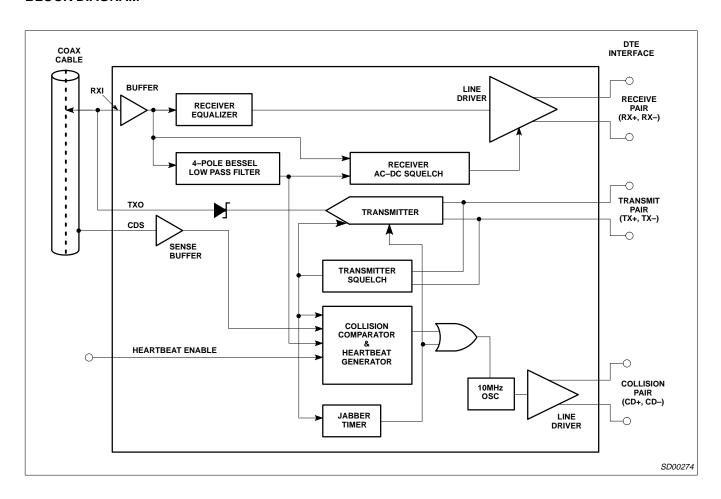

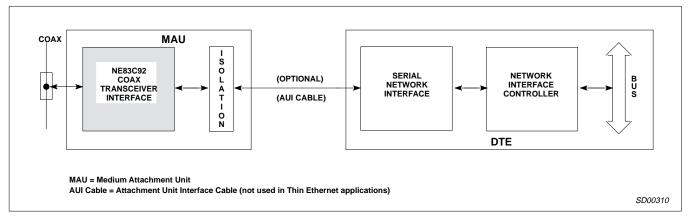

The NE83C92 is a low power BiCMOS coaxial transceiver interface (CTI) for Ethernet (10base5) and Thin Ethernet (10base2) local area networks. The CTI is connected between the coaxial cable and the Data Terminal Equipment (DTE) and consists of a receiver, transmitter, receive-mode collision detector, heartbeat generator and jabber timer (see Block Diagram). The transmitter output connects directly to a doubly terminated  $50\Omega$  cable, while the receiver output, collision detector output and transmitter input are connected to the DTE through isolation transformers. Isolation between the CTI and the DTE is an IEEE 802.3 requirement that can be met on signal lines by using a set of pulse transformers. Power isolation for the CTI is achieved using DC-to-DC conversion through a power transformer.

The part is fully pin compatible with the industry standard 8392, but has substantially lower current consumption, is fully compliant with the IEEE802.3 standard, and has additional features such as automatic selection between AUI and coaxial connections, and requires no external pull-down resistors for local integrated MAU application.

The NE83C92 is manufactured on an advanced BiCMOS process and is available with PLCC package which make it ideally suited to lap-top personal computers or systems where low power consumption, limited board space and jumperless design is required. Refer to selection flow chart for optimal application.

### **FEATURES**

- Fully compliant with Ethernet II, IEEE 802.3 10BASE-5 and 10BASE-2, and ISO 8802/3 interface specifications

- 100% drop-in compatible with industry standard 8392 sockets

- Optimal implementation can use 1 Watt DC-DC converter and reduces external part count (local/integrated MAU requires no external pull-down resistors).

- High efficiency AUI drivers automatically power-down under idle conditions to minimize current consumption

- Automatically disabling AUI drivers when disconnecting coax cable, allowing hardwiring of AUI connection and local/integrated CTI connection

- Smart squelch on data inputs eliminates false activations

- Advanced BiCMOS process for extremely low power operation

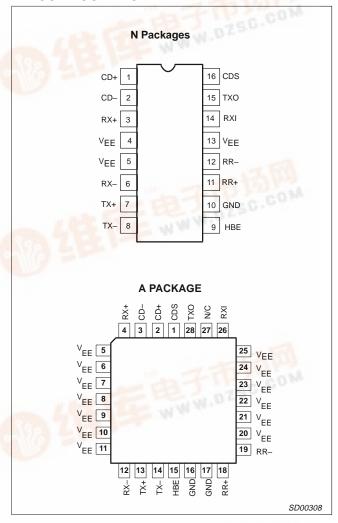

### **PIN CONFIGURATION**

- Available in 16-pin DIP, and 28-pin PLCC packages

- Expanded version (NE83Q93) with 5 LED status drivers is available for repeater and advanced system applications

- Full ESD protection

- Power-on reset prevents glitches on coaxial cable during power-up

### ORDERING INFORMATION

| DESCRIPTION                         | TEMPERATURE RANGE | ORDER CODE | DWG #    |  |

|-------------------------------------|-------------------|------------|----------|--|

| 16-Pin Plastic Dual In-Line Package | 0 to +70°C        | NE83C92N   | SOT28-4  |  |

| 28-Pin Plastic Leaded Chip Carrier  | 0 to +70°C        | NE83C92A   | SOT261-3 |  |

# Low-power coaxial Ethernet transceiver

NE83C92

### **PIN DESCRIPTIONS**

| PIN NO.<br>N PKG | PIN NO.<br>PLCC     | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                                                |

|------------------|---------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2              | 2<br>3              | CD+<br>CD-      | <b>Collision Outputs.</b> Balanced differential line driver outputs which send a 10MHz signal to the DTE in the event of a collision, jabber interrupt or heartbeat test. External pull-down resistors are optional with local/integrated MAU application. |

| 3<br>6           | 4<br>12             | RX+<br>RX–      | <b>Receiver Outputs.</b> Balanced differential line driver outputs which send the received signal to the DTE. External pull-down resistors are optional with local/integrated MAU application.                                                             |

| 7<br>8           | 13<br>14            | TX+<br>TX-      | <b>Transmitter Inputs.</b> Balanced differential line receiver inputs which accept the transmission signal from the DTE and apply it to the coaxial cable at TXO, once it meets Tx squelch threshold.                                                      |

| 9                | 15                  | HBE             | <b>Heartbeat Enable.</b> The heartbeat function is disabled when this pin is connected to $V_{EE}$ and enabled when connected to GND or left floating.                                                                                                     |

| 11<br>12         | 18<br>19            | RR+<br>RR-      | <b>External Resistor.</b> A $1k\Omega$ (1%) resistor connected between these pins establishes the signaling current at TXO.                                                                                                                                |

| 14               | 26                  | RXI             | <b>Receiver Input.</b> This pin is connected directly to the coaxial cable. Received signals are equalized, amplified, and sent to the DTE through the RX± pins, once it meets Rx squelch threshold.                                                       |

| 15               | 28                  | TXO             | <b>Transmitter Output.</b> This pin is connected directly (Thin Ethernet) or through an external isolating diode (Ethernet) to the coaxial cable.                                                                                                          |

| 16               | 1                   | CDS             | <b>Collision Detect Sense.</b> Ground sense connection for the collision detection circuitry. This pin should be connected directly to the coaxial cable shield for standard Ethernet operation.                                                           |

| 10               | 16<br>17            | GND             | Positive Supply Pin.                                                                                                                                                                                                                                       |

| 4<br>5<br>13     | 5 to 11<br>20 to 25 | V <sub>EE</sub> | Negative Supply Pins.                                                                                                                                                                                                                                      |

### NOTE:

<sup>1.</sup> The IEEE 802.3 name for CD is CI; for RX is DI; for TX is DO.

# Low-power coaxial Ethernet transceiver

NE83C92

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL            | PARAMETER                                         | RATING      | UNIT |  |

|-------------------|---------------------------------------------------|-------------|------|--|

| V <sub>EE</sub>   | Supply voltage <sup>1</sup>                       | -12         | V    |  |

| V <sub>IN</sub>   | Voltage at any input <sup>1</sup>                 | 0 to −12    | V    |  |

| T <sub>STG</sub>  | Storage temperature range                         | -65 to +150 | °C   |  |

| T <sub>SOLD</sub> | Lead soldering temperature (10sec.)               | +300        | °C   |  |

| TJ                | Recommended max junction temperature <sup>2</sup> | +150        | °C   |  |

| $\theta_{JA}$     | Thermal impedance (N and A packages)              | 60          | °C/W |  |

#### NOTE:

- 1. 100% measured in production.

2. The junction temperature is calculated from the following expression:

$T_J = T_A + \theta_{JA} [(V_{EE} \times 0.015 \times n_{IDL}) + (V_{EE} \times 0.018 \times n_{RX}) + (V_{EE} \times 0.066 \times n_{TX})]$ where

- $T_A$  = Ambient temperature in  ${}^{\circ}C$ .

- $\begin{array}{ll} \theta_{JA} &=& Thermal\ resistance\ of\ package. \\ V_{EE} &=& Normal\ operating\ supply\ voltage\ in\ volts. \end{array}$

- n<sub>IDL</sub> = Percentage of duty cycle idle

- n<sub>RX</sub> = Percentage of duty cycle receiving n<sub>TX</sub> = Percentage of duty cycle transmitting

# Low-power coaxial Ethernet transceiver

NE83C92

### **ELECTRICAL CHARACTERISTICS**

$V_{EE} = -9V \pm 6\%$ ;  $T_A = 0$ °C to +70°C unless otherwise specified 1,2. No external isolation

|                   |                                                                                    | TEST CONDITIONS                                   | LIMITS               |       |                      |           |

|-------------------|------------------------------------------------------------------------------------|---------------------------------------------------|----------------------|-------|----------------------|-----------|

| SYMBOL            | PARAMETER                                                                          |                                                   | MIN                  | TYP   | MAX                  | UNIT<br>V |

| V <sub>UVL</sub>  | Under voltage lockout. Transceiver disabled for $ V_{EE}  <  V_{UVL} $             |                                                   |                      | -7.5  |                      |           |

|                   | Supply current idle                                                                |                                                   |                      | -15   | -20                  | mA        |

| I <sub>EE</sub>   | Supply current transmitting (without collision)                                    | Without external pull-down resistors              |                      | -70   | -85                  | mA        |

| I <sub>RXI</sub>  | Receive input bias current                                                         | V <sub>RXI</sub> = 0V                             | -2                   |       | +25                  | μΑ        |

| I <sub>CDS</sub>  | Cable sense input bias current                                                     | V <sub>CDS</sub> = 0V                             |                      | +1    | +3                   | μΑ        |

| V <sub>IH</sub>   | HBE input HIGH voltage                                                             |                                                   | V <sub>EE</sub> +2.4 |       |                      | V         |

| V <sub>IL</sub>   | HBE input LOW voltage                                                              |                                                   |                      |       | V <sub>EE</sub> +1.6 | V         |

| I <sub>IH</sub>   | HBE input HIGH current                                                             | V <sub>HBE</sub> = 0V                             |                      |       | +10                  | μΑ        |

| I <sub>I</sub> L  | HBE input LOW current                                                              | V <sub>HBE</sub> = V <sub>EE</sub>                | -30                  |       |                      | μΑ        |

| I <sub>TDC</sub>  | Transmit output DC current level <sup>3</sup>                                      |                                                   | -37                  |       | -45                  | mA        |

| I <sub>TAC</sub>  | Transmit output AC current level <sup>3</sup>                                      |                                                   | ±28                  |       | ±I <sub>TDC</sub>    | mA        |

| I <sub>TX10</sub> | Transmit current                                                                   | V <sub>TXO</sub> = −10V                           | -250                 |       | +250                 | μΑ        |

| V <sub>TCOM</sub> | Transmitter output voltage compliance <sup>4</sup>                                 |                                                   |                      |       | -3.7                 | V         |

| V <sub>CD</sub>   | Collision threshold <sup>5</sup>                                                   | Measured by applying DC voltage at RXI (CDS = 0V) | -1450                | -1530 | -1580                | mV        |

| V <sub>DIS</sub>  | AUI disable voltage at RXI                                                         | Measured as DC voltage at RXI                     |                      | -3.5  |                      | V         |

| V <sub>OD</sub>   | Differential output voltage – non idle at RX $\pm$ and CD $\pm^6$                  |                                                   | ±600                 |       | ±1100                | mV        |

| V <sub>OB</sub>   | Differential output voltage imbalance – idle at RX $\pm$ and CD $\pm$ <sup>7</sup> |                                                   |                      |       | ±40                  | mV        |

| V <sub>OC</sub>   | Output common mode voltage at RX± and CD±                                          | RXI = 0V                                          | -4.0                 | -5.5  | -7.0                 | V         |

| V <sub>RS</sub>   | Receiver squelch threshold                                                         | V <sub>RXI</sub> average DC<br>(CDS = 0V)         | -150                 | -250  | -350                 | mV        |

| $V_{TS}$          | Transmitter squelch threshold                                                      | (V <sub>TX+</sub> – V <sub>TX-</sub> ) peak       | -175                 | -225  | -275                 | mV        |

| R <sub>RXI</sub>  | Shunt resistance at RXI non–transmitting                                           |                                                   | 100                  |       |                      | kΩ        |

| C <sub>RXI</sub>  | Input capacitance at RXI <sup>8</sup>                                              |                                                   |                      | 1     | 2                    | pF        |

| R <sub>TXO</sub>  | Shunt resistance at TXO transmitting                                               |                                                   | 7.5                  | 10    |                      | kΩ        |

| R <sub>AUIZ</sub> | Differential impedance at RX± and CD± with no coaxial cable connected              |                                                   |                      | 6     |                      | kΩ        |

| R <sub>TX</sub>   | Differential impedance at TX±                                                      |                                                   |                      | 20    |                      | kΩ        |

- 1. Currents flowing into device pins are positive. All voltages are referenced to ground unless otherwise specified. For ease of interpretation, the parameter limit that appears in the MAX column is the largest value of the parameter, irrespective of sign. Similarly, the value in the MIN column is the smallest value of the parameter, irrespective of sign.

- Column is the smallest value of the parameter, irrespective of sign.

All typicals are for V<sub>EE</sub> = –9V and T<sub>A</sub> = 27°C.

I<sub>TDC</sub> is measured as (V<sub>MAX</sub> + V<sub>MIN</sub>)/(2 x 25) where V<sub>MAX</sub> and V<sub>MIN</sub> are the max and min voltages at TXO with a 25Ω load between TXO and GND. I<sub>TAC</sub> is measured as (V<sub>MAX</sub> V<sub>MIN</sub>)/(2 x 25).

The TXO pin shall continue to sink at least I<sub>TDC</sub> min when the idle (no signal) voltage on this pin is –3.7V.

Collision threshold for an AC signal is within 5% of V<sub>CD</sub>.

Measured on secondary side of isolation transformer. The transformer has a 1:1 turns ratio with an inductance between 30 and 100μH at

- 5MHz.

- Measured as the voltage difference between the RX pins or the CD pins with the transformer removed.

- 8. Not 100% tested in production.

# Low-power coaxial Ethernet transceiver

NE83C92

### **TIMING CHARACTERISTICS**

$V_{EE}$  = -9V  $\pm 6\%$ ;  $T_A$  = 0 to 70°C, unless otherwise specified<sup>1</sup>. No external isolation diode on TXO.

| SYMBOL            |                                                                                                                  | TEST CONDITIONS                   | LIMITS |     |                      |      |

|-------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|-----|----------------------|------|

|                   | PARAMETER                                                                                                        |                                   | MIN    | TYP | MAX                  | UNIT |

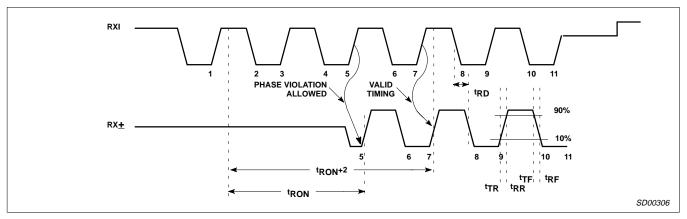

| t <sub>RON</sub>  | Receiver start up delay RXI to RX± (Figure 3) First received bit on RX±                                          | V <sub>RXI</sub> = -2V peak       |        | 3   | 5                    | bits |

|                   | First validly timed bit on RX±                                                                                   |                                   |        |     | t <sub>RON</sub> +2  | bits |

| t <sub>RD</sub>   | Receiver prop. delay RXI to RX±                                                                                  | V <sub>RXI</sub> = -2V peak       |        | 20  | 50                   | ns   |

| t <sub>RR</sub>   | Differential output rise time on RX $\pm$ and CD $\pm$ <sup>2,3</sup>                                            |                                   |        | 5   | 7                    | ns   |

| t <sub>RF</sub>   | Differential output fall time on RX $\pm$ and CD $\pm^{2,3}$                                                     |                                   |        | 5   | 7                    | ns   |

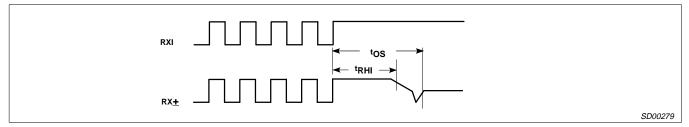

| tos               | Differential output settling time on RX $\pm$ and CD $\pm$ to V <sub>OB</sub> = 40mV <sup>2</sup> (see Figure 4) |                                   |        | 1   |                      | μѕ   |

| t <sub>RJ</sub>   | Receiver and cable total jitter                                                                                  |                                   |        | ±2  | ±6                   | ns   |

| t <sub>RHI</sub>  | Receiver high to idle time                                                                                       | Measured to +210mV                | 200    |     | 850                  | ns   |

| t <sub>RM</sub>   | Rise and fall time matching on RX± and CD±                                                                       | t <sub>RF</sub> – t <sub>RR</sub> |        | 0.1 | ±2                   | ns   |

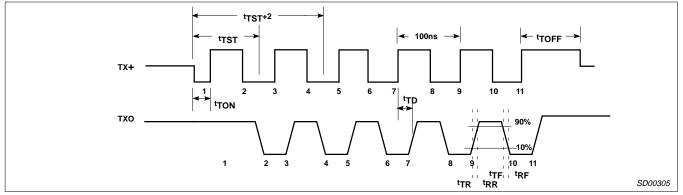

| t <sub>TST</sub>  | Transmitter start-up delay TX± to TXO (Figure 5) First transmitted bit on TXO                                    | V <sub>TX</sub> ± = −1V peak      |        | 1   | 2                    | bits |

| <sup>τ</sup> TST  | First validly timed bit                                                                                          |                                   |        |     | t <sub>TST</sub> + 2 | bits |

| t <sub>TD</sub>   | Transmitter prop delay TX± to TXO (see Figure 5)                                                                 | V <sub>TX</sub> ± = 1V peak       | 5      | 20  | 50                   | ns   |

| t <sub>TR</sub>   | Transmitter rise time 10% to 90% (see Figure 5)                                                                  |                                   | 20     | 25  | 30                   | ns   |

| t <sub>TF</sub>   | Transmitter fall time 10% to 90% (see Figure 5)                                                                  |                                   | 20     | 25  | 30                   | ns   |

| t <sub>TM</sub>   | t <sub>TF</sub> – t <sub>TR</sub> mismatch <sup>5</sup>                                                          |                                   |        | 0   | ±2                   | ns   |

| t <sub>TS</sub>   | Transmitter added skew <sup>4,5</sup>                                                                            |                                   |        | 0   | ±2                   | ns   |

| t <sub>TON</sub>  | Transmitter turn on pulse width (see Figure 5)                                                                   | V <sub>TX±</sub> = 1V peak        | 10     |     | 35                   | ns   |

| t <sub>TOFF</sub> | Transmitter turn off pulse width (see Figure 5)                                                                  | V <sub>TX</sub> ± = 1V peak       | 125    |     | 200                  | ns   |

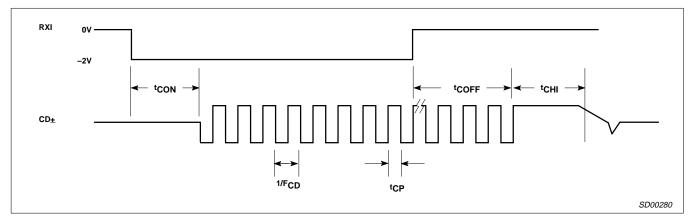

| t <sub>CON</sub>  | Collision turn on delay (see Figure 6)                                                                           | 0V to –2V step at RXI             |        |     | 13                   | bits |

| t <sub>COFF</sub> | Collision turn off delay (see Figure 6)                                                                          | –2V to 0V step at RXI             |        |     | 16                   | bits |

| t <sub>CHI</sub>  | Collision high to idle time (see Figure 6)                                                                       | Measured to +210mV                | 200    |     | 850                  | ns   |

| f <sub>CD</sub>   | Collision frequency (see Figure 6)                                                                               |                                   | 8.5    | 10  | 11.5                 | MHz  |

| t <sub>CP</sub>   | Collision signal pulse width (see Figure 6)                                                                      |                                   | 35     |     | 70                   | ns   |

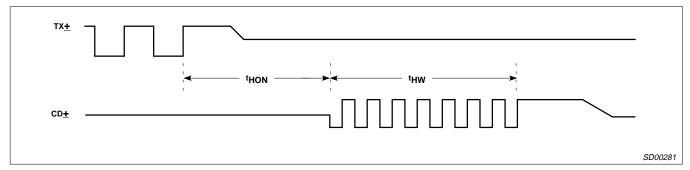

| t <sub>HON</sub>  | Heartbeat turn on delay (see Figure 7)                                                                           |                                   | 0.6    |     | 1.6                  | μs   |

| t <sub>HW</sub>   | Heartbeat test duration (see Figure 7)                                                                           |                                   | 0.5    |     | 1.5                  | μs   |

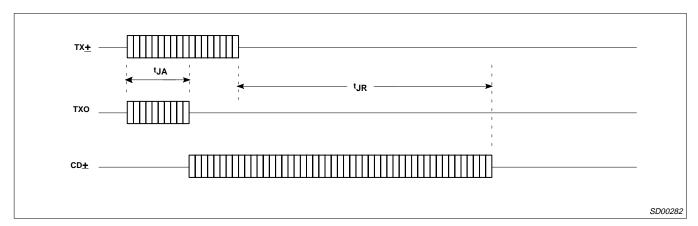

| t <sub>JA</sub>   | Jabber activation delay measured from TX± to CD± (see Figure 8)                                                  |                                   | 20     |     | 60                   | ms   |

| t <sub>JR</sub>   | Jabber reset delay measured from TX± to CD± (see Figure 8)                                                       |                                   | 250    |     | 650                  | ms   |

- All typicals are for V<sub>EE</sub> = -9V and T<sub>A</sub> = 27°C.

Measured on secondary side of isolation transformer (see Figure 2). The transformer has a 1:1 turn ratio with an inductance between 30 and  $100\mu H$  at 5MHz.

- The rise and fall times are measured as the time required for the differential voltage to change from -225mV to +225mV, or +225mV to -225mV, respectively.

4. Difference in propagation delay between rising and falling edges at TXO.

- 5. Not 100% tested in production.

## Low-power coaxial Ethernet transceiver

NE83C92

### **FUNCTIONAL DESCRIPTION**

The NE83C92 is a low power BiCMOS coaxial Ethernet transceiver which complies with the IEEE 802.3 specification and offers the following features:

- Low current consumption of typically 15mA when idling and 70mA while transmitting and no collision allows smaller DC-DC converter to be used for the isolated power supply. (No external pull-down resistors.)

- 2. Automatic selection of the AUI connector (for remote MAU) instead of the direct local (Thin) coaxial connection is possible by automatically placing the AUI drivers in high-impedance state when the local coaxial cable is disconnected. This eliminates the need for changing a jumper position on the Ethernet board when selecting either one of the connections. (Automatic selection of the local (Thin) connection is done by disconnecting the AUI cable and reconnecting the local coaxial one, which allows the NE83Q92 to automatically activate itself.)

- High-efficiency AUI drivers for the RX± and CD± ports automatically power down when idling and are powered up when a receive signal is detected. This is very important/useful for power sensitive applications such as lap-top computers or PCMCIA cards.

- 4. The NE83C92 advanced AUI driver (RX± and CD±) design does require external pull-down resistors (500Ω) to drive a terminated (78Ω) AUI cable. However, these drivers will operate correctly without the external resistors for integrated/local MAU applications where no AUI cable is used. Hence, they can be retro-fitted into existing 8392 designs with or without external pull-down resistors depending on the application. An extra current of 7mA/output (for 500Ω resistors) would be generated, by these resistors, regardless of whether the transceiver is idle or responding to traffic.

### **Receiver Functions**

The receiver consists of an input buffer, a cable equalizer, a 4-pole Bessel low pass filter, a squelch circuit and a differential line driver.

The buffer provides high input resistance and low input capacitance to minimize loading and reflections on the coaxial cable.

The equalizer is a high pass filter that compensates for the low pass effect of the coaxial cable and results in a flatband response over all signal frequencies to minimize signal distortion.

The 4-pole Bessel low pass filter extracts the average DC voltage level on the coaxial cable for use by the receiver squelch and collision detection circuits.

The receiver squelch circuit prevents noise on the coaxial cable from falsely triggering the receiver in the absence of a true signal. At the beginning of a packet, the receiver turns on when the DC level from the low pass filter exceeds the DC squelch threshold and the received packet has started with a 01 bit sequence with acceptable timing parameters. For normal signal levels this will take less than 500ns, or 5 bits. However, at the end of a packet, a fast receiver turn off is needed to reject both dribble bits on the coaxial cable and spurious responses due to settling of the on-chip bandpass filter. This is accomplished by an AC timing circuit that disables the receiver if the signal level on the coaxial cable remains high for typically 250ns and only enables the receiver again after approximately .5µs. Figures 3 and 4 illustrate receiver timing.

The differential line driver provides typically ±900mV signals to the DTE with less than 7ns rise and fall times. When in idle state (no received signal) its outputs provide <20mV differential voltage offset to minimize DC standing current in the isolation transformer.

### **Transmitter Functions**

The transmitter has differential inputs and an open collector current driver output. The differential input common mode voltage is established by the CTI and should not be altered by external circuitry. Controlled rise and fall times of 25ns (±5ns) minimize higher harmonic components in the transmitted spectrum, while matching of these rise and fall times to typically 2ns minimizes signal jitter. The drive current levels of the CTI are set by an on-chip bandgap voltage reference and an external 1% resistor. An on-chip isolation diode is provided to reduce the transmitter's coaxial cable load capacitance. For Thin Ethernet applications, no further external isolation diode is required, since the NE83C92 meets the capacitive loading specifications. For Ethernet applications a further external diode should be added to reduce loading capacitance.

The transmitter squelch circuit ensures that the transmitter can only be enabled if the transmitted packet begins with a 01 bit sequence where the negative-going differential signals are typically greater than 225mV in magnitude and 25ns in duration.

The transmitter will be disabled at the end of a packet if there are no negative going signals of greater than 225mV for more than typically 150ns. Figure 5 illustrates transmitter timing.

### **Collision Functions**

The collision detection scheme implemented in the NE83C92 is receive mode detection, which detects a collision between any two stations on the network with certainty at all times, irrespective of whether or not the local DTE is producing one of the colliding signals. This is the only detection scheme allowed by the IEEE 802.3 standard for both repeater and non-repeater nodes.

The collision circuitry consists of the 4-pole Bessel low pass filter, a comparator, a precision voltage reference that sets up the collision threshold, a heartbeat generator, a 10MHz oscillator, and a differential line driver.

The collision comparator monitors the DC level at the output of the low pass filter and enables the line driver if it is more negative than the collision threshold. A collision condition is indicated to the DTE by a 10MHz oscillation signal at the CD outputs and typically occurs within 700ns of the onset of the collision. The collision signal begins with a negative-going pulse and ends with a continuous high-to-idle state longer than 170ns. Figure 6 illustrates collision timing.

At the end of every transmission, the heartbeat generator creates a pseudo collision to ensure that the collision circuitry is properly functioning. This pseudo collision consists of a  $1\mu s$  burst of 10 MHz oscillation at the line driver outputs approximately  $1\mu s$  after the end of the transmission. The heartbeat function can be disabled externally by connecting the HBE (heartbeat enable) to  $V_{EE}.$  This allows the CTI to be used in repeater applications. Figure 7 illustrates heartbeat timing.

### **Jabber Functions**

The jabber timer monitors the transmitter and inhibits transmission if it is active for longer than typically 30ms. The jabber circuit then enables the collision outputs for the remainder of the data packet and for typically 450ns (unjab time) after it has ended. At this point the transmitter becomes uninhibited. Figure 8 illustrates jabber timing.

## Low-power coaxial Ethernet transceiver

NE83C92

### POR/Under Voltage Lockout/AUI Selection

The transmit and receive squelch circuits of the NE83C92 remain active if the absolute value of  $V_{EE}$  is less than the threshold for under voltage lockout,  $V_{UVL}$ . This prevents glitches from appearing on either the AUI or coaxial cable during power up and power down.

There is no collision announcement during power up and the transceiver waits for 400ms before becoming enabled.

If RXI is disconnected from the coaxial cable after power-up, its voltage will fall towards VEE. If the absolute value of this voltage exceeds the AUI disable voltage, VDIS, for longer than 800ms, the transmit and receive squelch circuits remain active and, in addition, the AUI drivers become high impedance. This permits AUI connections to be hard wired together, e.g., the coaxial transceiver and 10BASE-T transceiver, with the signal path determined by which transceiver is connected to its external cable.

There is a 400ms collision announcement on disconnecting RXI, but there is no announcement on re-connection. This feature can be disabled by pulling RXI up with a 200k $\Omega$  to ground.

### **Detection of Coaxial Cable Faults**

In the NE83C92 there is no internal loopback path from the TX inputs to the RX outputs. This means that, when the local DTE is transmitting, the signal will only be present at the receiver outputs RX+ and RX– if it appears on the coaxial cable and is larger than the receiver squelch threshold  $\mathsf{V}_{RS}.$  If a short circuit fault condition occurs at the cable connector to the CTI, then no signal will appear at the receiver outputs.

In the case of an open circuit at the coaxial cable connector there will also be no signal at the receiver outputs due to the AUI disabling mode of the NE83Q92. However, a heartbeat signal will be present following a transmission attempt for the short circuit condition, but not for the open circuit.

A coaxial cable with only a single  $50\Omega$  termination will generate a collision not only at every transmission attempt, but also for every reception attempt due to the receive mode collision detection of the NE83C92.

# Low-power coaxial Ethernet transceiver

NE83C92

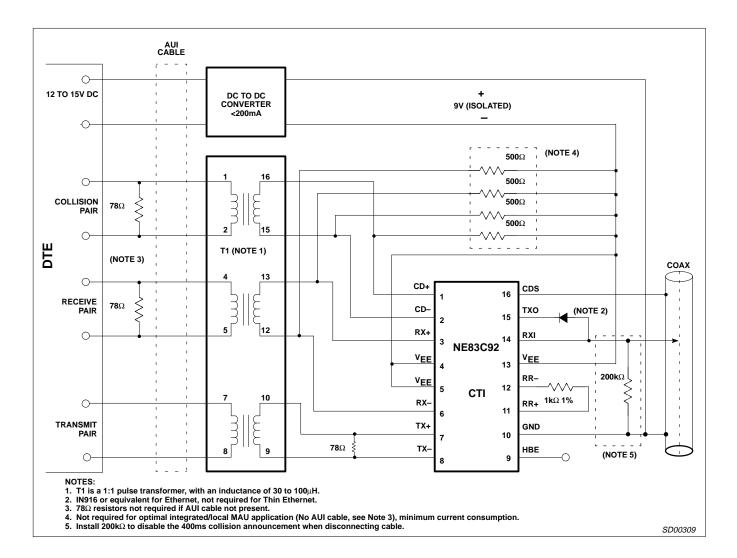

Figure 2. Interface Diagram for Ethernet/Thin Ethernet Local Area Network

Figure 3. Receiver Timing

Figure 4. Receiver End-of-Packet Timing

Figure 5. Transmitter Timing

# Low-power coaxial Ethernet transceiver

NE83C92

Figure 6. Collision Timing

Figure 7. Heartbeat Timing

Figure 8. Jabber Timing