### QUARTZ CRYSTAL OSCILLATOR

#### GENERAL DESCRIPTION

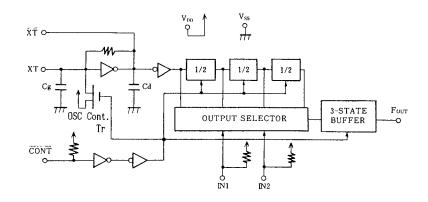

The NJU6321 series is a C-MOS quartz crystal oscillator which consists of an oscillation amplifier, 3-stage divider, output frequency selector and 3-state output buffer.

The oscillation frequency is as wide as up to 50MHz and the symmetry of 45-55% is realized over full oscillation frequency range.

The oscillation amplifier incorporates feed-back resistance and oscillation capacitors(Cg, Cd), therefore, it requires no external component except quartz crystal.

The 3-stage divider outputs  $f_0$ ,  $f_0/2$ ,  $f_0/4$  and  $f_0/8$  to the output frequency selector and it determined one output frequency according to the combination of two input-signal.

The 3-state output buffer is C-MOS compatible and capable of 10 LSTTL driving.

NJU6321XC

PACKAGE OUTLINE

NJU6321XE

#### PIN CONFIGURATION/PAD LOCATION

|      | - |        | CONT  | ° 0 8 |      |

|------|---|--------|-------|-------|------|

| CONT | 0 | 8 Vop  |       |       | L    |

| XT   | 2 | 🗹 X T  | хтd   | 2 7   | Рхт  |

| IN1  |   | 6 IN2  | IN I  | 3 6   |      |

| Vss  | 1 | 5 Four | Vss 🗖 | 4 5   | Fout |

#### FEATURES

- Operating Voltage -- 3.0~6.0V

- Maximum Oscillation Frequency -- 50MHz

- Low Operating Current

- High Fan-out -- LSTTL 10

- 3-state Output Buffer

- Selected Frequency Output (mask option) Only one frequency out of fo, fo/2, fo/4 and fo/8 output

- Oscillation Capacitors Cg and Cd on-chip

- Oscillation and/or Output Stand-by Function

- Package Outline -- CHIP/EMP 8

- C-MOS Technology

🖬 COORDINATES Unit:µm

| No.                                  | PAD                                                  | Х                                                 | Y                                                    |

|--------------------------------------|------------------------------------------------------|---------------------------------------------------|------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | CONT<br>XT<br>IN1<br>Vss<br>Fout<br>IN2<br>XT<br>Vdd | 165<br>165<br>165<br>1113<br>1113<br>1113<br>1113 | 651<br>484<br>317<br>149<br>149<br>317<br>484<br>651 |

| Chip Size<br>Chip Thickness          |                                                      |                                                   | X 0.8mm<br>m±30μm                                    |

#### ■ LINE-UP TABLE

| Туре Мо. | Cg   | Cd   | Osc. Stop (Tr) |

|----------|------|------|----------------|

| NJU6321A | 21pF | 23pF | Yes            |

| NJU6321P | NO   | NO   | NO             |

# JRC

### BLOCK DIAGRAM

(Note) Oscillation Stop Function is available only for NJU6321A. NJU6321P has only output stand-by function.

#### TERMINAL DESCRIPTION

| NO.    | SYMBOL     | FUNCTION                                                                                                                                                                                                                                                   |  |  |  |

|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1      | CONT       | Oscillation Stop Control and Divider Reset         CONT         FOUT         H       Output either one frequency from fo, fo/2, fo/4, and fo/8         L       Output High Impedance and Divider Reset         In       the NJU6321A also oscillation stop |  |  |  |

| 2<br>7 | XT<br>XT   | Quartz Crystal Connecting Terminals                                                                                                                                                                                                                        |  |  |  |

| 8      | $V_{DD}$   | + 5V                                                                                                                                                                                                                                                       |  |  |  |

| 3      | N1<br>  N2 | 3-State Divider Outputs selected by IN1 and IN2<br>$ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                  |  |  |  |

| 5      | Four       | Output either one frequency from $f_0$ , $f_0/2$ , $f_0/4$ , and $f_0/8$                                                                                                                                                                                   |  |  |  |

| 4      | Vss        | GND                                                                                                                                                                                                                                                        |  |  |  |

#### ■ ABSOLUTE MAXIMUM RATINGS

( Ta=25℃ )

| A                           |        |                             |      |

|-----------------------------|--------|-----------------------------|------|

| PARAMETER                   | SYMBOL | RATINGS                     | UNIT |

| Supply Voltage              | VDD    | -0.5 ~ +7.0                 | V    |

| Input Voltage               | VIN    | $-0.5 \sim V_{DD}+0.5$      | ٧    |

| Output Voltage              | Vo     | -0.5 ~ V <sub>DD</sub> +0.5 | V    |

| Input Current               | IN     | <b>±</b> 10                 | mA   |

| Output Current              | lo     | <b>±</b> 25                 | mA   |

| Power Dissipation (EMP)     | PD     | 200                         | m₩   |

| Operating Temperature Range | Topr   | -40 ~ + 85                  | ືະ   |

| Storage Temperature Range   | Tstg   | -65 ~ +150                  | ĉ    |

Note ) Decoupling capacitor should be connected between  $V_{\text{DD}}$  and  $V_{\text{SS}}$  due to the stabilized operation for the circuit.

#### ELECTRICAL CHARACTERISTICS

( Ta=25℃, V<sub>DD</sub>=5V )

| PARAMETER               | SYMBOL | CONDITIONS                                                         | MIN | ТҮР | MAX | UNIT |

|-------------------------|--------|--------------------------------------------------------------------|-----|-----|-----|------|

| Operating Voltage       | VDD    |                                                                    | 3   |     | 6   | ٧    |

| Operating Current       | DD     | fosc=16MHz, No load                                                |     |     | 10  | mA   |

| Stand-by Current        | lst    | CONT,XT=Vss, No load (Note)                                        |     |     | 1   | μA   |

| Input Voltage           | VIH    |                                                                    | 3.5 |     | 5.0 | v    |

|                         | VIL    |                                                                    | 0   |     | 1.5 | , v  |

| Output Current          | Гон    | V <sub>DD</sub> =5V, V <sub>OH</sub> =4.5V                         | 4   |     |     | mA   |

|                         | lol    | VDD=5V, Vol=0.5V                                                   | 4   |     |     | IIIA |

| Input Current           | Пи     | <u>CONT</u> , IN1, IN2 Terminals<br>CONT, IN1, IN2=V <sub>SS</sub> |     |     | 400 | μA   |

|                         | Cg     | A Version                                                          |     | 21  |     |      |

| Internal Capacitor      | Cd     | A Version                                                          |     | 23  |     | ۶q   |

|                         | Cg,Cd  | P Version                                                          |     | -   |     |      |

| Max. Oscillation Freq.  | fмах   | $V_{DD}=5V$ , $C_L=15pF$                                           | 50  |     |     | MHz  |

| Output Signal Symmetry  | SYM    | $V_{DD}=5V$ , $C_L=15pF$ at $1/2V_{DD}$                            | 45  | 50  | 55  | %    |

| Output Signal Rise Time | tr     | V <sub>DD</sub> =5V, C <sub>L</sub> =15pF, 10% - 90%               |     |     | 8   | ns   |

| Output Signal Fall Time | tf     | $V_{DD}=5V$ , CL=15pF, 90% - 10%                                   |     |     | 8   | ns   |

Note ) Excluding input current on CONT terminal.

## JRC

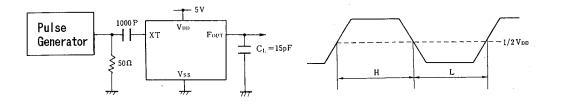

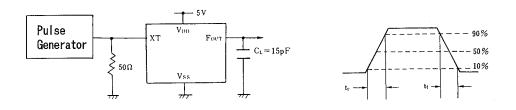

#### MEASUREMENT CIRCUITS

(1) Output Signal Symmetry (C<sub>L</sub>=15pF)

(2) Output Signal Rise/Fall Time (CL=15pF)

### **MEMO**

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

New Japan Radio Co., Ltd.