August 1994

## NM93CS06/CS46/CS56/CS66 (MICROWIRE™ Bus Interface) 256-/1024-/2048-/4096-Bit Serial EEPROM with Data Protect and Sequential Read

## **General Description**

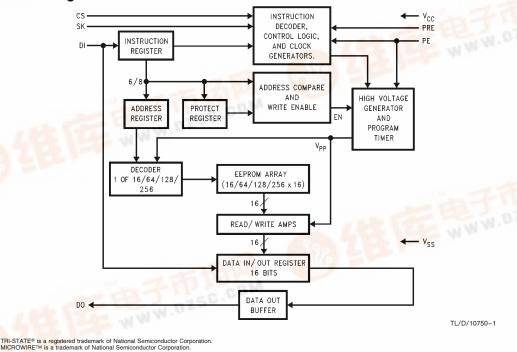

The NM93CS06/CS46/CS56/CS66 devices are 256/1024/2048/4096 bits, respectively, of CMOS non-volatile electrically erasable memory divided into 16/64/128/256 16-bit registers. Selected registers can be protected against data modification by programming the Protect Register with the address of the first register to be protected against data modification (all registers greater than, or equal to, the selected address are then protected from further change). Additionally, this address can be "locked" into the device, making all future attempts to change data impossible. These devices are fabricated using National Semiconductor floating-gate CMOS process for high reliability, high endurance and low power consumption. The NM93CSXX Family is offered in an SO package for small space considerations.

The EEPROM interfacing is MICROWIRE compatible providing simple interfacing to standard microcontrollers and microprocessors. There are a total of 10 instructions, 5 which operate on the EEPROM memory, and 5 which operate on the Protect Register. The memory instructions are

READ, WRITE, WRITE ALL, WRITE ENABLE, and WRITE DISABLE. The Protect register instructions are PRREAD, PRWRITE, PRENABLE, PRCLEAR, and PRDISABLE.

#### **Features**

- Write protection in a user defined section of memory

- Sequential register read

- $\blacksquare$  Typical active current of 400  $\mu\text{A}$  and standby current of 25  $\mu\text{A}$

- No erase required before write

- Reliable CMOS floating gate technology

- MICROWIRE compatible serial I/O

- Self timed write cycle

- Device status during programming mode

- 40 year data retention

- Endurance: 10<sup>6</sup> data changes

- 4.5V to 5.5V operation in all modes of operation

- Packages available: 8-pin SO, 8-pin DIP

## **Block Diagram**

©1995 National Semiconductor Corporation TL/

RRD-B30M75/Printed in U. S. A.

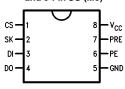

## **Connection Diagram**

# Dual-In-Line Package (N) and 8-Pin SO (M8)

TL/D/10750-2

Top View NS Package Number N08E and M08A

#### Pin Names

| CS              | Chip Select             |  |  |  |  |

|-----------------|-------------------------|--|--|--|--|

| SK              | Serial Data Clock       |  |  |  |  |

| DI              | Serial Data Input       |  |  |  |  |

| DO              | Serial Data Output      |  |  |  |  |

| GND             | Ground                  |  |  |  |  |

| PE              | Program Enable          |  |  |  |  |

| PRE             | Protect Register Enable |  |  |  |  |

| V <sub>CC</sub> | Power Supply            |  |  |  |  |

## **Ordering Information**

## Commercial Temp. Range (0°C to $\,+\,70^{\circ}$ C)

#### Order Number\*

NM93CS06N/NM93CS46N/NM93CS56N/NM93CS66N NM93CS06M8/NM93CS46M8/NM93CS56M8/NM93CS66M8

## Extended Temp. Range ( $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ )

#### Order Number\*

NM93CS06EN/NM93CS46EN/NM93CS56EN/NM93CS66EN NM93CS06EM8/NM93CS46EM8/NM93CS56EM8/NM93CS66EM8

## Military Temp. Range ( $-55^{\circ}$ C to $+125^{\circ}$ C)

## Order Number\*

NM93CS06MN/NM93CS46MN/NM93CS56MN/NM93CS66MN NM93CS06MM8/NM93CS46MM8/NM93CS56MM8/NM93CS66MM8

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Ambient Storage Temperature  $-65^{\circ}$ C to  $+150^{\circ}$ C All Input or Output Voltages +6.5V to -0.3V

with Respect to Ground

Lead Temperature (Soldering, 10 sec.) + 300°C ESD rating 2000V

## **Operating Conditions**

Ambient Operating Temperature NM93CSxx

NM93CSxxE NM93CSxxM 0°C to +70°C -40°C to +85°C -55°C to +125°C

Power Supply (V<sub>CC</sub>) 4.5V to 5.5V

# **DC and AC Electrical Characteristics** $V_{CC} = 4.5 V$ to 5.5V unless otherwise specified Throughout this table, "M" refers to temperature range ( $-55^{\circ}$ C to $+125^{\circ}$ C), not package.

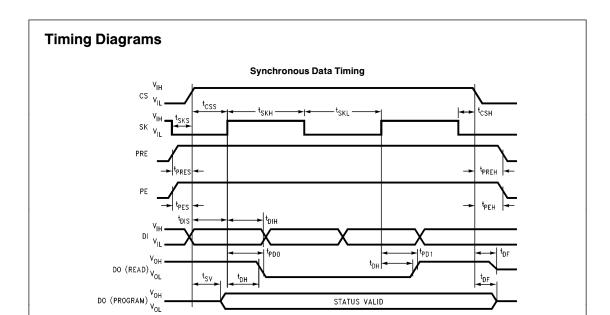

**Parameter Part Number** Conditions Min Max Units NM93CS06-NM93CS66  $CS = V_{IH}$ , SK = 1.0 MHz**I**CCA Operating Current NM93CS06E-NM93CS66E SK = 1.0 MHzmΑ NM93CS06M-NM93CS66M SK = 0.5 MHzNM93CS06-NM93CS66  $CS = V_{IL}$ 50 Standby Current Iccs NM93CS06E-NM93CS06E 50 μΑ NM93CS06M-NM93CS06M 100 Input Leakage  $V_{IN} = 0V \text{ to } V_{CC}$  $\pm -1$ μΑ (Note 4)  $I_{OL}$ Output Leakage Input Low Voltage -0.1 $V_{\mathsf{IL}}$ 8.0 V Input High Voltage  $V_{\text{IH}}$ 2  $V_{CC} + 1$  $V_{OL1}$ Output Low Voltage  $I_{OL} = 2.1 \text{ mA}$ 0.4 ٧  $I_{OH}^-=-400~\mu A$  $V_{\text{OH}\underline{1}}$ Output High Voltage 2.4 Output Low Voltage  $I_{OL}=10~\mu A$ 0.2  $V_{OL2}$  $V_{\text{OH2}}$ Output High Voltage  $I_{OH} = -10 \,\mu A$  $V_{\text{CC}}-0.2$ SK Clock Frequency NM93CS06-NM93CS66 (Note 5) 0  $f_{SK}$ 1 NM93CS06E-NM93CS66E MHz 0 NM93CS06M-NM93CS66M 0 0.5 SK High Time NM93CS06-NM93CS66 250  $t_{SKH}$ NM93CS06E-NM93CS66E 300 ns NM93CS06M-NM93CS66M 500 SK Low Time 250 ns tSKL SK Must Be at V<sub>IL</sub> SK Setup Time 50  $t_{SKS}$ for t<sub>SKS</sub> before CS 50 ns goes high 100 Minimum CS NM93CS06-NM93CS66 250 (Note 2)  $t_{CS}$ Low Time NM93CS06E-NM93CS66E 250 ns NM93CS06M-NM93CS66M 500 100 CS Setup Time ns  $t_{CSS}$ NM93CS06-NM93CS66 PRE Setup Time 50 t<sub>PRES</sub> NM93CS06E-NM93CS66E 50 ns NM93CS06M-NM93CS66M 100 DO Hold Time 70 ns  $t_{DH}$ PE Setup Time NM93CS06-NM93CS66 50  $t_{\text{PES}}$ NM93CS06E-NM93CS66E 50 NM93CS06M-NM93CS66M 100  $t_{\text{DIS}}$ DI Setup Time NM93CS06-NM93CS66 100 NM93CS06E-NM93CS66E 100 ns NM93CS06M-NM93CS66M 200 0 CS Hold Time  $t_{CSH}$ ns

| DC and AC Electrical Characteristic | $V_{CC} = 4.5V$ to 5.5V unless otherwise specified (Continued) |

|-------------------------------------|----------------------------------------------------------------|

|-------------------------------------|----------------------------------------------------------------|

| Symbol            | Parameter                 | Part Number                                                     | Conditions    | Min               | Max                | Units |

|-------------------|---------------------------|-----------------------------------------------------------------|---------------|-------------------|--------------------|-------|

| t <sub>PEH</sub>  | PE Hold Time              | NM93CS06-NM93CS66<br>NM93CS06E-NM93CS66E<br>NM93CS06M-NM93CS66M |               | 250<br>250<br>500 |                    | ns    |

| t <sub>PREH</sub> | PRE Hold Time             |                                                                 |               | 50                |                    | ns    |

| t <sub>DIH</sub>  | DI Hold Time              |                                                                 |               | 20                |                    | ns    |

| t <sub>PD1</sub>  | Output Delay to "1"       | NM93CS06-NM93CS66<br>NM93CS06E-NM93CS66E<br>NM93CS06M-NM93CS66M |               |                   | 500<br>500<br>1000 | ns    |

| t <sub>PD0</sub>  | Output Delay to "0"       | NM93CS06-NM93CS66<br>NM93CS06E-NM93CS66E<br>NM93CS06M-NM93CS66M |               |                   | 500<br>500<br>1000 | ns    |

| t <sub>SV</sub>   | CS to Status Valid        | NM93CS06-NM93CS66<br>NM93CS06E-NM93CS66E<br>NM93CS06M-NM93CS66M |               |                   | 500<br>500<br>1000 | ns    |

| t <sub>DF</sub>   | CS to DO in<br>TRI-STATE® | NM93CS06-NM93CS66<br>NM93CS06E-NM93CS66E<br>NM93CS06M-NM93CS66M | $CS = V_{IL}$ |                   | 100<br>100<br>200  | ns    |

| t <sub>WP</sub>   | Write Cycle Time          |                                                                 |               |                   | 10                 | ms    |

# $\begin{array}{l} \textbf{Capacitance} \text{ (Note 3)} \\ T_A = 25^{\circ}\text{C, f} = 1 \text{ MHz} \end{array}$

| Symbol           | Test               | Тур | Max | Units |

|------------------|--------------------|-----|-----|-------|

| C <sub>OUT</sub> | Output Capacitance |     | 5   | pF    |

| C <sub>IN</sub>  | Input Capacitance  |     | 5   | pF    |

Note 1: Stress ratings above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and operation of the device at these or any other conditions above those indicated in the operations of the specification is not implied. Exposure to absolute  $\label{eq:maximum rating conditions} \ \ \text{for extended periods may affect device reliability}.$

Note 2: CS (Chip Select) must be brought low (to V<sub>IL</sub>) for an interval of t<sub>CS</sub> in order to reset all internal device registers (device reset) prior to beginning another opcode cycle (this is shown in the opcode diagrams in the following pages).

Note 3: This parameter is periodically sampled and not 100% tested.

Note 4: Typical leakage values are in the 20 nA range.

Note 5: The shortest allowable SK clock period =  $1/f_{SK}$  (as shown under the  $f_{SK}$  parameter). Maximum SK clock speed (minimum SK period) is determined by the interaction of several AC parameters stated in the datasheet. Within this SK period, both  $t_{SKH}$  and  $t_{SKL}$  limits must be observed. Therefore, it is not allowable to set  $1/f_{SK} = t_{SKH \text{ (minimum)}} + t_{SKL \text{ (minimum)}}$  for shorter SK cycle time operation.

## **AC Test Conditions**

| V <sub>CC</sub> Range                                                                                           | V <sub>IL</sub> /V <sub>IH</sub><br>Input Levels | V <sub>IL</sub> /V <sub>IH</sub><br>Timing Level | V <sub>OL</sub> /V <sub>OH</sub><br>Timing Level | I <sub>OL</sub> /I <sub>OH</sub> |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------|

| $\begin{array}{l} \text{4.5V} \leq \text{V}_{\text{CC}} \\ \leq \text{5.5V} \\ \text{(TTL Levels)} \end{array}$ | 0.4V/2.4V                                        | 1.0V/2.0V                                        | 0.4V/2.4V                                        | −2.1 mA/<br>0.4 mA               |

Output Load: 1 TTL Gate ( $C_L = 100 \text{ pF}$ )

## **Functional Description**

The NM93CSxx EEPROM Family has 10 instructions as described below. All Data-In signals are clocked into the device on the low-to-high SK transition.

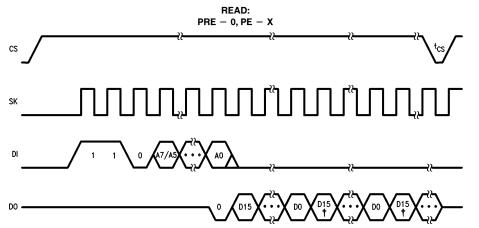

#### Read and Sequential Register Read (READ):

The READ instruction outputs serial data on the D0 pin. After a READ instruction is received, the instruction and address are decoded, followed by data transfer from the selected memory register into a 16-bit serial-out shift register. A dummy bit (logical 0) precedes the 16-bit data output string. Output data changes are initiated by a low to high transition of the SK clock. In the **sequential register read** mode of operation, the memory automatically cycles to the next register after each 16 data bits are clocked out. The dummy-bit is suppressed in this mode and a continuous string of data is obtained.

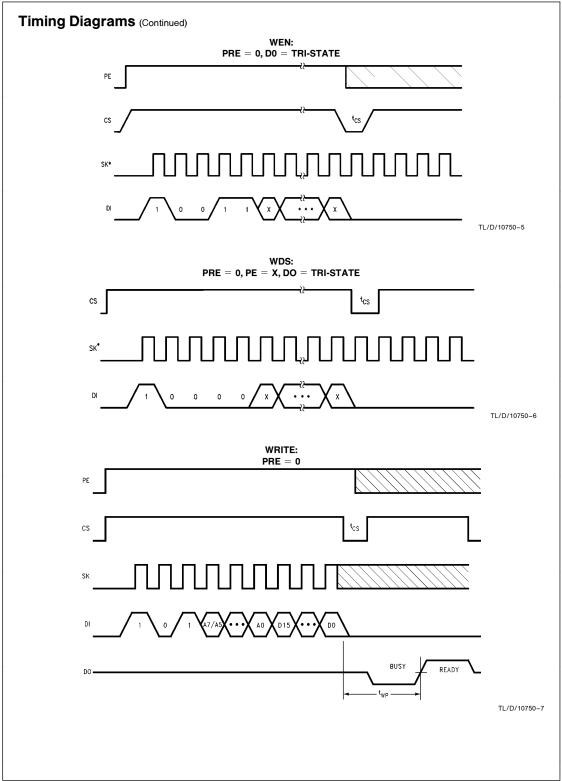

#### Write Enable (WEN):

When  $V_{CC}$  is applied to the part, it "powers up" in the Write Disable (WDS) state. Therefore, all programming modes must be preceded by a Write Enable (WEN) instruction. Once a Write Enable instruction is executed, programming remains enabled until a Write Disable (WDS) instruction is executed or  $V_{CC}$  is completely removed from the part.

#### Write (WRITE):

The WRITE instruction is followed by 16 bits of data to be written into the specified address. After the last bit of data is put on the data-in (DI) pin, CS must be brought low before the next rising edge of the SK clock. This falling edge of the CS initiates the self-timed programming cycle. The PE pin MUST be held high while loading the WRITE instruction, however, after loading the WRITE instruction the PE pin becomes a "don't care". The D0 pin indicates the READY/BUSY status of the chip if CS is brought high after the  $t_{\rm CS}$  interval. D0 = logical 0 indicates that programming is still in progress. D0 = logical 1 indicates that the register at the address specified in the instruction has been written with the data pattern specified in the instruction and the part is ready for another instruction.

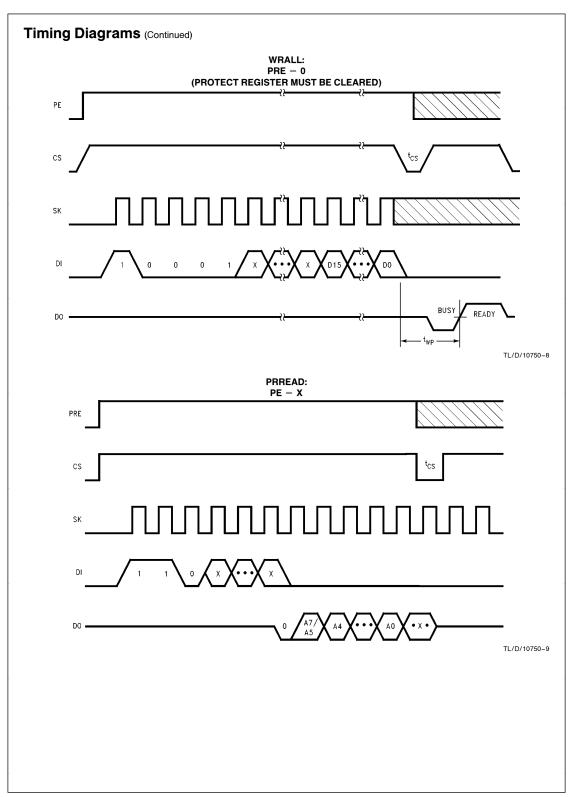

### Write All (WRALL):

The WRALL instruction is valid only when the Protect Register has been cleared by executing a PRCLEAR instruction. The WRALL instruction will simultaneously program all registers with the data pattern specified in the instruction. Like the WRITE instruction, the PE pin **MUST** be held high while loading the WRALL instruction, however, after loading the instruction the PE pin becomes a "don't care". As in the WRITE mode, the DO pin indicates the READY/BUSY status of the chip if CS is brought high after the  ${\rm tcs}$  interval. This function is DISABLED if the Protect Register is in use to lock out a section of memory.

## Write Disable (WDS):

To protect against accidental data disturb, the Write Disable (WDS) instruction disables all programming modes and should follow all programming operations. Execution of a READ instruction is independent of both the WEN and WDS instructions.

**Note:** For all Protect Register Operations: If the PRE pin is not held at  $V_{IH}$ , all instructions will be applied to the EEPROM array, rather than the Protect Register.

#### Protect Register Read (PRREAD):

The PRREAD instruction outputs the address stored in the Protect Register on the DO pin. The PRE pin **MUST** be held high while loading the instruction sequence. Following the PRREAD instruction the 6- or 8-bit address stored in the memory protect register is transferred to the serial out shift register. As in the READ mode, a dummy bit (logical 0) precedes the 6- or 8-bit address string.

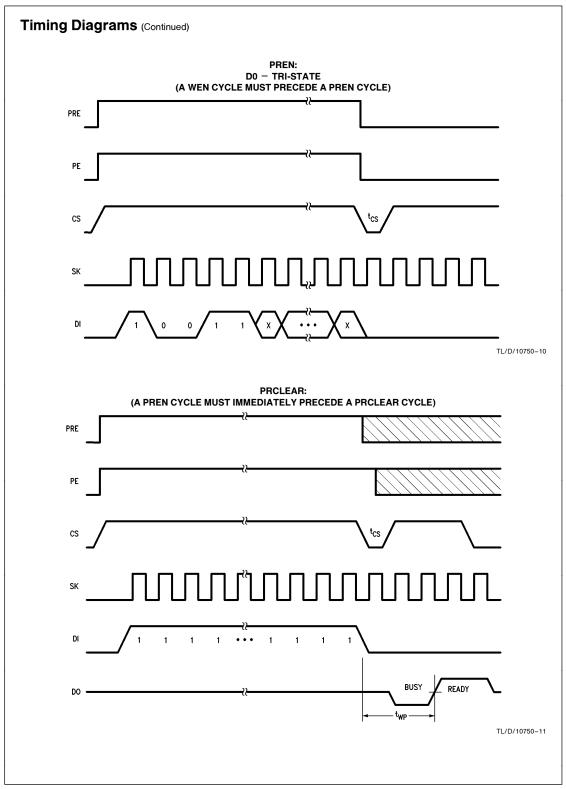

### Protect Register Enable (PREN):

The PREN instruction is used to enable the PRCLEAR, PRWRITE, and PRDS modes. Before the PREN mode can be entered, the part must be in the Write Enable (WEN) mode. Both the PRE and PE pins **MUST** be held high while loading the instruction sequence.

Note that a PREN instruction must **immediately** precede a PRCLEAR, PRWRITE, or PRDS instruction.

#### Protect Register Clear (PRCLEAR):

The PRCLEAR instruction clears the address stored in the Protect Register and, therefore, enables **all** registers for the WRITE and WRALL instruction. The PRE and PE pins **must** be held high while loading the instruction sequence, however, after loading the PRCLEAR instruction the PRE and PE pins become "don't care". Note that a PREN instruction must **immediately** precede a PRCLEAR instruction.

Please note that the PRCLEAR instruction and the PRWRITE instruction will both program the Protect Register with all 1s. However, the PRCLEAR instruction will allow the LAST register to be programmed, whereas the PRWRITE instruction = all 1s will PREVENT the last register from being programmed. In addition, the PRCLEAR instruction will allow the use of the WRALL command, where the PRWRITE = all 1s will lock out the Bulk programming operation.

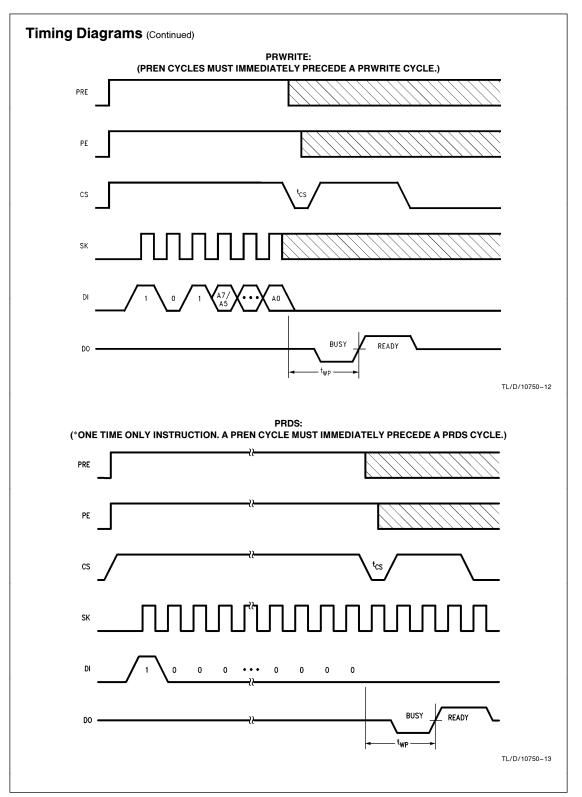

#### Protect Register Write (PRWRITE):

The PRWRITE instruction is used to write into the Protect Register the address of the first register to be protected. After the PRWRITE instruction is executed, all memory registers whose addresses are greater than or equal to the address specified in the Protect Register are protected from the WRITE operation. Note that before executing a PRWRITE instruction the Protect Register must first be cleared by executing a PRCLEAR operation and that the PRE and PE pins must be held high while loading the instruction, however, after loading the PRWRITE instruction the PRE and PE pins become 'don't care'. Note that a PREN instruction must immediately precede a PRWRITE instruction

#### Protect Register Disable (PRDS):

The PRDS instruction is a **ONE** TIME ONLY instruction which renders the Protect Register unalterable in the future. Therefore, the specified registers become **PERMANENTLY** protected against data changes. As in the PRWRITE instruction the PRE and PE pins **must** be held high while loading the instruction, and after loading the PRDS instruction the PRE and PE pins become "don't care".

Note that a PREN instruction must **immediately** precede a PRDS instruction.

| Instruction Set for the NM93CS06 and NM93CS46 |    |         |         |        |     |    |                                                                                                                                  |

|-----------------------------------------------|----|---------|---------|--------|-----|----|----------------------------------------------------------------------------------------------------------------------------------|

| Instruction                                   | SB | Op Code | Address | Data   | PRE | PE | Comments                                                                                                                         |

| READ                                          | 1  | 10      | A5-A0   |        | 0   | Х  | Reads data stored in memory, starting at specified address.                                                                      |

| WEN                                           | 1  | 00      | 11XXXX  |        | 0   | 1  | Enable all programming modes.                                                                                                    |

| WRITE                                         | 1  | 01      | A5-A0   | D15-D0 | 0   | 1  | Writes address if unprotected.                                                                                                   |

| WRALL                                         | 1  | 00      | 01XXXX  | D15-D0 | 0   | 1  | Writes all registers. Valid only when Protect Register is cleared.                                                               |

| WDS                                           | 1  | 00      | 00XXXX  |        | 0   | Х  | Disables all programming modes.                                                                                                  |

| PRREAD                                        | 1  | 10      | XXXXXX  |        | 1   | Х  | Reads address stored in Protect Register.                                                                                        |

| PREN                                          | 1  | 00      | 11XXXX  |        | 1   | 1  | Must immediately precede PRCLEAR, PRWRITE, and PRDS instructions.                                                                |

| PRCLEAR                                       | 1  | 11      | 111111  |        | 1   | 1  | Clears the Protect Register so that no registers are protected from WRITE.                                                       |

| PRWRITE                                       | 1  | 01      | A5-A0   |        | 1   | 1  | Programs address into Protect Register. Thereafter, memory addresses ≥ the address in Protect Register are protected from WRITE. |

| PRDS                                          | 1  | 00      | 000000  |        | 1   | 1  | ONE TIME ONLY instruction after which the address in the Protect Register cannot be altered.                                     |

Note: Address bits A5 and A4 become "Don't Care" for the NM93CS06.

## Instruction Set for the NM93CS56 and NM93CS66

| Instruction | SB | Op Code | Address  | Data   | PRE | PE | Comments                                                                                                                         |

|-------------|----|---------|----------|--------|-----|----|----------------------------------------------------------------------------------------------------------------------------------|

| READ        | 1  | 10      | A7-A0    |        | 0   | Х  | Reads data stored in memory, starting at specified address.                                                                      |

| WEN         | 1  | 00      | 11XXXXXX |        | 0   | 1  | Enable all programming modes.                                                                                                    |

| WRITE       | 1  | 01      | A7-A0    | D15-D0 | 0   | 1  | Writes address if unprotected.                                                                                                   |

| WRALL       | 1  | 00      | 01XXXXXX | D15-D0 | 0   | 1  | Writes all registers. Valid only when Protect Register is cleared.                                                               |

| WDS         | 1  | 00      | 00XXXXXX |        | 0   | Х  | Disables all programming modes.                                                                                                  |

| PRREAD      | 1  | 10      | XXXXXXX  |        | 1   | Х  | Reads address stored in Protect Register.                                                                                        |

| PREN        | 1  | 00      | 11XXXXXX |        | 1   | 1  | Must immediately precede PRCLEAR, PRWRITE, and PRDS instructions.                                                                |

| PRCLEAR     | 1  | 11      | 11111111 |        | 1   | 1  | Clears the "protect register" so that no registers are protected from WRITE.                                                     |

| PRWRITE     | 1  | 01      | A7-A0    |        | 1   | 1  | Programs address into Protect Register. Thereafter, memory addresses ≥ the address in Protect Register are protected from WRITE. |

| PRDS        | 1  | 00      | 00000000 |        | 1   | 1  | ONE TIME ONLY instruction after which the address in the Protect Register cannot be altered.                                     |

Note: Address bit A7 becomes "Don't Care" for the NM93CS56.

TL/D/10750-15

STATUS VALID

$^\dagger \text{The memory automatically cycles to the next register with continued clocking of SK.}$

TL/D/10750-4

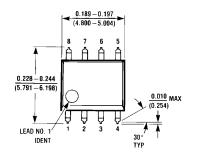

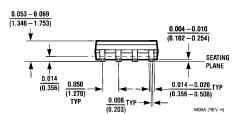

## Physical Dimensions inches (millimeters)

Molded Package, Small Outline, 0.15 Wide, 8-Lead (M8)

Order Number NM93CS06M8, NM93CS46M8 or NM93CS56M8

NS Package Number M08A

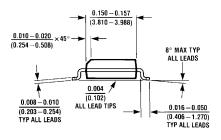

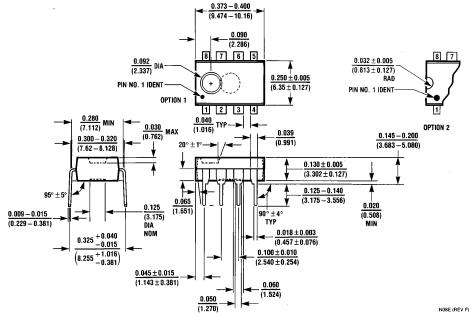

# Physical Dimensions inches (millimeters) (Continued)

Molded Dual-In-Line Package (N) Order Number NM93CS06N, NM93CS46N, NM93CS56 or NM93CS66N NS Package Number N08E

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: 1(800) 272-9959 TWX: (910) 339-9240

National Semiconductor GmbH Livry-Gargan-Str. 10 D-82256 Fürstenfeldbruck Germany Tel: (81-41) 35-0 Telex: 527649 Fax: (81-41) 35-1

National Semiconductor Japan Ltd. Sumitomo Chemical Engineering Center Bldg. 7F 1-7-1, Nakase, Mihama-Ku Chiba-City, Ciba Prefecture 261 Tel: (043) 299-2300 Fax: (043) 299-2500

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductores Do Brazil Ltda. Rue Deputado Lacorda Franco 120-3A Sao Paulo-SP Brazil 05418-000 Tel: (55-11) 212-5066 Telex: 391-1131931 NSBR BR Fax: (55-11) 212-1181 National Semiconductor (Australia) Pty, Ltd. Building 16 Business Park Drive Monash Business Park Nottinghill, Melbourne Victoria 3168 Australia Tel: (3) 558-9998 Fax: (3) 558-9998