## NMC9307 256-Bit Serial Electrically Erasable Programmable Memory

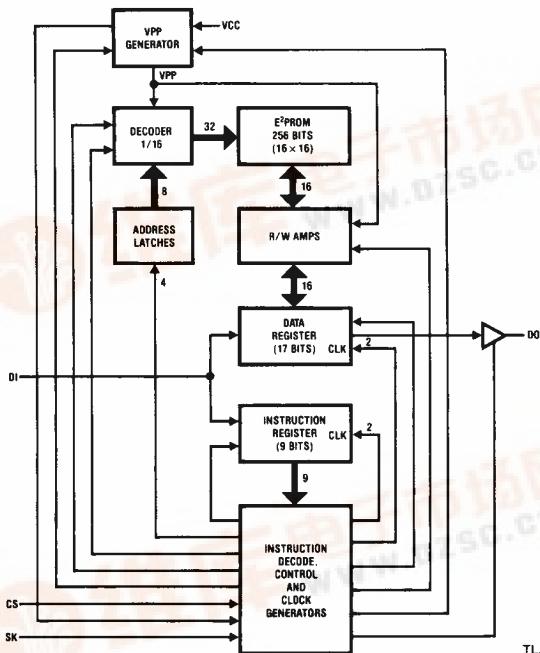

### General Description

The NMC9307 is a 256-bit non-volatile sequential access memory fabricated using advanced floating gate N-channel E2PROM technology. It is a peripheral memory designed for data storage and/or timing and is accessed via the simple MICROWIRE™ serial interface. The device contains 256 bits of read/write memory divided into 16 registers of 16 bits each. Each register can be serially read or written by a COP400 series controller. Bulk programming instructions (chip erase, chip write) can be enabled or disabled by the user for enhanced data protection. Written information is stored in a floating gate cell with at least 10 years data retention and can be updated by an erase-write cycle. The NMC9307 has been designed to meet applications requiring up to 40,000 erase/write cycles per register. A power down mode reduces power consumption by 70 percent.

### Features

- 40,000 erase/write cycles

- 10 year data retention

- Low cost

- Single supply operation (5V ± 10%)

- TTL compatible

- 16×16 serial read/write memory

- MICROWIRE compatible serial I/O

- Compatible with COP400 processors

- Low standby power

- Non-volatile erase and write

- Reliable floating gate technology

### Block and Connection Diagrams

TL/D/9204-1

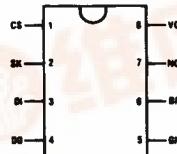

#### Dual-In-Line Package (N)

TL/D/9204-2

#### Top View

See NS Package Number N08E

#### SO Package (M)

TL/D/9204-3

#### Top View

See NS Package Number M14B

Note: Contact factory for SO8 availability.

#### Pin Names

|     |                    |

|-----|--------------------|

| CS  | Chip Select        |

| SK  | Serial Data Clock  |

| DI  | Serial Data Input  |

| DO  | Serial Data Output |

| VCC | Power Supply       |

| GND | Ground             |

## Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

|                                          |                 |

|------------------------------------------|-----------------|

| Voltage Relative to GND                  | +6V to -0.3V    |

| Ambient Operating Temperature<br>NMC9307 | 0°C to +70°C    |

| NMC9307E                                 | -40°C to +85°C  |

| Ambient Storage Temperature              | -65°C to +125°C |

Lead Temperature (Soldering, 10 sec.) 300°C

ESD Rating 2000V

**Note:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Electrical Characteristics

| Parameter                                            | Conditions                        | Part No | Min            | Max                 | Units    |

|------------------------------------------------------|-----------------------------------|---------|----------------|---------------------|----------|

| Operating Voltage (V <sub>CC</sub> )                 |                                   |         | 4.5            | 5.5                 | V        |

| Operating Current (I <sub>CC1</sub> )                | V <sub>CC</sub> = 5.5V, CS = 1    | 9307    |                | 10                  | mA       |

|                                                      |                                   | 9307E   |                | 12                  |          |

| Standby Current (I <sub>CC2</sub> )                  | V <sub>CC</sub> = 5.5V, CS = 0    | 9307    |                | 3                   | mA       |

|                                                      |                                   | 9307E   |                | 4                   |          |

| Input Voltage Levels                                 |                                   |         |                |                     |          |

| V <sub>IL</sub>                                      |                                   |         | -0.1           | 0.8                 | V        |

| V <sub>IH</sub>                                      |                                   |         | 2.0            | V <sub>CC</sub> + 1 | V        |

| Output Voltage Levels                                |                                   |         |                |                     |          |

| V <sub>OL</sub>                                      | I <sub>OL</sub> = 2.1 mA          |         |                | 0.4                 | V        |

| V <sub>OH</sub>                                      | I <sub>OH</sub> = -400 μA         |         | 2.4            |                     | V        |

| Input Leakage Current                                | V <sub>IN</sub> = 5.5V            |         |                | 10                  | μA       |

| Input Leakage Current<br>PINS 1, 2, 3<br>PIN 6       | V <sub>IN</sub> = 0 to 5.5V       |         |                | ±10<br>±50          | μA<br>μA |

| Output Leakage Current                               | V <sub>OUT</sub> = 5.5V, CS = 0   |         |                | 10                  | μA       |

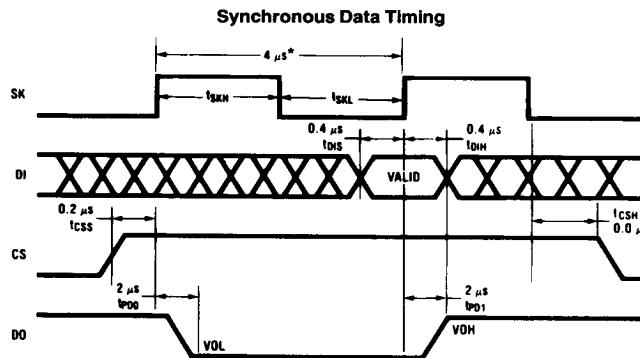

| SK Frequency                                         |                                   |         | 0              | 250                 | kHz      |

| SK HIGH TIME t <sub>SKH</sub> (Note 2)               |                                   |         | 1              |                     | μs       |

| SK LOW TIME t <sub>SKL</sub> (Note 2)                |                                   |         | 1              |                     | μs       |

| Input Set-Up and Hold Times                          |                                   |         |                |                     |          |

| CS                                                   | t <sub>CS</sub>                   |         | 0.2            |                     | μs       |

|                                                      | t <sub>CSH</sub>                  |         | 0              |                     | μs       |

| DI                                                   | t <sub>DIS</sub>                  |         | 0.4            |                     | μs       |

|                                                      | t <sub>DIH</sub>                  |         | 0.4            |                     | μs       |

| Output Delay                                         | CL = 100 pF                       |         |                |                     |          |

| DO                                                   | t <sub>PD1</sub>                  |         |                | 2                   | μs       |

|                                                      | t <sub>PD0</sub>                  |         |                | 2                   | μs       |

| Erase/Write Pulse Width (t <sub>E/W</sub> ) (Note 1) |                                   |         | 10             | 30                  | ms       |

| CS Low Time (t <sub>CS</sub> ) (Note 3)              |                                   |         | 1              |                     | μs       |

| Endurance                                            | Number of Data<br>Changes per Bit |         | 40,000 Typical |                     |          |

**Note 1:** t<sub>E/W</sub> measured to rising edge of SK or CS, whichever occurs last.

**Note 2:** The SK frequency spec. specifies a minimum SK clock period of 4 μs, therefore in an SK clock cycle, t<sub>SKH</sub> + t<sub>SKL</sub> must be greater than or equal to 4 μs. e.g. if t<sub>SKL</sub> = 1 μs then the minimum t<sub>SKH</sub> = 3 μs in order to meet the SK frequency specification.

**Note 3:** CS must be brought low for a minimum of 1 μs (t<sub>CS</sub>) between consecutive instruction cycles.

## Instruction Set

| Instruction | SB   | Op Code | Address  | Data     | Comments                |

|-------------|------|---------|----------|----------|-------------------------|

| READ        | 0, 1 | 10xx    | A3A2A1A0 |          | Read register A3A2A1A0  |

| WRITE       | 0, 1 | 01xx    | A3A2A1A0 | D15 – D0 | Write register A3A2A1A0 |

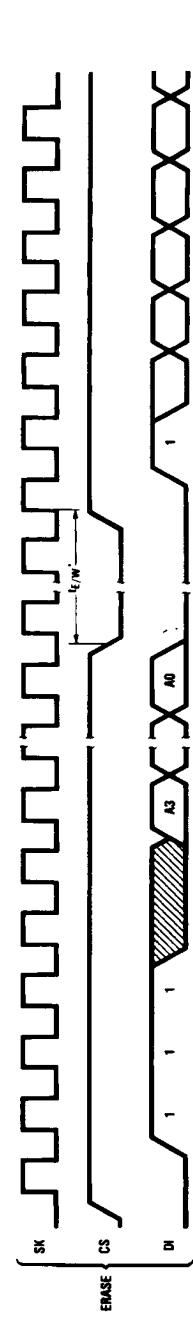

| ERASE       | 0, 1 | 11xx    | A3A2A1A0 |          | Erase register A3A2A1A0 |

| EWEN        | 0, 1 | 0011    | xxxx     |          | Erase/write enable      |

| EWDS        | 0, 1 | 0000    | xxxx     |          | Erase/write disable     |

| ERAL        | 0, 1 | 0010    | xxxx     |          | Erase all registers     |

| WRAL        | 0, 1 | 0001    | xxxx     | D15 – D0 | Write all registers     |

The NMC9307 has 7 instructions as shown. Note that MSB of any given instruction is a "1" and is viewed as a start bit in the interface sequence. The next 8 bits carry the op code and the 4-bit address for 1 of 16, 16-bit registers.

X is a don't care state.

## Functional Description

The NMC9307 is a small peripheral memory intended for use with COPSTM controllers and other non-volatile memory applications. The NMC9307 is organized as sixteen registers and each register is sixteen bits wide. The input and output pins are controlled by separate serial formats. Seven 9-bit instructions can be executed. The instruction format has a logical '1' as a start bit, four bits as an op code, and four bits of address. SK clock cycle is necessary after CS equals logical "1" before the instruction can be loaded. The on-chip programming-voltage generator allows the user to use a single power supply ( $V_{CC}$ ). Only during the read mode is the serial output (DO) pin valid. During all other modes the DO pin is in TRI-STATE®, eliminating bus contention.

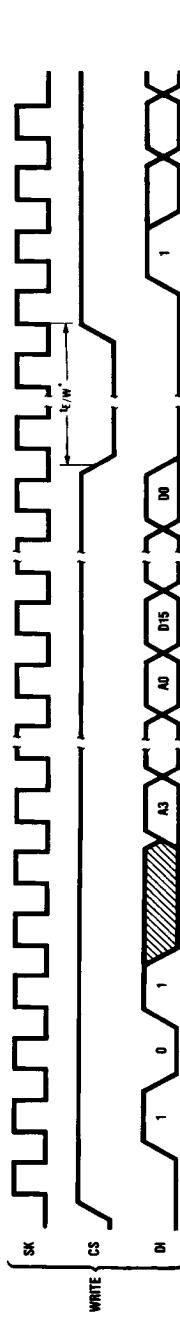

### READ

The read instruction is the only instruction which outputs serial data on the DO pin. After a READ instruction is received, the instruction and address are decoded, followed by data transfer from the memory register into a 16-bit serial-out shift register. A dummy bit (logical '0') precedes the 16-bit data output string. Output data changes are initiated by a low to high transition of the SK clock.

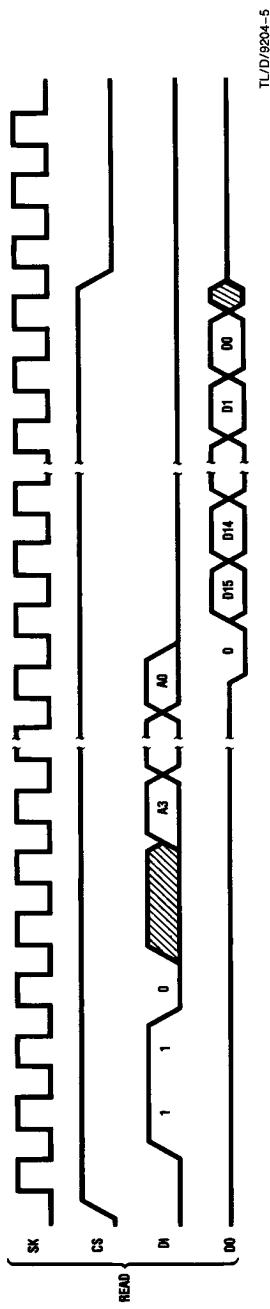

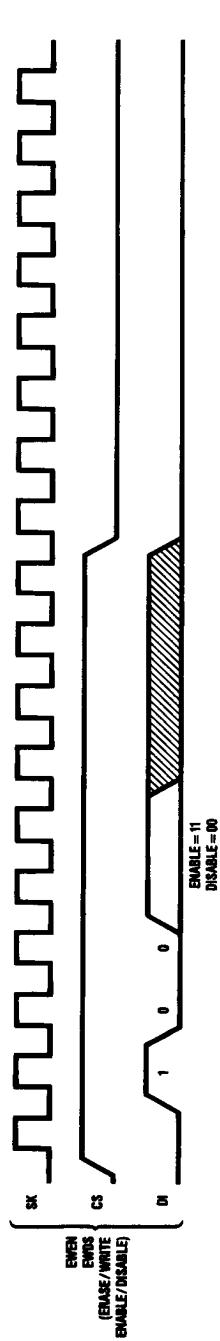

### ERASE/WRITE ENABLE AND DISABLE

Programming must be preceded once by a programming enable (EWEN) instruction. Programming remains enabled until a programming disable (EWDS) instruction is executed. The programming disable instruction is provided to protect against accidental data disturb. Execution of a READ instruction is independent of both EWEN and EWDS instructions.

### ERASE (Note 4)

Like most E2PROMS, the register must first be erased (all bits set to 1s) before the register can be written (certain bits set to 0s). After an ERASE instruction is input, CS is dropped low. This falling edge of CS determines the start of programming. The register at the address specified in the

instruction is then set entirely to 1s. When the erase/write programming time ( $t_{E/W}$ ) constraint has been satisfied, CS is brought up for at least one SK period. A new instruction may then be input, or a low-power standby state may be achieved by dropping CS low.

### WRITE (Note 4)

The WRITE instruction is followed by 16 bits of data which are written into the specified address. This register must have been previously erased. Like any programming mode, erase/write time is determined by the low state of CS following the instruction. The on-chip high voltage section only generates high voltage during these programming modes, which prevents spurious programming during other modes. When CS rises to  $V_{IH}$ , the programming cycle ends. All programming modes should be ended with CS high for one SK period, or followed by another instruction.

### CHIP ERASE (Note 4)

Entire chip erasing is provided for ease of programming. Erasing the chip means that all registers in the memory array have each bit set to a 1. Each register is then ready for a WRITE instruction. The chip erase (ERAL) instruction is ignored if the BPE pin is at  $V_{IL}$ , i.e., data is not changed.

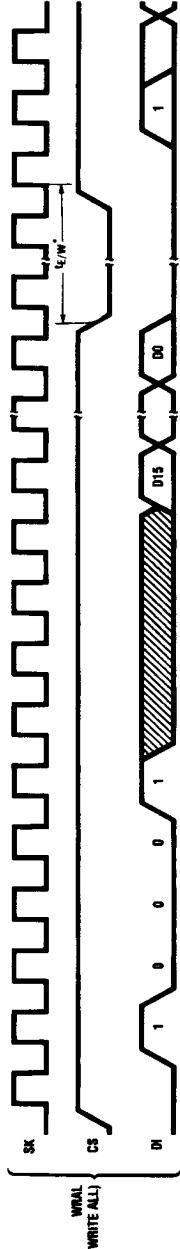

### CHIP WRITE (Note 4)

All registers must be erased before a chip write operation. The chip write cycle is identical to the write cycle, except for the different op code. All registers are simultaneously written with the data pattern specified in the instruction.

The chip write (WRAL) instruction is ignored if the BPE pin is at  $V_{IL}$ , i.e., the array data is not changed.

**Note 4:** During a programming mode (write, erase, chip erase, chip write), SK clock is only needed while the actual instruction, i.e., start bit, op code, address and data, is being input. It can remain deactivated during the Erase/Write pulse width ( $t_{E/W}$ ).

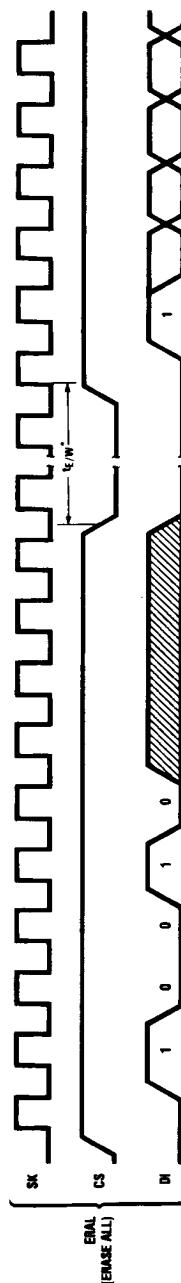

## Timing Diagrams

TL/D/9204-4

\*This is the minimum SK period

## Timing Diagrams (Continued)

## Instruction Timing

\* $t_{E/W}$  measured to rising edge of SK or CS, whichever occurs last.

## Timing Diagrams (Continued)

Instruction Timing (Continued)

TLD/9204-8

TLD/9204-9

TLD/9204-10

\* $t_{EV}$  measured to rising edge of SK or CS, whichever occurs last.