OMAP5910 Dual-Core Processor Silicon Errata

SPRZ016F August 2002 – Revised February 2006

# **REVISION HISTORY**

This revision history highlights the technical changes made to the SPRZ016E errata to make it an SPRZ016F revision.

### Scope: Added new Advisory

| PAGE(s)<br>NO. | ADDITIONS/CHANGES/DELETIONS |

|----------------|-----------------------------|

| 56             | Added Advisory MMC_12       |

# Contents

| 1 | Introduction      |                                                                                          | 7    |

|---|-------------------|------------------------------------------------------------------------------------------|------|

|   | 1.1 Device and I  | Development-Support Tool Nomenclature                                                    | 7    |

|   | 1.2 Device Mark   | ings                                                                                     | 8    |

| 2 | Important Notice  | es and Information About OMAP5910                                                        | 9    |

|   | 2.1 Useful Inform | nation Regarding TMS320C55xE Assembler Diagnostic Messages                               | 9    |

|   | 2.1.1 ERR         | OR Diagnostics                                                                           | 9    |

|   | 2.1.2 WAR         | NING Diagnostics                                                                         | 9    |

|   | 2.1.3 REM         | IARK Diagnostics                                                                         | 9    |

| 3 | Usage Notes       |                                                                                          | . 11 |

|   | Usage_Note_1:     | MPU Public/Private TIPB Strobe0 and 1 Frequency Limitation                               | 11   |

|   | Usage_Note_2:     | DSP TIPB Strobe1 and 2 Frequency Limitation                                              | 11   |

|   | Usage_Note_3:     | Configuring the MPUI Strobe                                                              | 12   |

|   | Usage_Note_4:     | ARMPER_CK Maximum Frequency                                                              | 13   |

|   | Usage_Note_5:     | DSP MMU Clock frequency limitations                                                      |      |

|   | Usage_Note_6:     | 13 MHz ULPD Clock                                                                        | 14   |

|   | Usage_Note_7:     | PLL Usage Recommendation                                                                 |      |

|   | Usage_Note_8:     | Clock Control and Configuration Guidelines.                                              |      |

|   | Usage_Note_9:     | Programming Guidelines for LCD Clock and Pixel Clock Frequencies                         |      |

|   | Usage_Note_10:    | USB_W2FC Suspend Functionality in HMC_MODE13 and HMC_MODE15                              | 18   |

|   | Usage_Note_11:    | Remote Wake Non-functional through TLL in HMC_MODEs 9, 10, 11, 12, 14,21, 23, 24, and 25 | 18   |

|   | Usage_Note_12:    | DMA Configuration Recommendations                                                        | 19   |

| 4 | DSP Subsystem     | Advisories                                                                               | . 20 |

|   | 4.1 DSP System    | Advisories                                                                               | . 20 |

|   | DSP_SYS_1         | Use Caution When Reading Following a Configuration Change on The DSP                     | 20   |

|   | 4.2 DSP DMA Ad    | lvisories                                                                                | . 20 |

|   | DSP_DMA_1         | DSP EMIF/DMA Port Hangs During EMIF Bus Error                                            | 20   |

|   | DSP_DMA_2         | DSP DMA IDLE Prevents Transfer Completion                                                | 21   |

|   | DSP_DMA_3         | Potential Deadlock in Burst Accesses                                                     | 21   |

|   | DSP_DMA_4         | DSP DMA IDLE and Transfer Completion                                                     | 22   |

|   | DSP_DMA_5         | DSP DMA Potential Deadlock in Burst Accesses                                             | 22   |

|   | 4.3 DSP ICACHE    | Advisories                                                                               | . 23 |

|   | DSP_ICACHE_1      | DSP Instruction Cache Two-Way Set-Associative Line Valid Bit Set Incorrectly             | 23   |

|   | DSP_ICACHE_2      | Two-Way Misses to the Same Line Can Become Corrupted                                     | 24   |

|   | DSP_ICACHE_3      | DSP ICACHE is Servicing a Missed Program Bus Request During a RAMSET Preload             | 27   |

|   |                   |                                                                                          |      |

|   | 4.4 DSP Emulation  | on Advisories                                                                                                    | 29 |

|---|--------------------|------------------------------------------------------------------------------------------------------------------|----|

|   | DSP_EMU_1          | Hardware Breakpoint Set on the Instruction Immediately Following a                                               |    |

|   |                    | Conditional Instruction Fails to Halt CPU                                                                        |    |

|   | DSP_EMU_2          | DSP IDLE Interrupt Not Serviced When Emulator is Connected                                                       |    |

|   |                    | on Advisories                                                                                                    |    |

|   | MPU_EMU_1          | The W2FC Data Register Should Not Be Read From The Emulator                                                      |    |

|   | 4.6 DSP Hardwar    | re Accelerator Advisories                                                                                        | 33 |

|   | DSP_HWA_1          | Pixel Interpolation Hardware Accelerator                                                                         | 33 |

|   | 4.7 DSP EMIF Ad    | lvisories                                                                                                        | 35 |

|   | DSP_EMIF_1         | DSP IDLE Wakeup With Program Code in External Memory and EMIF Domain in IDLE Hangs                               | 35 |

| 5 | MPU Subsystem      | Advisories                                                                                                       | 36 |

|   | 5.1 MPU System     | Advisories                                                                                                       | 36 |

|   | MPU_SYS_1          | Access Factor Must Be >1 for API Access to DSP Peripherals                                                       | 36 |

|   | 5.2 MPU Data-Ca    | che Advisories                                                                                                   | 36 |

|   | MPU_DCACHE_1       | Data Cache Transparent Mode Restriction During Copy-Back Operation                                               | 36 |

|   | MPU_DCACHE_2       | Data Cache Entry Operations With VA Depends On CleanCache Mode                                                   | 37 |

|   | 5.3 MPU Instruct   | ion Advisories                                                                                                   | 37 |

|   | MPU_INST_1         | Unpredictable Results After MCR Instructions                                                                     | 37 |

|   | 5.4 MPU DMA Ac     | lvisories                                                                                                        | 38 |

|   | MPU_DMA_3          | DMA Hardware Synchronized Channel is Not Disabled for TIPB Access<br>When DMA's Root Clock is Cut Off            | 38 |

|   | 5.5 System DMA     | Advisories                                                                                                       | 39 |

|   | SYS_DMA_1          | DMA Clocks Turned Off During Transfers Allows Corruption                                                         | 39 |

|   | SYS_DMA_2          | Pending System DMA Request Causes Erroneous Transfer                                                             | 39 |

|   | SYS_DMA_6          | System DMA Potential Deadlock in Burst Accesses                                                                  | 40 |

| 6 | Traffic Controlle  | r Subsystem Advisories                                                                                           | 41 |

|   | 6.1 Traffic Contro | oller (TC) Advisories                                                                                            | 41 |

|   | TC_1               | Traffic Controller ELRU Arbitration Does Not Work Properly                                                       | 41 |

|   | 6.2 EMIF Slow (E   | MIFS) Advisories                                                                                                 | 42 |

|   | EMIFS_1            | Burst Writes in EMIFS Causes Latency of Two TC Clock Cycles Extra<br>From the Second Data Write in the Data Path | 42 |

|   | EMIFS_2            | WELEN = 0 and FDIV = 1 With 16-Bit Memory                                                                        | 42 |

|   | EMIFS_3            | Minimum EMIFS Wait States for Proper Operation                                                                   | 43 |

|   | EMIFS_4            | FLASH.RDY Does Not Operate Correctly                                                                             |    |

|   | EMIFS_5            | Extra Flash Clock is Generated With FDIV4 and FDIV6 in Synchronous Mode                                          | 44 |

|   |                    |                                                                                                                  |    |

|   | 6.3 EMIF Fast (E  | MIFF) Advisories                                                                                | 45   |

|---|-------------------|-------------------------------------------------------------------------------------------------|------|

|   | EMIFF_1           | EMIFF Configuration Preventing Deep Sleep Entry                                                 | . 45 |

|   | EMIFF_2           | EMIFF MRS Request Could Be Lost                                                                 | . 47 |

|   | EMIFF_3           | EMIFF MRS Can Cause Read Failure                                                                | . 48 |

| 7 | OMAP5910 Perip    | oheral Advisories                                                                               | 49   |

|   | 7.1 LCD Advisor   | ies                                                                                             | 49   |

|   | LCD_1             | Missing Palette Loading Interrupt                                                               | . 49 |

|   | 7.2 UART Adviso   | pries                                                                                           | 50   |

|   | UART_1            | Software Flow Control Mode of UART1/2/3                                                         | . 50 |

|   | UART_2            | UART Clock Request Prevents Deep Sleep                                                          | . 50 |

|   | UART_3            | OSC_12M_SEL and EBLR Registers are not Readable                                                 | . 51 |

|   | UART_4            | UART1, 2, 3 RX Time-Out IRQ With No Status                                                      | . 51 |

|   | UART_5            | Incorrect Behavior of UART3 TX_EMPTY_CTL_IT Bit in SIR Mode                                     | . 52 |

|   | UART_6            | UART3 RX_LAST_BYTE Not Cleared Upon Read in the SIR_LSR Register                                |      |

|   | UART_7            | UART1/2/3 Sleep Mode                                                                            |      |

|   | UART_8            | FIFO LAST BYTE Interrupt in the UART_IRDA Peripheral is Not Reliable                            | . 54 |

|   | 7.3 MMC/SD Adv    | visories                                                                                        | 55   |

|   | MMC_1             | MMC/SD Does Not Support Stream Mode Reads                                                       | . 55 |

|   | MMC_2             | Stop Transmissions Command Cannot be Sent During Multi-Block Transfer of the MMC/SD Module . 55 |      |

|   | MMC_10            | SPI Mode on the MMC/SD Peripheral is Not Supported                                              |      |

|   | MMC_11            | MMC Exit Busy State With 16 Mbytes Card                                                         | . 56 |

|   | MMC_12            | MMC/SD Peripheral in SD 4 Wire Mode Gives the Same Performance as SD 1 Wire Mode .              | . 56 |

|   | 7.4 MICROWIRE     | Advisories                                                                                      | 56   |

|   | UWIRE_1           | Pulldown on the UWIRE.SDI Pin Needs to be Disabled by Software                                  | . 56 |

|   | UWIRE_2           | MICROWIRE Interface RX Data Failures Possible                                                   | . 57 |

|   | 7.5 I2C Advisorie | es                                                                                              | 58   |

|   | I2C_1             | I2C Prescalar Value of 0 Not Supported in Slave Mode                                            | . 58 |

|   | I2C_2             | Transfer Using Polling of I2C XRDY Bit Fails                                                    | . 59 |

|   | I2C_3             | Maximum SCL Frequency Configuration in I2C Master Mode With PSC = 1                             | . 60 |

|   | I2C_4             | Test Mode for Driving SCL Clock Does Not Work on the I2C Peripheral                             | . 60 |

|   | 7.6 USB Function  | n Advisories                                                                                    | 61   |

|   | USBF_1            | Read of USB Function Data Register Has a Side-Effect and Should Not be<br>Read From Emulator    | . 61 |

|   | USBF_2            | USB Function Suspend Functionality in HMC_MODE 13 and HMC_MODE 15                               | . 62 |

|   | USBF_3            | USB Function Double-Buffering Not Supported                                                     | . 62 |

|   |                   |                                                                                                 |      |

| 7.7 USB Host Ad  | dvisories                                                                                            | 63        |

|------------------|------------------------------------------------------------------------------------------------------|-----------|

| USBH_1           | Remote Wake Non-Functional Through TLL in HMC_Mode Settings 9, 10, 11, 12, 14, 21, 23, 24, and 25    | 63        |

| USBH 2           | Fast Multiple Accesses on EP_NUM Register in USB_W2F Can Cause                                       | 00        |

| CODII_2          | Failure Following USB Transactions                                                                   | 64        |

| 7.8 32K Timer A  | dvisories                                                                                            | 65        |

| TIMER_1          | 32K Timer Erroneous Interrupt                                                                        | 65        |

| TIMER_2          | Timer32K Reload TRB Bit Does Not Work Correctly                                                      | 66        |

| 7.9 MPUIO Advis  | sories                                                                                               | 67        |

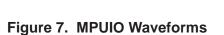

| MPUIO_1          | Latch of MPUIO INPUT_LATCH Register is Disabled During TIPB Read Access                              | 67        |

| MPUIO_2          | MPUIO GPIO_INT is no Longer Generated                                                                |           |

| MPUIO_3          | ARM_BOOT Multiplexing When MPU_RESET is Activated                                                    | 69        |

| 7.10 PWT Adviso  | ries                                                                                                 | 70        |

| PWT_1            | PWT Signal Can Stop in its High State                                                                | 70        |

| 7.11 Camera Inte | rface Advisories                                                                                     | 71        |

| CMR_1            | Shutdown of Camera Interface                                                                         | 71        |

| 7.12 HDQ/1-Wire  | Advisories                                                                                           | 72        |

| HDQ_1            | 1-Wire Interface is Susceptible to Locking-Up if Noise is Seen on the DQ Line<br>During IDLE Time 72 |           |

| OMAP5910 Devi    | ice/System-Level Advisories                                                                          | 73        |

| 8.1 System Advi  | isories                                                                                              | 73        |

| SYS_1            | Timeout Abort on a Posted-Write Access in the TIPB Bridge                                            | 73        |

| SYS_2            | Write Followed by Immediate Read Not Supported on Specific Addresses (TIPB Switch and PWT Module)    |           |

| SYS_3            | Impact on IDDC(0) Current if DSP Held in Reset Without Proper Initialization                         |           |

| SYS_5            | ARM BOOT Multiplexing When mpu_n_reset is Activated                                                  | 75        |

| SYS_6            | OMAP Cannot Go Into Chip_IDLE When the Internal Auto_Clock_Gating of the                             |           |

|                  | System DMA is Turned OFF                                                                             |           |

| Documentation    | Support 7                                                                                            | <b>76</b> |

|                  |                                                                                                      |           |

8

9

### 1 Introduction

This document describes the silicon updates to the functional specifications for the OMAP5910, silicon Revision J. Issues related to DSP operation are documented in the *TMS320C55x DSP CPU Programmer's Reference Supplement* (literature number SPRU652).

#### 1.1 Device and Development-Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all OMAP<sup>™</sup> processors and support tools. Each commercial OMAP platform member has one of three prefixes: X, P, or null (no prefix). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMDX) through fully qualified production devices/tools (TMDS).

Device development evolutionary flow:

- **X** Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow. (TMX definition)

- **P** Prototype device that is not necessarily the final silicon die and may not necessarily meet final electrical specifications. (TMP definition)

- **null** Production version of the silicon die that is fully qualified. (TMS definition)

Support tool development evolutionary flow:

TMDX Development support product that has not yet completed Texas Instruments internal qualification testing.

TMDS Fully qualified development support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Production devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (X or P), have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

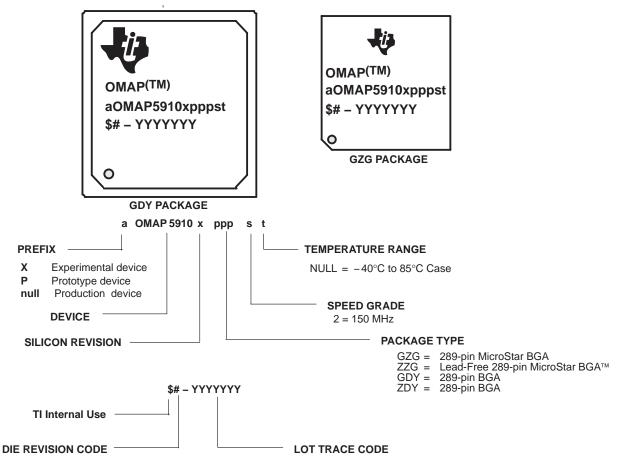

### 1.2 Device Markings

Figure 1 provides an example of the OMAP5910 device markings and defines each of the markings. The device revision can be determined by the symbols marked on the top of the package as shown in Figure 1. Some prototype devices may have markings different from those illustrated.

Figure 1. Example Markings for OMAP5910 Packages, Revision J

### 2 Important Notices and Information About OMAP5910

### 2.1 Useful Information Regarding TMS320C55x<sup>TM</sup> Assembler Diagnostic Messages

The TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSP assembler will generate three types of diagnostic messages when it detects a potential or probable Silicon Exception.

#### 2.1.1 ERROR Diagnostics

The assembler generates ERROR diagnostics in cases where it can fully determine that the code will cause a silicon exception to occur on hardware.

#### 2.1.2 WARNING Diagnostics

The assembler generates WARNING diagnostics in cases where it can fully determine that the code will cause a silicon exception to occur on hardware, but which, under certain circumstances, may not be an issue for the user.

### 2.1.3 REMARK Diagnostics

The assembler generates REMARK diagnostics in conditions where it can fully determine that the code may cause a silicon exception to occur on hardware, but the exception itself also depends on non-visible trigger conditions that the assembler has no knowledge of, such as whether interrupts are enabled.

Since the assembler cannot determine the state of these trigger conditions, it cannot know that the exception will affect this code. Therefore, it generates a REMARK to instruct the user to examine the code and evaluate whether this is a potential silicon exception situation. (Please see the following sections for how to suppress remarks in situations where you have determined that the other trigger conditions do not exist.)

#### Intended Treatment of REMARK Diagnostics

The intent of generating REMARK diagnostics is to inform the user that the code could potentially cause a silicon exception and that it should be reviewed by the user side by side with the trigger conditions and a determination be made whether the code is a potential silicon exception situation.

If the code is determined to be a potential silicon exception situation, users should modify their code to prevent that exception from occurring.

If users determine that their code will not cause a silicon exception based on the trigger conditions, then the REMARK that the assembler generates can be suppressed. There are two methods of doing so; please see the "Suppressing REMARK Diagnostics" section.

#### Suppressing REMARK Diagnostics

Once the user determines that a silicon exception REMARK diagnostic is not appropriate for the code as written, the REMARK diagnostic can be suppressed in one of the following ways.

- REMARK directives

- REMARK command-line options

TMS320C55x and C55x are trademarks of Texas Instruments.

#### **REMARK Directives:**

The .noremark.remark directives can be used to suppress the generation of a REMARK diagnostic for particular regions of code. The .noremark directive turns off the generation of a particular REMARK diagnostic. The .remark directive re-enables the generation of a particular REMARK diagnostic.

A '.noremark ##' (where ## is the remark id) directive is placed at the beginning of the region, and a '.remark ##' directive is placed at the end of the region.

**NOTE:** The .noremark.remark directive combination should always be placed around the entire region of code that participates in the potential silicon exception. Otherwise, spurious diagnostics may still be generated.

Additionally, the user has the option of disabling a silicon exception diagnostic for the entire file by placing just the .noremark directive at the top of the assembly file. However, this may be dangerous if, during inevitable code maintenance, the code is modified by someone not familiar with all the exception conditions. Please take great care when using the directives in this manner.

#### **REMARK Command-Line Options:**

The compiler shell (cl55) supports a command line option to suppress a particular REMARK diagnostic. The shell option –ar# (where # is the assembler's silicon exception id as described above) will suppress the named REMARK for the entire scope of all assembly files compiled with that command. Using the option –ar without a number will suppress all REMARK diagnostics.

Again, this may be dangerous if, during inevitable code maintenance, the code is modified by someone not familiar with all the silicon exception conditions. Please take great care when using the command-line REMARK options. Using the .noremark/.remark directives covering the shortest possible range of source lines is much safer.

### 3 Usage Notes

Usage Notes highlight and describe particular situations where the device's behavior may not match the presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### Usage\_Note\_1: MPU Public/Private TIPB Strobe0 and 1 Frequency Limitation

The frequency of the MPU Public and Private TIPB strobe0 and 1 are derived from the traffic controller clock or CLKM3 block. Both Strobe0 and Strobe1 frequencies must be less than or equal to 40 MHz.

The TIPB\_CNTL register bit fields [3:0] and [7:4] control the divide factor for strobe0/ strobe1 frequencies. The divide factor for both is shown below.

| BIT FIELD TIPB_CNTL [3:0] and [7:4] | MPU TIPB STROBE1 and STROBE2 FREQUENCY |

|-------------------------------------|----------------------------------------|

| 0                                   | TC Clk / 1                             |

| 1                                   | TC Clk / 2                             |

| 2                                   | TC Clk / 4                             |

| 3                                   | TC Clk / 6                             |

|                                     |                                        |

| 15                                  | TC Clk / 30                            |

#### Example:

If the TC clock is running at 70MHz, then the strobe divide factor should be set to 1. That is 70MHz / 2 = 35MHz which is less than 40MHz and meets the requirement.

#### Usage\_Note\_2: DSP TIPB Strobe1 and 2 Frequency Limitation

The strobe frequency for DSP peripherals is derived from the DSP clock or CLKM2 block and is configured by the control mode register (CMR). In the CMR, bits 5–3 control strobe1 frequency and bits 8–6 control strobe2 frequency. The frequency of these strobes should be less than or equal to 32 MHz. The divide factor for the strobes is shown below.

| BIT FIELD CMR [5:3] and [8:6] | DSP TIPB STROBE1 and STROBE2 FREQUENCY |

|-------------------------------|----------------------------------------|

| 0                             | DSP Clk / 2                            |

| 1                             | DSP Clk / 3                            |

| 2                             | DSP Clk / 4                            |

| 3                             | DSP Clk / 5                            |

| 4                             | DSP Clk / 6                            |

| 5                             | DSP Clk / 7                            |

| 6                             | DSP Clk / 8                            |

| 7                             | DSP Clk / 9                            |

#### Example:

If the DSP clock frequency is 120 MHz, then the bit fields should be set to a wait state of 2. That is 120 MHz / 4 = 30 MHz which meets the requirement. The bit fields should be programmed with a 010 binary.

When the DSP is in SAM (Shared Access Mode), the DSP clock is used as the input to the wait state generator that creates the DSP TIPB strobe1 and strobe2 signals. However, while the DSP is in HOM (Host Only Mode) the Strobe 1 and 2 are derived by the MPUI Strobe.

#### Usage\_Note\_3: Configuring the MPUI Strobe

When the MPU accesses the DSP memory or its peripherals it communicates via the MPUI port. The MPUI strobe clock is derived from the TC or CLKM3 block. If the DSP is in HOM mode, then the MPUI strobe is used for DSP peripheral access. The frequency of this strobe should be less than or equal to 24MHz The strobe frequency for the MPUI is controlled by the MPUI : CTRL\_REG bits 7–4. The divide factor for the strobes is shown below.

| BIT FIELD CNTL_REG [7:4] | MPUI STROBE FREQUENCY |

|--------------------------|-----------------------|

| 0                        | TC Clk / 1            |

| 1                        | TC Clk /2             |

| 2                        | TC Clk / 4            |

| 3                        | TC Clk / 6            |

|                          |                       |

| 15                       | TC Clk / 30           |

#### Example:

If the TC clock is configured to 60MHz then the access factor should be set to 2. That is 60MHz / 4 = 15MHz which is less than the required 24MHz. The bit field is to be programmed with a 010.

#### Usage\_Note\_4: ARMPER\_CK Maximum Frequency

The ARM peripheral clock frequency (ARMPER\_CK) is determined by dividing CK\_GEN1 by the value associated with the PERDIV[1:0] field of the ARM\_CKCTL register (0xFFFECE00). The permissible divisors are 1, 2, 4, or 8. For OMAP5910, the ARMPER\_CK frequency is limited to a maximum of 50MHz. Therefore, depending on the output frequency selected for CK\_GEN1, an appropriate divisor must be selected for PERDIV.

| BIT FIELD PERDIV | ARMPER_CK FREQUENCY |

|------------------|---------------------|

| 0                | DPLL1 Clk / 1       |

| 1                | DPLL1 Clk /2        |

| 2                | DPLL1 Clk / 4       |

| 3                | DPLL1 Clk / 8       |

#### Example:

If the frequency of CK\_GEN1 is 120MHz, then it is necessary to divide this clock by 4 to produce a 30MHz ARMPER\_CK. In this case, PERDIV[1:0] would be programmed to 10b.

#### Usage\_Note\_5 DSP MMU Clock frequency limitations

The DSPMMU clock must adhere to all the following rules:

- 1. DSPMMU clock frequency must ≥ traffic controller clock

- 2. DSPMMU clock frequency must be 1/2x or 1x the DSP clock

- 3. DSPMMU frequency should not be greater than max frequency of the traffic controller

#### Usage\_Note\_6 13 MHz ULPD Clock

A new feature has been added to the TMS OMAP5910 device allowing a 13MHz–clock reference to be used instead of a 12MHz–clock reference. The feature allows the APLL in the ULPD module to generate the required 48MHz–clock signal from either the 12MHz or 13MHz reference. When using the on–chip oscillator (normal mode), either a 12MHz crystal or a 13MHz crystal can be connected to the OSC1\_IN and OSC1\_OUT. In external master mode, the on–chip oscillator is disabled and a 12MHz or 13MHz reference clock must be provided by an external oscillator connected to the OSC1\_IN pin. In both of these cases, the APLL may be configured to generate the 48MHz clock from either a 12MHz or a 13MHz–clock. If a 13MHz–clock is used, then the APLL should be used to generate the 48MHz clock as opposed to using the ULPD DPLL. The ULPD DPLL can only generate a 48MHz clock when the reference is 12MHz.

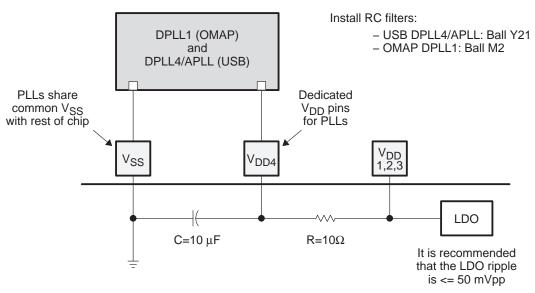

#### Usage\_Note\_7: PLL Usage Recommendation

To reduce jitter, minimize power supply noise on  $V_{DD4}$  and  $V_{DDA}$  by the use of filters or bypass capacitors. A potential solution is to use the following circuit:

#### Usage\_Note\_8: Clock Control and Configuration Guidelines.

OMAP CLK GLOBAL RULES: The following rules need to be followed while choosing any dividers for OMAP. For all clock modes:

- 1. TC cannot run faster than ARM.

- 2. TC cannot run faster than DSPMMU

- 3. DSP speed has to be 1x or 2x of DSPMMU

- 4. All dividers should be chosen not to exceed maximum physical speed limits for each domain.

GLOBAL RULES apply to all modes of operations. In addition to global rules, each clock mode and local rules outlined in the following. For each clock mode, both the global rules and its own local rules have to be followed.

Local rules for each clock mode are as follows:

#### Fully Synchronous Mode (ARM\_SYSST register, CLOCK\_SELECT[2:0] = 000b)

The following rules apply to fully synchronous mode:

- In fully synchronous mode ARM, TC, and DSPMMU must run at the same frequency.

- In fully synchronous mode, DSP Speed can be 1x or 2x of DSPMMU.

- Valid dividers for fully synchronous mode:

| Fully Synchronous Mode Dividers |        |         |         |  |

|---------------------------------|--------|---------|---------|--|

| ARM DIV                         | TC DIV | MMU DIV | DSP DIV |  |

| 00                              | 00     | 00      | 00      |  |

| 01                              | 01     | 01      | 00      |  |

| 01                              | 01     | 01      | 01      |  |

| 10                              | 10     | 10      | 01      |  |

| 10                              | 10     | 10      | 10      |  |

| 11                              | 11     | 11      | 10      |  |

| 11                              | 11     | 11      | 11      |  |

#### Synchronous Scalable Mode (ARM\_SYSST register, CLOCK\_SELECT[2:0] = 010b)

The following rules apply to synchronous scalable mode:

- In synchronous scalable mode, the ARM and DSPMMU must be at least a 2x multiple of TC.

- The ARM and DSPMMU can be the same or different multiples of each other (i.e., DSPMMU can be 2x and ARM can be 4x of TC).

- The DSPMMU cannot run faster than the maximum physical speed of the TC.

- Valid dividers for synchronous scalable mode:

SPRZ016F

| Usage Note 8: PLL Usage Recommendation (C | Continued) |

|-------------------------------------------|------------|

|-------------------------------------------|------------|

| ARM DIV | TC DIV | MMU DIV | DSP DIV |

|---------|--------|---------|---------|

| 00      | 01     | 00      | 00      |

| 00      | 10     | 00      | 00      |

| 00      | 10     | 01      | 00      |

| 00      | 10     | 01      | 01      |

| 01      | 10     | 01      | 00      |

| 01      | 10     | 01      | 01      |

| 00      | 11     | 00      | 00      |

| 00      | 11     | 01      | 00      |

| 00      | 11     | 01      | 01      |

| 00      | 11     | 10      | 01      |

| 00      | 11     | 10      | 10      |

| 01      | 11     | 01      | 00      |

| 01      | 11     | 01      | 01      |

| 01      | 11     | 10      | 01      |

| 01      | 11     | 10      | 10      |

| 10      | 11     | 10      | 01      |

| 10      | 11     | 10      | 10      |

Table 1. Synchronous Scalable Mode Dividers

#### Mixed Mode #3 (ARM\_SYSST register, CLOCK\_SELECT[2:0] = 100b)

The following rules apply to mixed mode #3:

- The ARM and TC must be at the same frequency

- The DSPMMU must be at least a 2x multiple of the TC.

- The DSPMMU cannot run faster than the maximum physical speed of the TC.

- Valid dividers for mixed mode #3:

SPRZ016F

Usage Note 8: PLL Usage Recommendation (Continued)

| ARM DIV | TC DIV | MMU DIV | DSP DIV |

|---------|--------|---------|---------|

| 01      | 01     | 00      | 00      |

| 10      | 10     | 00      | 00      |

| 10      | 10     | 01      | 00      |

| 10      | 10     | 01      | 01      |

| 11      | 11     | 00      | 00      |

| 11      | 11     | 01      | 00      |

| 11      | 11     | 01      | 01      |

| 11      | 11     | 10      | 01      |

| 11      | 11     | 10      | 10      |

Table 2. Mixed Mode #3 Dividers

#### Mixed Mode #4 (ARM\_SYSST register, CLOCK\_SELECT[2:0] = 111b)

The following rules apply to mixed mode #3:

- DSPMMU and TC must be at the same frequency

- ARM must be at least a 2x multiple of the TC.

- Valid dividers for mixed mode #4:

| ARM DIV | TC DIV | MMU DIV | DSP DIV |

|---------|--------|---------|---------|

| 01      | 01     | 01      | 00      |

| 00      | 01     | 01      | 01      |

| 00      | 10     | 10      | 01      |

| 00      | 10     | 10      | 10      |

| 01      | 10     | 10      | 01      |

| 01      | 10     | 10      | 10      |

| 01      | 11     | 11      | 10      |

| 01      | 11     | 11      | 11      |

| 10      | 11     | 11      | 10      |

| 10      | 11     | 11      | 11      |

| 00      | 11     | 11      | 10      |

| 00      | 11     | 11      | 11      |

#### Table 3. Mixed Mode #4 Dividers

#### Usage\_Note\_9: Programming Guidelines for LCD Clock and Pixel Clock Frequencies

#### General Rule:

The LCD clock divider and the Pixel clock divider are not designed to be modified while the LCD controller is on. There is no hardware synchronization handshaking between LCD output to panel (vysnc) and when to change the pixel clock or LCD functional clock frequencies. If you attempt to change these frequencies without turning off the LCD controller first, then be aware the pixel clock frequency will be changed somewhere in the middle of the current video frame.

However, depending upon the tolerance of the specific panel connected to the controller, here are some guidelines you should follow.

#### To change LCD Pixel Clock frequency:

#### Option 1:

• Change PCD value at any time, preferably using the DMS's led channel "End Of Frame" interrupt as a trigger (Not guaranteed to update before the next frame starts).

#### Option 2:

- Disable the LCD ControllerWait for the frame done interrupt (be sure frame done is not masked) of the LCD controller.

- Program the new PCD value

- Program the new TC and LCD frequencies (if needed)

- Re-enable the LCD controller

**NOTE:** Some panels will flicker when the LCD controller is disabled.

#### Usage\_Note\_10: USB\_W2FC Suspend Functionality in HMC\_MODE13 and HMC\_MODE15

When in HMC\_MODE13 or HMC\_MODE15, the TLL receives its suspend and pullup enable signals from the USB\_W2FC. In its default operating mode, the USB\_W2FC will not transition from suspend to enabled until it senses that it has successfully enabled the pullup. The TLL prioritizes its suspend input over its pullup enable input, so the TLL will not signal the presence of the pullup, and the USB\_W2FC cannot sense that it has enabled the pullup. The USB\_W2FC will not exit Suspend mode. Do not use transceiverless link logic with the USB\_W2FC and an external USB Host Controller. Use a transceiver-based solution instead.

# Usage\_Note\_11: Remote Wake Non-functional Through TLL in HMC\_MODEs 9, 10, 11, 12, 14, 21, 23, 24, and 25

When in HMC\_MODE 9, 10, 11, 12, 14, 21, 23, 24, or 25, the USB host will not receive remote wake from an external USB function controller connected to a transceiverless link logic. The external USB function controller cannot wake the USB link from suspend using remote wake. This does not affect other connectivity that does not use the transceiverless link logic.

1. Systems that do not use USB Remote wake through the transceiverless link logic may ignore this usage note.

- 2. Use a transceiver-based connection (may require use of a different HMC\_MODE or a different set of OMAP5910 pins).

- 3. Use an OMAP5910 GPIO pin and software monitoring to indicate when software should take the appropriate USB host controller port out of USB suspend.

- 4. Avoid putting the USB host port that uses the transceiverless link logic into USB suspend.

#### Usage\_Note\_12: DMA Configuration Recommendations

Table 4 shows how the DMACK\_REQ, IDLIF\_ARM and DMA\_autogating bits are to be configured for correct functionality and optimal power saving.

#### Table 4. NIL Configuration for DMACK\_REQ, IDLIF\_ARM, and DMA\_autogating Bits

| # | DMACK_REQ | IDLIF_ARM | Autogating_on | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---|-----------|-----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | 1         | Х         | 1             | DO NOT USE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2 | 0         | 1         | 1             | Use this only when:<br>the LCD is DISABLED and it is appropriate for the DMA to go<br>to IDLE mode when the ARM goes into IDLE mode.<br>Characteristics:<br>When the ARM goes into IDLE mode, the DMA goes into IDLE<br>mode if there is no activity on ports. The DMA will then stay in<br>IDLE mode until the ARM comes out of IDLE. Even a<br>hardware request cannot wake up the DMA from IDLE mode.<br>The hardware request is processed after the ARM comes out<br>of IDLE mode.<br><b>Note:</b> This mode must be used for OMAP to enter into CHIP<br>IDLE. This is the recommended mode. |

| 3 | 0         | 0         | 1             | Use this only when:<br>It is required for the DMA to process requests and transfer<br>data even when the ARM is in IDLE mode.<br>OR<br>the LCD is ENABLED.<br><b>Note:</b> For OMAP to go into CHIP IDLE, the LCD must be<br>DISABLED first, then the IDLIF_ARM bit must be set to 1<br>(case #2).                                                                                                                                                                                                                                                                                               |

#### NOTES:

- 1. DMACK\_REQ -> CLKM IDLECT2(8)

- 2. IDLIF\_ARM -> CLKMIDLECT1(6)

- 3. DMA\_autogating\_ON -> DMA GCR(3)

- 4. LCD ENABLE/DISABLE -> LCD Control Register (LCD\_EN)

# 4 DSP Subsystem Advisories

### 4.1 DSP System Advisories

| Advisory<br>DSP_SYS_1 | Use Caution When Reading Following a Configuration Change on The DSP                                                                                                                                                                                                                                      |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | All Revisions                                                                                                                                                                                                                                                                                             |

| Details:              | Within the C55x CPU, writes occur later in the pipeline than reads do. This allows reads from a later instruction to sometimes occur prior to the write of an earlier instruction.                                                                                                                        |

|                       | This can be a problem when the write is to a configuration register in a peripheral that affects the read. If the user intends to reads memory that can be affected by the new configuration it is recommended that the user read from the configuration register being programmed prior to memory reads. |

|                       | Reads from the TIPB interface are pipeline protected, so writes and reads of peripheral registers are not affected. Also, sequential writes to peripherals work correctly.                                                                                                                                |

| Workaround:           | After configuring a peripheral the software should ensure that the writes have completed prior to using that configuration. This can be done with a read from the last register written or waiting 3 cycles. This configuration constraint is common to pipeline architectures.                           |

|                       | This exception will not be fixed in future silicon revisions.                                                                                                                                                                                                                                             |

### 4.2 DSP DMA Advisories

| Advisory<br>DSP_DMA_1 | DSP EMIF/DMA Port Hangs During EMIF Bus Error                                                                                                                                                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | All Revisions                                                                                                                                                                                                                  |

| Details:              | If the EMIF times out on an access, the DSP will get a time-out bus-error interrupt. The time-out condition may also cause a DMA interrupt. During this DMA interrupt, the DMA will not time out and go into an unknown state. |

| Workaround:           | Whenever an EMIF bus error interrupt occurs, the software needs to RESET the DMA and reschedule the transfer.                                                                                                                  |

|                       | This exception will not be fixed in future silicon revisions.                                                                                                                                                                  |

| Advisory<br>DSP_DMA_2 | DSP DMA IDLE Prevents Transfer Completion                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | All Revisions                                                                                                                                                                                                                                                                                                                                                                                                |

| Details:              | When DSP peripherals are placed in IDLE, there is an internal hardware handshaking mechanism between the DSP and its peripherals that ensure that the IDLE can occur. If a DMA transfer is occurring, this handshaking is supposed to prevent IDLEing until after the transfer is complete. The DSP DMA, however, can go into IDLE during the middle of a transfer resulting in the transfer not completing. |

| Workaround:           | In order to enforce that all DMA transfers are complete before attempting to IDLE the DMA, the DMA status first needs to be checked. Afterwards, the DMA channels need to be disabled from which the IDLE instruction can then be safely executed.                                                                                                                                                           |

|                       | This exception will not be fixed in future silicon revisions.                                                                                                                                                                                                                                                                                                                                                |

| Advisory<br>DSP_DMA_3 | Potential Deadlock in Burst Accesses                                                                                                                                                                                                                                                                                                                                                                         |

| Revision(s) Affected: | All Revisions                                                                                                                                                                                                                                                                                                                                                                                                |

| Details:              | If a transfer is configured with burst enabled and any of the accessed addresses (notably start address) are not 4x32-bits aligned (i.e., byte address is not multiple of 16) then the DMA may deadlock and the transfer may never terminate.                                                                                                                                                                |

| Workaround:           | Configure start address, block size, frame size, element size and indexes such that all DMA burst accesses are made on 4x32-bits aligned addresses.                                                                                                                                                                                                                                                          |

|                       | This same functional limitation is present on the System DMA controller, but the programming restrictions stated in this workaround are documented in the <i>OMAP5910 Dual-Core Processor</i> System DMA Controller Reference Guide (literature number SPRU674).                                                                                                                                             |

|                       | This exception will not be fixed in future silicon revisions.                                                                                                                                                                                                                                                                                                                                                |

| Advisory<br>DSP_DMA_4 | DSP DMA IDLE and Transfer Completion                                                                                                                                                                                                                           |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | All Revisions                                                                                                                                                                                                                                                  |

| Details:              | When system peripherals are placed in IDLE, there is hardware handshaking to ensure that an IDLE can occur without any system consequences. The DSP DMA, however, can go into IDLE in the middle of a transfer. This may prevent the transfer from completing. |

| Workaround:           | In order to put the DSP DMA into IDLE after the completion of a transfer, the DSP DMA status needs to be checked and the channels need to be disabled. Then, the IDLE instruction can safely be executed.                                                      |

|                       | This exception will not be fixed in future silicon revisions.                                                                                                                                                                                                  |

| Advisory<br>DSP_DMA_5 | DSP DMA Potential Deadlock in Burst Accesses                                                                                                                                                                                                                    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | All Revisions                                                                                                                                                                                                                                                   |

| Details:              | If a DSP DMA transfer is configured with burst enabled and some of the accessed addresses (notably the start address) are not 4x32-bits aligned (i.e., byte address is not multiple of 16), then the DSP DMA may deadlock and the transfer may never terminate. |

| Workaround:           | Two workarounds are available:                                                                                                                                                                                                                                  |

|                       | <ol> <li>To use the DSP DMA for burst access on both source and destination, the start address,<br/>block size, frame size, element size and indexes must be set in such a way that all DMA<br/>accesses are made on 4x32-bit aligned addresses.</li> </ol>     |

|                       | <ol> <li>If the DSP DMA is configured for burst access on only one side (source or destination).<br/>Burst accesses do not need to be 4x32 bit aligned. On the side that does not use bursting,<br/>packing should be used for improved performance.</li> </ol> |

|                       | This exception will not be fixed in future silicon revisions.                                                                                                                                                                                                   |

### 4.3 DSP ICACHE Advisories

| Advisory                 | DCD Instruction Cooks Two May Sat Associative Line Valid Bit Sat Inserroathy                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advisory<br>DSP_ICACHE_1 | DSP Instruction Cache Two-Way Set-Associative Line Valid Bit Set Incorrectly                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Revision(s) Affected:    | Fixed in Revision J. Applicable to all other revisions.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Details:                 | Under an unlikely combination of events, there is a possibility for an instruction cache line valid<br>bit to be set incorrectly to valid while the instruction packet (data contained in the line) is not<br>actually correct. Thus, if there is ever a hit to this line, the instruction cache will return an<br>invalid instruction packet and the DSP could try to decode this invalid instruction packet. The<br>following configuration and events are necessary for this issue to occur: |  |  |

|                          | <ol> <li>DSP instruction cache is configured in 2-way, set-associative mode (note that neither<br/>direct mapped or RAMSET modes are affected by this issue).</li> </ol>                                                                                                                                                                                                                                                                                                                        |  |  |

|                          | 2. DSP, DSP_MMU, and TC clocks are the same frequency (synchronous with each other).                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                          | 3. DSP program is in either external SDRAM or internal RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                          | <ol> <li>The DSP instruction cache has been globally flushed during the invocation of a new<br/>program. (The DSP's program is changed and the cache is flushed.)</li> </ol>                                                                                                                                                                                                                                                                                                                    |  |  |

|                          | 5. And there is, particular to this condition, a combination of out-of-order DSP accesses to a cache line (speculative branch) and specific timing-related events.                                                                                                                                                                                                                                                                                                                              |  |  |

| Workaround:              | Due to the timing nature of the problem, the condition should not occur if the fill rate of the instruction cache is always 1/4th or lower the DSP frequency. It is possible to respect this constraint by observing the following rules:                                                                                                                                                                                                                                                       |  |  |

|                          | <ol> <li>The DSP program is located in either DSP internal SARAM/DARAM or external EMIFF<br/>(SDRAM) or EMIFS (FLASH, SRAM) memory space and not the internal 1.5M-bit RAM<br/>space.</li> </ol>                                                                                                                                                                                                                                                                                                |  |  |

|                          | 2. The Traffic Controller and DSP MMU clock rate are one-half or lower the DSP clock rate.<br>That is, the DSP should be running at twice or higher the frequency of the Traffic<br>Controller and DSP MMU. Because the external interfaces are 16 bits wide and the<br>instruction cache fills at 32 bit rate, the 1/4th fill rate constraint will be respected.                                                                                                                               |  |  |

| Advisory<br>DSP_ICACHE_2 | Two-Way Misses to the Same Line Can Become Corrupted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:    | All Revisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Details:                 | A failure may occur when a speculative branch occurs inside the DSP which coincides with a miss to the same line inside the I-cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                          | Within the C55x DSP core, the Instruction Buffer Queue (IBQ) always tries to stay several instruction fetches ahead of the decoder. Any time a conditional branch occurs within the DSP, the false condition would be to continue executing the next instruction, which is already in the IBQ. Therefore, in anticipation that the conditional test might be true, the IBQ sometimes fetches the instruction from the true condition as well. This allows for the necessary code to exist within the IBQ for quick access, regardless of whether the condition proves to be true or false. This operation of fetching the instructions for both true and false conditions is referred to as speculative fetching. |

|                          | Since instructions are fed into the IBQ 4 bytes per fetch, but are extracted from the IBQ at a variable rate of 1 to 6 bytes per instruction, the IBQ will stop fetching when it is sufficiently far ahead of the instruction decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                          | • For relative branches, a speculative fetch happens for offsets of 0x20 to 0x27.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                          | For absolute branches, speculative fetches always occur.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                          | <ul> <li>For conditional goto instructions, the IBQ (instruction buffer queue) will fetch<br/>the target address prior to the condition being evaluated.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                          | This failure exists if the speculative fetches and normal execution fetches miss within the same I-cache line as will be shown below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                          | Each I-cache line consists of 16 bytes, which are addressed in a sequence of 4 bytes, addressable on 4-byte boundaries.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                          | Consider the following program sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                          | if ( cond false ) goto A3<br>A1<br>A2<br>A3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                          | Typically, when A1 is returned from the I-cache, A2 is requested next. When the conditional goto is decoded, the DSP will request A3 for the speculative fetch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                          | The IBQ stores requests prior to decode, so many instructions can be fetched from the<br>I-cache prior to decode. While the IBQ is filling up and addresses are sequentially fetched,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

the address A1 is eventually requested.

Two-Way Misses to the Same Line Can Become Corrupted (Continued)

If the IBQ is sufficiently far ahead of the decoder, the DSP will stop fetching prior to requesting A2. If the conditional branch is decoded at this point, the speculative fetch will occur next, retrieving A3. The resulting order of fetches would then be A1–A3–A2.

If the test of the conditional branch results in a false condition and following occurs:

- -The resulting order of A1-A3-A2 matches one of the conditions listed below.

- -The instructions all exist within the same I-cache line.

- -The instruction request from the cache results in a cache miss.

Then the program may become corrupted.

| A1 | A3 | A2                                                |

|----|----|---------------------------------------------------|

| 0  | 0  | 8                                                 |

| 0  | 0  | С                                                 |

| 0  | 8  | 0                                                 |

| 0  | 8  | 4                                                 |

| 0  | С  | 0                                                 |

| 0  | С  | $4 \leftarrow$ This is the SW example used below. |

| 0  | С  | 8                                                 |

| 4  | 0  | С                                                 |

| 4  | 4  | C                                                 |

| 4  | С  | 0                                                 |

| 4  | С  | 4                                                 |

| 4  | С  | 8                                                 |

Addresses coinciding with this sequence will not necessarily cause a problem since the corner condition depends on the latency of the target memory and the time when the DSP issues the program request. In order to guarantee that this condition is not present, the following sequences need to be avoided. The hardware corner case is very rare (17 out of 100 million cycles of targeted random simulation) since it is based on protocol interactions between the DSP and target memory, IBQ state, and the I-cache line needs to be a miss. Of all of the theoretical values for A1, A2 and A3 within the same I-cache line, only those above have the potential to exhibit the error. However, since this corner case is difficult to isolate in software, speculative fetches need to be isolated entirely to avoid this condition.