# Inductorless Voltage Converter

The NCP7662 is a pin–compatible upgrade to the industry standard TC7660 charge pump voltage converter. It converts a +1.5 V to +15 V input to a corresponding -1.5 to -15 V output using only two low–cost capacitors, eliminating inductors and their associated cost, size and EMI.

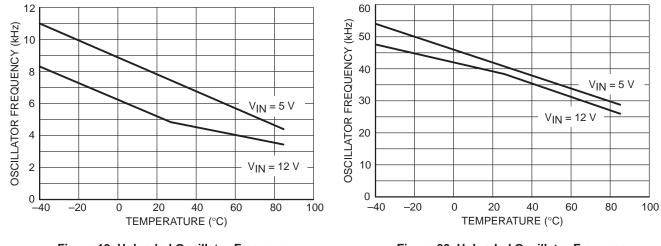

The on–board oscillator operates at a nominal frequency of 10 kHz. Frequency is increased to 35 kHz when pin 1 is connected to V+, allowing the use of smaller external capacitors. Operation below 10 kHz (for lower supply current applications) is also possible by connecting an external capacitor from OSC to ground (with pin 1 open).

The NCP7662 is available in both 8–pin DIP and 8–pin small outline (SO) packages in commercial and extended temperature ranges.

## Features

- Wide Operating Voltage Range: 1.5 V to 15 V

- Boost Pin (Pin 1) for Higher Switching Frequency

- High Power Efficiency is 96%

- Easy to Use Requires Only 2 External Non–Critical Passive Components

- Improved Direct Replacement for Industry Standard ICL7660 and Other Second Source Devices

## Applications

- Simple Conversion of +5 V to  $\pm 5$  V Supplies

- Voltage Multiplication  $V_{OUT} = \pm n V_{IN}$

- Negative Supplies for Data Acquisition Systems and Instrumentation

- RS232 Power Supplies

- Supply Splitter,  $V_{OUT} = \pm V_S/2$

# **ON Semiconductor**

http://onsemi.com

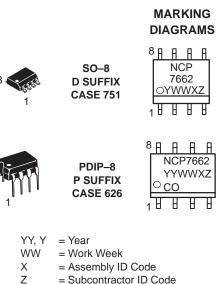

CO = Country of Orgin

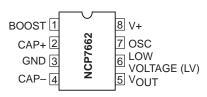

## PIN CONNECTIONS

## ORDERING INFORMATION

| Device     | Package | Shipping         |

|------------|---------|------------------|

| NCP7662DR2 | SO–8    | 2500 Tape & Reel |

| NCP7662P   | PDIP-8  | 50 Units/Rail    |

### **Functional Block Diagram**

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                          | Symbol | Value                                                                                     | Unit |

|-----------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------|------|

| Supply Voltage                                                  |        | +16.5                                                                                     | V    |

| LV, Boost and OSC Inputs Voltage (Note 1.) V+ $<5.5$ V $>5.5$ V |        | -0.3 V to (V <sup>+</sup> + 0.3 V)<br>(V <sup>+</sup> -5.5 V) to (V <sup>+</sup> + 0.3 V) | V    |

| Current into LV (Note 1.) $V^+ > 3.5 V$                         |        | 20                                                                                        | μΑ   |

| Output Short Duration<br>(VSUPPLY $\leq 5.5$ V)                 |        | Continuous                                                                                | V    |

| Power Dissipation (Note 2.)<br>Plastic DIP<br>SO                |        | 730<br>470                                                                                | mW   |

| Operating Temperature Range                                     |        | -40 to +85                                                                                | °C   |

| Storage Temperature Range                                       |        | -65 to +150                                                                               | °C   |

| Lead Temperature (Soldering, 10 sec)                            |        | +300                                                                                      | °C   |

Static-sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 1. Connecting any terminal to voltages greater than V+ or less than GND may cause destructive latch-up. It is recommended that no inputs from sources operating from external supplies be applied prior to "power up" of the NCP7662.

- 2. Derate linearly above 50°C by 5.5 mW/°C.

| Characteristics                                     | Test Conditions                                                                                                                                             | Symbol  | Min         | Тур          | Max               | Unit     |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|--------------|-------------------|----------|

| Supply Current (Note 3.)<br>(Boost Pin OPEN or GND) | $\begin{array}{r} R_{L} = \infty, +25^{\circ}C \\ 0^{\circ}C \leq T_{A} \leq +70^{\circ}C \\ -40^{\circ}C \leq T_{A} \leq +85^{\circ}C \end{array}$         | l+      | -<br>-<br>- | 80<br>-<br>- | 160<br>180<br>180 | μΑ       |

| Supply Current<br>(Boost Pin = V+)                  | $\begin{array}{l} 0^{\circ}C \ \leq \ T_{A} \ \leq \ +70^{\circ}C \\ -40^{\circ}C \ \leq \ T_{A} \ \leq \ +85^{\circ}C \end{array}$                         | l+      | -           |              | 300<br>350        | μA       |

| Supply Voltage Range, High (Note 4.)                | $\label{eq:RL} \begin{array}{l} R_{L} = 10 \ k\Omega, \\ LV \ Open, \ T_{MIN} \ \leq \ T_{A} \ \leq \ T_{MAX} \end{array}$                                  | V+H     | 3.0         | -            | 15                | V        |

| Supply Voltage Range, Low                           | $\label{eq:RL} \begin{array}{l} R_L = 10 \ k\Omega, \\ LV \mbox{ to GND}, \ T_{MIN} \ \leq \ T_A \ \leq \ T_{MAX} \end{array}$                              | V+L     | 1.5         | -            | 3.5               | V        |

| Output Source Resistance                            | $I_{OUT}$ = 20 mA, 0°C $\leq$ T <sub>A</sub> $\leq$ +70°C                                                                                                   | ROUT    | -           | 65           | 100               | Ω        |

|                                                     | $I_{OUT} = 20 \text{ mA}, -40^{\circ}\text{C} \le T_{\text{A}} \le +85^{\circ}\text{C}$                                                                     |         | _           | -            | 120               |          |

|                                                     | $I_{OUT} = 3 \text{ mA}, V^+ = 2 \text{ V}, \text{ LV to GND},$<br>$0^{\circ}\text{C} \le \text{T}_{\text{A}} \le +70^{\circ}\text{C}$                      |         | -           | -            | 250               |          |

|                                                     | $\begin{split} I_{OUT} = 3 \text{ mA}, \ V^+ = 2 \text{ V}, \ LV \text{ to GND}, \\ -40^\circ\text{C} &\leq T_\text{A} &\leq +85^\circ\text{C} \end{split}$ |         | -           | -            | 300               |          |

| Oscillator Frequency                                | C <sub>OSC</sub> = 0, Pin 1 Open or GND<br>Pin 1 = V+                                                                                                       | fosc    | 5.0<br>_    | 10<br>35     |                   | kHz      |

| Power Efficiency                                    | $\begin{array}{l} R_{L}=5 \ k\Omega, \\ T_{MIN} \leq T_{A} \leq T_{MAX} \end{array}$                                                                        | PEff    | 96<br>95    | 96<br>97     | -                 | %        |

| Voltage Conversion Efficiency                       | RL= ∞                                                                                                                                                       | VOUTEff | 99          | 99.9         | -                 | %        |

| Oscillator Impedance                                | V <sup>+</sup> = 2 V<br>V <sup>+</sup> = 5 V                                                                                                                | ZOSC    | -           | 1.0<br>100   |                   | MΩ<br>kΩ |

3. In the test circuit, there is no external capacitor applied to pin 7. However, when the device is plugged into a test socket, there is usually a very small but finite stray capacitance present, of the order of 5 pF.

4. The NCP7662 can operate without an external diode over the full temperature and voltage range. This device will function in existing designs which incorporate an external diode with no degradation in overall circuit performance.

### DETAILED DESCRIPTION

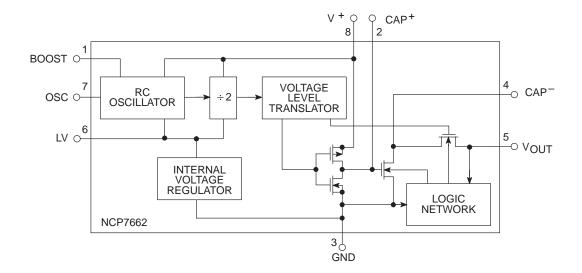

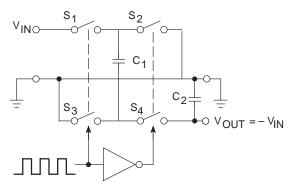

The NCP7662 contains all the necessary circuitry to complete a negative voltage converter, with the exception of two external capacitors which may be inexpensive 1  $\mu$ F polarized electrolytic types. The mode of operation of the device may be best understood by considering Figure 2, which shows an idealized negative voltage converter. Capacitor C<sub>1</sub> is charged to a voltage V+ for the half cycle when switches S<sub>1</sub> and S<sub>3</sub> are closed. (Note: Switches S<sub>2</sub> and S<sub>4</sub> are open during this half cycle.) During the second half cycle of operation, switches S<sub>2</sub> and S<sub>4</sub> are closed, with S<sub>1</sub> and S<sub>3</sub> open, thereby shifting capacitor C<sub>1</sub> negatively by V+ volts. Charge is then transferred from C<sub>1</sub> to C<sub>2</sub> such that the voltage on C<sub>2</sub> is exactly V+, assuming ideal switches and no load on C<sub>2</sub>. The NCP7662 approaches this ideal situation more closely than existing non–mechanical circuits.

In the NCP7662 the four switches of Figure 2 are MOS power switches; S<sub>1</sub> is a P–channel device and S<sub>2</sub>, S<sub>3</sub> and S<sub>4</sub> are N–channel devices. The main difficulty with this approach is that in integrating the switches, the substrates of S<sub>3</sub> and S<sub>4</sub> must always remain reverse biased with respect to their sources, but not so much as to degrade their "ON" resistances. In addition, at circuit start up, and under output short circuit conditions (V<sub>OUT</sub> = V+), the output voltage must be sensed and the substrate bias adjusted accordingly. Failure to accomplish this would result in high power losses and probable device latchup.

The problem is eliminated in the NCP7662 by a logic network which senses the output voltage ( $V_{OUT}$ ) together with the level translators, and switches the substrates of S<sub>3</sub> and S<sub>4</sub> to the correct level to maintain necessary reverse bias.

The voltage regulator portion of the NCP7662 is an integral part of the anti–latchup circuitry; however, its inherent voltage drop can degrade operation at low voltages. Therefore, to improve low voltage operation, the "LV" pin should be connected to GND, disabling the regulator. For supply voltages greater than 3.5 volts, the LV terminal must be left open to insure latchup proof operation and prevent device damage.

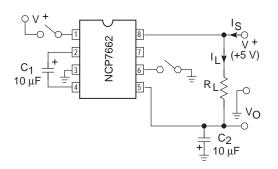

Figure 1. Test Circuit

## THEORETICAL POWER EFFICIENCY CONSIDERATIONS

In theory, a voltage converter can approach 100% efficiency if certain conditions are met:

- A. The drive circuitry consumes minimal power.

- B. The output switches have extremely low ON resistance and virtually no offset.

- C. The impedances of the pump and reservoir capacitors are negligible at the pump frequency.

The NCP7662 approaches these conditions for negative voltage conversion if large values of  $C_1$  and  $C_2$  are used. **Energy is lost only in the transfer of charge between capacitors if a change in voltage occurs.** The energy lost is defined by:

$$E = 1/2 C_1 (V_1^2 - V_2^2)$$

where  $V_1$  and  $V_2$  are the voltages on  $C_1$  during the pump and transfer cycles. If the impedances of  $C_1$  and  $C_2$  are relatively high at the pump frequency (refer to Figure 2) compared to the value of  $R_L$ , there will be a substantial difference in voltages  $V_1$  and  $V_2$ . Therefore, it is desirable not only to make  $C_2$  as large as possible to eliminate output voltage ripple, but also to employ a correspondingly large value for  $C_1$  in order to achieve maximum efficiency of operation.

#### Dos and Don'ts

- 1. Do not exceed maximum supply voltages.

- 2. Do not connect the LV terminal to GND for supply voltages greater than 3.5 volts.

- 3. Do not short circuit the output to V+ supply for voltages above 5.5 volts for extended periods; however, transient conditions including start–up are okay.

- 4. When using polarized capacitors in the inverting mode, the + terminal of C<sub>1</sub> must be connected to pin 2 of the NCP7662 and the – terminal of C<sub>2</sub> must be connected to GND.

- 5. If the voltage supply driving the NCP7662 has a large source impedance (25–30 ohms), then a 2.2  $\mu$ F capacitor from pin 8 to ground may be required to limit the rate of rise of the input voltage to less than 2 V/ $\mu$ s.

Figure 2. Idealized Negative Voltage Capacitor

## **TYPICAL APPLICATIONS**

#### Simple Negative Voltage Converter

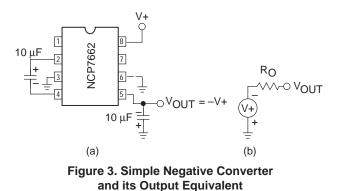

The majority of applications will undoubtedly utilize the NCP7662 for generation of negative supply voltages. Figure 3 shows typical connections to provide a negative supply where a positive supply of +1.5 V to +15 V is available. Keep in mind that pin 6 (LV) is tied to the supply negative (GND) for supply voltages below 3.5 volts.

The output characteristics of the circuit in Figure 3 can be approximated by an ideal voltage source in series with a resistance as shown in Figure 3b. The voltage source has a value of -(V+). The output impedance (R<sub>O</sub>) is a function of the ON resistance of the internal MOS switches (shown in Figure 2), the switching frequency, the value of C<sub>1</sub> and C<sub>2</sub>, and the ESR (equivalent series resistance) of C<sub>1</sub> and C<sub>2</sub>. A good first order approximation for R<sub>O</sub> is:

$$R_{O} \cong 2(R_{SW1} + R_{SW3} + ESR_{C1}) + 2(R_{SW2} + R_{SW4} + ESR_{C1}) + \frac{1}{f_{PUMP} \times C_1} + ESR_{C2}$$

$(f_{PUMP} = \frac{f_{OSC}}{2}, R_{SWX} = MOSFET \text{ switch resistance})$

Combining the four  $R_{SWX}$  terms as  $R_{SW}$ , we see that:

$$R_{O} \cong 2 \times R_{SW} + \frac{1}{f_{PUMP} \times C_{1}} + 4 \times ESR_{C1} + ESR_{C2}\Omega$$

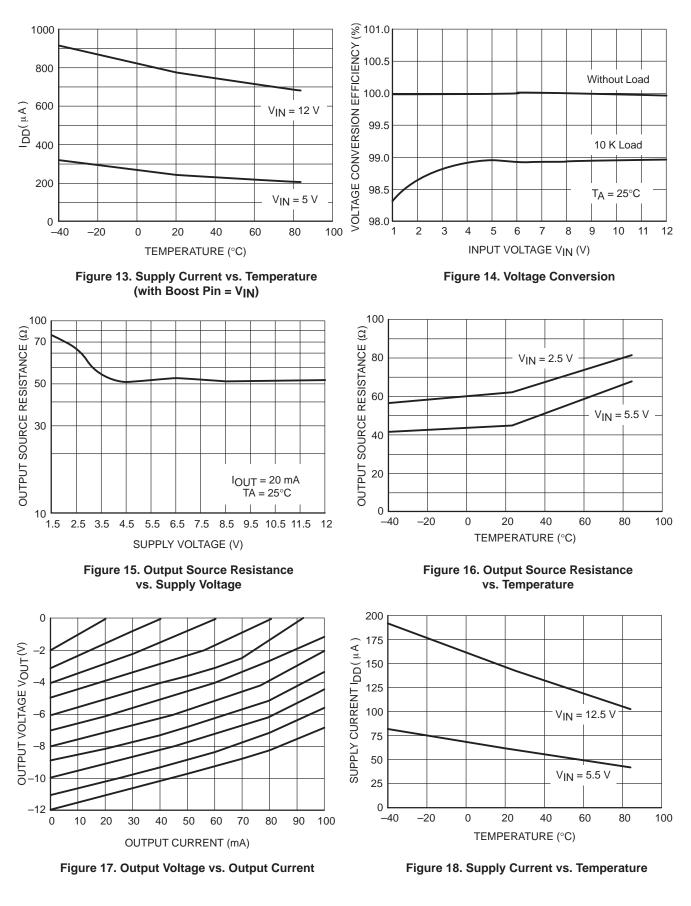

R<sub>SW</sub>, the total switch resistance, is a function of supply voltage and temperature (see the Output Source Resistance graphs), typically 23  $\Omega$  at +25°C and 5 V. Careful selection of C<sub>1</sub> and C<sub>2</sub> will reduce the remaining terms, minimizing the output impedance. High value capacitors will reduce the 1/(fpUMP × C<sub>1</sub>) component, and low ESR capacitors will lower the ESR term. Increasing the oscillator frequency will reduce the 1/(fpUMP × C<sub>1</sub>) term, but may have the side effect of a net increase in output impedance when C<sub>1</sub> > 10  $\mu$ F and there is not enough time to fully charge the capacitors every cycle. In a typical application when fOSC = 10 kHz and C = C<sub>1</sub> = C<sub>2</sub> = 10  $\mu$ F:

$$R_{O} \cong 2 \times 23 + \frac{1}{5 \times 10^{3} \times 10 \times 10^{-6})}$$

$$+ 4 \times ESR_{C1} + ESR_{C2}$$

$$R_{O} \cong (46 + 20 + 5 \times ESR_{C})\Omega$$

Since the ESRs of the capacitors are reflected in the output impedance multiplied by a factor of 5, a high value could potentially swamp out a low  $1/(f_{PUMP} \times C_1)$  term, rendering an increase in switching frequency or filter capacitance ineffective. Typical electrolytic capacitors may have ESRs as high as 10  $\Omega$ .

#### **Output Ripple**

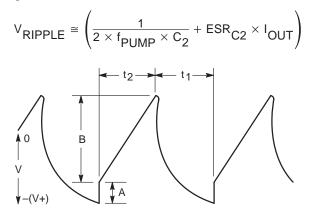

ESR also affects the ripple voltage seen at the output. The total ripple is determined by 2 voltages, A and B, as shown in Figure 4. Segment A is the voltage drop across the ESR of C<sub>2</sub> at the instant it goes from being charged by C<sub>1</sub> (current flowing into C<sub>2</sub>) to being discharged through the load (current flowing out of C<sub>2</sub>). The magnitude of this current change is  $2 \times I_{OUT}$ , hence the total drop is  $2 \times I_{OUT} \times ESR_{C2}$  volts. Segment B is the voltage change across C<sub>2</sub> during time t<sub>2</sub>, the half of the cycle when C<sub>2</sub> supplies current to the load. The drop at B is  $I_{OUT} \times t_2/C_2$  volts. The peak–to–peak ripple voltage is the sum of these voltage drops:

Figure 4. Output Ripple

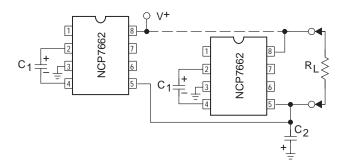

#### **Paralleling Devices**

Any number of NCP7662 voltage converters may be paralleled to reduce output resistance (Figure 5). The reservoir capacitor,  $C_2$ , serves all devices, while each device requires its own pump capacitor,  $C_1$ . The resultant output resistance would be approximately:

$$R_{OUT} = \frac{R_{OUT} \text{ (of NCP7662)}}{n \text{ (number of devices)}}$$

Figure 5. Paralleling Devices

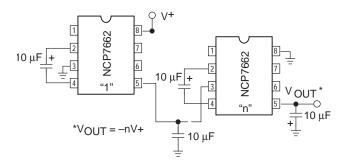

#### **Cascading Devices**

The NCP7662 may be cascaded as shown to produce larger negative multiplication of the initial supply voltage. However, due to the finite efficiency of each device, the practical limit is 10 devices for light loads. The output voltage is defined by:

$$V_{OUT} = -n(V_{IN})$$

where n is an integer representing the number of devices cascaded. The resulting output resistance would be approximately the weighted sum of the individual NCP7662 ROUT values.

Figure 6. Cascading Devices for Increased Output Voltage

#### Changing the NCP7662 Oscillator Frequency

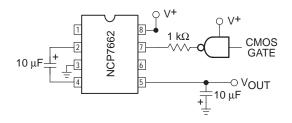

It may be desirable in some applications (due to noise or other considerations) to increase the oscillator frequency. This is achieved by one of several methods described below:

By connecting the Boost Pin (Pin 1) to V+, the oscillator charge and discharge current is increased and, hence the oscillator frequency is increased by approximately 3-1/2times. The result is a decrease in the output impedance and ripple. This is of major importance for surface mount applications where capacitor size and cost are critical. Smaller capacitors, e.g., 0.1 µF, can be used in conjunction with the Boost Pin in order to achieve similar output currents compared to the device free running with  $C_1 = C_2 = 1 \mu F$  or 10 µF. (Refer to graph of Output Source Resistance as a Function of Oscillator Frequency).

Increasing the oscillator frequency can also be achieved by overdriving the oscillator from an external clock as shown in Figure 7. In order to prevent device latchup, a 1 k $\Omega$  resistor must be used in series with the clock output. In a situation where the designer has generated the external clock frequency using TTL logic, the addition of a 10 k $\Omega$  pullup resistor to V+ supply is required. Note that the pump frequency with external clocking, as with internal clocking, will be 1/2 of the clock frequency. Output transitions occur on the positive–going edge of the clock.

Figure 7. External Clocking

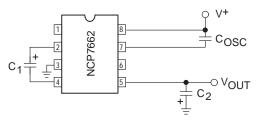

It is also possible to increase the conversion efficiency of the NCP7662 at low load levels by lowering the oscillator frequency. This reduces the switching losses, and is shown in Figure 8. However, lowering the oscillator frequency will cause an undesirable increase in the impedance of the pump (C<sub>1</sub>) and reservoir (C<sub>2</sub>) capacitors; this is overcome by increasing the values of C<sub>1</sub> and C<sub>2</sub> by the same factor that the frequency has been reduced. For example, the addition of a 100 pF capacitor between pin 7 (Osc) and V+ will lower the oscillator frequency to 1 kHz from its nominal frequency of 10 kHz (multiple of 10), and thereby necessitate a corresponding increase in the value of C<sub>1</sub> and C<sub>2</sub> (from 10 µF to 100 µF).

Figure 8. Lowering Oscillator Frequency

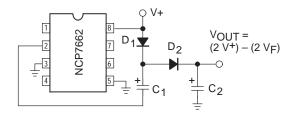

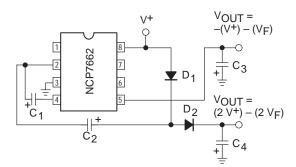

#### **Positive Voltage Doubling**

The NCP7662 may be employed to achieve positive voltage doubling using the circuit shown in Figure 9. In this application, the pump inverter switches of the NCP7662 are used to charge C<sub>1</sub> to a voltage level of V+ – V<sub>F</sub> (where V+ is the supply voltage and V<sub>F</sub> is the forward voltage on C<sub>1</sub> plus the supply voltage (V+) applied through diode D<sub>2</sub> to capacitor C<sub>2</sub>). The voltage thus created on C<sub>2</sub> becomes  $(2 V+) - (2 V_F)$ , or twice the supply voltage minus the combined forward voltage drops of diodes D<sub>1</sub> and D<sub>2</sub>.

The source impedance of the output (V<sub>OUT</sub>) will depend on the output current, but for V+=5 V and an output current of 10 mA, it will be approximately 60  $\Omega$ .

Figure 9. Positive Voltage Multiplier

# Combined Negative Voltage Conversion and Positive Supply Multiplication

Figure 10 combines the functions shown in Figures 3 and 9 to provide negative voltage conversion and positive voltage doubling simultaneously. This approach would be, for example, suitable for generating +9 V and -5 V from an existing +5 V supply. In this instance, capacitors C<sub>1</sub> and C<sub>3</sub> perform the pump and reservoir functions, respectively, for the generation of the negative voltage, while capacitors C<sub>2</sub> and C<sub>4</sub> are pump and reservoir, respectively, for the doubled positive voltage. There is a penalty in this configuration which combines both functions, however, in that the source impedances of the generated supplies will be somewhat higher due to the finite impedance of the common charge pump driver at pin 2 of the device.

#### Figure 10. Combined Negative Converter and Positive Doubler

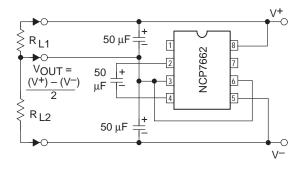

#### **Voltage Splitting**

The bidirectional characteristics can also be used to split a higher supply in half, as shown in Figure 11. The combined load will be evenly shared between the two sides and a high value resistor to the LV pin ensures start–up. Because the switches share the load in parallel, the output impedance is much lower than in the standard circuits, and higher currents can be drawn from the device. By using this circuit, and then the circuit of Figure 6, +15 V can be converted (via +7.5 V and -7.5 V) to a nominal -15 V, though with rather high series resistance ( $\sim 250 \Omega$ ).

Figure 11. Splitting a Supply in Half

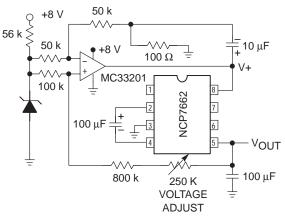

### **Regulated Negative Voltage Supply**

In some cases, the output impedance of the NCP7662 can be a problem, particularly if the load current varies substantially. The circuit of Figure 12 can be used to overcome this by controlling the input voltage, via the MC33201 op amp, in such a way as to maintain a nearly constant output voltage. Direct feedback is advisable, since the NCP7662's output does not respond instantaneously to change in input, but only after the switching delay. The circuit shown supplies enough delay to accommodate the NCP7662, while maintaining adequate feedback. An increase in pump and storage capacitors is desirable, and the values shown provide an output impedance of less than 5  $\Omega$ to a load of 10 mA.

Figure 12. Regulating the Output Voltage

Figure 19. Unloaded Oscillator Frequency vs. Temperature

Figure 20. Unloaded Oscillator Frequency vs. Temperature with Boost Pin = VIN

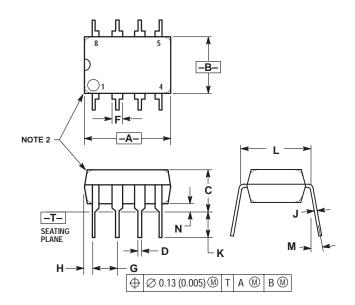

## PACKAGE DIMENSIONS

PDIP-8 **P SUFFIX** CASE 626-05 ISSUE K

NOTES: 1. DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL. 2. PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CORREFS). 3. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

|     | MILLIMETERS |       | INCHES    |       |  |

|-----|-------------|-------|-----------|-------|--|

| DIM | MIN         | MAX   | MIN       | MAX   |  |

| Α   | 9.40        | 10.16 | 0.370     | 0.400 |  |

| В   | 6.10        | 6.60  | 0.240     | 0.260 |  |

| С   | 3.94        | 4.45  | 0.155     | 0.175 |  |

| D   | 0.38        | 0.51  | 0.015     | 0.020 |  |

| F   | 1.02        | 1.78  | 0.040     | 0.070 |  |

| G   | 2.54 BSC    |       | 0.100 BSC |       |  |

| Н   | 0.76        | 1.27  | 0.030     | 0.050 |  |

| J   | 0.20        | 0.30  | 0.008     | 0.012 |  |

| K   | 2.92        | 3.43  | 0.115     | 0.135 |  |

| L   | 7.62        | BSC   | 0.300     | BSC   |  |

| Μ   |             | 10°   |           | 10°   |  |

| N   | 0.76        | 1.01  | 0.030     | 0.040 |  |

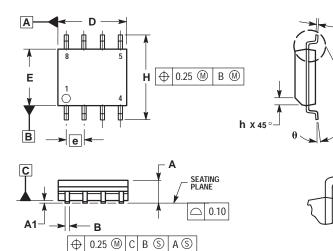

SO-8 **D SUFFIX** CASE 751-06 ISSUE T

С

NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

DIMENSION S ARE IN MILLIMETER.

DIMENSION D AND E DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 1.35        | 1.75 |  |

| A1  | 0.10        | 0.25 |  |

| В   | 0.35        | 0.49 |  |

| С   | 0.19        | 0.25 |  |

| D   | 4.80        | 5.00 |  |

| Е   | 3.80        | 4.00 |  |

| е   | 1.27 BSC    |      |  |

| Н   | 5.80        | 6.20 |  |

| h   | 0.25        | 0.50 |  |

| L   | 0.40        | 1.25 |  |

| θ   | 0 °         | 7 °  |  |

# **Notes**

**ON Semiconductor** and without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com Fax Response Line: 303–675–2167 or 800–344–3810 Toll Free USA/Canada

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor – European Support German Phone: (+1) 303–308–7140 (M–F 1:00pm to 5:00pm Munich Time)

Email: ONlit-german@hibbertco.com

- French Phone: (+1) 303–308–7141 (M–F 1:00pm to 5:00pm Toulouse Time) Email: ONlit-french@hibbertco.com

- English Phone: (+1) 303–308–7142 (M–F 12:00pm to 5:00pm UK Time) Email: ONlit@hibbertco.com

EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781 \*Available from Germany, France, Italy, England, Ireland

#### CENTRAL/SOUTH AMERICA:

Spanish Phone: 303–308–7143 (Mon–Fri 8:00am to 5:00pm MST) Email: ONlit–spanish@hibbertco.com

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support Phone: 303–675–2121 (Tue–Fri 9:00am to 1:00pm, Hong Kong Time) Toll Free from Hong Kong & Singapore: 001–800–4422–3781 Email: ONlit–asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031 Phone: 81–3–5740–2745 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com