## Features

- 22.8 SPECint95 (estimated), 17SPECfp95 at 500 MHz (estimated)

- 917MIPS at 500 MHz

- Selectable Bus Clock (14 CPU Bus Dividers Up To 9x)

- Seven Selectable Core-to-L2 Frequency Divisors

- Selectable 603 Interface Voltage Below 3.3V (1.8V, 2.5V)

- Selectable L2 interface of 1.8V or 2.5V

- $P_D$  Typical 5.3W at 500 MHz, Full Operating Conditions

- Nap, Doze and Sleep Modes for Power Saving

- Superscalar (Four Instructions fetched per Clock Cycle)

- 4 GB Direct Addressing Range

- Virtual Memory: 4 hexabytes ( $2^{52}$ )

- 64-bit Data and 32-bit Address Bus Interface

- 32 KB Instruction and Data Cache

- Eight Independent Execution Units and Three Register Files

- Write-back and Write-through Operations

- $f_{INT}$  Max = 450 MHz 500 MHz

- $f_{BUS}$  Max = 133 MHz

## Description

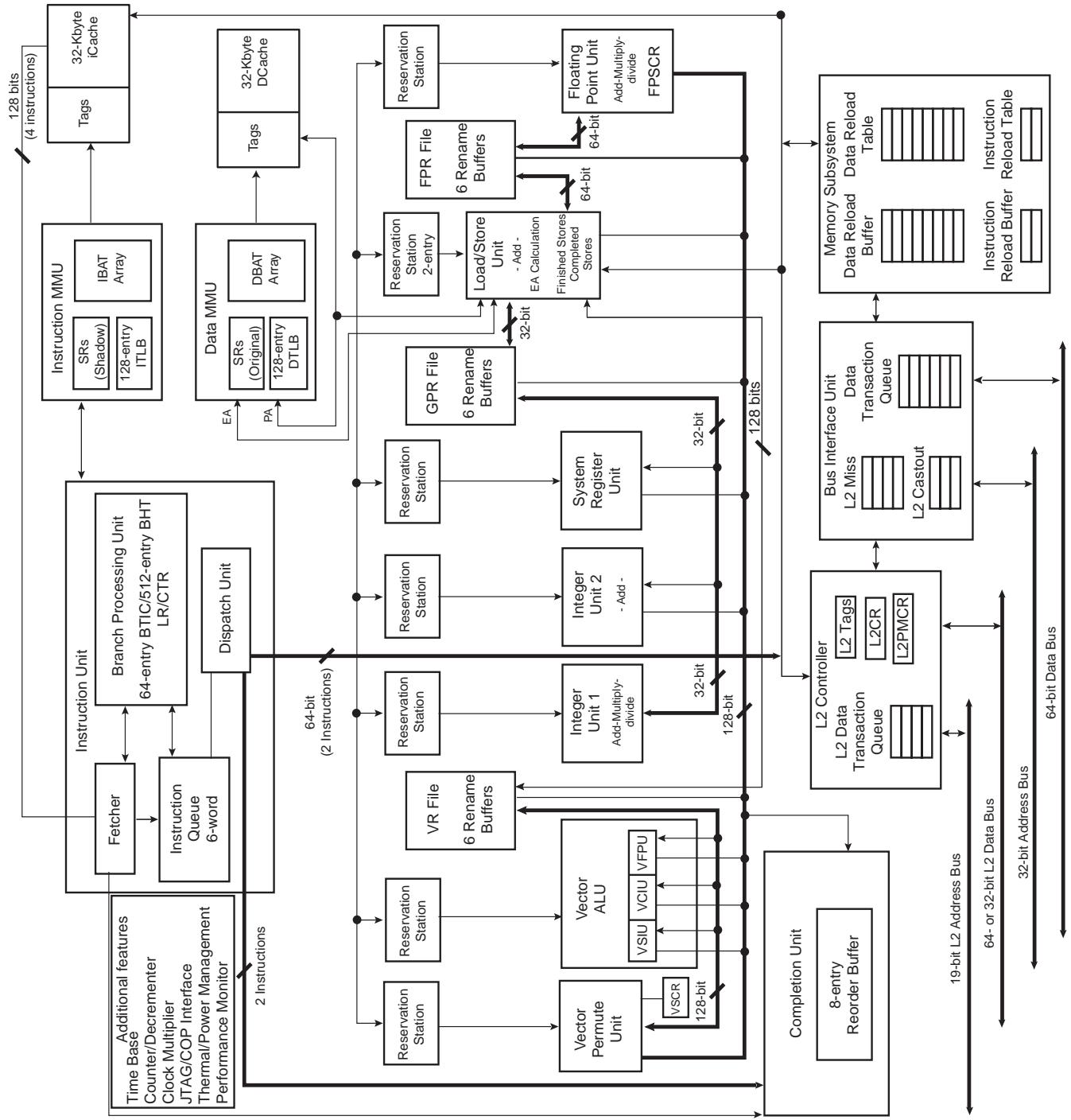

The PC7410 is the second microprocessor that uses the fourth (G4) full implementation of the PowerPC™ Reduced Instruction Set Computer (RISC) architecture. It is fully JTAG-compliant.

The PC7410 maintains some of the characteristics of G3 microprocessors:

- The design is superscalar, capable of issuing three instructions per clock cycle into eight independent execution units

- The microprocessor provides four software controllable power-saving modes and a thermal assist unit management

- The microprocessor has separate 32-Kbyte, physically-addressed instruction and data caches with dedicated L2 cache interface with on-chip L2 tags

In addition, the PC7410 integrates full hardware-based multiprocessing capability, including a 5-state cache coherency protocol (4 MESI states plus a fifth state for shared intervention) and an implementation of the new AltiVec™ technology instruction set.

New features have been developed to make latency equal for double-precision and single-precision floating-point operations involving multiplication. Additionally, in memory subsystem (MSS) bandwidth, the PC7410 offers an optional, high-bandwidth MPX bus interface.

Unlike the PC7400, the PC7410 does not support the 3.3V I/O on the L2 cache interface.

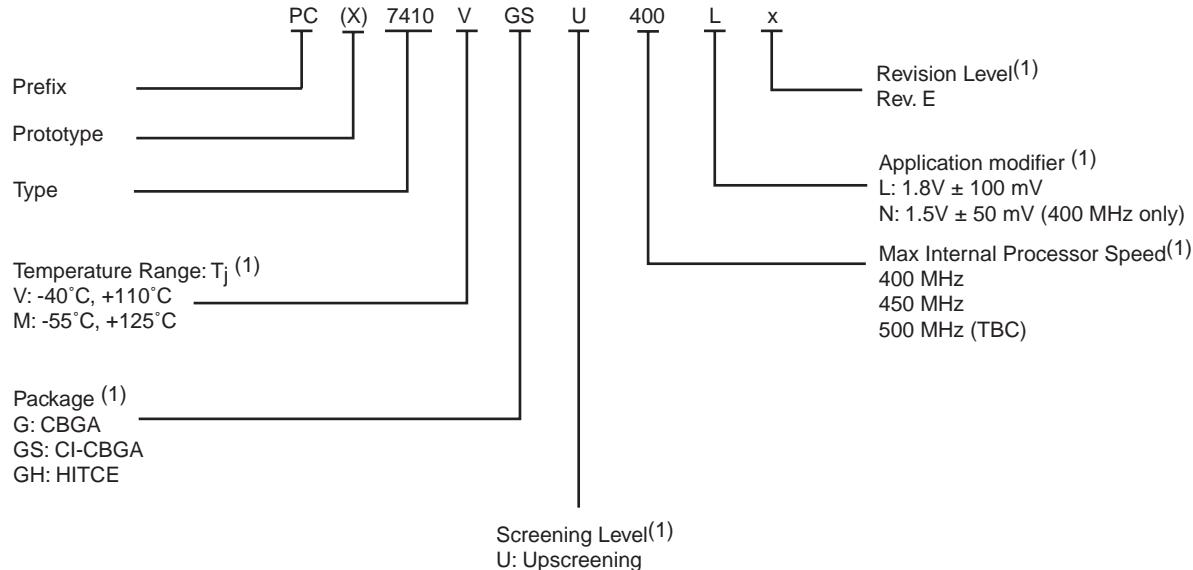

# PowerPC 7410 RISC Microprocessor Product Specification

## PC7410

## Screening

- CBGA Upscreenings Based on Atmel Standards

- Full Military Temperature Range ( $T_j = -55^{\circ}\text{C}, +125^{\circ}\text{C}$ ),

Industrial Temperature Range ( $T_j = -40^{\circ}\text{C}, +110^{\circ}\text{C}$ )

- CI-CGA Package Version, HiTCE Package Version

G suffix

**CBGA 360**

Ceramic Ball Grid Array

GS suffix

**CI±CGA 360**

Ceramic Ball Grid Array

with Solder Column Interposer (SCI)

GH suffix

**HITCE 360**

Ceramic Ball Grid Array

## Block Diagram

Figure 1. PC7410 Microprocessor Block Diagram

## General Parameters

Table 1 provides a summary of the general parameters of the PC7410.

**Table 1.** Device Parameters

| Parameter         | Description                                                                                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology        | 0.18 $\mu$ m CMOS, six-layer metal                                                                                                                                                        |

| Die size          | 6.32 mm $\times$ 8.26 mm (52 mm <sup>2</sup> )                                                                                                                                            |

| Transistor count  | 10.5 million                                                                                                                                                                              |

| Logic design      | Fully-static                                                                                                                                                                              |

| Packages          | Surface-mount 360 ceramic ball grid array (CBGA)<br>Surface mount 360 high coefficient of thermal expansion<br>ceramic ball grid array (HiTCE)<br>Surface mount 360-column Ci-CGA Package |

| Core power supply | 1.8V $\pm$ 100 mV dc or 1.5V $\pm$ 50 mV dc (nominal; see Table 4 for<br>Recommended Operating Conditions)                                                                                |

| I/O power supply  | 1.8V $\pm$ 100 mV dc or<br>2.5V $\pm$ 100 mV<br>3.3V $\pm$ 165 mV (603 bus only) <sup>(1)</sup><br>(input thresholds are configuration pin selectable) or                                 |

Note: 1. 3.3V I/O bus not supported for 1.5V core power supply processor version.

## Features

This section summarizes features of the PC7410's implementation of the PowerPC architecture. Major features of the PC7410 are as follows:

- Branch Processing Unit

- Four instructions fetched per clock

- One branch processed per cycle (plus resolving two speculations)

- Up to one speculative stream in execution, one additional speculative stream in fetch

- 512-entry branch history table (BHT) for dynamic prediction

- 64-entry, 4-way set associative branch target instruction cache (BTIC) for eliminating branch delay slots

- Dispatch Unit

- Full hardware detection of dependencies (resolved in the execution units)

- Dispatch two instructions to eight independent units (system, branch, load/store, fixed-point unit 1, fixed-point unit 2, floating-point, AltiVec permute, AltiVec ALU)

- Serialization control (predispatch, postdispatch, execution serialization)

- Decode

- Register file access

- Forwarding control

- Partial instruction decode

- Completion

- 8-entry completion buffer

- Instruction tracking and peak completion of two instructions per cycle

- Completion of instructions in program order while supporting out-of-order instruction execution, completion serialization and all instruction flow changes

- Fixed-point Units (FXUs) that Share 32 GPRs for Integer Operands

- Fixed-point unit 1 (FXU1)—multiply, divide, shift, rotate, arithmetic, logical

- Fixed-point unit 2 (FXU2)—shift, rotate, arithmetic, logical

- Single-cycle arithmetic, shifts, rotates, logical

- Multiply and divide support (multi-cycle)

- Early out multiply

- Three-stage Floating-point Unit and a 32-entry FPR File

- Support for IEEE-754 standard single- and double-precision floating-point arithmetic

- Three-cycle latency, one-cycle throughput (single or double precision)

- Hardware support for divide

- Hardware support for denormalized numbers

- Time deterministic non-IEEE mode

- System Unit

- Executes CR logical instructions and miscellaneous system instructions

- Special register transfer instructions

- AltiVec Unit

- Full 128-bit data paths

- Two dispatchable units: vector permute unit and vector ALU unit

- Contains its own 32-entry 128-bit vector register file (VRF) with six renames

- The vector ALU unit is further sub-divided into the vector simple integer unit (VSIU), the vector complex integer unit (VCIU) and the vector floating-point unit (VFPU).

- Fully pipelined

- Load/Store Unit

- One-cycle load or store cache access (byte, half-word, word, double-word)

- Two-cycle load latency with one-cycle throughput

- Effective address generation

- Hits under misses (multiple outstanding misses)

- Single-cycle unaligned access within double-word boundary

- Alignment, zero padding, sign extend for integer register file

- Floating-point internal format conversion (alignment, normalization)

- Sequencing for load/store multiples and string operations

- Store gathering

- Executes the cache and TLB instructions

- Big- and little-endian byte addressing supported

- Misaligned little-endian supported

- Supports FXU, FPU, and AltiVec load/store traffic

- Complete support for all four architecture AltiVec DST streams

- Level 1 (L1) Cache Structure

- 32K 32-byte line, 8-way set associative instruction cache (iL1)

- 32K 32-byte line, 8-way set associative data cache (dL1)

- Single-cycle cache access

- Pseudo least-recently-used (LRU) replacement

- Data cache supports AltiVec LRU and transient instructions algorithm

- Copy-back or write-through data cache (on a page-per-page basis)

- Supports all PowerPC memory coherency modes

- Non-blocking instruction and data cache

- Separate copy of data cache tags for efficient snooping

- No snooping of instruction cache except for ICBI instruction

- Level 2 (L2) Cache Interface

- Internal L2 cache controller and tags; external data SRAMs

- 512K, 1M and 2-Mbyte 2-way set associative L2 cache support

- Copyback or write-through data cache (on a page basis or for all L2)

- 32-byte (512K), 64-byte (1M), or 128-byte (2M) sectored line size

- Supports pipelined (register-register) synchronous burst SRAMs and pipelined (register-register) late-write synchronous burst SRAMs

- Supports direct mapped mode for 256K, 512K, 1M or 2 Mbytes of SRAM (either all, half or none of L2 SRAM must be configured as direct mapped).

- Core-to-L2 frequency divisors of  $\div 1$ ,  $\div 1.5$ ,  $\div 2$ ,  $\div 2.5$ ,  $\div 3$ ,  $\div 3.5$ , and  $\div 4$  supported

- 64-bit data bus which also support 32-bits bus mode

- Selectable interface voltages of 1.8V and 2.5V

- Memory Management Unit

- 128 entry, 2-way set associative instruction TLB

- 128 entry, 2-way set associative data TLB

- Hardware reload for TLBs

- Four instruction BATs and four data BATs

- Virtual memory support for up to four petabytes ( $2^{52}$ ) of virtual memory

- Real memory support for up to four gigabytes ( $2^{32}$ ) of physical memory

- Snooped and invalidated for TLBI instructions

- Efficient Data Flow

- All data buses between VRF, load/store unit, dL1, iL1, L2 and the bus are 128 bits wide

- dL1 is fully pipelined to provide 128 bits per cycle to/from the VRF

- L2 is fully pipelined to provide 128 bits per L2 clock cycle to the L1s

- Up to eight outstanding out-of-order cache misses between dL1 and L2/bus

- Up to seven outstanding out-of-order transactions on the bus

- Load folding to fold new dL1 misses into older outstanding load and store misses to the same line

- Store miss merging for multiple store misses to the same line. Only coherency action taken (i.e., address only) for store misses merged to all 32 bytes of a cache line (no data tenure needed).

- Two-entry finished store queue and four-entry completed store queue between load/store unit and dL1

- Separate additional queues for efficient buffering of outbound data (castouts, write throughs, etc.) from dL1 and L2

- Bus Interface

- MPX bus extension to 60X processor interface

- Mode-compatible with 60x processor interface

- 32-bit address bus

- 64-bit data bus

- Bus-to-core frequency multipliers of 2x, 2.5x, 3x, 3.5x, 4x, 4.5x, 5x, 5.5x, 6x, 6.5x, 7x, 7.5x, 8x, 9x supported

- Selectable interface voltages of 1.8V, 2.5V and 3.3V

- Power Management

- Low-power design with thermal requirements very similar to PC740 and PC750

- Low voltage 1.8V or 1.5V processor core

- Selectable interface voltages of 1.8V can reduce power in output buffers

- Three static power saving modes: doze, nap, and sleep

- Dynamic power management

- Testability

- LSSD scan design

- IEEE 1149.1 JTAG interface

- Array built-in self test (ABIST) – factory test only

- Redundancy on L1 data arrays and L2 tag arrays

- Reliability and Serviceability

- Parity checking on 60x and L2 cache buses

## Signal Description

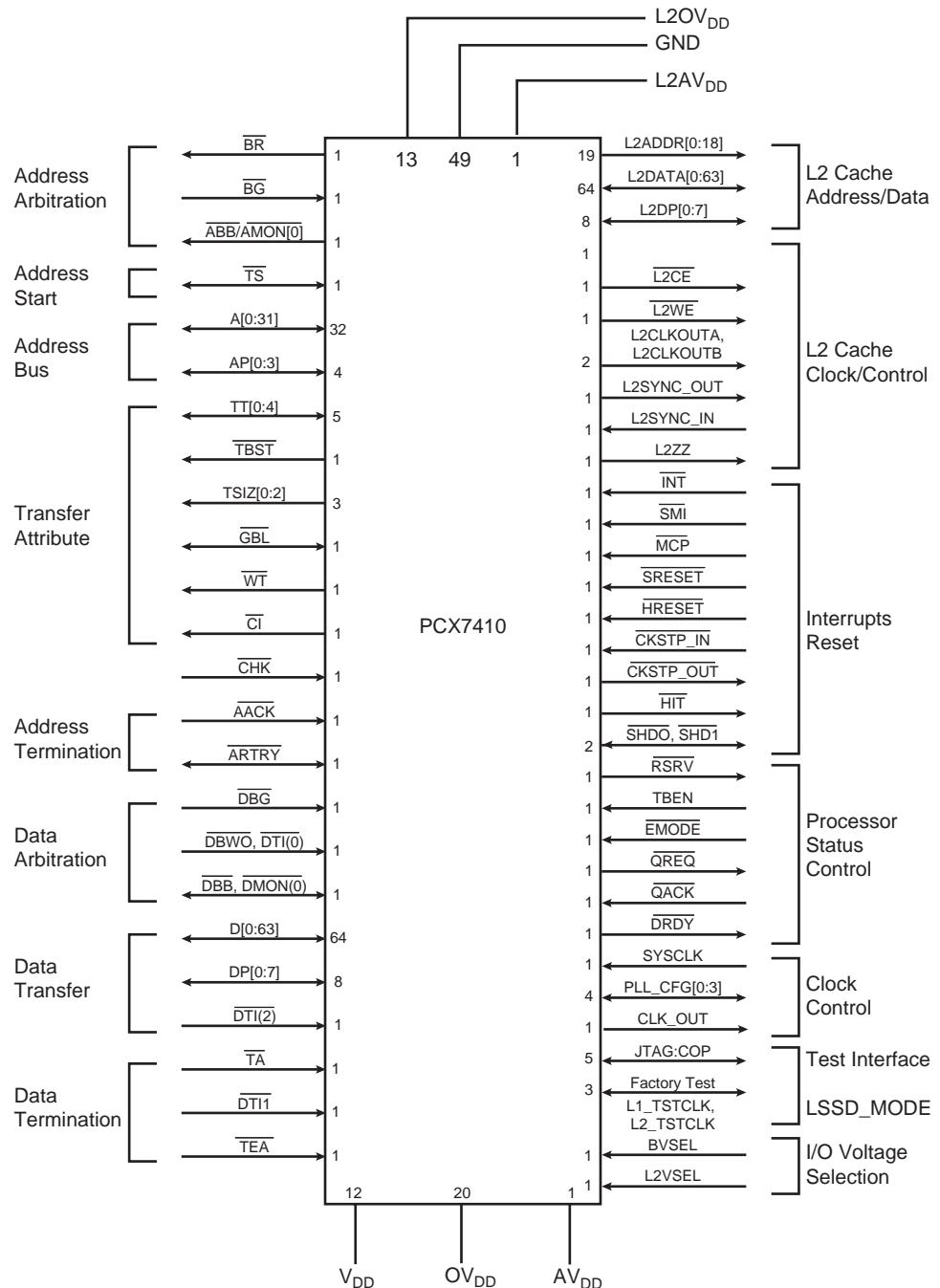

Figure 2. PC7410 Microprocessor Signal Groups

## Detailed Specification

### Scope

This drawing describes the specific requirements for the microprocessor PC7410 in compliance with Atmel-Grenoble standard screening.

### Applicable Documents

1. MIL-STD-883: Test methods and procedures for electronics

2. MIL-PRF-38535: Appendix A: General specifications for microcircuits

### Requirements

#### General

The microcircuits are in accordance with the applicable documents and as specified herein.

#### Design and Construction

#### Terminal Connections

Depending on the package, the terminal connections are as shown in Table 16, Table 4 and Figure 2.

#### Absolute Maximum Ratings

**Table 2.** Absolute Maximum Ratings<sup>(1)</sup>

| Symbol      | Characteristic              | Value                               | Unit |

|-------------|-----------------------------|-------------------------------------|------|

| $V_{DD}$    | Core supply voltage         | -0.3 to 2.1 <sup>(4)</sup>          | V    |

| $AV_{DD}$   | PLL supply voltage          | -0.3 to 2.1 <sup>(4)</sup>          | V    |

| $L2AV_{DD}$ | L2 DLL supply voltage       | -0.3 to 2.1 <sup>(4)</sup>          | V    |

| $OV_{DD}$   | 60x bus supply voltage      | -0.3 to 3.465 <sup>(3)(6)</sup>     | V    |

| $L2OV_{DD}$ | L2 bus supply voltage       | -0.3 to 2.6 <sup>(3)</sup>          | V    |

| $V_{IN}$    | Processor bus input voltage | -0.3 to $OV_{DD} + 0,2V^{(2)(5)}$   | V    |

| $V_{IN}$    | L2 bus input voltage        | -0.3 to $L2OV_{DD} + 0,2V^{(2)(5)}$ | V    |

| $V_{IN}$    | JTAG signal input voltage   | -0.3 to $OV_{DD} + 0,2V$            | V    |

| $T_{STG}$   | Storage temperature range   | -55 to 150                          | °C   |

|             | Rework temperature          | 260                                 | °C   |

Notes:

1. Functional and tested operating conditions are given in Table 4. Absolute maximum ratings are stress ratings only. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

2. Caution:  $V_{IN}$  must not exceed  $OV_{DD}$  or  $L2OV_{DD}$  by more than 0.2V at any time including during power-on reset.

3. Caution:  $L2OV_{DD}/OV_{DD}$  must not exceed  $V_{DD}/AV_{DD}/L2AV_{DD}$  by more than 2.0V at any time including during power-on reset; this limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

4. Caution:  $V_{DD}/AV_{DD}/L2AV_{DD}$  must not exceed  $L2OV_{DD}/OV_{DD}$  by more than 0.4V at any time including during power-on reset; this limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

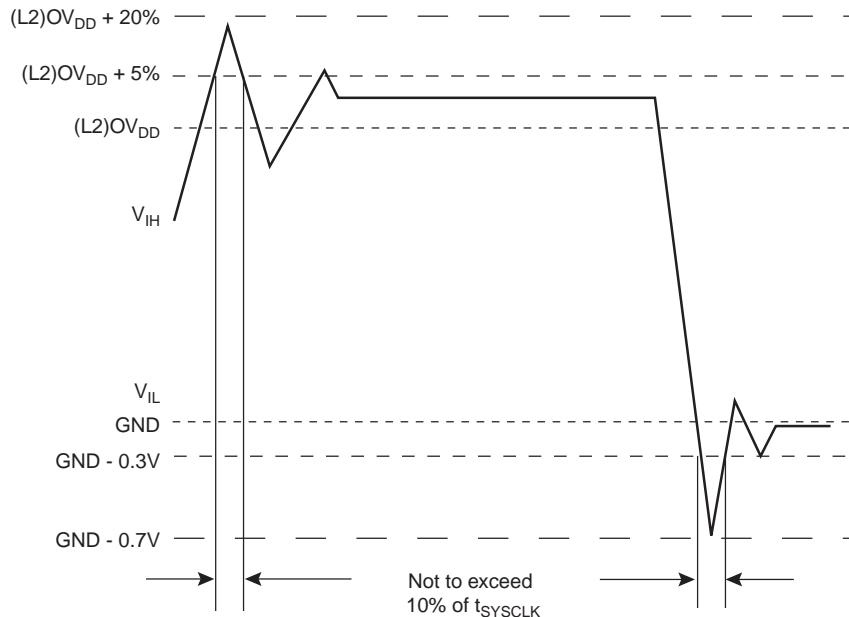

5.  $V_{IN}$  may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 3.

6. PC7410RXnnnLE (Rev 1.4) and later only. Previous revisions do not support 3.3V  $OV_{DD}$  and have a maximum value  $OV_{DD}$  of -0.3 to 2.6V.

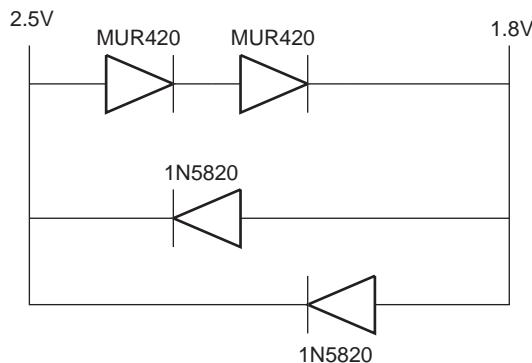

**Figure 3.** Overshoot/Undershoot Voltage

The PC7410 provides several I/O voltages to support both compatibility with existing systems and migration to future systems. The PC7410 “core” voltage must always be provided at nominal voltage (see Table 4 for actual recommended core voltage). Voltage to the L2 I/Os and processor interface I/Os are provided through separate sets of supply pins and may be provided at the voltages shown in Table 3. The input voltage threshold for each bus is selected by sampling the state of the voltage select pins at the negation of the signal HRESET. The output voltage will swing from GND to the maximum voltage applied to the OV<sub>DD</sub> or L2OV<sub>DD</sub> power pins.

**Table 3.** Input Threshold Voltage Setting

| BVSEL Signal             | Processor Bus Input Threshold is Relative to: | L2VSEL Signal <sup>(3)</sup> | L2 Bus Input Threshold is Relative to: |

|--------------------------|-----------------------------------------------|------------------------------|----------------------------------------|

| 0 <sup>(1)</sup>         | 1.8V                                          | 0                            | 1.8                                    |

| HRESET <sup>(1)(2)</sup> | 2.5V                                          | HRESET                       | 2.5                                    |

| 1 <sup>(1)(4)(5)</sup>   | 3.3V <sup>(7)</sup>                           | 1                            | 2.5                                    |

| HRESET <sup>(6)</sup>    | 3.3V <sup>(7)</sup>                           | HRESET                       | Not supported                          |

Notes:

1. Caution: The input threshold selection must agree with the OV<sub>DD</sub>/L2OV<sub>DD</sub> voltages supplied.

2. To select the 2.5V threshold option, L2VSEL/BVSEL should be tied to HRESET so that the two signals change state together. This is the preferred method for selecting this mode operation.

3. To overcome the internal pull-up resistance, a pull-down resistance less than 250Ω should be used.

4. Default voltage setting if left unconnected (internal pulled-up). Parts Rev 1.4 and later only. Previous revisions do not support 3.3V OV<sub>DD</sub>, the default voltage setting if left unconnected is 2.5V.

5. Parts Rev 1.4 and later only. Previous revisions do not support 3.3V OV<sub>DD</sub>, having BVSEL = 1 selects the 2.5V threshold.

6. Parts Rev 1.4 and later only. Previous revisions do not support BVSEL = HRESET.

7. NSpec does not support the default OV<sub>DD</sub> setting of 3.3V. The BVSEL input must be tie either low or HRESET.

## Recommended Operating Conditions

**Table 4.** Recommended Operating Conditions<sup>(1)</sup>

| Symbol             | Characteristic                                       | Recommended Value                                      | Unit                     |    |

|--------------------|------------------------------------------------------|--------------------------------------------------------|--------------------------|----|

| $V_{DD}$           | Core supply voltage                                  | $1.8 \pm 100 \text{ mV}$<br>or $1.5 \pm 50 \text{ mV}$ | V                        |    |

| $AV_{DD}$          | PLL supply voltage                                   | $1.8 \pm 100 \text{ mV}$<br>or $1.5 \pm 50 \text{ mV}$ | V                        |    |

| $L2AV_{DD}$        | L2 DLL supply voltage                                | $1.8 \pm 100 \text{ mV}$<br>or $1.5 \pm 50 \text{ mV}$ | V                        |    |

| $OV_{DD}$          | Processor bus supply voltage see note <sup>(3)</sup> | BVSEL = 0                                              | $1.8 \pm 100 \text{ mV}$ | V  |

| $OV_{DD}$          |                                                      | BVSEL = $\overline{HRESET}$                            | $2.5 \pm 100 \text{ mV}$ | V  |

| $OV_{DD}^{(2)(3)}$ |                                                      | BVSEL = 1 or = $\overline{HRESET}^{(4)}$               | $3.3 \pm 165 \text{ mV}$ | V  |

| $L2OV_{DD}$        | L2 bus supply voltage                                | $L2VSEL = 0$                                           | $1.8 \pm 100 \text{ mV}$ | V  |

| $L2OV_{DD}$        |                                                      | $L2VSEL = 1^{(2)}$ or $L2VSEL = \overline{HRESET}$     | $2.5 \pm 100 \text{ mV}$ | V  |

| $V_{IN}$           | Input voltage                                        | Processor bus                                          | GND to $OV_{DD}$         | V  |

| $V_{IN}$           |                                                      | L2 Bus                                                 | GND to $L2OV_{DD}$       | V  |

| $V_{IN}$           |                                                      | JTAG Signals                                           | GND to $OV_{DD}$         | V  |

| $T_j$              | Die-junction temperature                             |                                                        | -55 to 125               | °C |

Notes:

1. These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

2. PC7410RXnnnLE (Rev 1.4) and later only. Previous revisions do not support 3.3V  $OV_{DD}$  and have a recommended  $OV_{DD}$  value of  $2.5V \pm 100 \text{ mV}$  for  $BVSEL = 1$ .

3. PC7410RXnnnLE (Rev 1.4) and later only. Previous revisions do not support  $BVSEL = \overline{HRESET}$ .

4. Not supported for N spec with  $V_{DD} = 1.5V$

## Thermal Characteristics

### Package Characteristics

**Table 5.** Package Thermal Characteristics CBGA

| Symbol           | Characteristic                                                                                        | Value<br>PC7410 CBGA | Unit |

|------------------|-------------------------------------------------------------------------------------------------------|----------------------|------|

| $R_{\theta JA}$  | Junction-to-ambient thermal resistance, natural convection, single-layer (1s) board <sup>(1)(2)</sup> | 24                   | °C/W |

| $R_{\theta JMA}$ | Junction-to-ambient thermal resistance, natural convection, four-layer (2s2p) board <sup>(1)(3)</sup> | 17                   | °C/W |

| $R_{\theta JMA}$ | Junction-to-ambient thermal resistance, 200 ft/min airflow, single-layer (1s) board <sup>(1)(3)</sup> | 18                   | °C/W |

| $R_{\theta JMA}$ | Junction-to-ambient thermal resistance, 400 ft/min airflow, single-layer (1s) board                   | 16                   | °C/W |

| $R_{\theta JMA}$ | Junction-to-ambient thermal resistance, 200 ft/min airflow, four-layer (2s2p) board <sup>(1)(3)</sup> | 14                   | °C/W |

| $R_{\theta JMA}$ | Junction-to-ambient thermal resistance, 400 ft/min airflow, four-layer (2s2p) board                   | 13                   | °C/W |

| $R_{\theta JB}$  | Junction-to-board thermal resistance <sup>(4)</sup>                                                   | 8                    | °C/W |

| $R_{\theta JC}$  | Junction-to-case thermal resistance <sup>(5)</sup>                                                    | < 0.1                | °C/W |

Notes:

1. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

3. Per JEDEC JESD51-6 with the board horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature. The actual value of  $R_{\theta JC}$  for the part is less than 0.1°C/W.

See "Thermal Management Information" on page 13 for more details about thermal management.

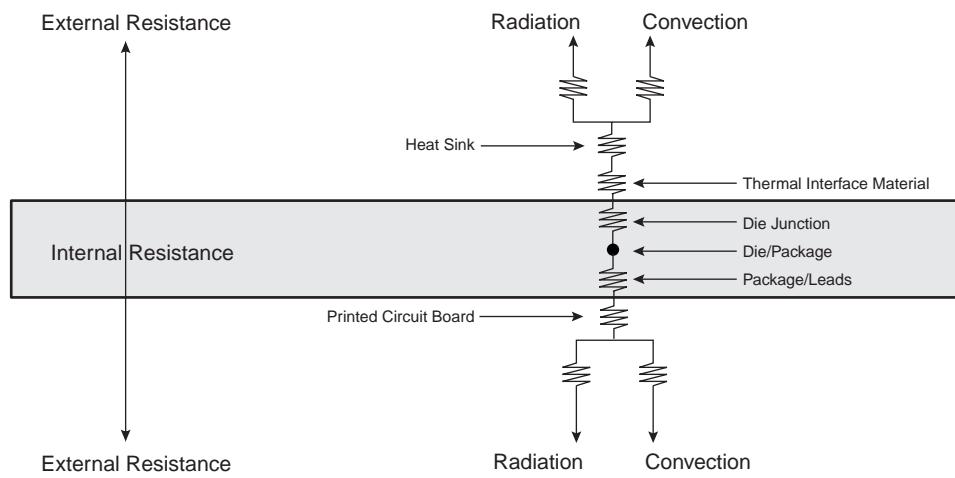

The board designer can choose between several commercially available heat sink types to place on the PC7410. For exposed-die packaging technology as in Table 5, the intrinsic conduction thermal resistance paths are shown in Figure 4.

### Package Thermal Characteristics for HiTCE

Table 6 provides the package thermal characteristics for the PC7410, HiTCE.

**Table 6.** Package Thermal Characteristics for HiTCE Package

| Characteristic                                                                                        | Symbol           | Value        | Unit |

|-------------------------------------------------------------------------------------------------------|------------------|--------------|------|

|                                                                                                       |                  | PC7410 HiTCE |      |

| Junction-to-bottom of balls <sup>(1)</sup>                                                            | $R_{\theta J}$   | 6.8          | °C/W |

| Junction-to-ambient thermal resistance, natural convection, four-layer (2s2p) board <sup>(1)(2)</sup> | $R_{\theta JMA}$ | 20.7         | °C/W |

| Junction to board thermal resistance                                                                  | $R_{\theta JB}$  | 11.0         | °C/W |

Notes:

1. Simulation, no convection air flow.

2. Per JEDEC JESD51-6 with the board horizontal.

### Package Thermal Characteristics for CI-CGA

**Table 7.** Package Thermal Characteristics for CI-CGA

| Characteristic                       | Symbol          | Value         | Unit |

|--------------------------------------|-----------------|---------------|------|

|                                      |                 | PC7410 CI-CGA |      |

| Junction to board thermal resistance | $R_{\theta JB}$ | 8.42          | °C/W |

### Internal Package Conduction Resistance

Figure 4 depicts the primary heat transfer path for a package with an attached heat sink mounted on a printed circuit board.

Heat generated on the active side of the chip is conducted through the silicon, then through the heat sink attach material (or thermal interface material) and finally to the heat sink where it is removed by forced-air convection.

Since the silicon thermal resistance is quite small, for a first-order analysis the temperature drop in the silicon may be neglected. Thus, the heat sink attach material and the heat sink conduction/convective thermal resistances are the dominant terms.

**Figure 4.** C4 Package with Heat Sink Mounted on a Printed Circuit Board

### Thermal Management Information

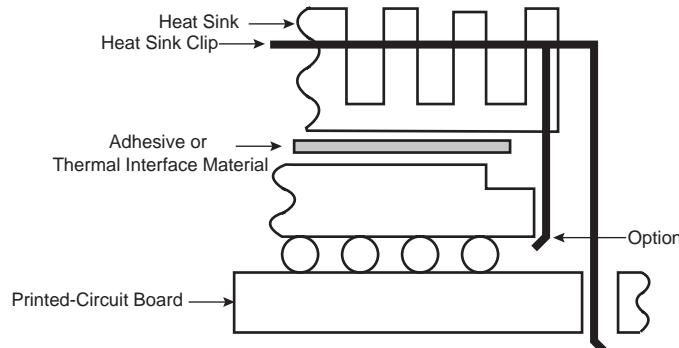

This section provides thermal management information for the ceramic ball grid array (CBGA) package for air-cooled applications. Proper thermal control design is primarily dependent upon the system-level design – the heat sink, airflow and thermal interface material. To reduce the die-junction temperature, heat sinks may be attached to the package by several methods: adhesive, spring clip to holes in the printed-circuit board or package and mounting clip and screw assembly; see Figure 5. This spring force should not exceed 5.5 pounds of force. Ultimately, the final selection of an appropriate heat sink depends on many factors such as thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly and cost.

**Figure 5.** CBGA Package Cross-section with Heat Sink Options

## Adhesives and Thermal Interface Materials

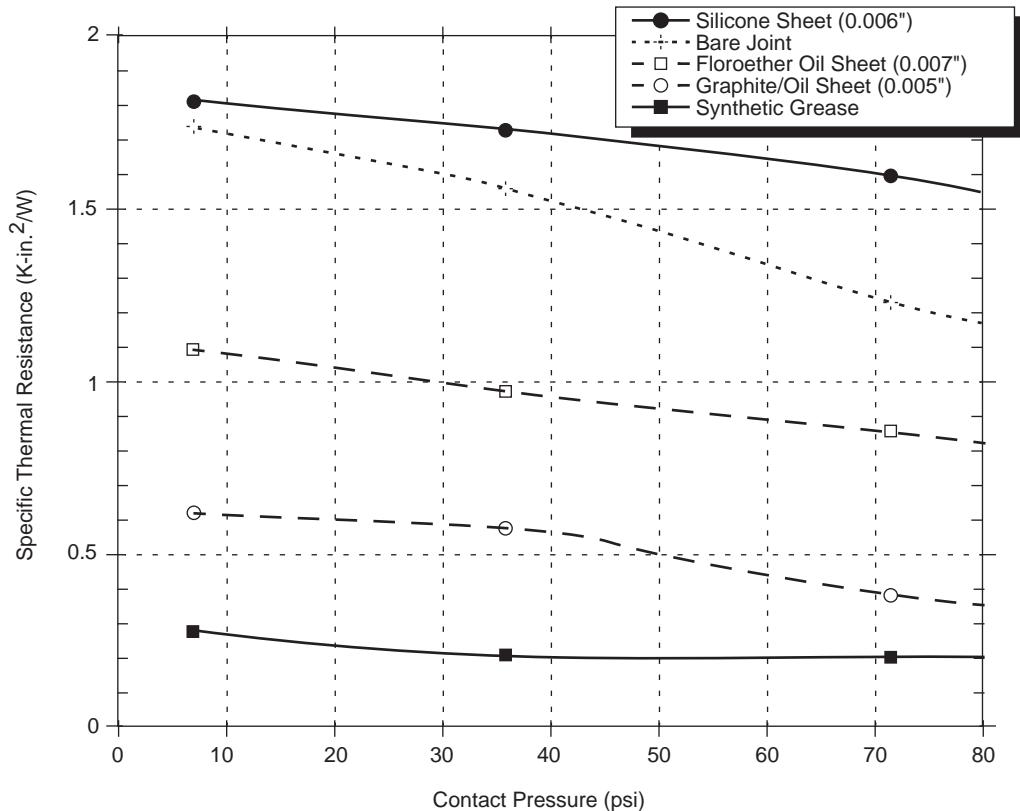

A thermal interface material is recommended at the package lid-to-heat sink interface to minimize the thermal contact resistance. For those applications where the heat sink is attached by spring clip mechanism, Figure 6 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, floroether oil), a bare joint and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. The use of thermal grease significantly reduces the interface thermal resistance. That is, the bare joint results in a thermal resistance approximately seven times greater than the thermal grease joint.

Heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 5). This spring force should not exceed 5.5 pounds of force. Therefore, synthetic grease offers the best thermal performance, considering the low interface pressure.

The board designer can choose between several types of thermal interface. Heat sink adhesive materials should be selected based upon high conductivity, yet must have adequate mechanical strength to meet equipment shock/vibration requirements.

**Figure 6.** Thermal Performance of Different Thermal Interface Materials

**Heat Sink Selection Example**

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_j = T_a + T_r + (\theta_{jc} + \theta_{int} + \theta_{sa}) \times P_d$$

where:

$T_j$  = die-junction temperature

$T_a$  = inlet cabinet ambient temperature

$T_r$  = air temperature rise within the computer cabinet

$\theta_{jc}$  = junction-to-case thermal resistance

$\theta_{int}$  = adhesive or interface material thermal resistance

$\theta_{sa}$  = heat sink base-to-ambient thermal resistance

$P_d$  = power dissipated by the device

During operation, the die-junction temperatures ( $T_j$ ) should be maintained less than the value specified in Table 4. The temperature of the air cooling the component greatly depends upon the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature ( $T_a$ ) may range from 30°C to 40°C. The air temperature rise within a cabinet ( $T_r$ ) may be in the range of 5°C to 10°C. The thermal resistance of the thermal interface material ( $\theta_{int}$ ) is typically about 1°C/W. Assuming a  $T_a$  of 30°C, a  $T_r$  of 5°C, a CBGA package  $\theta_{jc} = 0.03$ , and a power consumption ( $P_d$ ) of 5.0 watts, the following expression for  $T_j$  is obtained:

$$T_j = 30^\circ C + 5^\circ C + (0.03^\circ C/W + 1.0^\circ C/W + \theta_{sa}) \times 5W$$

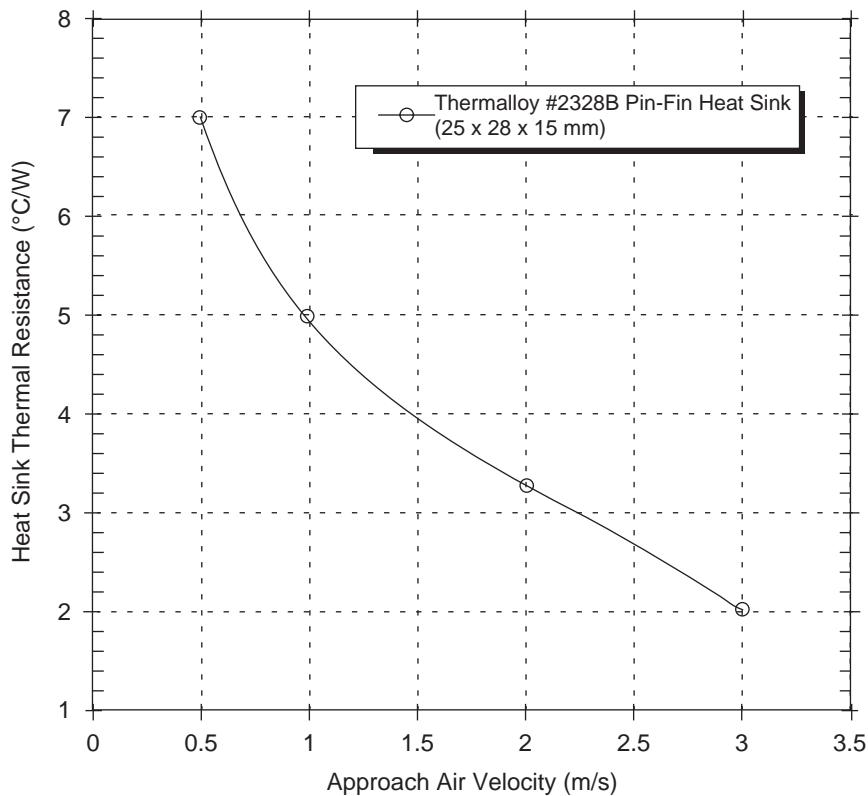

For a Thermally heat sink #2328B, the heat sink-to-ambient thermal resistance ( $\theta_{sa}$ ) versus airflow velocity is shown in Figure 7.

**Figure 7.** Thermalloy #2328B Heat Sink-to-ambient Thermal Resistance vs. Airflow Velocity

Assuming an air velocity of 0.5 m/s, the effective  $R_{sa}$  is 7°C/W, thus

$$T_j = 30^\circ C + 5^\circ C + (0.03^\circ C/W + 1.0^\circ C/W + 7^\circ C/W) \times 5W,$$

resulting in a die-junction temperature of approximately 75°C which is well within the maximum operating temperature of the component.

Other heat sinks offered by Chip Coolers, IERC, Thermalloy, Wakefield Engineering and Aavid Engineering offer different heat sink-to-ambient thermal resistances and may or may not need air flow.

Though the die junction-to-ambient and the heat sink-to-ambient thermal resistances are a common figure of merit used for comparing the thermal performance of various microelectronic packaging technologies, one should exercise caution when only using this metric in determining thermal management because no single parameter can adequately describe three-dimensional heat flow. The final die-junction operating temperature is not only a function of the component-level thermal resistance, but of the system-level design and its operating conditions. In addition to the component's power consumption, a number of factors affect the final operating die-junction temperature – airflow, board population (local heat flux of adjacent components), heat sink efficiency, heat sink attach, heat sink placement, next-level interconnect technology, system air temperature rise, altitude, etc.

Due to the complexity and the many variations of system-level boundary conditions for today's microelectronic equipment, the combined effects of the heat transfer mechanisms (radiation, convection and conduction) may vary widely. For these reasons, it is recommended to use conjugate heat transfer models for the board, as well as system-level designs.

To expedite system-level thermal analysis, several "compact" thermal-package models are available within FLOTHERM®. These are available upon request.

## Power Consideration

### Power Management

The PC7410 provides four power modes, selectable by setting the appropriate control bits in the MSR and HIDO registers. The four power modes are:

- Full-power: This is the default power state of the PC7410. The PC7410 is fully powered and the internal functional units are operating at the full processor clock speed. If the dynamic power management mode is enabled, functional units that are idle will automatically enter a low-power state without affecting performance, software execution or external hardware.

- Doze: All the functional units of the PC7410 are disabled except for the time base/decrementer registers and the bus snooping logic. When the processor is in doze mode, an external asynchronous interrupt, a system management interrupt, a decrementer exception, a hard or soft reset or machine check brings the PC7410 into the full-power state. The PC7410 in doze mode maintains the PLL in a fully powered state and locked to the system external clock input (SYSCLK) so a transition to the full-power state takes only a few processor clock cycles.

- Nap: The nap mode further reduces power consumption by disabling bus snooping, leaving only the time base register and the PLL in a powered state. The PC7410 returns to the full-power state upon receipt of an external asynchronous interrupt, a system management interrupt, a decrementer exception, a hard or soft reset or a machine check input (MCP). A return to full-power state from a nap state takes only a few processor clock cycles. When the processor is in nap mode, if  $\overline{QACK}$  is negated, the processor is put in doze mode to support snooping.

- Sleep: Sleep mode minimizes power consumption by disabling all internal functional units, after which external system logic may disable the PLL and SYSCLK. Returning the PC7410 to the full-power state requires the enabling of the PLL and SYSCLK, followed by the assertion of an external asynchronous interrupt, a system management interrupt, a hard or soft reset or a machine check input (MCP) signal after the time required to relock the PLL.

## Power Dissipation

**Table 8.** Power Consumption for PC7410 (1.8V)

| Power Mode                               | Processor (CPU) Frequency |      |         |      |         | Unit |

|------------------------------------------|---------------------------|------|---------|------|---------|------|

|                                          | 400 MHz                   |      | 450 MHz |      | 500 MHz |      |

|                                          | 1.5V                      | 1.8V | 1.5V    | 1.8V | 1.8 V   |      |

| <b>Full-On Mode</b>                      |                           |      |         |      |         |      |

| Typical <sup>(1)(3)</sup>                | 2.92                      | 4.2  | 3.29    | 4.7  | 5.3     | W    |

| Maximum <sup>(1)(2)(4)(5)</sup>          | 6.6                       | 9.5  | 7.43    | 10.7 | 11.9    | W    |

| <b>Doze Mode</b>                         |                           |      |         |      |         |      |

| Maximum <sup>(1)(2)(5)</sup>             | 3.6                       | 4.3  | 4.1     | 4.8  | 5.3     | W    |

| <b>Nap Mode</b>                          |                           |      |         |      |         |      |

| Maximum <sup>(1)(2)(5)</sup>             | 1.35                      | 1.35 | 1.5     | 1.5  | 1.65    | W    |

| <b>Sleep Mode</b>                        |                           |      |         |      |         |      |

| Maximum <sup>(1)(2)(5)</sup>             | 1.3                       | 1.3  | 1.45    | 1.45 | 1.6     | W    |

| <b>Sleep Mode - PLL and DLL Disabled</b> |                           |      |         |      |         |      |

| Typical <sup>(1)(3)</sup>                | 600                       | 600  | 600     | 600  | 600     | mW   |

| Maximum <sup>(1)(2)(5)</sup>             | 1.1                       | 1.1  | 1.1     | 1.1  | 1.1     | W    |

Notes: 1. These values apply for all valid processor bus and L2 bus ratios. The values do not include I/O supply power ( $OV_{DD}$  and  $L2OV_{DD}$ ) or PLL/DLL supply power ( $AV_{DD}$  and  $L2AV_{DD}$ ).  $OV_{DD}$  and  $L2OV_{DD}$  power is system dependent, but is typically  $<10\%$  of  $V_{DD}$  power. Worst case power consumption for  $AV_{DD} = 15$  mW and  $L2AV_{DD} = 15$  mW.

2. Maximum power is measured at 105°C, at  $V_{DD} = 1.8V$  or  $1.5V$  while running an entirely cache-resident, contrived sequence of instructions which keep the execution units, including AltiVec, maximally busy.

3. Typical power is an average value measured at 65°C,  $V_{DD} = 1.8V$  or  $1.5V$ ,  $OV_{DD} = L2OV_{DD} = 2.5V$  in a system while running a codec application that is AltiVec intensive.

4. These values include the use of AltiVec. Without AltiVec operation, estimate a 25% decrease.

5. Power consumption derating at low temperatures to be defined after device characterization.

## Electrical Characteristics

### Static Characteristics

**Table 9.** DC Electrical Specifications (see Table 4 for Recommended Operating Conditions)

| Symbol    | Characteristic                                                                              | Nominal Bus Voltage <sup>(1)</sup> | Min                       | Max                       | Unit    |

|-----------|---------------------------------------------------------------------------------------------|------------------------------------|---------------------------|---------------------------|---------|

| $V_{IH}$  | Input high voltage<br>(all inputs except SYSCLK) <sup>(2)(3)(8)</sup>                       | 1.8                                | $0.65 \times (L2)OV_{DD}$ | $(L2)OV_{DD} + 0.2$       | V       |

| $V_{IH}$  |                                                                                             | 2.5                                | 1.7                       | $(L2)OV_{DD} + 0.2$       |         |

| $V_{IH}$  |                                                                                             | 3.3                                | 2.0                       | $OV_{DD} + 0.3$           |         |

| $V_{IL}$  | Input low voltage<br>(all inputs except SYSCLK) <sup>(8)</sup>                              | 1.8                                | -0.3                      | $0.35 \times (L2)OV_{DD}$ | V       |

| $V_{IL}$  |                                                                                             | 2.5                                | -0.3                      | $0.2 \times (L2)OV_{DD}$  |         |

| $V_{IL}$  |                                                                                             | 3.3                                | -0.3                      | 0.8                       |         |

| $CV_{IH}$ | SYSCLK input high voltage <sup>(2)(8)</sup>                                                 | 1.8                                | 1.5                       | $OV_{DD} + 0.2$           | V       |

| $CV_{IH}$ |                                                                                             | 2.5                                | 2.0                       | $OV_{DD} + 0.2$           |         |

| $CV_{IH}$ |                                                                                             | 3.3                                | 2.4                       | $OV_{DD} + 0.3$           |         |

| $CV_{IL}$ | SYSCLK input low voltage <sup>(8)</sup>                                                     | 1.8                                | -0.3                      | 0.2                       | V       |

| $CV_{IL}$ |                                                                                             | 2.5                                | -0.3                      | 0.4                       |         |

| $CV_{IL}$ |                                                                                             | 3.3                                | -0.3                      | 0.4                       |         |

| $I_{IN}$  | Input leakage current,<br>$V_{IN} = L2OV_{DD}/OV_{DD}$ <sup>(2)(3)(6)(7)</sup>              | 1.8                                | —                         | 20                        | $\mu A$ |

| $I_{IN}$  |                                                                                             | 2.5                                | —                         | 35                        |         |

| $I_{IN}$  |                                                                                             | 3.3                                | —                         | 70                        |         |

| $I_{TSI}$ | High-Z (off-state) leakage current,<br>$V_{IN} = L2OV_{DD}/OV_{DD}$ <sup>(2)(3)(5)(7)</sup> | 1.8                                | —                         | 20                        | $\mu A$ |

| $I_{TSI}$ |                                                                                             | 2.5                                | —                         | 35                        |         |

| $I_{TSI}$ |                                                                                             | 3.3                                | —                         | 70                        |         |

| $V_{OH}$  | Output high voltage, $I_{OH} = -6 \text{ mA}^{(8)}$                                         | 1.8                                | $(L2)OV_{DD} - 0.45$      | —                         | V       |

| $V_{OH}$  |                                                                                             | 2.5                                | 1.7                       | —                         |         |

| $V_{OH}$  |                                                                                             | 3.3                                | 2.4                       | —                         |         |

| $V_{OL}$  | Output low voltage, $I_{OL} = 6 \text{ mA}^{(8)}$                                           | 1.8                                | —                         | 0.45                      | V       |

| $V_{OL}$  |                                                                                             | 2.5                                | —                         | 0.4                       |         |

| $V_{OL}$  |                                                                                             | 3.3                                | —                         | 0.4                       |         |

| $C_{IN}$  | Capacitance, $V_{IN} = 0V$ , $f = 1 \text{ MHz}^{(3)(4)(7)}$                                |                                    | —                         | 6.0                       | pF      |

Notes:

1. Nominal voltages; see Table 4 for recommended operating conditions.

2. For processor bus signals, the reference is  $OV_{DD}$  while  $L2OV_{DD}$  is the reference for the L2 bus signals.

3. Excludes factory test signals.

4. Capacitance is periodically sampled rather than 100% tested.

5. The leakage is measured for nominal  $OV_{DD}$  and  $L2OV_{DD}$ , or both  $OV_{DD}$  and  $L2OV_{DD}$  must vary in the same direction (for example, both  $OV_{DD}$  and  $L2OV_{DD}$  vary by either +5% or -5%).

6. Measured at max  $OV_{DD}/L2OV_{DD}$

7. Excludes IEEE 1149.1 boundary scan (JTAG) signals.

8. For JTAG support: all signals controlled by BVSEL and L2VSEL will see  $V_{IL}/V_{IH}/V_{OL}/V_{OH}/CV_{IH}/CV_{IL}$  DC limits of 1.8V mode while either the EXTEST or CLAMP instruction is loaded into the IEEE 1149.1 instruction register by the UpdateIR TAP state until a different instruction is loaded into the instruction register by either another UpdateIR or a Test-Logic-Reset TAP state. If only  $\overline{TSRT}$  is asserted to the part, and then a SAMPLE instruction is executed, there is no way to control or predict what the DC voltage limits are. If  $\overline{HRESET}$  is asserted before executing a SAMPLE instruction, the DC voltage limits will be controlled by the BVSEL/L2VSEL settings during  $\overline{HRESET}$ . Anytime  $\overline{HRESET}$  is not asserted (i.e., just asserting  $\overline{TRST}$ ), the voltage mode is not known until either EXTEST or CLAMP is executed, at which time the voltage level will be at the DC limits of 1.8V.

## Dynamic Characteristics

After fabrication, parts are sorted by maximum processor core frequency as shown in "Clock AC Specifications" and tested for conformance to the AC specifications for that frequency. These specifications are for valid processor core frequencies. The processor core frequency is determined by the bus (SYSCLK) frequency and the settings of the PLL\_CFG[0:3] signals. Parts are sold by maximum processor core frequency.

## Clock AC Specifications

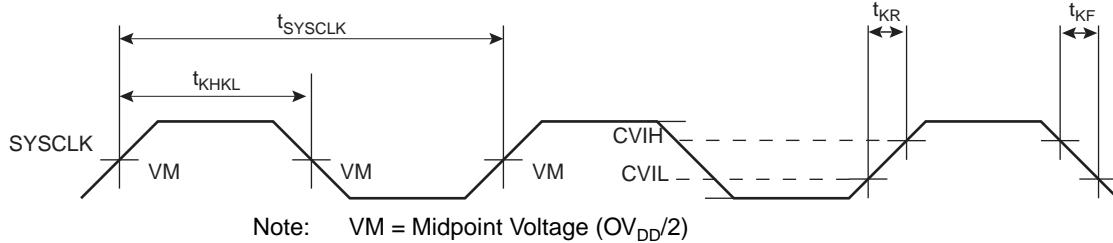

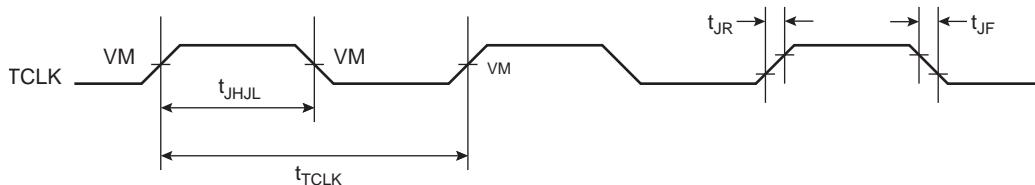

Table 10 provides the clock AC timing specifications as defined in Figure 8.

**Table 10.** Clock AC Timing Specifications (See Table 4 for Recommended Operating Conditions)

| Symbol                      | Characteristic                            | Maximum Processor Core Frequency |           |         |           |         |           | Unit    |  |

|-----------------------------|-------------------------------------------|----------------------------------|-----------|---------|-----------|---------|-----------|---------|--|

|                             |                                           | 400 MHz                          |           | 450 MHz |           | 500 MHz |           |         |  |

|                             |                                           | Min                              | Max       | Min     | Max       | Min     | Max       |         |  |

| $f_{CORE}^{(1)}$            | Processor frequency                       | 350                              | 400       | 350     | 450       | 350     | 500       | MHz     |  |

| $f_{VCO}^{(1)}$             | VCO frequency                             | 700                              | 800       | 700     | 900       | 700     | 1000      | MHz     |  |

| $f_{SYSCLK}^{(1)}$          | SYSCLK frequency                          | 33                               | 133       | 33      | 133       | 33      | 133       | MHz     |  |

| $t_{SYSCLK}$                | SYSCLK cycle time                         | 7.5                              | 30        | 7.5     | 30        | 7.5     | 30        | ns      |  |

| $t_{KR} \& t_{KF}^{(2)}$    | SYSCLK rise and fall time                 |                                  | 1.0       |         | 1.0       |         | 1         | ns      |  |

| $t_{KR} \& t_{KF}^{(3)}$    |                                           |                                  | 0.5       |         | 0.5       |         | 0.5       | ns      |  |

| $t_{KHKL}/t_{SYSCLK}^{(4)}$ | SYSCLK duty cycle measured at $OV_{DD}/2$ | 40                               | 60        | 40      | 60        | 40      | 60        | %       |  |

|                             | SYSCLK jitter <sup>(5)</sup>              |                                  | $\pm 150$ |         | $\pm 150$ |         | $\pm 150$ | ps      |  |

|                             | Internal PLL relock time <sup>(6)</sup>   |                                  | 100       |         | 100       |         | 100       | $\mu s$ |  |

Notes:

1. Caution: The SYSCLK frequency and PLL\_CFG[0:3] settings must be chosen such that the resulting SYSCLK (bus) frequency, CPU (core) frequency and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0:3] signal description in "Clock Selection" on page 39 for valid PLL\_CFG[0:3] settings

2. Rise and fall times for the SYSCLK input measured from 0.4V to 2.4V when  $OV_{DD} = 3.3V$  nominal.

3. Rise and fall times for the SYSCLK input measured from 0.2V to 1.2V when  $OV_{DD} = 1.8V$  or 2.5V nominal.

4. Timing is guaranteed by design and characterization.

5. This represents total input jitter, short-term and long-term combined, and is guaranteed by design.

6. Relock timing is guaranteed by design and characterization. PLL-relock time is the maximum amount of time required for PLL lock after a stable  $V_{DD}$  and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that  $\overline{HRESET}$  must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

**Figure 8.** SYSCLK Input Timing Diagram

### Processor Bus AC Specifications

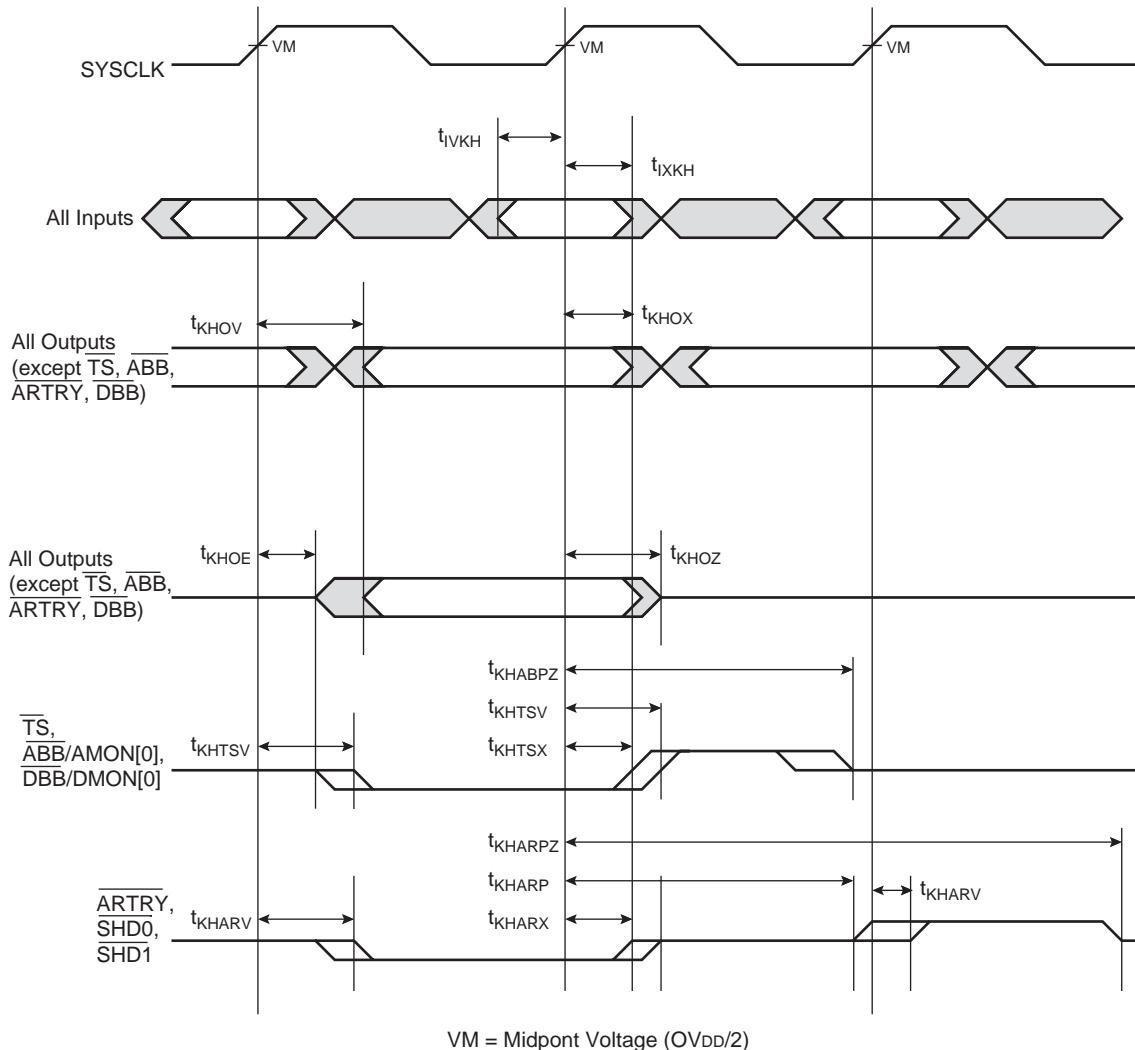

Table 11 provides the processor AC timing specifications for the PC7410 as defined in Figure 10 and Figure 11. Timing specifications for the L2 bus are provided in "L2 Bus AC Specifications" on page 26.

**Table 11.** Processor Bus AC Timing Specifications<sup>(1)</sup> at  $V_{DD} = AV_{DD} = 1.8V \pm 100 \text{ mV}$ ;

$-55^\circ\text{C} \leq T_j \leq 125^\circ\text{C}$ ,  $OV_{DD} = 1.8V \pm 100 \text{ mV}$

| Symbol <sup>(2)</sup>     | Parameter                                                                                                                                                                                                            | 400, 450, 500 MHz |     | Unit         |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|--------------|

|                           |                                                                                                                                                                                                                      | Min               | Max |              |

| $t_{IVKH}$                | Input Setup                                                                                                                                                                                                          | 1.0               | —   | ns           |

| $t_{IXKH}$                | Input Hold                                                                                                                                                                                                           | 0                 | —   | ns           |

| $t_{KHTSV}$               | Output Valid Times: <sup>(7)(8)</sup>                                                                                                                                                                                |                   |     | ns           |

| $t_{KHARV}$               | TS                                                                                                                                                                                                                   | —                 | 3.0 |              |

| $t_{KHOV}$                | $\overline{\text{ARTRY}}/\overline{\text{SHD0}}/\overline{\text{SHD1}}$                                                                                                                                              | —                 | 2.3 |              |

|                           | All Other Outputs                                                                                                                                                                                                    | —                 | 3.0 |              |

| $t_{KHTSX}$               | Output Hold Times: <sup>(7)(12)</sup>                                                                                                                                                                                |                   |     | ns           |

| $t_{KHARX}$               | TS                                                                                                                                                                                                                   | 0.5               | —   |              |

| $t_{KHOX}$                | $\overline{\text{ARTRY}}/\overline{\text{SHD0}}/\overline{\text{SHD1}}$                                                                                                                                              | 0.5               | —   |              |

|                           | All Other Outputs                                                                                                                                                                                                    | 0.5               | —   |              |

| $t_{KHOE}^{(11)}$         | SYSCLK to Output Enable                                                                                                                                                                                              | 0.5               | —   | ns           |

| $t_{KHOZ}$                | SYSCLK to Output High Impedance (all except ABB/AMON[0], $\overline{\text{ARTRY}}/\overline{\text{SHD}}$ , $\overline{\text{DBB}}/\overline{\text{DMON}}[0]$ , $\overline{\text{SHD0}}$ , $\overline{\text{SHD1}}$ ) | —                 | 3.5 | ns           |

| $t_{KHABPZ}^{(5)(9)(11)}$ | SYSCLK to $\overline{\text{ABB}}/\overline{\text{AMON}}[0]$ , $\overline{\text{DBB}}/\overline{\text{DMON}}[0]$ High Impedance after precharge                                                                       | —                 | 1   | $t_{SYSCLK}$ |

| $t_{KHARP}^{(5)(10)(11)}$ | Maximum Delay to $\overline{\text{ARTRY}}/\overline{\text{SHD0}}/\overline{\text{SHD1}}$ Precharge                                                                                                                   | —                 | 1   | $t_{SYSCLK}$ |

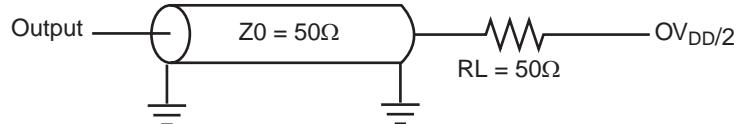

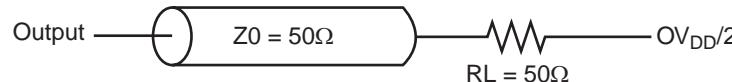

Notes: 1. All input specifications are measured from the midpoint of the signal in question to the midpoint of the rising edge of the input SYSCLK. All output specifications are measured from the midpoint of the rising edge of SYSCLK to the midpoint of the signal in question. All output timings assume a purely resistive 50Ω load (see Figure 10). Input and output timings are measured at the pin; time-of-flight delays must be added for trace lengths, vias and connectors in the system.

2. The symbology used for timing specifications herein follows the pattern of  $t_{(\text{signal})(\text{state})(\text{reference})(\text{state})}$  for inputs and  $t_{(\text{reference})(\text{state})(\text{signal})(\text{state})}$  for outputs. For example,  $t_{IVKH}$  symbolizes the time input signals (I) reach the valid state (V) relative to the SYSCLK reference (K) going to the high (H) state or input setup time. And  $t_{KHOV}$  symbolizes the time from SYSCLK (K) going high (H) until outputs (O) are valid (V) or output valid time. Input hold time can be read as the time that the input signal (I) went invalid (X) with respect to the rising clock edge (KH) - note the position of the reference and its state for inputs - and output hold time can be read as the time from the rising edge (KH) until the output went invalid (OX).

3. The setup and hold time is with respect to the rising edge of  $\overline{\text{HRESET}}$  (see Figure 11).

4. This specification is for configuration mode select only. Also note that the  $\overline{\text{HRESET}}$  must be held asserted for a minimum of 255 bus clocks after the PLL re-lock time during the power-on reset sequence.

5.  $t_{SYSCLK}$  is the period of the external clock (SYSCLK) in nanoseconds(ns). The numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the parameter in question.

6. Mode select signals are BVSEL, EMODE, L2VSEL, PLL\_CFG[0:3]

7. All other output signals are composed of the following - A[0:31], AP[0:3], TT[0:4],  $\overline{\text{TBST}}$ , TSIZ[0:2],  $\overline{\text{GBL}}$ ,  $\overline{\text{WT}}$ ,  $\overline{\text{CI}}$ , DH[0:31], DL[0:31], DP[0:7], BR, CKSTP\_OUT, DRDY, HIT, QREQ, RSRV.

8. Output valid time is measured from 2.4V to 0.8V which may be longer than the time required to discharge from Vdd to 0.8V.

9. According to the 60x bus protocol,  $\overline{\text{ABB}}$  and  $\overline{\text{DBB}}$  are driven only by the currently active bus master. They are asserted low then precharged high before returning to high-Z as shown in Figure 9. The nominal precharge width for  $\overline{\text{ABB}}$  or  $\overline{\text{DBB}}$  is  $0.5 \times t_{\text{SYSCLK}}$  i.e., less than the minimum  $t_{\text{SYSCLK}}$  period, to ensure that another master asserting  $\overline{\text{ABB}}$ , or  $\overline{\text{DBB}}$  on the following clock will not contend with the precharge. Output valid and output hold timing is tested for the signal asserted. Output valid time is tested for precharge. The high-Z behavior is guaranteed by design.

10. According to the 60x bus protocol,  $\overline{\text{ARTRY}}$  can be driven by multiple bus masters through the clock period immediately following  $\overline{\text{AACK}}$ . Bus contention is not an issue since any master asserting  $\overline{\text{ARTRY}}$  will be driving it low. Any master asserting it low in the first clock following  $\overline{\text{AACK}}$  will then go to high-Z for one clock before precharging it high during the second cycle after the assertion of  $\overline{\text{AACK}}$ . The nominal precharge width for  $\overline{\text{ARTRY}}$  is  $1.0 t_{\text{SYSCLK}}$ ; i.e., it should be high-Z as shown in Figure 9 before the first opportunity for another master to assert  $\overline{\text{ARTRY}}$ . Output valid and output hold timing are tested for the signal asserted. Output valid time is tested for precharge. The high-Z behavior is guaranteed by design.

11. Guaranteed by design and not tested.

12. Output hold time characteristics can be altered by the use of the L2\_TSTCLK pin during system reset, similar to L2 output hold being altered by the use of bits [14-15] in the L2CR register. Information on the operation of the L2\_TSTCLK will be included in future revisions of this specification.

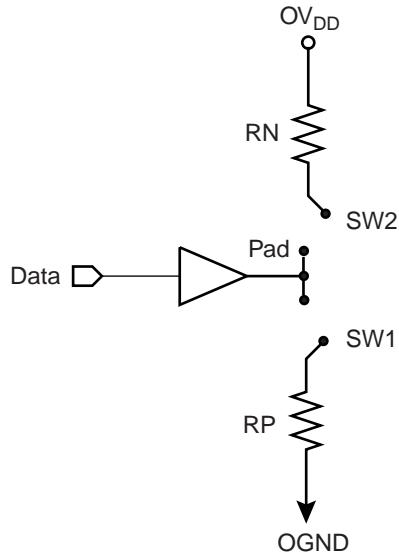

**Figure 9.** Input/Output Timing Diagram

**Figure 10.** AC Test Load for the 60x Interface

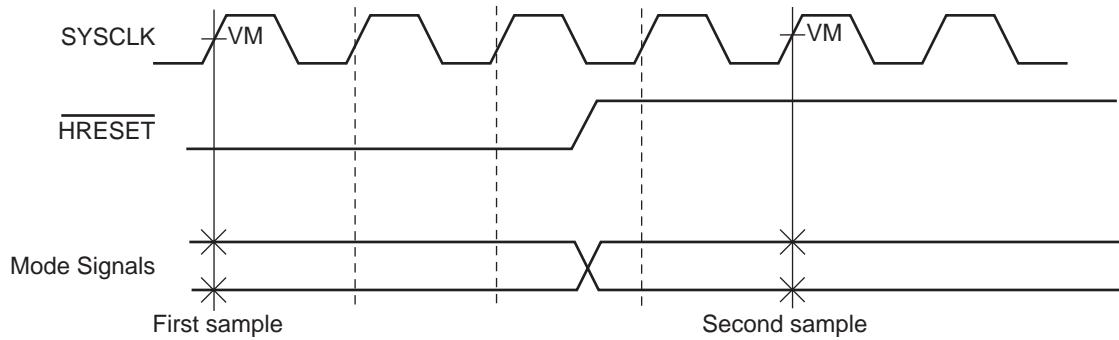

Figure 11 provides the mode select input timing diagram for the PC7410. The mode select inputs are sampled twice, once before and once after HRESET negation.

**Figure 11.** Mode Input Timing Diagram

where VM = Midpoint Voltage ( $OV_{DD}/2$ )

#### L2 Clock AC Specifications

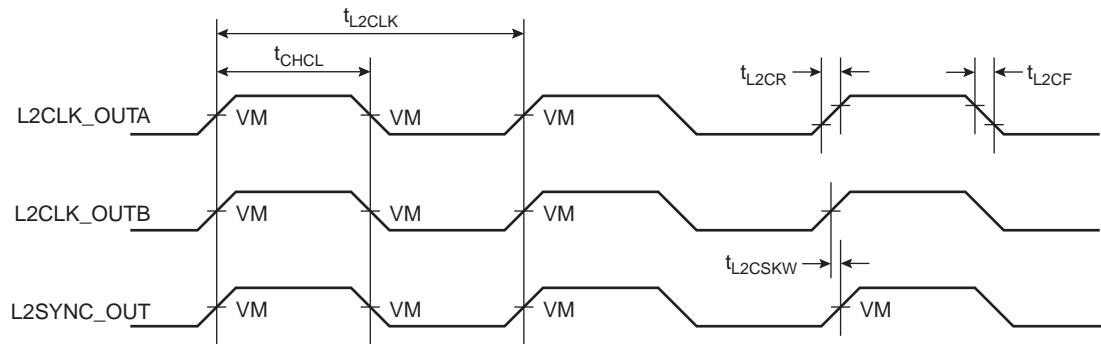

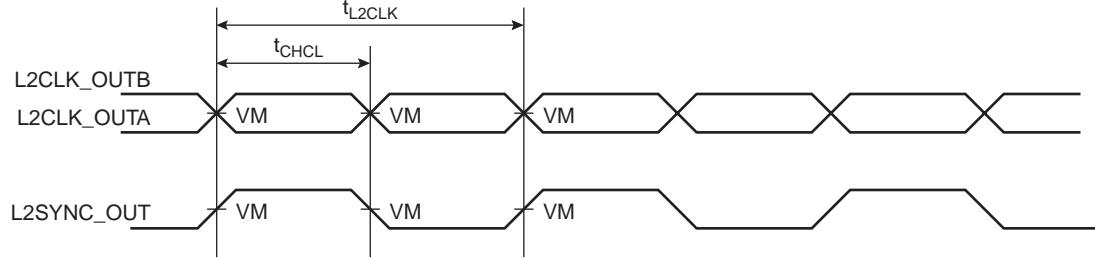

The L2CLK frequency is programmed by the L2 configuration register (L2CR[4:6]) core-to-L2 divisor ratio. See Table 18 for example core and L2 frequencies at various divisors. Table 12 provides the potential range of L2CLK output AC timing specifications as defined in Figure 12.

The L2SYNC\_OUT signal is intended to be routed halfway out to the SRAMs and then returned to the L2SYNC\_IN input of the PC7410 to synchronize L2CLKOUT at the SRAM with the processor's internal clock. L2CLKOUT at the SRAM can be offset forward or backward in time by shortening or lengthening the routing of L2SYNC\_OUT to L2SYNC\_IN. See Motorola Application Note AN179/D "PowerPC Backside L2 Timing Analysis for the PCB Design Engineer."

The minimum L2CLK frequency of Table 12 is specified by the maximum delay of the internal DLL. The variable-tap DLL introduces up to a full clock period delay in the L2CLKOUTA, L2CLKOUTB and L2SYNC\_OUT signals so that the returning L2SYNC\_IN signal is phase aligned with the next core clock (divided by the L2 divisor ratio). Do not choose a core-to-L2 divisor which results in an L2 frequency below this minimum, or the L2CLKOUT signals provided for SRAM clocking will not be phase aligned with the PC7410 core clock at the SRAMs.

The maximum L2CLK frequency shown in Table 12 is the core frequency divided by one. Very few L2 SRAM designs will be able to operate in this mode. Most designs will select a greater core-to-L2 divisor to provide a longer L2CLK period for read and write access to the L2 SRAMs. The maximum L2CLK frequency for any application of the PC7410 will be a function of the AC timings of the PC7410, the AC timings for the SRAM, bus loading and printed circuit board trace length.

Atmel is similarly limited by system constraints and cannot perform tests of the L2 interface on a socketed part on a functional tester at the maximum frequencies of Table 12. Therefore, functional operation and AC timing information are tested at core-to-L2 divisors of 2 or greater.

L2 input and output signals are latched or enabled respectively by the internal L2CLK (which is SYSCLK multiplied up to the core frequency and divided down to the L2CLK frequency). In other words, the AC timings of Table 13 are entirely independent of L2SYNC\_IN. In a closed loop system, where L2SYNC\_IN is driven through the board trace by L2SYNC\_OUT, L2SYNC\_IN only controls the output phase of L2CLKOUTA and L2CLKOUTB which are used to latch or enable data at the SRAMs. However, since in a closed loop system L2SYNC\_IN is held in phase alignment with the internal L2CLK, the signals of Table 13 are referenced to this signal rather than the not-externally-visible internal L2CLK. During manufacturing test, these times are actually measured relative to SYSCLK.

**Table 12.** L2CLK Output AC Timing Specifications at Recommended Operating Conditions (See Table 4)

| Symbol                     | Parameter                                     | 400 MHz |           | 450 MHz |           | 500 MHz |           | Unit  |

|----------------------------|-----------------------------------------------|---------|-----------|---------|-----------|---------|-----------|-------|

|                            |                                               | Min     | Max       | Min     | Max       | Min     | Max       |       |

| $f_{L2CLK}^{(1)(4)}$       | L2CLK frequency                               | 133     | 400       | 133     | 400       | 133     | 400       | MHz   |

| $t_{L2CLK}$                | L2CLK cycle time                              | 2.5     | 7.5       | 2.5     | 7.5       | 2.5     | 7.5       | ns    |

| $t_{CHCL}/t_{L2CLK}^{(2)}$ | L2CLK duty cycle                              | 50      |           | 50      |           | 50      |           | %     |

|                            | Internal DLL-relock time <sup>(3)</sup>       | 640     |           | 640     |           | 640     | -         | L2CLK |

|                            | DLL capture window <sup>(5)</sup>             | 0       | 10        | 0       | 10        | 0       | 10        | ns    |

| $t_{L2CSKW}$               | L2CLKOUT output-to-output skew <sup>(6)</sup> | -       | 50        | -       | 50        | -       | 50        | ps    |

|                            | L2CLKOUT output jitter <sup>(6)</sup>         | -       | $\pm 150$ | -       | $\pm 150$ | -       | $\pm 150$ | ps    |

Notes:

1. L2CLK outputs are L2CLK\_OUTA, L2CLK\_OUTB, and L2SYNC\_OUT pins. The L2CLK frequency to core frequency settings must be chosen such that the resulting L2CLK frequency and core frequency do not exceed their respective maximum or minimum operating frequencies. The maximum L2CLK frequency will be system-dependent. L2CLK\_OUTA and L2CLK\_OUTB must have equal loading.

2. The nominal duty cycle of the L2CLK is 50% measured at midpoint voltage.

3. The DLL re-lock time is specified in terms of L2CLKs. The number in the table must be multiplied by the period of L2CLK to compute the actual time duration in nanoseconds. Re-lock timing is guaranteed by design and characterization.

4. The L2CR[L2SL] bit should be set for L2CLK frequencies less than 110 MHz. This adds more delay to each tap of the DLL.

5. Allowable skew between L2SYNC\_OUT and L2SYNC\_IN.

6. Guaranteed by design and not tested. This output jitter number represents the maximum delay of one tap forward or one tap back from the current DLL tap as the phase comparator seeks to minimize the phase difference between L2SYNC\_IN and the internal L2CLK. This number must be comprehended in the L2 timing analysis. The input jitter on SYSCLK affects L2CLKOUT and the L2 address/data/control signals equally and therefore is already comprehended in the AC timing and does not have to be considered in the L2 timing analysis.

**Figure 12.** L2CLK\_OUT Output Timing Diagram

## L2 Single-Ended Clock Mode

## L2 Differential Clock Mode

Note: VM = Midpoint Voltage ( $L2OV_{DD}/2$ )

## L2 Bus AC Specifications

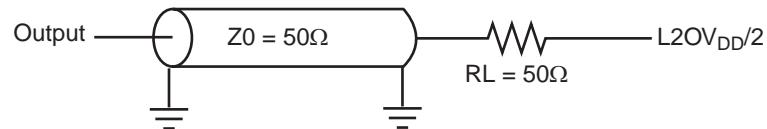

Table 13 provides the L2 bus interface AC timing specifications for the PC7410 as defined in Figure 13 and Figure 14 for the loading conditions described in Figure 15.

**Table 13.** L2 Bus Interface AC Timing Specifications at  $V_{DD} = AV_{DD} = L2AV_{DD} = 1.8V \pm 100mV$  or  $1.5V \pm 50mV$  ;  $-55^\circ C \leq T_j \leq 125^\circ C$ ,  $L2OV_{DD} = 2.5V \pm 100mV$  or  $L2OV_{DD} = 1.8V \pm 100mV$

| Symbol                                 | Parameter                                                                                                                                                                       | 400, 450, 500 MHz        |                          | Unit |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------|

|                                        |                                                                                                                                                                                 | Min                      | Max                      |      |

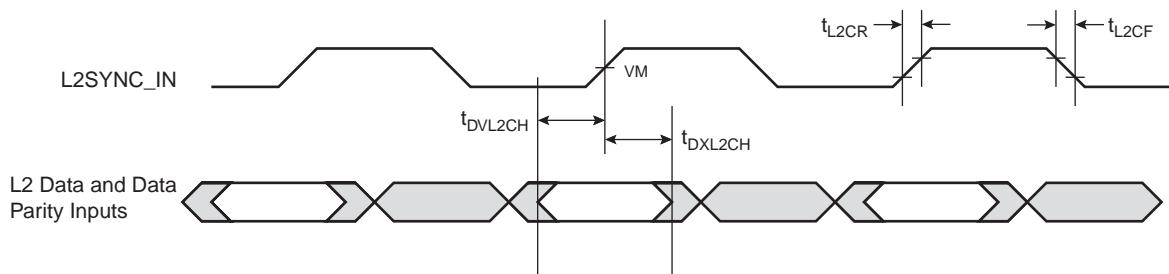

| $t_{L2CR}$ & $t_{L2CF}$ <sup>(1)</sup> | L2SYNC_IN rise and fall time                                                                                                                                                    |                          | 1.0                      | ns   |

| $t_{DVL2CH}$ <sup>(2)</sup>            | Setup Times<br>Data and parity                                                                                                                                                  | 1.5                      |                          | ns   |

| $t_{DXL2CH}$ <sup>(2)</sup>            | Input Hold Times<br>Data and parity                                                                                                                                             |                          | 0.0                      | ns   |

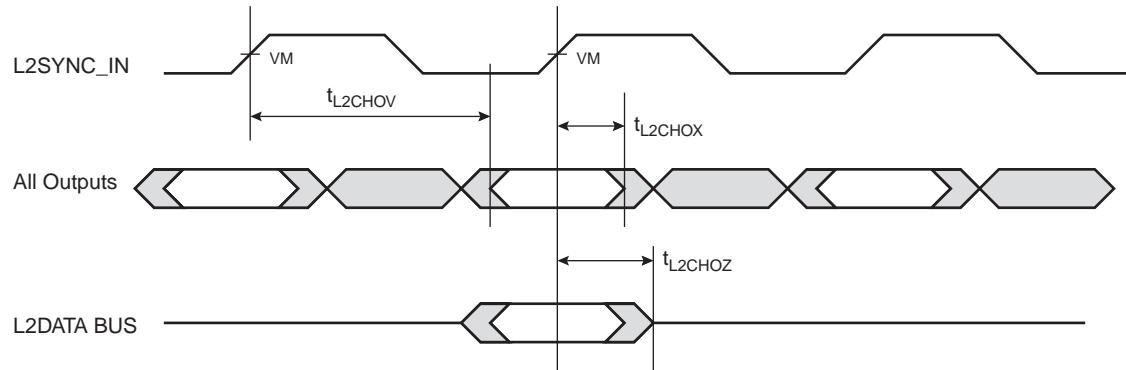

| $t_{L2CHOV}$ <sup>(3)(4)</sup>         | Valid Times<br>All outputs when L2CR[14:15] = 00<br>All outputs when L2CR[14:15] = 01<br>All outputs when L2CR[14:15] = 10<br>All outputs when L2CR[14:15] = 11                 |                          | 2.5<br>2.5<br>2.9<br>3.5 | ns   |

| $t_{L2CHOX}$ <sup>(3)</sup>            | Output Hold Times<br>All outputs when L2CR[14:15] = 00<br>All outputs when L2CR[14:15] = 01<br>All outputs when L2CR[14:15] = 10<br>All outputs when L2CR[14:15] = 11           | 0.4<br>0.8<br>1.2<br>1.6 |                          | ns   |

| $t_{L2CHOZ}$                           | L2SYNC_IN to high impedance<br>All outputs when L2CR[14:15] = 00<br>All outputs when L2CR[14:15] = 01<br>All outputs when L2CR[14:15] = 10<br>All outputs when L2CR[14:15] = 11 |                          | 2.0<br>2.5<br>3.0<br>3.5 | ns   |

Notes:

1. Rise and fall times for the L2SYNC\_IN input are measured from 20% to 80% of  $L2OV_{DD}$ .

2. All input specifications are measured from the midpoint of the signal in question to the midpoint voltage of the rising edge of the input L2SYNC\_IN (see Figure 13). Input timings are measured at the pins.

3. All output specifications are measured from the midpoint voltage of the rising edge of L2SYNC\_IN to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive  $50\ \Omega$  load (see Figure 15).

4. The outputs are valid for both single-ended and differential L2CLK modes. For pipelined registered synchronous burst RAMs, L2CR[14:15] = 00 is recommended. For pipelined late-write synchronous burst SRAMs, L2CR[14:15] = 10 is recommended.

**Figure 13.** L2 Bus Input Timing Diagram

Note: VM = Midpoint Voltage ( $L2OV_{DD}/2$ )

**Figure 14.** L2 Bus Output Timing Diagram

Note: VM = Midpoint Voltage ( $L2OV_{DD}/2$ )

**Figure 15.** AC Test Load for the L2 Interface

## IEEE 1149.1 AC Timing Specifications

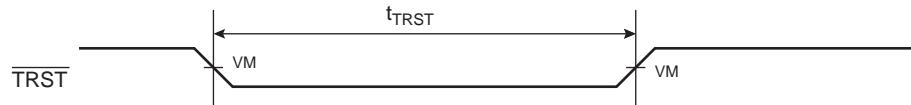

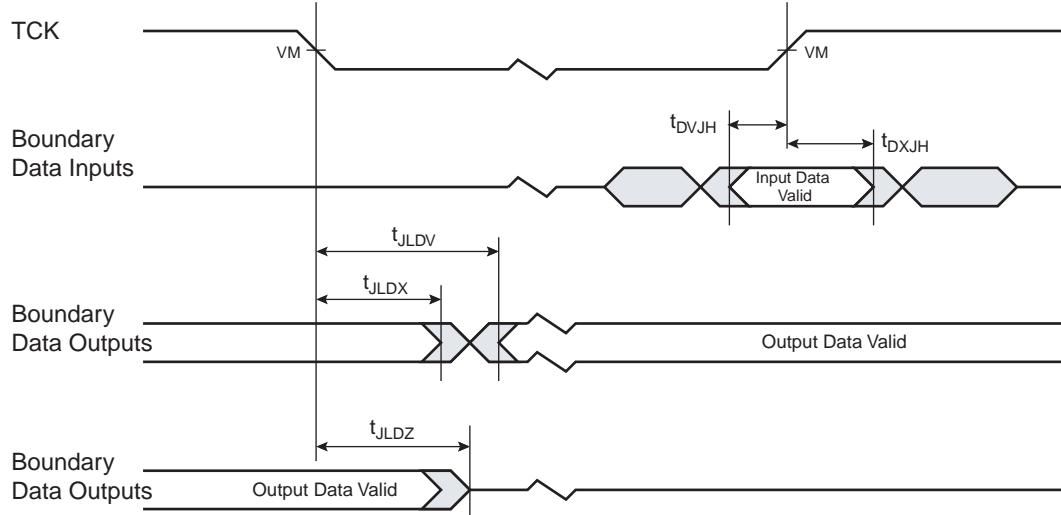

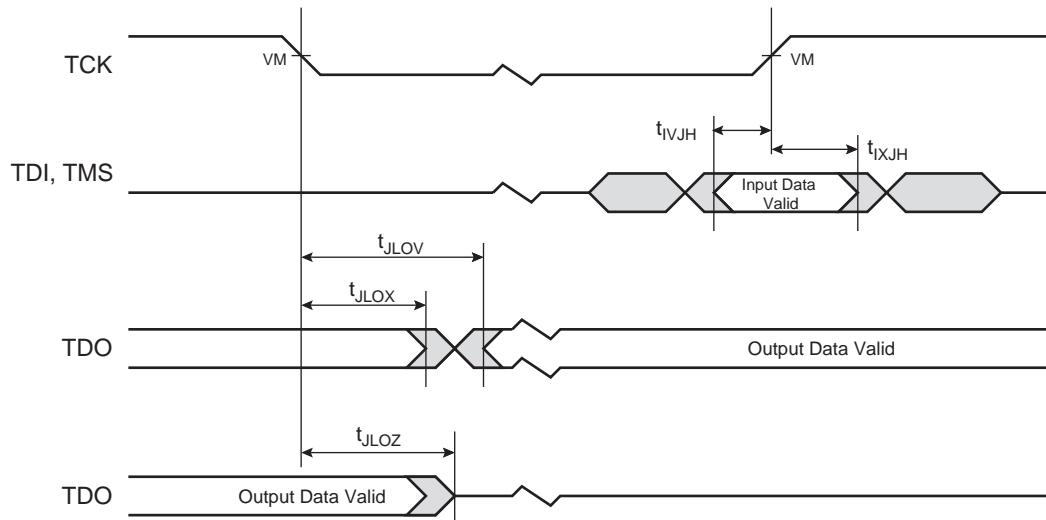

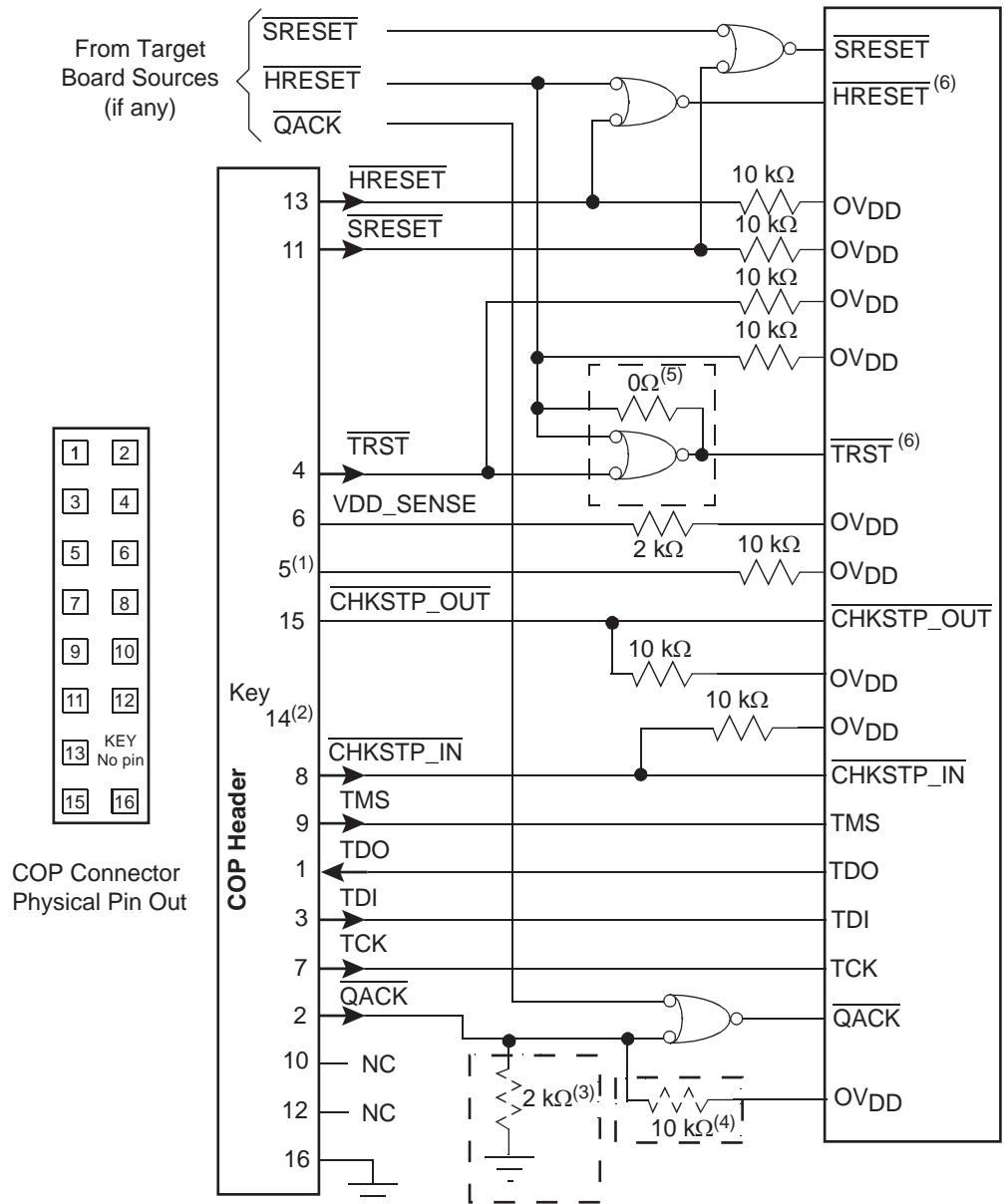

Table 14 provides the IEEE 1149.1 (JTAG) AC timing specifications as defined in Figure 16, Figure 17, Figure 18 and Figure 19.

**Table 14.** JTAG AC Timing Specifications (Independent of SYSCLK) <sup>(1)</sup>at Recommended Operating Conditions (see Table 4)

| Symbol                                                    | Parameter                                                  | Min      | Max      | Unit |

|-----------------------------------------------------------|------------------------------------------------------------|----------|----------|------|

| $f_{TCLK}$                                                | TCK frequency of operation                                 | 0        | 33.3     | MHz  |

| $t_{TCLK}$                                                | TCK cycle time                                             | 30       |          | ns   |

| $t_{JHJL}$                                                | TCK clock pulse width measured at OVDD/2                   | 15       |          | ns   |

| $t_{JR}$ & $t_{JF}$                                       | TCK rise and fall times                                    | 0        | 2        | ns   |

| $t_{TRST}$ <sup>(2)</sup>                                 | TRST assert time                                           | 25       |          | ns   |

| $t_{DVJH}$ <sup>(3)</sup><br>$t_{IVJH}$                   | Input Setup Times:<br>Boundary-scan data<br>TMS, TDI       | 4<br>0   |          | ns   |

| $t_{DXJH}$ <sup>(3)</sup><br>$t_{IXJH}$                   | Input Hold Times:<br>Boundary-scan data<br>TMS, TDI        | 20<br>25 |          | ns   |

| $t_{JLDV}$ <sup>(4)</sup><br>$t_{JLOV}$                   | Valid Times:<br>Boundary-scan data<br>TDO                  | 4<br>4   | 20<br>25 | ns   |

| $t_{JLDZ}$ <sup>(4)(5)</sup><br>$t_{JLOZ}$ <sup>(5)</sup> | TCK to output high impedance:<br>Boundary-scan data<br>TDO | 3<br>3   | 19<br>9  | ns   |

Notes:

1. All outputs are measured from the midpoint voltage of the falling/rising edge of TCLK to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50  $\Omega$  load (see Figure 16). Time-of-flight delays must be added for trace lengths, vias and connectors in the system.

2. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

3. Non-JTAG signal input timing with respect to TCK.

4. Non-JTAG signal output timing with respect to TCK.

5. Guaranteed by design and characterization

**Figure 16.** Alternate AC Test Load for the JTAG Interface

**Figure 17.** JTAG Clock Input Timing Diagram

Note: VM = Midpoint Voltage (OV<sub>DD</sub>/2)

**Figure 18.**  $\overline{\text{TRST}}$  Timing Diagram

Note: VM = Midpoint Voltage ( $\text{OV}_{\text{DD}}/2$ )

**Figure 19.** Boundary-scan Timing Diagram

Note: VM = Midpoint Voltage ( $\text{OV}_{\text{DD}}/2$ )

**Figure 20.** Test Access Port Timing Diagram

Note: VM = Midpoint Voltage ( $\text{OV}_{\text{DD}}/2$ )

## Preparation for Delivery

### Handling

MOS devices must be handled with certain precautions to avoid damage due to accumulation of static charge. Input protection devices have been designed in the chip to minimize the effect of static buildup. However, the following handling practices are recommended:

- Devices should be handled on benches with conductive and grounded surfaces.

- Ground test equipment, tools and operator.

- Do not handle devices by the leads.

- Store devices in conductive foam or carriers.

- Avoid use of plastic, rubber or silk in MOS areas.

- Maintain relative humidity above 50% if practical.

- For CI-CGA packages, use specific tray to take care of the highest height of the package compared with the normal CBGA.

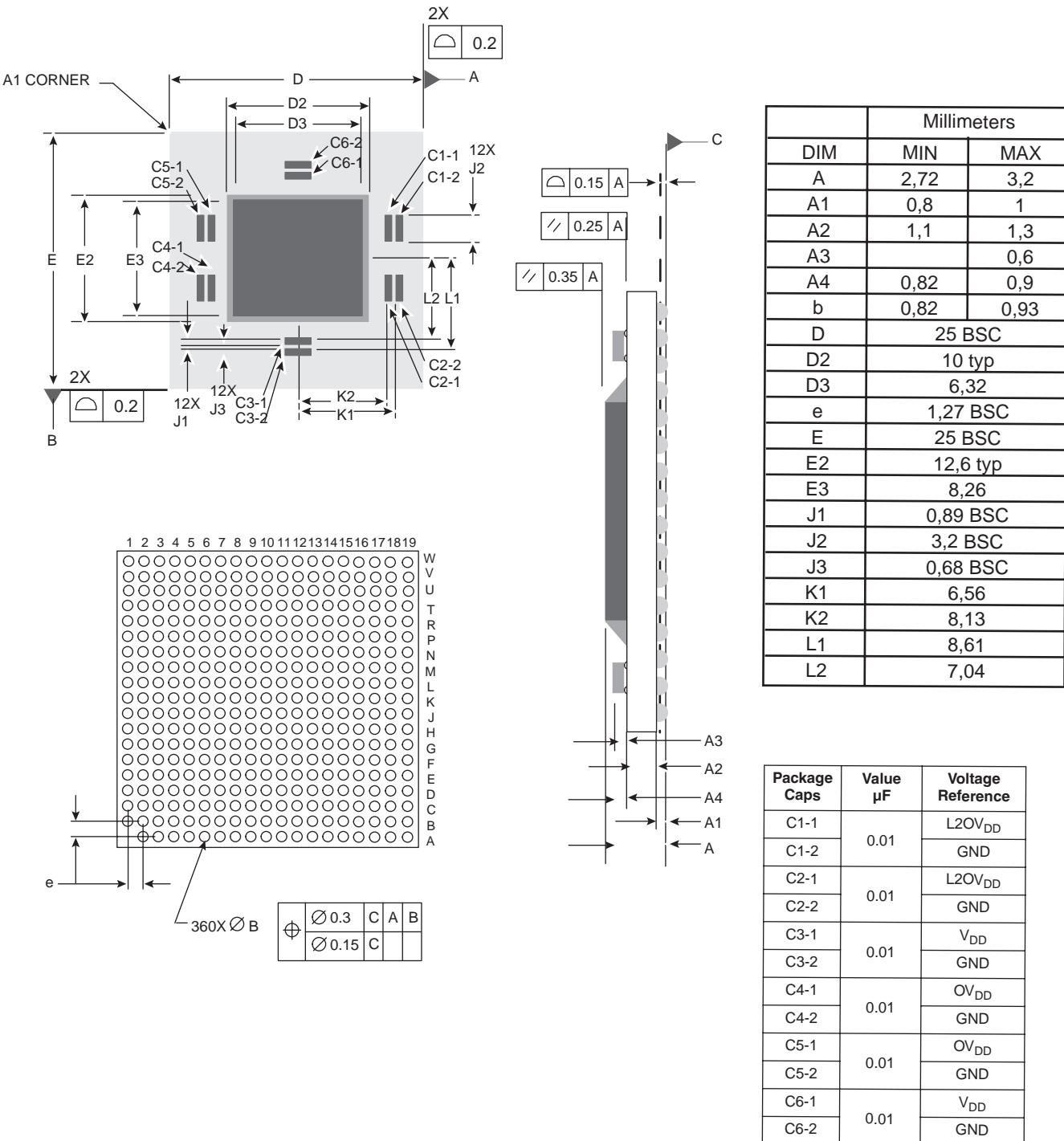

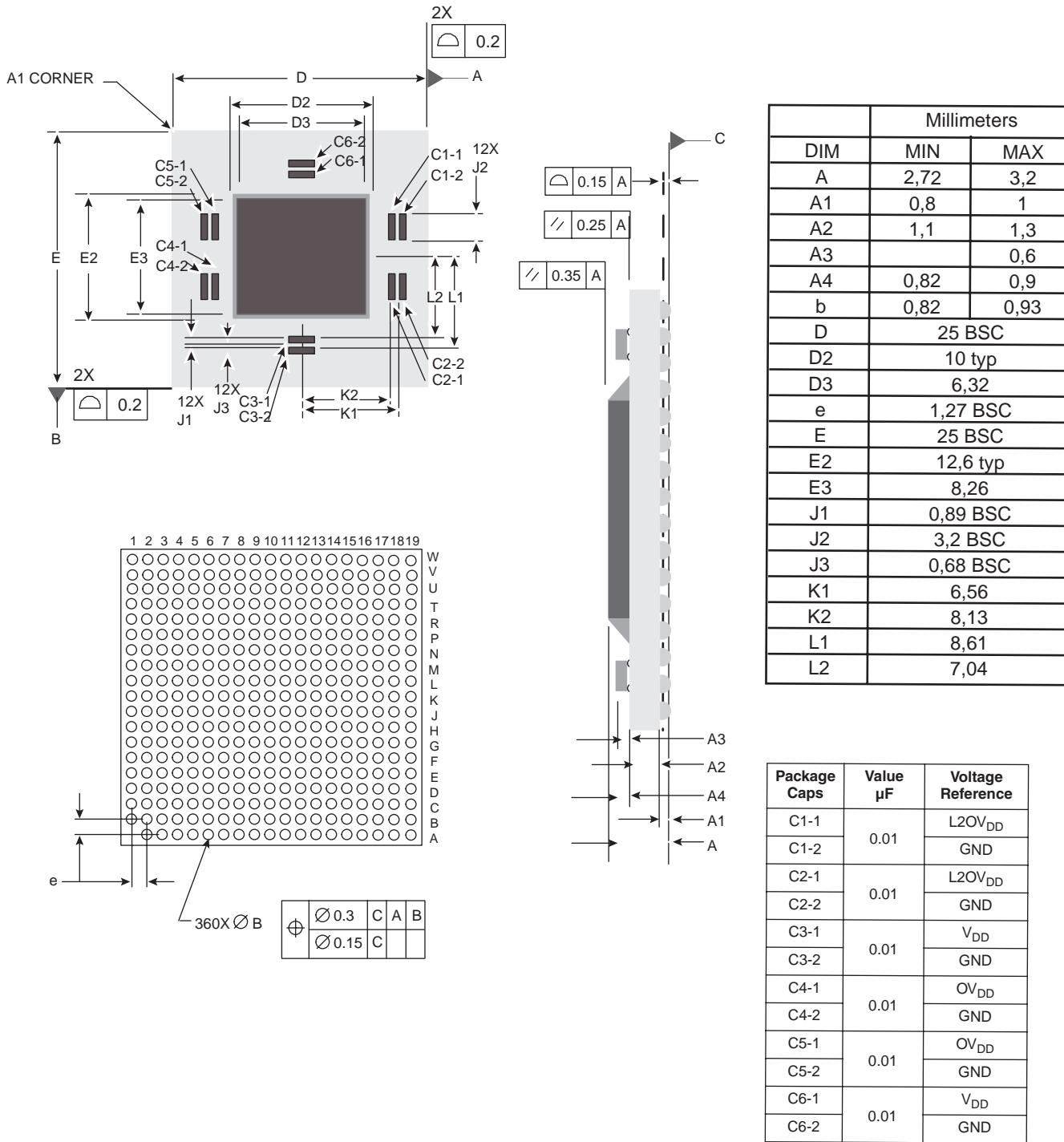

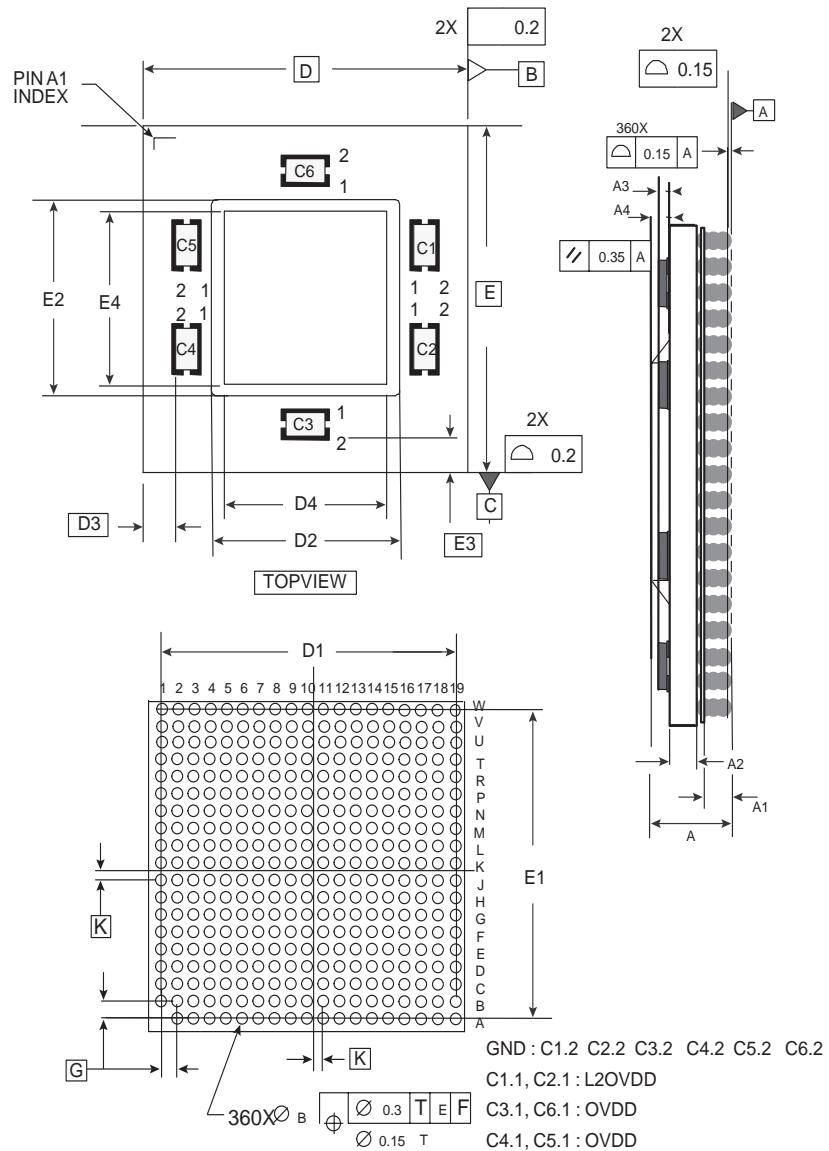

## Package Mechanical Data

### Parameters

The package parameters are as provided in the following list. The package type is 25x25 mm, 360-lead CBGA, HiTCE and CI-CGA.

**Table 15.** Package Parameters

| Parameter               |                                                   |

|-------------------------|---------------------------------------------------|

| Package outline         | 25 mm x 25 mm                                     |

| Interconnects           | 360 (19 x 19 ball array minus one)                |

| Pitch                   | 1.27 mm (50 mil)                                  |

| Minimum module height   | 2.65 mm (CBGA, HiTCE), 3.65 mm (CI-CGA)           |

| Maximum module height   | 3.20 mm (CBGA), 3.24 mm (HiTCE), 4.20 mm (CI-CGA) |

| Ball or column diameter | 0.89 mm (35 mil)                                  |

The following remarks apply to Figure 26 and Figure 27:

- Dimensions and tolerancing are as per ASME Y14.5M-1994.

- All dimensions are in millimeters.

- Top side A1 corner index is a metallized feature with various shapes. Bottom side A1 corner is designated with a ball missing from the array.

- Dimension B is the maximum solder ball diameter measured parallel to datum A.

- D2 and E2 define the area occupied by the die and underfill. Actual size of this area may be smaller than shown. D3 and E3 are the minimum clearance from the package edge to the chip capacitors.

## Pin Assignment

### BGA360 Package

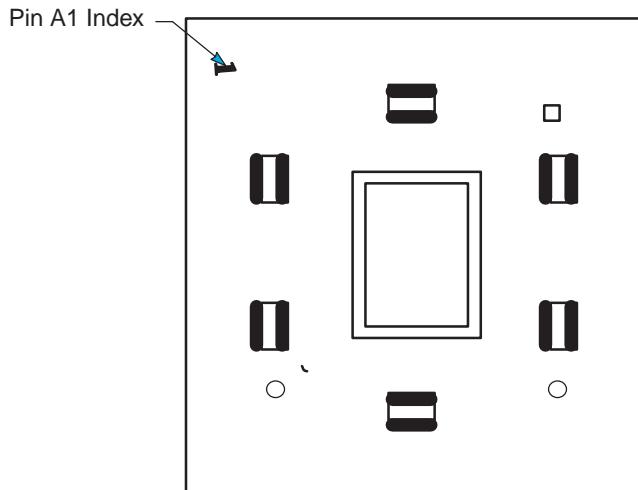

Figure 21, Figure 22, Figure 23 and Figure 24 show top views of the packages available for the PC7410. Note that these drawings are not to scale.

**Figure 21.** Top View of 360-Ball CBGA and 360-Pin CI-CGA Packages

**Figure 22.** Top View of 360-pin CBGA and CI-CGA Packages

|   | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|

| A | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| B | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| C | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| D | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| E | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| F | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| G | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| H | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| J | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| K | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| L | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| M | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| N | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| P | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| R | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| T | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| U | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| V | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

| W | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○ | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  | ○  |    |

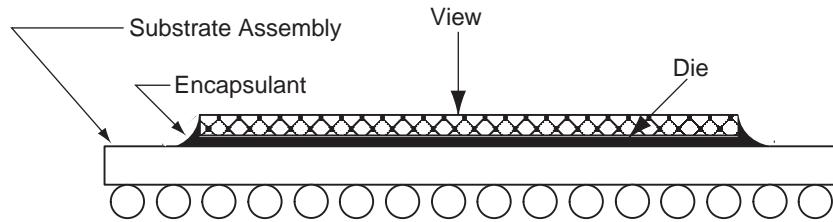

**Figure 23.** Cross-section of 360-ball CBGA and HiTCE Package

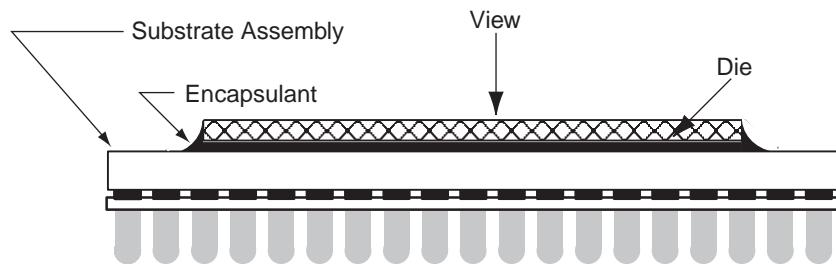

**Figure 24.** Cross-section of 360-column CI-CGA Package

**Table 16.** Pinout Listing for the PC7410, 360-ball CBGA and CI-CGA packages

| Signal Name                       | Pin Number                                                                                                                           | Active | I/O    | I/F Select <sup>(1)</sup> |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------|--------|---------------------------|

| A[0:31]                           | A13, D2, H11, C1, B13, F2, C13, E5, D13, G7, F12, G3, G6, H2, E2, L3, G5, L4, G4, J4, H7, E1, G2, F3, J7, M3, H3, J2, J6, K3, K2, L2 | High   | I/O    | BVSEL                     |

| AACK                              | N3                                                                                                                                   | Low    | Input  | BVSEL                     |

| ABB <sup>(12)</sup>               | L7                                                                                                                                   | Low    | Output | BVSEL                     |

| AMON[0] <sup>(12)</sup>           |                                                                                                                                      |        |        |                           |