#### **PRELIMINARY**

September 2003 Revision 1.0

## PC87427 ServerI/O with SensorPath™ Health Monitoring

### **General Description**

The National Semiconductor PC87427 is targeted for a wide range of servers, workstations and high-end desktops that use the Low Pin Count (LPC) bus for the host interface and an SMBus<sup>®</sup> interface for either a Baseboard Management Controller (BMC) or mini-BMC (mBMC), both of which are optional.

For LPC and SMBus access, the PC87427 features a fast X-Bus, over which boot flash and I/O devices can be accessed. The PC87427 supports X-Bus address line forcing (to 0 or 1) to create memory windows for BIOS data storage.

When  $V_{SB}$  exists, the BMC or mBMC can access the PC87427 and its fast X-Bus via SMBus. The SMBus also controls serial port float, RTC access, and serial port interconnection (snoop and take-over modes). In addition, the PC87427 provides routing of up to two selected LPC I/O port transactions to the GPIO Extension Port.

The PC87427 provides a V<sub>SB</sub>-powered high-frequency clock for on-chip peripherals; it also provides a configurable high-frequency clock for other V<sub>SB</sub>-powered platform components.

The PC87427 supports SensorPath health monitor interface to LMPCxx sensors, fan monitoring and control, and a chassis intrusion detector.

The System Wake-Up Control (SWC) module supports flexible wake-up and power-off request mechanisms for all platforms (i.e., with or without BMC/mBMC).

The PC87427 supports both I/O and memory mapping of module registers and enables building legacy-free systems.

The PC87427 also incorporates a Floppy Disk Controller (FDC), two serial ports (UARTs), a Keyboard and Mouse Controller (KBC), General-Purpose Input/Output (GPIO), GPIO extension for additional off-chip GPIO ports, and an interrupt serializer for parallel IRQs.

#### **Outstanding Features**

- Legacy-reduced Advanced I/O, optimized for high-end platforms. Legacy modules: FDC, two Serial Ports (UARTs) and a Keyboard and Mouse Controller (KBC).

- SensorPath system health support for LMXX sensors, fan monitor/control, and chassis intrusion detection, for all platforms (i.e., with or without a BMC or mBMC).

- 8/16-bit fast X-Bus extension for boot flash, memory and I/O.

- I/O-mapped and memory-mapped registers.

- V<sub>SB</sub>-powered SMBus access to modules and fast X-Bus.

- Two sets of BIOS code and data support, for main and back-up BIOS.

- Extremely low current consumption in Battery Backup mode.

- Serial Interface for manageability (Serial Interface M). Two-to-one multiplexing of Serial Ports 1 and 2.

- 52 GPIO ports with a variety of wake-up events, plus GPIO extension for additional off-chip GPIO ports.

- Watchdog for autonomous system recovery for BIOS Boot process and for operating system use.

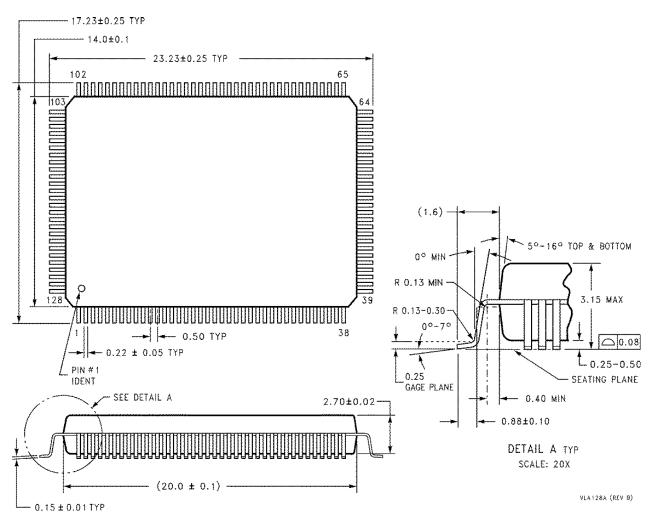

- 128-pin PQFP package.

#### **Block Diagram** PS/2 **KBC** Fan Fan Serial LPC Serial Serial Serial Floppy Disk Serial PWM Tach Interface 1 Interface 2 Interface M Interface Interfaces **Ports** IRQ Interface Clock Data Route Matrix ServerI/O Clock LPC Bus Keyboard & Fan Monitor SMBus Slave Serial Serial **FDC** $V_{DD}$ Mousé Controller and Control Interface Interface Port 1 Port 2 Internal Clocks $V_{BAT}$ Clock Health Monitor **GPIO GPIO** X-Bus $V_{SB}$ System Wake-Up Control RTC Watchdog Generator Extension Ports Extension and Control $-\Box$ Power SCI & Chassis 32.768 Low-F High-F Wake-Up I/O Port SensorPath **WDO** XIRQ X-Bus SMI Intrusion KHz Clock Clock Ports Extension Interface Interface

National Semiconductor and TRI-STATE® are registered trademarks of National Semiconductor Corporation. SensorPath™ is a trademark of National Semiconductor Corporation. All other brand or product names are trademarks or registered trademarks of their respective holders.

#### **Features**

#### **System Health Support**

- SensorPath interface to sensors optimizes digital/analog partitioning

- Simplifies board design and routing

- Supports distributed sensors and centralized control

- Off-loads SMBus, faster boot time

- Fan Monitor and Control (FMC)

- Four PWM-based fan controls

- Eight 16-bit resolution tachometer inputs

- Software or local temperature feedback control

- Chassis intrusion detection

#### **Bus Interfaces**

- LPC Bus Interface

- Based on Intel's LPC Interface Specification Revision 1.0, September 29, 1997

- Synchronous cycles using up to 33 MHz bus clock

- 8-bit I/O and 8-bit Memory read and write cycles

- Up to four 8-bit DMA channels

- Serial IRQ

- Supports bootable memory

- Supports LPC and FWH boot transactions

- Supports registers memory and I/O mapping

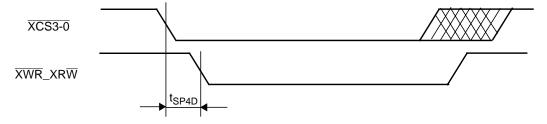

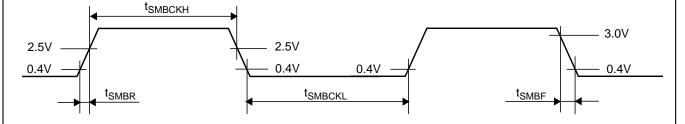

- SMBus Interface

- Compliant with SMBus Specification Revision 2.0, August 3, 2000

- Enables a system controller to access the internal functions and the fast X-Bus extension

- Proprietary commands for read/write byte from/to:

- Internal register

- □ X-Bus I/O device

- □ X-Bus memory device

- Slave address:

- One of two values selected by strap

- Programmable through the LPC bus

- V<sub>BAT</sub> backed-up

- Supports SMBALERT

- Concurrent access with the LPC bus

- V<sub>SB</sub> powered

- Optional internal pull-up on the two SMBus pins

- Fast X-Bus Extension

- Supports I/O and memory read/write operations

- 8- or 16-bit data bus, 28-bit addressing

- Accessible from both LPC bus and SMBus

- V<sub>SB</sub> powered

- Boot configuration selected by straps

- Programmable protection control for access from the LPC bus

- Supports three XIRQ external interrupts

- Multiplexed address-data lines:

- □ Four direct address lines

- Partial non-multiplexed option

- Four chip-select outputs, each supporting multiple zones:

- ☐ Two BIOS memory zones (up to 32 Mbytes total)

- ☐ Two user-defined memory zones (up to 32 Mbytes total)

- □ Four user-defined I/O zones

- Address line forcing (to 0 or 1) for access to two BIOS code and data sets

- Optional indirect addressing of memory

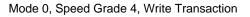

- XRD-XEN or XWR-XR/W mode support

- Supports both slow and fast devices

- For faster transactions in 16-bit data bus, strobe signals for address latches change automatically only when the address is changed

- Configuration Control

- Compliant with PC01 Specification Revision 1.0, 1999-2000

- Compliant with Hardware Design Guide Version 3.0 for Microsoft Windows 2000 Server, June 30 2000

- Plug and Play (PnP) Configuration register structure

- Base Address strap, to setup the address of the Index-Data register pair

- Flexible resource allocation for all logical devices:

- Relocatable base address

- □ 15 IRQ routing options to serial IRQ

- Up to four optional 8-bit DMA channels

- SMBus control over pin multiplexing, module disable and output TRI-STATE<sup>®</sup> for all Legacy modules

#### **Legacy Modules**

- Serial Ports 1 and 2

- Software compatible with the 16550A and the 16450

- Supports shadow register for write-only bit monitoring

- UART data rates up to 1.5 Mbaud

- Three sets of Serial Interface pins

- □ Serial Interface 1

- Snoop or Take-over connection of Serial Interface M

- ☐ Two-to-one multiplexing of Serial Ports 1 and 2 to Serial Interface 2

- Floppy Disk Controller (FDC)

- Programmable write protect

- Supports FM and MFM modes

- Supports Enhanced mode command for three-mode Floppy Disk Drive (FDD)

- Perpendicular recording drive support for 2.88 MB

- Burst and Non-Burst modes

- Full support for IBM Tape Drive Register (TDR) implementation of AT and PS/2 drive types

#### Features (Continued)

- 16-byte FIFO

- Error-free handling of data overrun and underrun

- Software compatible with the PC8477, which contains a superset of the FDC functions in the μDP8473, NEC μPD765A/B and N82077

- High-performance digital separator

- Supports standard 5.25" and 3.5" FDDs

- Supports one FDD

- Supports fast tape drives (2 Mbps) and standard tape drives (1 Mbps, 500 Kbps and 250 Kbps)

- Keyboard and Mouse Controller (KBC)

- 8-bit microcontroller, software compatible with 8042AH and PC87911

- Standard interface (60h, 64h, IRQ1 and IRQ12)

- Supports two external swapable PS/2 interfaces for keyboard and mouse

- Five programmable, dedicated, quasi-bidirectional I/O lines (Fast GA20/P21, KBRST/P20, P12, P16, P17)

#### **General-Purpose I/O Module**

- 52 General-Purpose I/O (GPIO) Ports

- Individually assigned to either LPC or SMBus control

- 45 ports individually configured as input or output

- 7 output ports

- Programmable features for each output pin:

- ☐ Drive type (open-drain, push-pull or TRI-STATE)

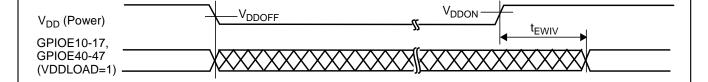

- □ TRI-STATE on V<sub>DD</sub>-fall detection for pins driving V<sub>DD</sub>-supplied devices

- Programmable option for internal pull-up resistor on each input pin

- Lock option for the configuration and data of each output pin

- 16 GPIO ports generate IRQ/SIOSMI/SIOSCI for wake-up events, with individual:

- □ Enable control

- □ Polarity and edge/level selection

- Debounce mechanism

- V<sub>SB</sub> powered

- Low-cost external GPIO port extension via a serial bus

- I/O ports transactions routing to the GPIO port extension

- Real-Time Clock

- DS1287, MC146818 and PC87911 compatible

- Battery-backed 242-byte CMOS RAM, in two banks (accessed through 70-71h and 72-73h)

- Selective lock mechanisms for the RTC RAM

- Y2K-compliant calendar, including century and automatic leap-year adjustment

- Time of day in seconds, minutes and hours, which allows a 12-hour or 24-hour format with optional adjustment for daylight saving time

- Separated SMBus access to RTC RAM and RTC Control D register

- Battery level measurement

#### **Power Management**

- Supports ACPI Specification Revision 2.0b, July 27, 2000

- System Wake-Up Control (SWC)

- Wake-up request on detection of:

- Preprogrammed Keyboard or Mouse sequence

- ☐ External modem ring from RI1 or RI2 on serial ports

- □ Predetermined RTC date and time alarm

- General-Purpose Input Events from up to 16 GPIO pins

- □ IRQs of internal logical devices

- Optional routing of power-up request to SERIRQ, SIOSMI, SIOSCI, PWBTOUT and ONCTL

- Routing control per input/output event combination

- Outputs enable/disable per event and system state combination (ACPI Sx states)

- Implements bank "b" of the ACPI registers

- Suspend modes via software emulation (control)

- Battery-backed event-logic configuration

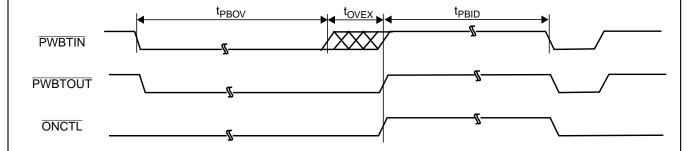

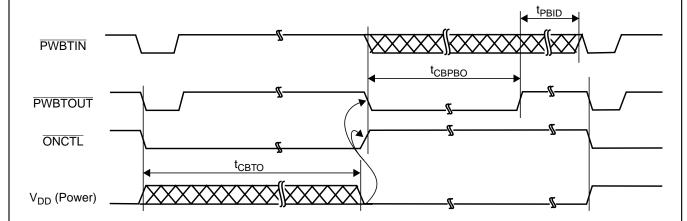

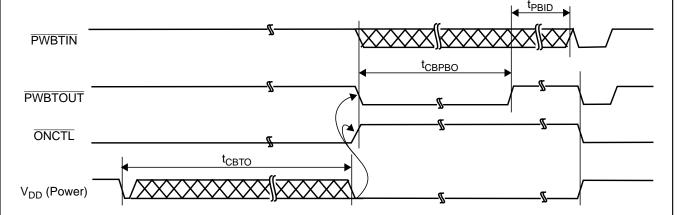

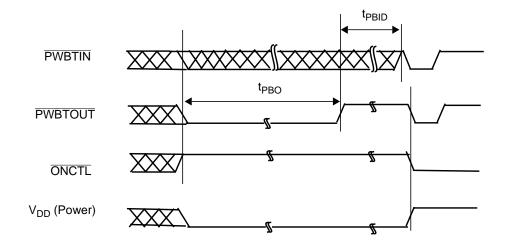

- Power Button support, featuring:

- □ On/Off control

- □ Power-off, 4-second override

- Power Button output

- Sleep Button support

- Power Supply On/Off control

- Supports Legacy- and ACPI-compatible Power Button

- Direct power supply control in response to wake-up events

- Programmable Crowbar time-out for "On" request

- On/Off control via software emulation

- Power-fail recovery

- Enhanced Power Management (PM), including:

- Special configuration registers for power down

- Reduced current leakage from pins

- Low-power CMOS technology

- Capability for disabling all modules

- Keyboard Events

- Wake-up on any key

- Supports programmable 8-byte sequence "password" for Power Management

- Simultaneous recognition of three programmable keys (sequences): "Power", "Sleep" and "Resume"

- Power Active Timers

- Two power-on, elapsed-time counters for the main  $(V_{DD})$  and standby  $(V_{SB})$  power supplies

- 32-bit counters, clocked by a 1-second clock

- V<sub>BAT</sub> backed-up counters

#### Features (Continued)

#### Watchdog

- Compliant with Watchdog Timer Hardware Requirements for Microsoft Windows .NET Server, April 2002

- Autonomous system reset and programmable address line forcing on expiration of watchdog timer

- Generates a 100 ms pulse at WDO pin

#### **Clocking, Supply and Package Information**

- Strap Input Controlled Operating Modes

- Base Address (BADDR) for the PnP Index-Data register pair

- Input clock presence (CKIN48) select

- X-Bus configuration (XCNF2-0) select

- SMBus slave address (SMBSA) select

- High frequency clock selection (HFCKS)

#### ■ Testability

- XOR tree structure

- Includes all the device pins (except the supply pins, oscillator pins and CHASSIS pin)

- ☐ Selected at power-up by strap input (TEST)

- TRI-STATE device pins, selected at power-up by strap input (TRIS)

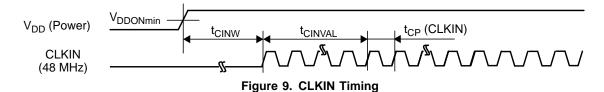

#### Clocks

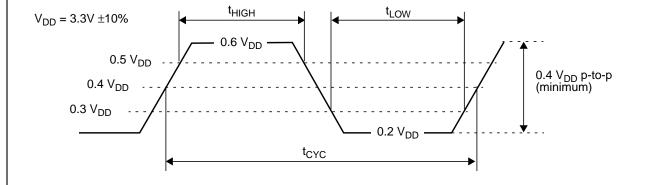

- LPC clock input (up to 33 MHz)

- ServerI/O modules clock: 48 MHz input or internal clock multiplier

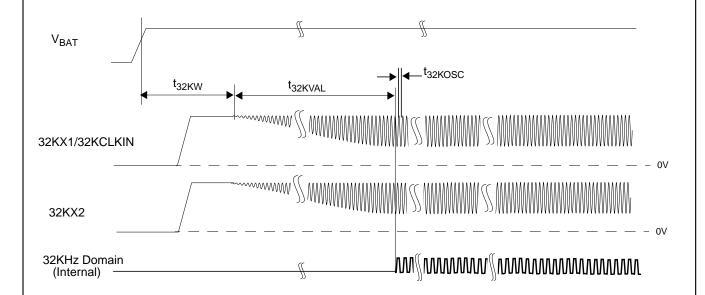

- 32.768 KHz crystal

- On-chip low-frequency clock generator:

- 32.768 KHz for RTC, System Wake-Up Control (SWC), Power Active timers and the high-frequency clock generator

- Very low power consumption

- □ V<sub>BAT</sub> powered

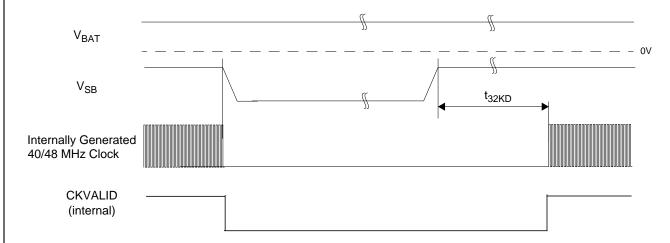

- On-chip high-frequency clock generator:

- □ Based on the 32.768 KHz clock

- V<sub>SB</sub> powered

- Clock outputs:

- □ LFCKOUT 32.768 KHz or 1 Hz

- ☐ HFCKOUT configurable up to 48 MHz. The default frequency 6, 10, 24 or 40 MHz, configurable by strap.

#### ■ Protection

- All pins are 5V tolerant and back-drive protected (except the LPC bus pins)

- Separate battery pin that includes an internal UL protection resistor

- GPIO multiplexing configuration lock

#### ■ Power Supply

- 3.3V supply operation

- Separate pins for main  $(V_{DD})$  and standby  $(V_{SB})$  power supplies

- Backup battery input for RTC, SWC and Power Active timers

- Separate pin for core voltage filtering (V<sub>CORF</sub>)

- Reduced standby power consumption

- Very low power consumption for RTC and timers (0.9 μA typical) from backup battery

#### Package

- 128-pin PQFP

### 1.0 Signal/Pin Connection and Description

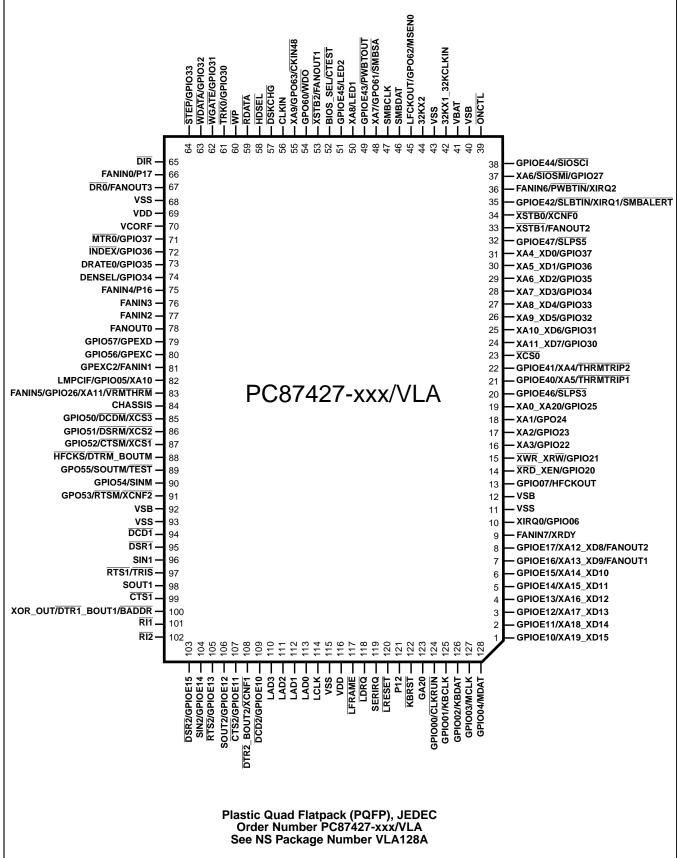

#### 1.1 CONNECTION DIAGRAM

xxx = Three-character identifier for National data, keyboard ROM and/or customer identification code.

#### 1.2 BUFFER TYPES AND SIGNAL/PIN DIRECTORY

The signal DC characteristics of the pins described in Section 1.4 are denoted by buffer type symbols, which are defined in Table 1. The pin multiplexing information refers to two different types of multiplexing:

- Multiplexed, denoted by a slash (/) between pins in the diagram in Section 1.1. Pins are shared between two different functions. Each function is associated with different board connectivity. Normally, the function selection is determined by the board design and cannot be changed dynamically. The multiplexing options must be configured by the BIOS on power-up to comply with the board implementation.

- Multiple Mode, denoted by an underscore (\_) between pins in the diagram in Section 1.1. Pins have two or more

modes of operation within the same function. These modes are associated with the same external (board)

connectivity. Mode selection can be controlled by the device driver through the registers of the functional block and

does not require a special BIOS setup upon power-up. These pins are not considered multiplexed pins from the

ServerI/O configuration perspective. The mode selection method (registers and bits), as well as the signal specification in each mode, are described within the functional description of the relevant functional block.

Table 1. Buffer Types

| Symbol            | Description                                                                   |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------|--|--|--|--|--|--|

| IN <sub>CS</sub>  | Input, CMOS compatible, with Schmitt Trigger                                  |  |  |  |  |  |  |

| IN <sub>OSC</sub> | Input, from crystal oscillator (not characterized)                            |  |  |  |  |  |  |

| IN <sub>PCI</sub> | Input, PCI 3.3V                                                               |  |  |  |  |  |  |

| IN <sub>SM</sub>  | Input, SMBus compatible                                                       |  |  |  |  |  |  |

| IN <sub>T</sub>   | put, TTL compatible                                                           |  |  |  |  |  |  |

| IN <sub>TS</sub>  | Input, TTL compatible, with Schmitt Trigger                                   |  |  |  |  |  |  |

| IN <sub>ULR</sub> | Input, power, resistor protected (not characterized)                          |  |  |  |  |  |  |

| O <sub>p/n</sub>  | Output, push-pull output buffer capable of sourcing $p$ mA and sinking $n$ mA |  |  |  |  |  |  |

| $OD_n$            | Output, open-drain output buffer capable of sinking <i>n</i> mA               |  |  |  |  |  |  |

| O <sub>OSC</sub>  | Output, to crystal oscillator (not characterized)                             |  |  |  |  |  |  |

| O <sub>PCI</sub>  | Output, PCI 3.3V                                                              |  |  |  |  |  |  |

| OD <sub>PCI</sub> | Output, open-drain, PCI 3.3V                                                  |  |  |  |  |  |  |

| PWR               | Power pin                                                                     |  |  |  |  |  |  |

| GND               | Ground pin                                                                    |  |  |  |  |  |  |

### 1.3 PIN MULTIPLEXING

The table below shows only multiplexed pins, their associated functional blocks and the configuration bits for the selection of the multiplexed options used in the PC87427.

**Table 2. Pin Multiplexing Configuration**

| Pin | Functional<br>Block | Signal    | Functional<br>Block | Signal                              | Functional<br>Block | Signal    | Functional<br>Block | Signal                           | Configuration<br>Select           |

|-----|---------------------|-----------|---------------------|-------------------------------------|---------------------|-----------|---------------------|----------------------------------|-----------------------------------|

| 1   |                     | GPIOE10   |                     | XA19_XD15                           |                     |           |                     |                                  | SIOCFC.XDATA16                    |

| 2   |                     | GPIOE11   |                     | XA18_XD14                           |                     |           |                     |                                  |                                   |

| 3   |                     | GPIOE12   |                     | XA17_XD13                           |                     |           |                     |                                  | SIOCFC.XDATA16                    |

| 4   |                     | GPIOE13   |                     | XA16_XD12                           |                     |           |                     |                                  |                                   |

| 5   | GPIO                | GPIOE14   |                     | XA15_XD11                           |                     |           |                     |                                  | SIOCFC.XDATA16                    |

| 6   |                     | GPIOE15   | X-Bus               | XA14_XD10                           |                     |           |                     |                                  | SIOCEC.XDAIA16                    |

| 7   |                     | GPIOE16   |                     | XA13_XD9                            |                     | FANOUT1   |                     |                                  | SIOCFC.XDATA16<br>SIOCFB.FANOUT1  |

| 8   |                     | GPIOE17   |                     | XA12_XD8                            | FMC                 | FANOUT2   |                     |                                  | SIOCFC.XDATA16 SIOCFB.FANOUT2     |

| 9   |                     |           |                     | XRDY                                |                     | FANIN7    |                     |                                  | SIOCF4.XRDYMUX                    |

| 10  |                     | GPIO06    |                     | XIRQ0                               |                     |           |                     |                                  | SIOCF5.XIRQ0MU                    |

| 13  |                     | GPIO07    | Clocks              | HFCKOUT                             |                     |           |                     |                                  | SIOCF4.HFCKMUX                    |

| 14  |                     | GPIO20    |                     | XRD_XEN                             |                     |           |                     |                                  |                                   |

| 15  |                     | GPIO21    |                     | $\overline{XWR}$ _XR $\overline{W}$ |                     |           |                     |                                  |                                   |

| 16  |                     | GPIO22    |                     | XA3                                 |                     |           |                     |                                  | SIOCE4 NOVBLIS                    |

| 17  |                     | GPIO23    | X-Bus               | XA2                                 |                     |           |                     |                                  | -SIOCF4.NOXBUS                    |

| 18  |                     | GPO24     |                     | XA1                                 |                     |           |                     |                                  |                                   |

| 19  |                     | GPIO25    |                     | XA0_XA20                            |                     |           |                     |                                  |                                   |

| 20  |                     | GPIOE46   | swc                 | SLPS3                               |                     |           |                     |                                  | SIOCF3.EXTSTMU                    |

| 21  | GPIO                | GPIOE40   |                     | XA5                                 | НМС                 | THRMTRIP1 |                     |                                  | SIOCF4.NOADDIR<br>SIOCFB.TRIP1    |

| 22  | GFIO                | GPIOE41   |                     | XA4                                 | HIVIC               | THRMTRIP2 |                     |                                  | SIOCF4.NOADDIR<br>SIOCFB.TRIP2    |

| 24  |                     | GPIO30    |                     | XA11_XD7                            |                     |           |                     |                                  |                                   |

| 25  |                     | GPIO31    |                     | XA10_XD6                            |                     |           |                     |                                  |                                   |

| 26  |                     | GPIO32    | X-Bus               | XA9_XD5                             |                     |           |                     |                                  |                                   |

| 27  |                     | GPIO33    |                     | XA8_XD4                             |                     |           |                     |                                  | SIOCF4.NOXBUS                     |

| 28  |                     | GPIO34    |                     | XA7_XD3                             |                     |           |                     |                                  | 310CF4.NOAB03                     |

| 29  |                     | GPIO35    |                     | XA6_XD2                             |                     |           |                     |                                  |                                   |

| 30  |                     | GPIO36    |                     | XA5_XD1                             |                     |           |                     |                                  |                                   |

| 31  |                     | GPIO37    |                     | XA4_XD0                             |                     |           |                     |                                  | 1                                 |

| 32  |                     | GPIOE47   | SWC                 | SLPS5                               |                     |           |                     |                                  | SIOCF3.EXTSTMU                    |

| 33  |                     | XSTB1     | FMC                 | FANOUT2                             |                     |           |                     |                                  | SIOCF5.XSTB1MU                    |

| 34  |                     | XSTB0     | Straps              | XCNF0                               |                     |           |                     |                                  |                                   |

| 35  | X-Bus               | XIRQ1     | GPIO                | GPIOE42                             |                     | SLBTIN    | SMBus               | SMBALERT                         | SIOCF3.SLBTIMUX & SIOCFC.XIRQ1MUX |

| 36  |                     | XIRQ2 FMC | FANIN6              | CMC                                 | PWBTIN              |           |                     | SIOCF3.PWBTIMUX SIOCFB.FANIN6MUX |                                   |

| 37  |                     | XA6       | GPIO                | GPIO27                              | SWC                 | SIOSMI    |                     |                                  | SIOCF3.SMIMUX & SIOCF4.NOADDIR    |

| 38  |                     |           |                     | GPIOE44                             |                     | SIOSCI    |                     |                                  | SIOCF3.SCIMUX                     |

**Table 2. Pin Multiplexing Configuration (Continued)**

| Pin | Functional<br>Block   | Signal            | Functional<br>Block | Signal  | Functional<br>Block | Signal  | Functional<br>Block | Signal | Configuration<br>Select             |  |

|-----|-----------------------|-------------------|---------------------|---------|---------------------|---------|---------------------|--------|-------------------------------------|--|

| 45  |                       | GPO62             | Clocks              | LFCKOUT | FDC                 | MSEN0   |                     |        | SIOCF4.LFCKMUX                      |  |

| 48  | GPIO                  | GPO61             | X-Bus               | XA7     | Straps              | SMBSA   |                     |        | SIOCF4.NOADDIR                      |  |

| 49  |                       | GPIOE43           |                     | PWBTOUT |                     |         |                     |        | SIOCF3.PWBTOMUX                     |  |

| 50  | X-Bus                 | XA8               | swc                 | LED1    |                     |         |                     |        | SIOCF4.NOADDIR                      |  |

| 51  | GPIO                  | GPIOE45           |                     | LED2    |                     |         |                     |        | SIOCF3.LED2MUX                      |  |

| 52  | X-Bus                 | BIOS_SEL          | Straps              | CTEST   |                     |         |                     |        |                                     |  |

| 53  | X-Bus                 | XSTB2             | FMC                 | FANOUT1 |                     |         |                     |        | SIOCF5.XSTB2MUX                     |  |

| 54  |                       | GPO60             | Watchdog            | WDO     |                     |         |                     |        | SIOCF2.WDOMUX                       |  |

| 55  | GPIO                  | GPO63             | X-Bus               | XA9     | Straps              | CKIN48  |                     |        | SIOCF4.NOADDIR                      |  |

| 61  |                       | GPIO30            |                     | TRK0    |                     |         |                     |        |                                     |  |

| 62  | CDIO                  | GPIO31            |                     | WGATE   |                     |         |                     |        | SIGOTO ODOANNIN                     |  |

| 63  | GPIO                  | GPIO32            | FDC                 | WDATA   |                     |         |                     |        | SIOCFC.GP3AMUX                      |  |

| 64  |                       | GPIO33            |                     | STEP    |                     |         |                     |        |                                     |  |

| 66  |                       | FANIN0            | KBC                 | P17     |                     |         |                     |        | SIOCF2.P17MUX                       |  |

| 67  | FMC                   | FANOUT3           |                     | DR0     |                     |         |                     |        | SIOCFB.FANOUT3                      |  |

| 71  |                       | GPIO37            | GPIO37              |         | MTR0                |         |                     |        |                                     |  |

| 72  | 0.010                 | GPIO36            | FDC                 | INDEX   |                     |         |                     |        | SIOCFC.GP3AMUX                      |  |

| 73  | GPIO                  | GPIO35            |                     | DRATE0  |                     |         |                     |        |                                     |  |

| 74  |                       | GPIO34            |                     | DENSEL  |                     |         |                     |        |                                     |  |

| 75  | FMC                   | FANIN4            | KBC                 | P16     |                     |         |                     |        | SIOCF2.P16MUX                       |  |

| 79  |                       | GPIO57            |                     | GPEXD   |                     |         |                     |        |                                     |  |

| 80  | GPIO                  | GPIO56            | GPIO                | GPEXC   |                     |         |                     |        | SIOCFC.GPEXMUX                      |  |

| 81  | FMC                   | FANIN1            |                     | GPEXC2  |                     |         |                     |        | SIOCFB.FANIN1MUX<br>SIOCFD.GPEXC2MU |  |

| 82  |                       | XA10              | НМС                 | LMPCIF  |                     | GPIO05  |                     |        | SIOCF4.NOADDIR & SIOCFD.LMPCIF      |  |

| 83  |                       | XA11              |                     | VRMTHRM |                     | GPIO26  | FMC                 | FANIN5 | SIOCF4.NOADDIR & SIOCFB.FANIN5      |  |

| 85  | X-Bus                 | XCS3              |                     | DCDM    | GPIO                | GPIO50  |                     |        | SIOCFC.SIMMUX & SIOCF5.XCS3MUX      |  |

| 86  |                       | XCS2              |                     | DSRM    |                     | GPIO51  |                     |        | SIOCFC.SIMMUX & SIOCF5.XCS2MUX      |  |

| 87  |                       | XCS1              | Serial              | СТЅМ    |                     | GPIO52  |                     |        | SIOCFC.SIMMUX & SIOCF5.XCS1MUX      |  |

| 88  | Straps                | HFCKS Interface M | DTRM_BOUTM          |         |                     |         |                     |        |                                     |  |

| 89  | Oliupo                | TEST              | -                   | SOUTM   | -                   | GPO55   |                     |        | SIOCFC.SIMMUX                       |  |

| 90  |                       |                   |                     | SINM    |                     | GPIO54  |                     |        |                                     |  |

| 91  | Straps                | XCNF2             |                     | RTSM    |                     | GPO53   |                     |        |                                     |  |

| 97  | Serial<br>Interface 1 | RTS1              | Straps              | TRIS    |                     |         |                     |        |                                     |  |

| 100 | Serial<br>Interface 1 | DTR1_BOUT1        | Straps              | BADDR   | Testability         | XOR_OUT |                     |        | For XOR_OUT selection               |  |

**Table 2. Pin Multiplexing Configuration (Continued)**

| Pin | Functional<br>Block | Signal  | Functional<br>Block | Signal     | Functional<br>Block | Signal | Functional<br>Block | Signal | Configuration<br>Select |

|-----|---------------------|---------|---------------------|------------|---------------------|--------|---------------------|--------|-------------------------|

| 103 |                     | GPIOE15 |                     | DSR2       |                     |        |                     |        |                         |

| 104 |                     | GPIOE14 |                     | SIN2       |                     |        |                     |        | SIGOTO ODIAMILIY        |

| 105 | GPIO                | GPIOE13 | Serial              | RTS2       |                     |        |                     |        | SIOCFC.GP1AMUX          |

| 106 |                     | GPIOE12 | Interface 2         | SOUT2      |                     |        |                     |        |                         |

| 107 |                     | GPIOE11 |                     | CTS2       |                     |        |                     |        | SIOCFC.GP1AMUX          |

| 108 | Straps              | XCNF1   |                     | DTR2_BOUT2 |                     |        |                     |        |                         |

| 109 |                     | GPIOE10 |                     | DCD2       |                     |        |                     |        | SIOCFC.GP1AMUX          |

| 124 |                     | GPIO00  | LPC                 | CLKRUN     |                     |        |                     |        | SIOCF2.CLKRNMUX         |

| 125 |                     | GPIO01  |                     | KBCLK      |                     |        |                     |        |                         |

| 126 |                     | GPIO02  | KBC                 | KBDAT      |                     |        |                     |        | SIGOES NOVES            |

| 127 |                     | GPIO03  |                     | MCLK       |                     |        |                     |        | SIOCF2.NOKBC            |

| 128 |                     | GPIO04  |                     | MDAT       |                     |        |                     |        |                         |

#### 1.4 DETAILED SIGNAL/PIN DESCRIPTIONS

This section describes all PC87427 signals.

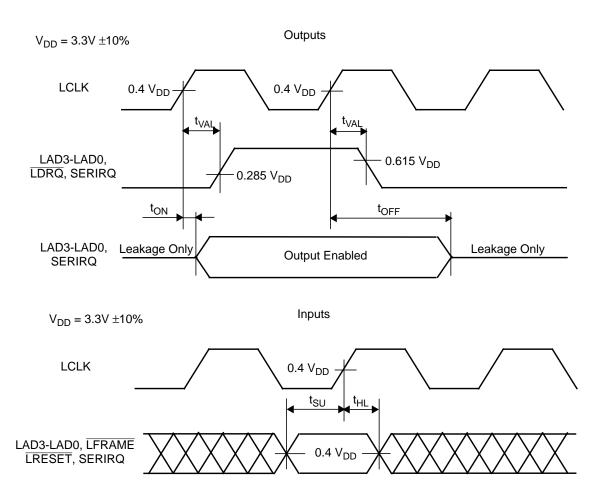

#### 1.4.1 LPC Interface

| Signal              | Pin(s)  | I/O | Buffer Type                          | Power Well      | Description                                                                                                                                  |

|---------------------|---------|-----|--------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| LAD3-0 <sup>1</sup> | 110-113 | I/O | IN <sub>PCI</sub> /O <sub>PCI</sub>  | V <sub>DD</sub> | LPC Address-Data. Multiplexed command, address bidirectional data, and cycle status.                                                         |

| LCLK <sup>1</sup>   | 114     | ı   | IN <sub>PCI</sub>                    | V <sub>DD</sub> | LPC Clock. Derived from the PCI clock (up to 33 MHz).                                                                                        |

| LFRAME <sup>1</sup> | 117     | I   | IN <sub>PCI</sub>                    | V <sub>DD</sub> | <b>LPC Frame.</b> Low pulse indicates the beginning of a new LPC cycle or termination of a broken cycle.                                     |

| LDRQ <sup>1</sup>   | 118     | 0   | O <sub>PCI</sub>                     | V <sub>DD</sub> | LPC DMA Request. Encoded DMA request for LPC Interface.                                                                                      |

| LRESET <sup>1</sup> | 120     | I   | IN <sub>PCI</sub>                    | V <sub>DD</sub> | LPC Reset. Derived from the PCI system reset.                                                                                                |

| SERIRQ <sup>1</sup> | 119     | I/O | IN <sub>PCI</sub> /O <sub>PCI</sub>  | V <sub>DD</sub> | <b>Serial IRQ.</b> The interrupt requests are serialized over a single pin, where each IRQ level is delivered during a designated time slot. |

| CLKRUN <sup>1</sup> | 124     | I/O | IN <sub>PCI</sub> /OD <sub>PCI</sub> | V <sub>DD</sub> | Clock Run. Indicates that LCLK is going to be stopped and requests full-speed LCLK (same behavior as PCI CLKRUN).                            |

<sup>1.</sup> This pin is neither 5-Volt tolerant nor back-drive protected.

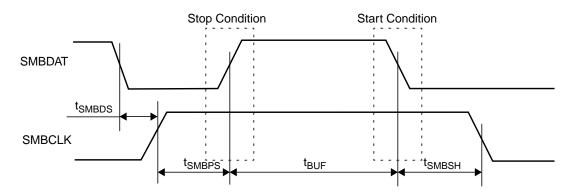

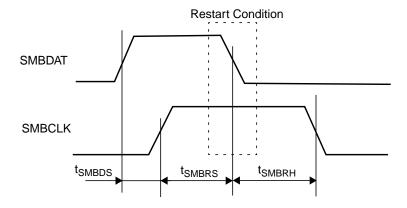

### 1.4.2 SMBus (SMB) Interface

| Signal   | Pin(s) | I/O | Buffer Type                       | Power Well      | Description                                                                            |

|----------|--------|-----|-----------------------------------|-----------------|----------------------------------------------------------------------------------------|

| SMBCLK   | 47     | I/O | IN <sub>SM</sub> /OD <sub>6</sub> | $V_{SB}$        | SMBus Clock. An internal pull-up for this pin is optional.                             |

| SMBDAT   | 46     | I/O | IN <sub>SM</sub> /OD <sub>6</sub> | $V_{SB}$        | SMBus Serial Data. An internal pull-up for this pin is optional.                       |

| SMBALERT | 35     | 0   | OD <sub>6</sub>                   | V <sub>SB</sub> | <b>SMBus Alert.</b> SMBus Interrupt line. An internal pull-up for this pin is optional |

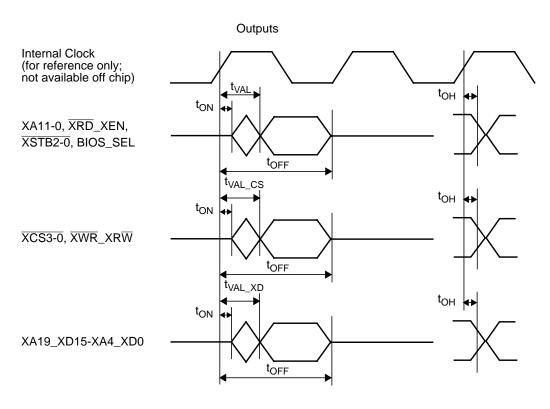

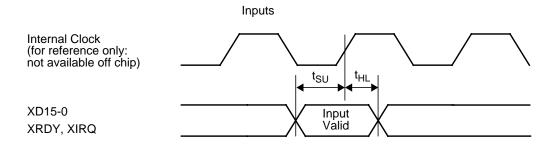

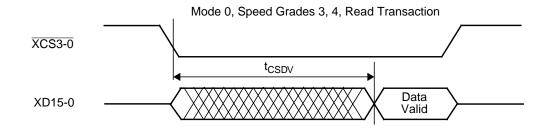

## 1.4.3 X-Bus Extension

| Signal                                         | Pin(s)                                                   | I/O | Buffer Type                        | Power Well      | Description                                                                                                                                                                                                                    |

|------------------------------------------------|----------------------------------------------------------|-----|------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XRD_XEN                                        | 14                                                       | 0   | O <sub>6/12</sub>                  | V <sub>SB</sub> | Read. Active (low) level indicates a read cycle on the X-Bus.  Enable. Active (high) level indicates valid data on the X-Bus.                                                                                                  |

| XWR_XRW                                        | 15                                                       | 0   | O <sub>14/14</sub>                 | $V_{SB}$        | Write. Active (low) level indicates a write cycle on the X-Bus.  Read/Write. A high level indicates a read cycle on the X-Bus; a low level indicates a write cycle on the X-Bus.                                               |

| XA19_XD15<br>-XA12_XD8<br>XA11_XD7<br>-XA4_XD0 | 1-8,                                                     | I/O | IN <sub>TS</sub> /O <sub>4/8</sub> | V <sub>SB</sub> | <b>Multiplexed Data/Address Bus Lines.</b> The XA11-4 address lines are multiplexed with the 8-bit data lines XD7-XD0. If the 16-bit data bus is selected, the XA19-12 address lines are multiplexed with data lines XD15-XD8. |

| XA11-1,<br>XA0_XA20                            | 83, 82,<br>55, 50,<br>48, 37,<br>21, 22,<br>16-18,<br>19 | 0   | O <sub>3/6</sub>                   | V <sub>SB</sub> | Non-Multiplexed Address Bus Lines. The XA0 address line pin is the XA20 address line for XCSn configured to 16-bit data bus.                                                                                                   |

| XSTB2-0                                        | 53,<br>33-34                                             | 0   | O <sub>3/6</sub>                   | V <sub>SB</sub> | Address Strobes. Controls the strobe of up to three external latches for the multiplexed address lines.                                                                                                                        |

| XCS3-0                                         | 85-87,<br>23                                             | 0   | O <sub>14/14</sub>                 | $V_{SB}$        | <b>Chip Selects.</b> Controls the selection of up to four devices residing on the X-Bus.                                                                                                                                       |

| XRDY                                           | 9                                                        | I   | IN <sub>TS</sub>                   | V <sub>SB</sub> | I/O Ready. Instructs the PC87427 to extend the access cycle.                                                                                                                                                                   |

| XIRQ2-0                                        | 36-35,<br>10                                             | I   | IN <sub>TS</sub>                   | V <sub>SB</sub> | <b>X-Bus Interrupt.</b> Converted into serial interrupt by the Interrupt Serializer. The system configuration includes the interrupt number associated with this signal.                                                       |

| BIOS_SEL                                       | 52                                                       | 0   | O <sub>3/6</sub>                   | $V_{SB}$        | BIOS Select. BIOS image selections.                                                                                                                                                                                            |

## 1.4.4 Serial Port Interfaces (SI1, SI2 and SIM)

| Signal       | Pin(s)    | I/O            | Buffer Type        | Power Well      | Description                                                        |

|--------------|-----------|----------------|--------------------|-----------------|--------------------------------------------------------------------|

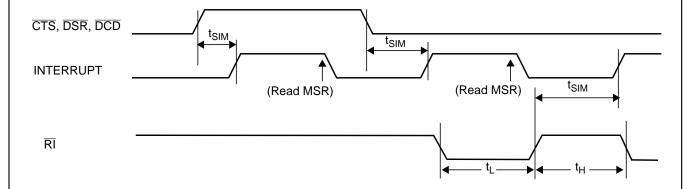

| CTS1         | 99        | I              | IN <sub>TS</sub>   | $V_{DD}$        | Clear to Send. When low, indicates that the modem or other data    |

| CTS2<br>CTSM | 107<br>87 |                |                    | V <sub>SB</sub> | transfer device is ready to exchange data.                         |

| DCD1         | 94        | I              | IN <sub>TS</sub>   | V <sub>DD</sub> | Data Carrier Detected. When low, indicates that the data transfer  |

| DCD2         | 109       |                |                    | V <sub>SB</sub> | device, e.g., modem, has detected the data carrier.                |

| DCDM         | 85        | O <sup>1</sup> | O <sub>14/14</sub> | V <sub>SB</sub> |                                                                    |

| DSR1         | 95        | I              | IN <sub>TS</sub>   | V <sub>DD</sub> | Data Set Ready. When low, indicates that the data transfer device, |

| DSR2<br>DSRM | 103<br>86 |                |                    | V <sub>SB</sub> | e.g., modem, is ready to establish a communications link.          |

| Signal         | Pin(s)    | I/O | Buffer Type      | Power Well                                                                                            | Description                                                                                                                                                                                                                                              |

|----------------|-----------|-----|------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTR1_<br>BOUT1 | 100       | 0   | O <sub>4/8</sub> | V <sub>DD</sub>                                                                                       | Data Terminal Ready. When low, indicates to the data transfer device, e.g., modem, that the UART is ready to establish a communications link. After a system reset, these pins provide the DTR function and set these signals to inactive high. Loopback |

| DTR2_          | 108       |     |                  | V <sub>SB</sub>                                                                                       | operation holds them inactive.                                                                                                                                                                                                                           |

| DTRM_<br>BOUTM | 88        |     |                  |                                                                                                       | <b>Baud Output.</b> Provides the associated serial channel baud rate generator output signal if Test mode is selected, i.e., bit 7 of EXCR1 register is set.                                                                                             |

| RI1            | 101       | ı   | IN <sub>TS</sub> | V <sub>DD</sub>                                                                                       | Ring Indicator. When low, indicates that a telephone ring signal                                                                                                                                                                                         |

| RI2            | 102       |     |                  | V <sub>SB</sub> was received by the modern. These pins are mor power-off for wake-up event detection. | was received by the modem. These pins are monitored during $V_{DD}$ power-off for wake-up event detection.                                                                                                                                               |

| RTS1           | 97        | 0   | O <sub>3/6</sub> | V <sub>DD</sub>                                                                                       | Request to Send. When low, indicates to the modem or other                                                                                                                                                                                               |

| RTS2<br>RTSM   | 105<br>91 |     |                  | V <sub>SB</sub>                                                                                       | data transfer device that the corresponding UART is ready to exchange data. A system reset sets these signals to inactive high, and loopback operation holds them inactive.                                                                              |

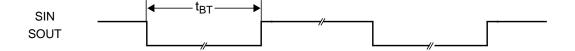

| SIN1           | 96        | ı   | IN <sub>TS</sub> | V <sub>DD</sub>                                                                                       | Serial Input. Receives composite serial data from the                                                                                                                                                                                                    |

| SIN2<br>SINM   | 104<br>90 |     |                  | V <sub>SB</sub>                                                                                       | communications link (peripheral device, modem or other data transfer device).                                                                                                                                                                            |

| SOUT1          | 98        | 0   | O <sub>3/6</sub> | V <sub>DD</sub>                                                                                       | Serial Output. Sends composite serial data to the communications                                                                                                                                                                                         |

| SOUT2<br>SOUTM | 106<br>89 |     |                  | V <sub>SB</sub>                                                                                       | link (peripheral device, modem or other data transfer device). These signals are set active high after a system reset.                                                                                                                                   |

<sup>1.</sup>  $\overline{DCDM}$  is an output signal due to its role in an exchange connection with an external BMC.

## 1.4.5 Fan Monitor & Control (FMC)

| Signal   | Pin(s)                                 | I/O | Buffer Type                         | Power Well      | Description                                                                               |

|----------|----------------------------------------|-----|-------------------------------------|-----------------|-------------------------------------------------------------------------------------------|

| FANINO-7 | 66, 81,<br>77, 76,<br>75, 83,<br>36, 9 | I   | IN <sub>TS</sub>                    | V <sub>DD</sub> | Fan Inputs. Used to feed the fan's tachometer pulse to the Fan Speed Monitor.             |

| FANOUT0  | 78                                     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> |                 | Fan Outputs. Pulse Width Modulation (PWM) signals, used to                                |

| FANOUT1  | 7                                      |     |                                     |                 | control the speed of cooling fans by controlling the voltage supplied to the fans motors. |

|          | 53                                     |     |                                     |                 |                                                                                           |

| FANOUT2  | 8                                      |     |                                     |                 |                                                                                           |

|          | 33                                     |     |                                     |                 |                                                                                           |

| FANOUT3  | 67                                     |     |                                     |                 |                                                                                           |

## 1.4.6 Health Monitoring & Control (HMC)

| Signal      | Pin(s) | 1/0 | Buffer Type                       | Power Well      | Description                                                                                                                                            |

|-------------|--------|-----|-----------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| LMPCIF      | 82     | I/O | IN <sub>SM</sub> /OD <sub>6</sub> | V <sub>SB</sub> | LMPC Sensor Interface. Bidirectional, SensortPath proprietary interface signal to LMPC sensor device(s). An internal pull-up for this pin is optional. |

| THRMTRIP1-2 | 21, 22 | I   | IN <sub>TS</sub>                  | V <sub>DD</sub> | <b>Thermal Trip Inputs.</b> Indicates that a thermal trip from a CPU occurred.                                                                         |

| VRMTHRM     | 83     | I   | IN <sub>TS</sub>                  | V <sub>DD</sub> | VRM Thermal Warning. Thermal warning from a VRM of a CPU.                                                                                              |

## 1.4.7 Keyboard and Mouse Controller (KBC)

| Signal   | Pin(s) | I/O | Buffer Type                                           | Power Well      | Description                                                                                                                                                                                     |

|----------|--------|-----|-------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KBCLK    | 125    | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                    | V <sub>DD</sub> | <b>Keyboard Clock.</b> Keyboard clock signal. An external pull-up resistor is required for PS/2 compliance. This pin is monitored during V <sub>DD</sub> power-off for wake-up event detection. |

| KBDAT    | 126    | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                    | V <sub>DD</sub> | <b>Keyboard Data.</b> Keyboard data signal. An external pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD}$ power-off for wake-up event detection.          |

| MCLK     | 127    | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                    | V <sub>DD</sub> | <b>Mouse Clock.</b> Mouse clock signal. An external pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD}$ power-off for wake-up event detection.              |

| MDAT     | 128    | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                    | V <sub>DD</sub> | <b>Mouse Data.</b> Mouse data signal. An external pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD}$ power-off for wake-up event detection.                |

| KBRST    | 122    | I/O | IN <sub>T</sub> /OD <sub>8,</sub><br>O <sub>4/8</sub> | V <sub>DD</sub> | KBD Reset. Keyboard reset (P20) quasi-bidirectional signal.                                                                                                                                     |

| GA20     | 123    | I/O | IN <sub>T</sub> /OD <sub>8,</sub><br>O <sub>4/8</sub> | V <sub>DD</sub> | Gate A20. KBC gate A20 (P21) quasi-bidirectional signal.                                                                                                                                        |

| P12      | 121    | I/O | IN <sub>T</sub> /OD <sub>8,</sub><br>O <sub>4/8</sub> | V <sub>DD</sub> | I/O Port. KBC quasi-bidirectional signal for general-purpose input and output (controlled by KBC firmware).                                                                                     |

| P16, P17 | 75, 66 | I/O | IN <sub>T</sub> /OD <sub>8,</sub><br>O <sub>4/8</sub> | V <sub>DD</sub> | I/O Port. KBC quasi-bidirectional signal for general-purpose input and output (controlled by KBC firmware).                                                                                     |

## 1.4.8 General-Purpose I/O (GPIO)

| Signal                 | Pin(s)               | I/O | Buffer Type                          | Power Well      | Description                                                                                                                                                                                                       |  |

|------------------------|----------------------|-----|--------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPIO00                 | 124                  | I/O | IN <sub>PCI</sub> /O <sub>PCI</sub>  | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIO01-04              | 125-128              | I/O | IN <sub>TS</sub> /O <sub>14/14</sub> | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIO05                 | 82                   | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIO06                 | 10                   | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIO07                 | 13                   | I/O | IN <sub>TS</sub> /O <sub>14/14</sub> | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| 0010540                | 1, 3-6               |     | IN <sub>TS</sub> /O <sub>3/6</sub>   |                 |                                                                                                                                                                                                                   |  |

| GPIOE10,<br>GPIOE12-15 | 109,<br>106-103      | I/O | IN <sub>TS</sub> /O <sub>14/14</sub> | $V_{SB}$        | General-Purpose I/O Ports. Each pin is configured independently as input or I/O with or without static pull-up and with either open-drain or push-pull output type. The GPIOEnn                                   |  |

| GPIOE11                | 2                    | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | V.              | pins have event detection capability.                                                                                                                                                                             |  |

| GPIOETT                | 107                  | 1/0 | IN <sub>TS</sub> /O <sub>3/6</sub>   | $V_{SB}$        |                                                                                                                                                                                                                   |  |

| GPIOE16-17             | 7-8                  | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIO20                 | 14                   | I/O | IN <sub>TS</sub> /O <sub>6/12</sub>  | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIO21                 | 15                   | I/O | IN <sub>TS</sub> /O <sub>14/14</sub> | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIO22-23              | 16-17                | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPO24                  | 18                   | 0   | O <sub>3/6</sub>                     | V <sub>SB</sub> | General-Purpose Output Port.                                                                                                                                                                                      |  |

| GPIO25-27              | 19, 83, 37           | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

|                        | 31,29-25             | I/O | IN <sub>TS</sub> /O <sub>4/8</sub>   | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIO37,35-31           | 71, 73-<br>74, 64-62 | 1/0 | IN <sub>TS</sub> /O <sub>6/12</sub>  | V <sub>DD</sub> |                                                                                                                                                                                                                   |  |

| CDIO26 20              | 30, 24               | 1/0 | IN <sub>TS</sub> /O <sub>4/8</sub>   | $V_{SB}$        |                                                                                                                                                                                                                   |  |

| GPIO36,30              | 72, 61               | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | V <sub>DD</sub> | General-Purpose I/O Ports. Each pin is configured independently as input or I/O with or without static pull-up and                                                                                                |  |

| GPIOE40-44             | 21-22,<br>35, 49, 38 | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | V <sub>SB</sub> | with either open-drain or push-pull output type. The GPIOEnn pins have event detection capability.                                                                                                                |  |

| GPIOE45                | 51                   | I/O | IN <sub>TS</sub> /O <sub>14/14</sub> | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIOE46-47             | 20, 32               | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPIO50-52              | 85-87                | I/O | IN <sub>TS</sub> /O <sub>14/14</sub> | V <sub>SB</sub> |                                                                                                                                                                                                                   |  |

| GPO53                  | 91                   | 0   | O <sub>3/6</sub>                     | V <sub>SB</sub> | General-Purpose Output Port.                                                                                                                                                                                      |  |

| GPIO54                 | 90                   | I/O | IN <sub>TS</sub> /O <sub>3/6</sub>   | $V_{SB}$        | General-Purpose I/O Port. The pin is configured independently as input or I/O with or without static pull-up and with either open-drain or push-pull output type.                                                 |  |

| GPO55                  | 89                   | 0   | O <sub>3/6</sub>                     | V <sub>SB</sub> | General-Purpose Output Port.                                                                                                                                                                                      |  |

| GPIO56-57              | 80-79                | I/O | IN <sub>TS</sub> /O <sub>14/14</sub> | $V_{SB}$        | General-Purpose I/O Ports. Each pin is configured independently as input or I/O with or without static pull-up a with either open-drain or push-pull output type. The GPIOE pins have event detection capability. |  |

| Signal   | Pin(s)          | I/O | Buffer Type                          | Power Well      | Description                            |

|----------|-----------------|-----|--------------------------------------|-----------------|----------------------------------------|

| GPO60-63 | 54,48,<br>45,55 | 0   | O <sub>3/6</sub>                     | V <sub>SB</sub> | General-Purpose Output Ports.          |

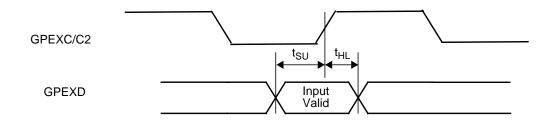

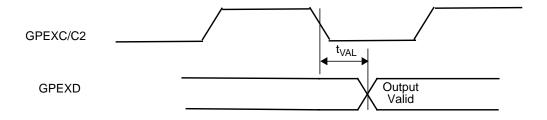

| GPEXD    | 79              | I/O | IN <sub>TS</sub> /O <sub>14/14</sub> | V <sub>SB</sub> | General-Purpose I/O Extension Data.    |

| GPEXC    | 80              | 0   | O <sub>14/14</sub>                   | V <sub>SB</sub> | General-Purpose I/O Extension Clock.   |

| GPEXC2   | 81              | 0   | O <sub>14/14</sub>                   | V <sub>SB</sub> | General-Purpose I/O Extension Clock 2. |

## 1.4.9 Floppy Disk Controller (FDC)

| Signal | Pin(s) | I/O | Buffer Type                         | Power Well      | Description                                                                                                                                                     |  |

|--------|--------|-----|-------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DENSEL | 74     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | V <sub>DD</sub> | <b>Density Select.</b> Indicates that either a high FDC density data rate (500 Kbps, 1 Mbps or 2 Mbps) or a low density data rate (250 or 30 Kbps) is selected. |  |

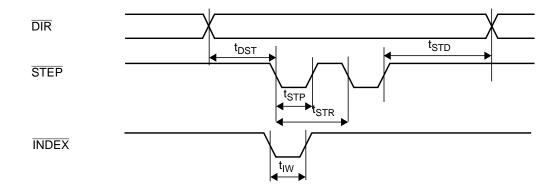

| DIR    | 65     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | V <sub>DD</sub> | <b>Direction.</b> Determines the direction of the Floppy Disk Drive (FDD) head movement (active = step in; inactive = step out) during a seek operation.        |  |

| DR0    | 67     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | $V_{DD}$        | <b>Drive Select.</b> Controlled by bit 0 of the Digital Output Register (DOR).                                                                                  |  |

| DRATE0 | 73     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | V <sub>DD</sub> | <b>Data Rate.</b> Reflects the value of bit 0 of the Configuration Contro Register (CCR) or the Data Rate Select Register (DSR), whicheve was written to last.  |  |

| DSKCHG | 57     | I   | IN <sub>TS</sub>                    | V <sub>DD</sub> | Disk Change. Indicates if the drive door was opened.                                                                                                            |  |

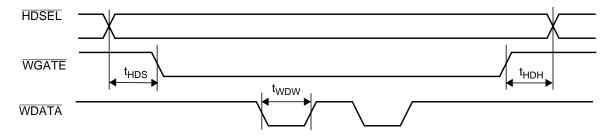

| HDSEL  | 58     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | $V_{DD}$        | <b>Head Select.</b> Determines which side of the FDD is accessed. Active low selects side 1; inactive selects side 0.                                           |  |

| INDEX  | 72     | I   | IN <sub>TS</sub>                    | V <sub>DD</sub> | Index. Indicates the beginning of an FDD track.                                                                                                                 |  |

| MSEN0  | 45     | I   | IN <sub>TS</sub>                    | V <sub>DD</sub> | <b>Automatic Media Sense.</b> Identifies the media type of the floppy disk in drives 1 and 0 (if the drives support this protocol).                             |  |

| MTR0   | 71     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | V <sub>DD</sub> | Motor Select. Motor enable lines for drives 0.                                                                                                                  |  |

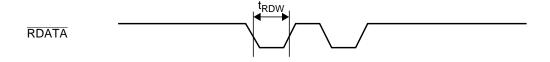

| RDATA  | 59     | ı   | IN <sub>TS</sub>                    | V <sub>DD</sub> | Read Data. Raw serial input data stream read from the FDD.                                                                                                      |  |

| STEP   | 64     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | $V_{DD}$        | <b>Step.</b> Sends pulses to the disk drive at a software programmable rate to move the head during a seek operation.                                           |  |

| TRK0   | 61     | I   | IN <sub>TS</sub>                    | V <sub>DD</sub> | <b>Track 0.</b> Indicates to the controller that the head of the selected floppy disk drive is at track 0.                                                      |  |

| WDATA  | 63     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | V <sub>DD</sub> | Write Data. Carries out the pre-compensated serial data that is written to the FDD. Pre-compensation is software selectable.                                    |  |

| WGATE  | 62     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | V <sub>DD</sub> | Write Gate. Enables the write circuitry of the selected FDD.                                                                                                    |  |

| WP     | 60     | I   | IN <sub>TS</sub>                    | V <sub>DD</sub> | Write Protected. Indicates that the disk in the selected drive is write protected.                                                                              |  |

## 1.4.10 System Wake-Up Control (SWC)

| Signal          | Pin(s)                              | I/O | Buffer Type        | Power Well                   | Description                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------|-------------------------------------|-----|--------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GPIOE17-16      | 8-7                                 |     |                    |                              |                                                                                                                                                                                                                                                                                                                           |  |  |

| GPIOE15-10      | 103-107,<br>109                     | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              | Wake-up Inputs. Generate a wake-up event or an interrup                                                                                                                                                                                                                                                                   |  |  |

| GPIOE11-10      | 2-1                                 | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              | These pins have programmable debounce protection.                                                                                                                                                                                                                                                                         |  |  |

| GPIOE40-47      | 21-22, 35,<br>49, 38,<br>51, 20, 32 | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              |                                                                                                                                                                                                                                                                                                                           |  |  |

| RI1<br>RI2      | 101<br>102                          | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              | Ring Indicator Wake-up. When low, generates a wake-up event or an interrupt, indicating that a telephone ring signal was received by the modem. When RI functionality is not required, an internal pull-up resistor allows this pin to be left floating.                                                                  |  |  |

| KBCLK           | 125                                 | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              | Keyboard Clock Wake-up. Generates a wake-up event or an interrupt, indicating a change in the keyboard clock signal.                                                                                                                                                                                                      |  |  |

| KBDAT           | 126                                 | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              | <b>Keyboard Data Wake-up.</b> Generates a wake-up event or an interrupt, indicating a change in the keyboard data signal.                                                                                                                                                                                                 |  |  |

| MCLK            | 127                                 | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              | Mouse Clock Wake-up. Generates a wake-up event or an interrupt, indicating a change in the mouse clock signal.                                                                                                                                                                                                            |  |  |

| MDAT            | 128                                 | 1   | IN <sub>TS</sub>   | V <sub>SB</sub>              | Mouse Data Wake-up. Generates a wake-up event or an interrupt, indicating a change in the mouse data signal.                                                                                                                                                                                                              |  |  |

| PWBTIN          | 36                                  | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              | Power Button In. Active (low) level indicates a user reque to turn the power on or off. This pin has debounce protecti                                                                                                                                                                                                    |  |  |

| PWBTOUT         | 49                                  | 0   | OD <sub>6</sub>    | V <sub>SB</sub>              | Power Button Out. Output for the chip-set Power Button inp                                                                                                                                                                                                                                                                |  |  |

| SLBTIN          | 35                                  | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              | Sleep Button In. Active (low) level indicates a user request to enter or exit Sleep mode. This pin has debounce protection.                                                                                                                                                                                               |  |  |

| SLPS3,<br>SLPS5 | 20<br>32                            | I   | IN <sub>TS</sub>   | V <sub>SB</sub>              | Sleep State 3 to 5. Active (low) level indicates the system is in one of the sleep states S3, S4 or S5. These signals are generated by an external ACPI controller.  Pins SLPS3 SLPS5 Functionality  1 1 Working state (S0) or sleep states S1 or S2 0 1 Sleep state S3 0 0 Sleep states S4 or S5 1 0 Illegal combination |  |  |

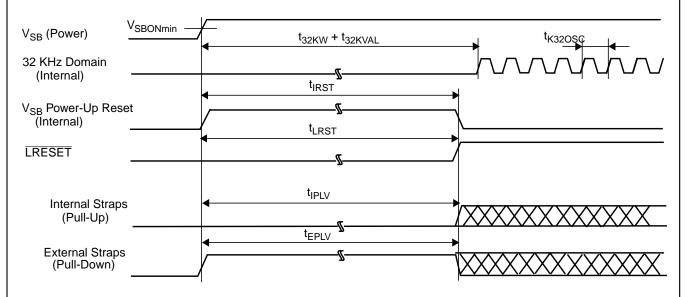

| SIOSCI          | 38                                  | 0   | OD <sub>6</sub>    | V <sub>SB</sub>              | System Control Interrupt. Active (low) level indicates that a wake-up event occurred, causing the system to exit its current sleep state.                                                                                                                                                                                 |  |  |