# **PRELIMINARY**

March 2004 Revision 1.07

# PC87591E, PC87591S and PC87591L LPC Mobile Embedded Controllers

# **General Description**

The National Semiconductor PC87591E, PC87591S and PC87591L are highly integrated, embedded controllers with an embedded-RISC core and integrated advanced functions. These devices are targeted for a wide range of portable applications that use the Low Pin Count (LPC) interface.

The PC87591S is targeted for security applications and includes supporting hardware such as the Hardware Random Number Generator. The PC8591L replaces the on-chip flash with 4K of boot ROM for value solutions using shared BIOS architecture. "PC87591x" refers to all the devices.

The PC87591x incorporates National's CompactRISC<sup>™</sup> CR16B core (a high-performance 16-bit RISC processor), on-chip flash (ROM for the PC87591L) and RAM memories, system support functions and a Bus Interface Unit (BIU) that directly interfaces with optional external memory (such as flash) and I/O devices.

System support functions include: WATCHDOG and other timers, interrupt control, general-purpose I/O (GPIO) with internal keyboard matrix scanning,  $PS/2^{\otimes}$  Interface, ACCESS.bus $^{\otimes}$  interface, high accuracy analog-to-digital (ADC) and digital-to-analog converters (DAC) for battery charging, system control, system health monitoring and analog controls.

The PC87591x interfaces with the host via an LPC interface that provides the host with access to the Keyboard and embedded controller interface channels, integrated functions, Real-Time Clock (RTC), BIOS firmware and security functions.

Like members of National's SuperI/O family, the PC87591x is PC01 and ACPI compliant.

# **Outstanding Features**

- Host interface, based on Intel's LPC Interface Specification Revision 1.0, September 29th, 1997

- PC01 Rev 1.0, and ACPI 2.0 compliant

- 16-bit RISC core, with 2 Mbyte address space, and running at up to 20 MHz

- Software and Hardware controlled clock throttling

- Shared BIOS flash memory (internal and/or external)

- Y2K-compliant RTC

- 84/117 GPIO ports (for 128-pin/176-pin packages) with a variety of wake-up events

- Extremely low current consumption in Idle mode

- JTAG-based debugger interface

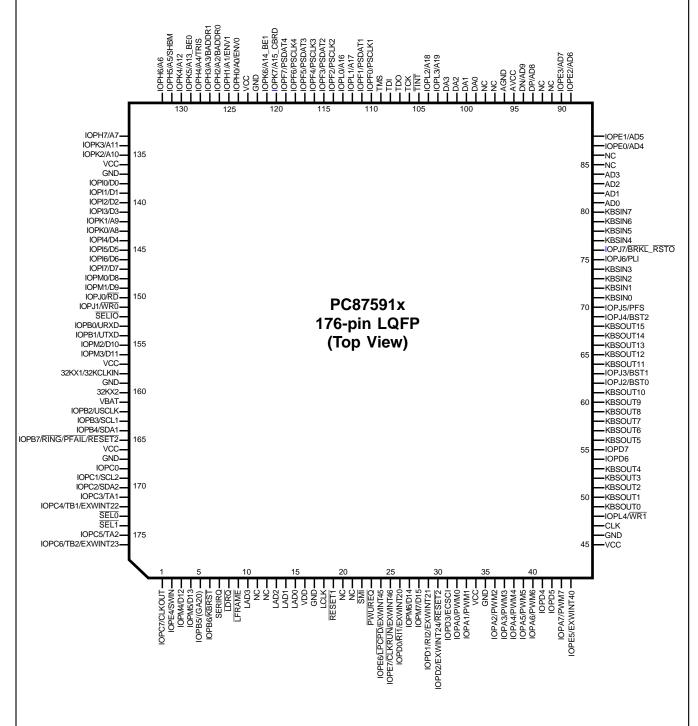

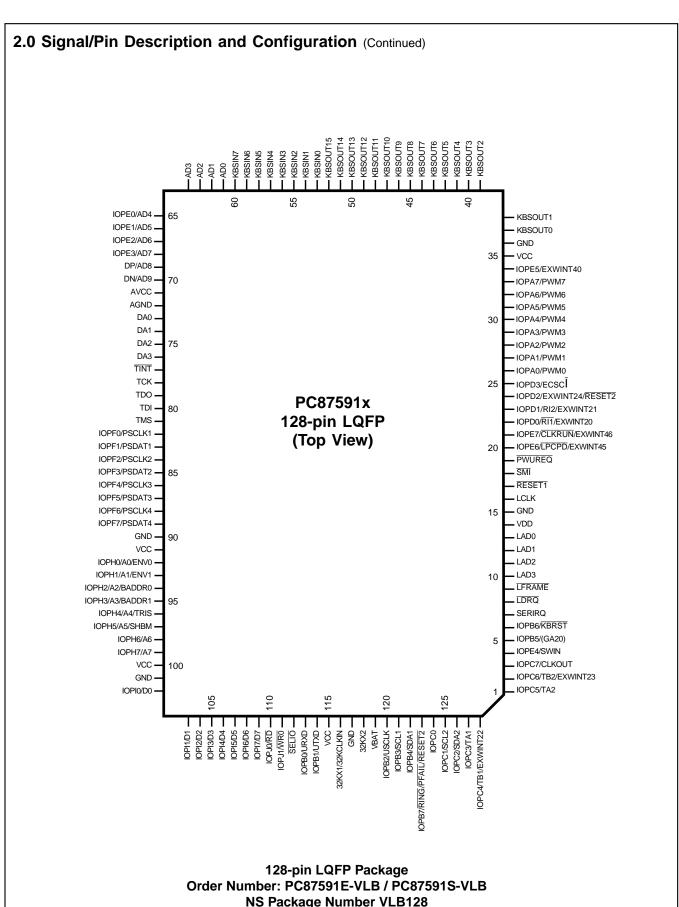

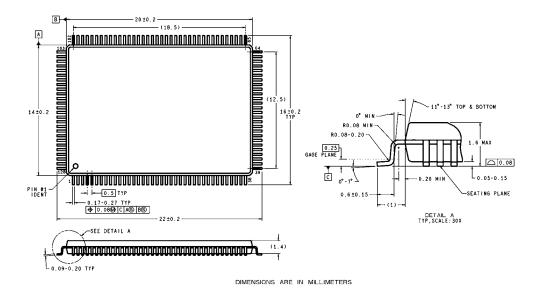

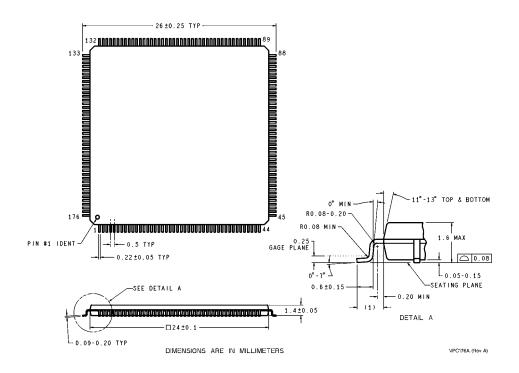

- 128-pin and 176-pin options, in LQFP package (PC87591L is 176-pin only)

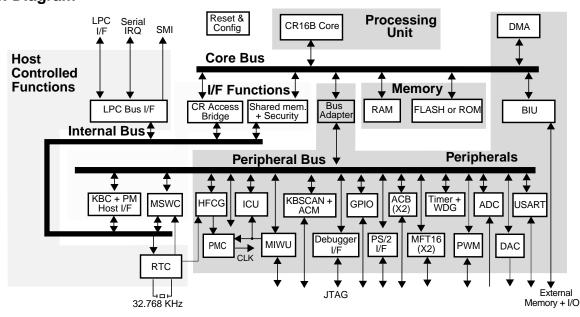

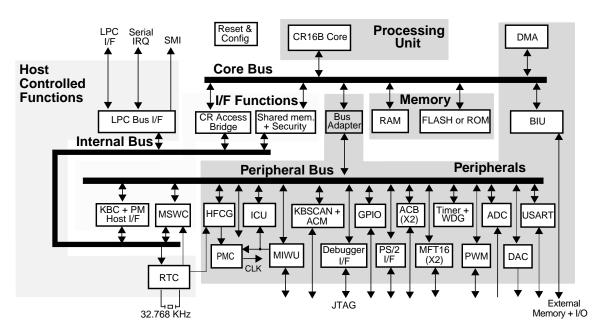

# **Block Diagram**

National Semiconductor is a registered trademark of National Semiconductor Corporation. All other brand or product names are trademarks or registered trademarks of their respective holders

# Features (Continued)

# **Device-Specific Information**

The following table compares features for the devices in the PC87591x family. The features listed below are a superset of the PC87591x family.

| Function                                  | PC87591E<br>128-Pin | PC87591E<br>176-Pin | PC87591S<br>128-Pin | PC87591S<br>176-Pin | PC87591L<br>176-Pin |

|-------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| Flash Size                                | 64K                 | 64K                 | 128K                | 128K                | _                   |

| ROM Size                                  | -                   | _                   | _                   | _                   | 4K                  |

| RAM Size                                  | 2K                  | 2K                  | 4K                  | 4K                  | 2K                  |

| General-Purpose Input/Output Ports (GPIO) | 62                  | 93                  | 62                  | 93                  | 93                  |

| Shared BIOS                               | NO                  | YES                 | NO                  | YES                 | YES                 |

| RNG                                       | NO                  | NO                  | YES                 | YES                 | NO                  |

| Memory Protection                         | NO                  | NO                  | YES                 | YES                 | YES                 |

#### **Features**

- Processing Unit

- CompactRISC CR16B 16-bit embedded RISC processor core (the "core")

- 2 Mbyte address space

- Internal Memory

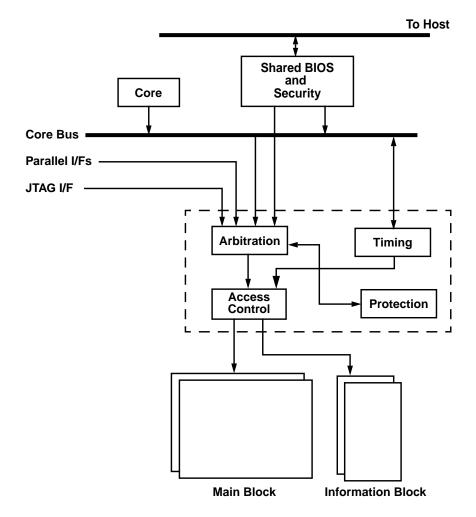

- Up to 128 Kbytes of on-chip flash memory (4 Kbytes of ROM in the PC87591L)

- Supports BIOS (flash) memory sharing with PC host

- On-chip flash is field upgradable by host, CR16B, parallel interface or JTAG

- Boot blocks for both CR16B and Host Code

- Memory contents protection and security

- Hardware-protected boot zone with block protection circuit

- 2K (PC87591E/L) or 4K of on-chip RAM (PC87591S)

- All memory types can hold both code and data

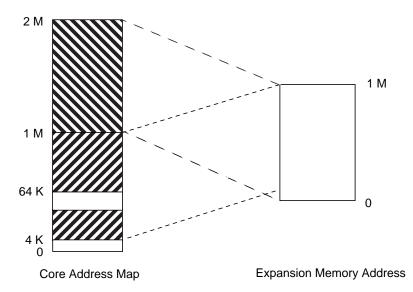

- Expansion Memory (Optional in 176-pin package)

- Up to 1 Mbyte of additional code and data

- Supports BIOS (flash) memory sharing with PC host

- Supports external memory power-down mode

- Field upgradable with flash or SRAM devices

- Supports host-controlled code download and update

- Bus Interface Unit (BIU)

- □ Three address zones for static devices (SRAM, ROM, flash, I/O)

- ☐ Configurable wait states and fast-read, single-cycle bus cycles

- 8- or 16-bit wide bus

# ■ LPC System Interface

- Synchronous cycles, up to 33 MHz bus clock

- Serial IRQ

- I/O and Memory read and write cycles

- Bootable memory support

- Bus Master read and write cycles

- Reset input

- Base Address (BADDR) strap to determine the base address of the Index-Data register pair

- LPCPD and CLKRUN support

- FWH Transaction support

#### ■ Security Function Support

- Random Number Generator (RNG)

- Full Random using temperature, voltage and system noise.

- Memory access protection

# **Embedded Controller System Features**

- Host Bus Interface (HBI)

- Three host interface channels, typically used for the KBC, ACPI Private or Shared EC channels

- 8042 KBC standard Interface (legacy 60<sub>16</sub>, 64<sub>16</sub>)

- Intel 80C51SL compatible

- IRQ1 and IRQ12 support

- Fast Gate A20 and Fast Host Reset via firmware

- PM interface port (legacy 62<sub>16</sub>, 66<sub>16</sub>)

- ACPI Embedded Controller with either Shared or Private interface

- IRQ, SMI or SCI generation

# Features (Continued)

- Interrupt Control Unit (ICU)

- 31 maskable vectored interrupts (of which 26 are external)

- General-purpose external interrupt inputs through MIWU

- Enable and pending indication for each interrupt

- Non-maskable interrupt input

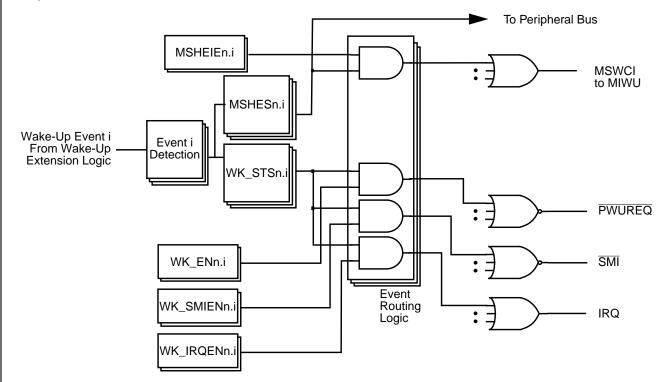

- Multi-Input Wake-Up (MIWU)

- Supports up to 32 wake-up or interrupt inputs

- Generates wake-up event to PMC (Power Management Controller)

- Generates interrupts to ICU

- Provides user-selectable trigger conditions

- General-Purpose I/O (GPIO)

- 84/117 port pins in 128-pin/176-pin package, respectively.

- I/O pins individually configured as input or output

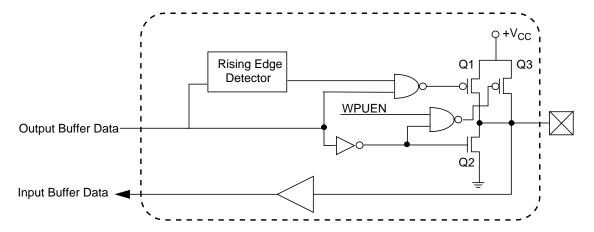

- Configurable internal pull-up resistors

- Special ports for internal keyboard matrix scanning

- □ 16 open-collector outputs

- ☐ Eight Schmitt inputs with internal pull-ups

- Input for system On/Off switch

- 27 external wake-up events

- Low-cost external GPIO expansion through the BIU I/O Expansion protocol

- PS/2 Interface

- Supports four external ports: Keyboard, mouse and two additional pointing devices

- Supports byte-level handling via hardware accelerator

- Two ACCESS.bus (ACB) Interface modules. Each is:

- Intel SMBus<sup>®</sup> and Philips I<sup>2</sup>C<sup>®</sup> compatible

- ACCESS.bus master and slave

- Up to three simultaneous slave addresses detected

- Supports polling and interrupt controlled operation

- Generates a wake-up signal on detection of a Start Condition while in Idle mode

- Optional internal pull-up on SDA and SCL pins

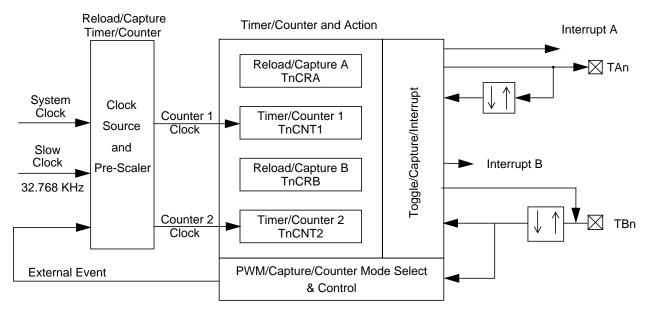

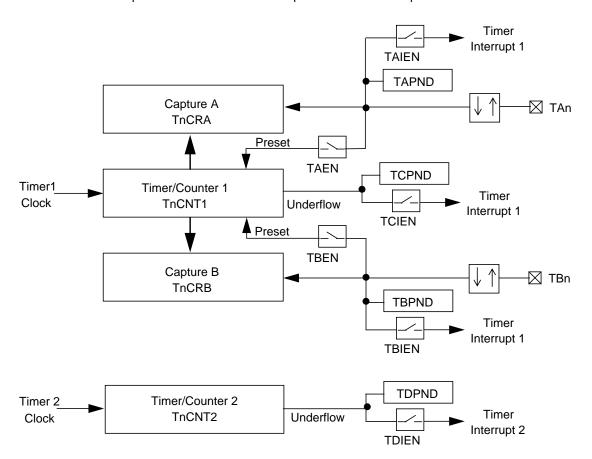

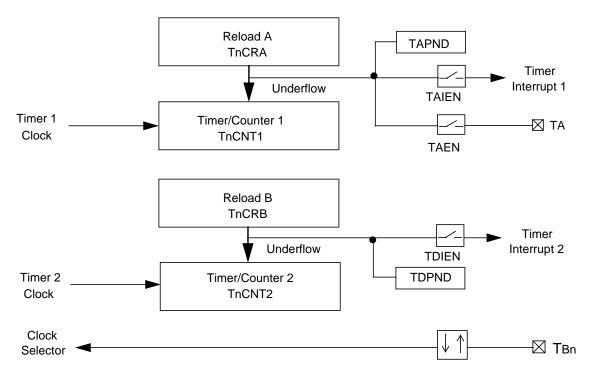

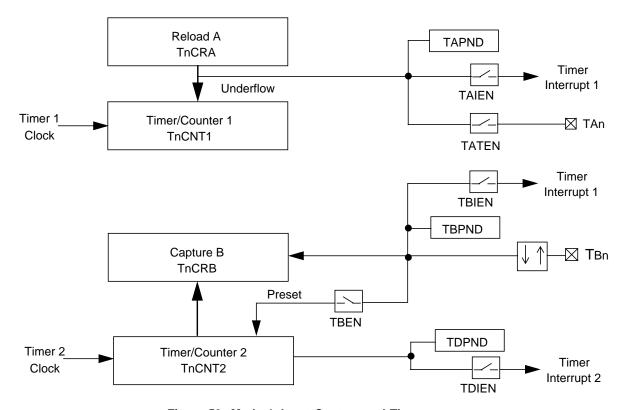

- Two 16-bit Multi Function Timer (MFT16) modules. Each module:

- Contains two 16-bit timers

- Supports Pulse Width Modulation (PWM), Capture and Counter

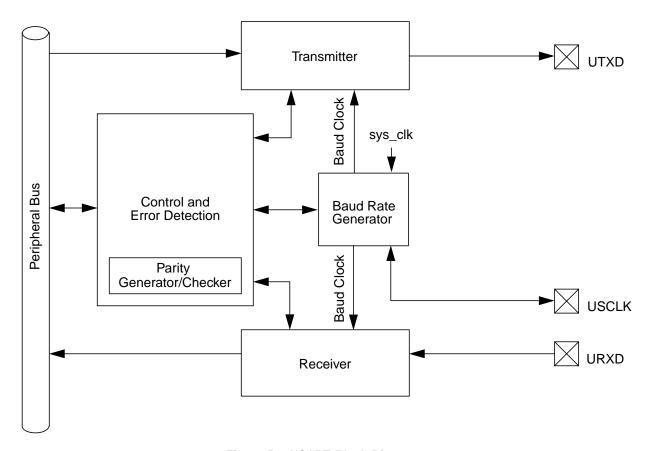

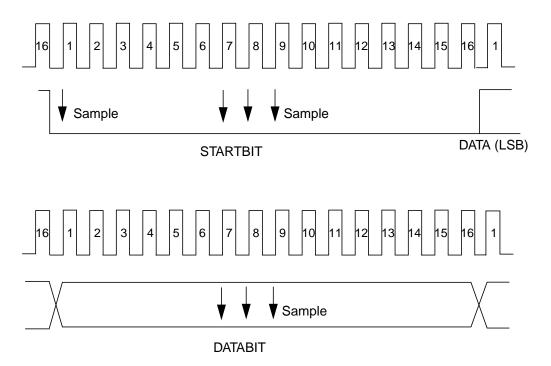

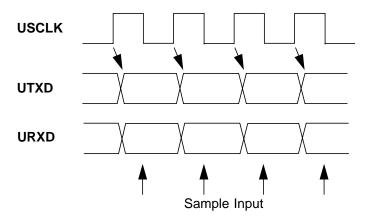

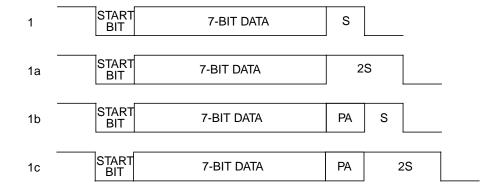

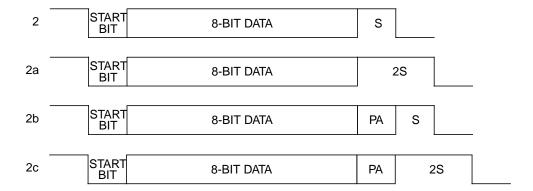

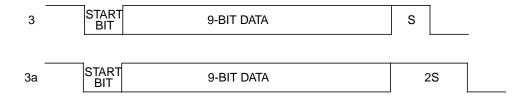

- Universal Synchronous/ Asynchronous Receiver-transmitter (USART)

- A full-duplex USART channel

- Programmable baud rate

- Data transfer via interrupt or polling

- Synchronous mode with either internal or external clock

- 7-, 8- or 9-bit protocols.

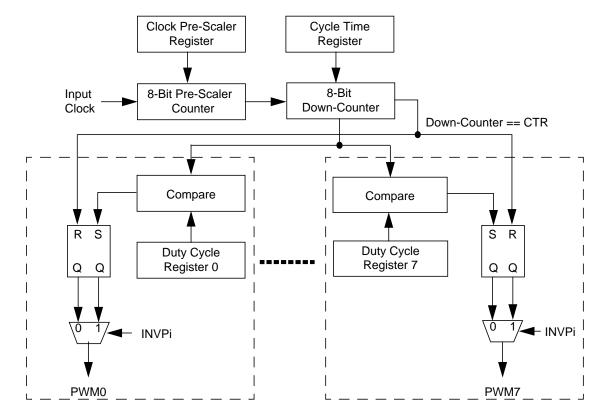

- Pulse Width Modulation (PWM) Module

- Eight outputs

- 8-bit duty cycle resolution

- Common input clock prescaler

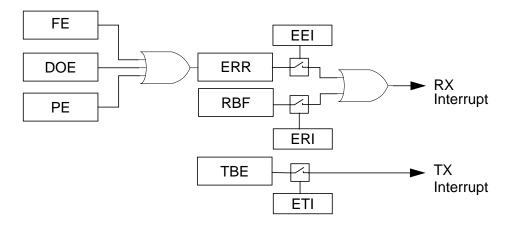

- Timer and WATCHDOG (TWM)

- 16-bit periodic interrupt timer with 30 µs resolution and 5-bit prescaler for system tick and periodic wake-up tasks

- 8-bit WATCHDOG timer

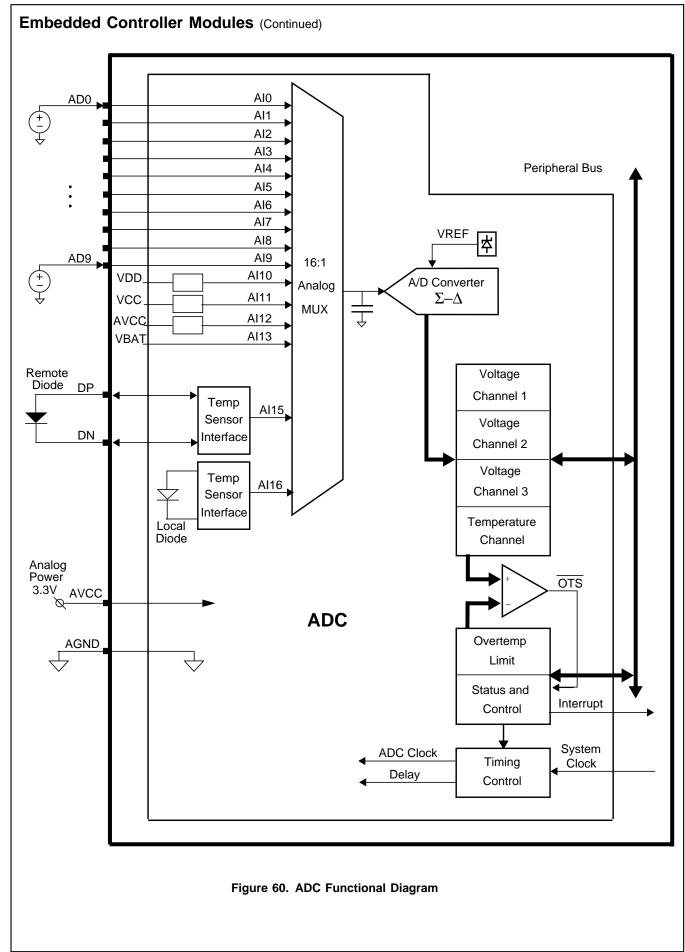

- Analog to Digital Converter (ADC)

- Fourteen channels, with 10-bit resolution

- Sigma-delta technology for high noise rejection

- Three voltage measurements and one temperature measurement every 100 ms

- Internal voltage reference

- Hardware Monitoring

- Controlled by embedded controller

- System Voltage Measurement

- Up to eight external measurement points

- □ Four internal measurement points

- Smart power failure detection

- Diode-Based Temperature Measurement

- □ Software-controlled fault detection

- ☐ Hardware-monitored over-temperature detection

- Production time calibration using flash parameters

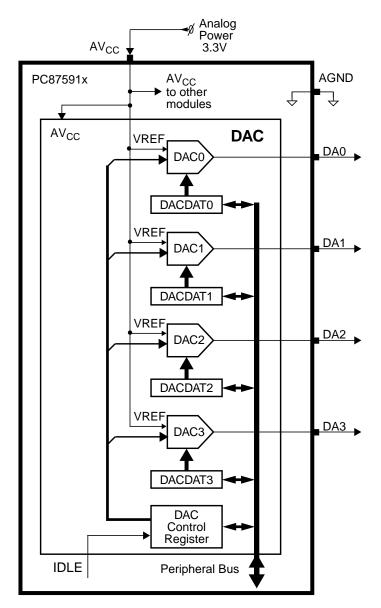

- Digital to Analog Converter (DAC)

- Four channels, 8-bit resolution

- 1 μs conversion time for 50 pF load

- Full output range from AGND to AVCC

- Analog Comparators Monitor (ACM)

- Eight comparator inputs on KBD scan inputs

- 6-bit input measurement resolution

- Scan and Threshold modes

- Supports low-current system wake-up

- Development Support Features

- Interface to debugger via JTAG pins

- □ ISE/ADB mode

- On-board Debug mode

- Flash programing via JTAG

- CR16B Access to Host Controlled Functions

- Enabled when host inactive

# **Host Controlled Functions Features**

- Supports Microsoft® Advanced Power Management (APM) Specifications Revision 1.2, February 1996

- Generates the System Management Interrupt (SMI)

- PC1 and ACPI Compliant

- PnP Configuration Register structure

- Flexible resource allocation for all logical devices

- Relocatable base address

# Features (Continued)

- □ 15 IRQ routing options

- Legacy free support

- Real-Time Clock (RTC)

- DS1287 and MC146818 compatible

- 242-byte battery backed-up CMOS RAM

- Calendar including century and automatic leap-year adjustment (Y2K compliant)

- Optional adjustment for daylight saving time

- BCD or binary format for timekeeping

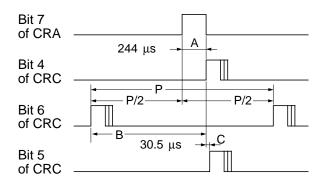

- Three individually maskable interrupt event flags: periodic rates from 122 μs to 500 ms; time-of-day alarm, once-per-second to once-per-day

- Double-buffer time registers

- Alarm wake-up

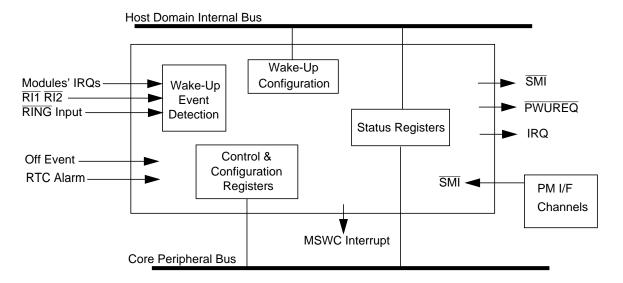

- Mobile System Wake-Up Control (MSWC)

- Wake-up on detection of RI1, RI2, RING activity

- External modem ring on serial port

- ☐ Ring pulse or pulse train on RING input signal

- □ Software-controlled off events

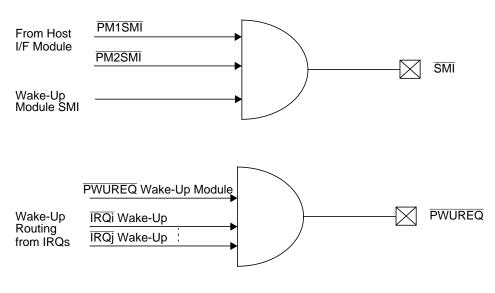

- Optional routing of power-up request on IRQ and/or SMI lines

### Clocking, Supply and Package Information

- Strap Input Controlled Operating Modes

- Turn on shared BIOS

- TRI-STATE

- Development

- On-board development

- Programing environment

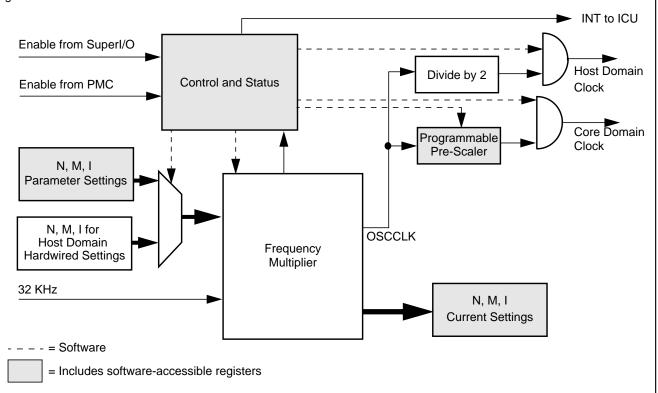

#### ■ Clocks

- Single 32.768 KHz crystal oscillator

- LPC clock, up to 33 MHz

- On-chip high frequency clock generator

- □ CPU clock 4-20 MHz

- Software-controlled frequency generation

- □ Multiplier source 32 KHz input

- 32 KHz clock out

- CR16B clock out

#### ■ Power Supply

- 3.3V supply operation

- 5V tolerance and back-drive protection on all pins (except LPC bus pins and keyboard scan inputs)

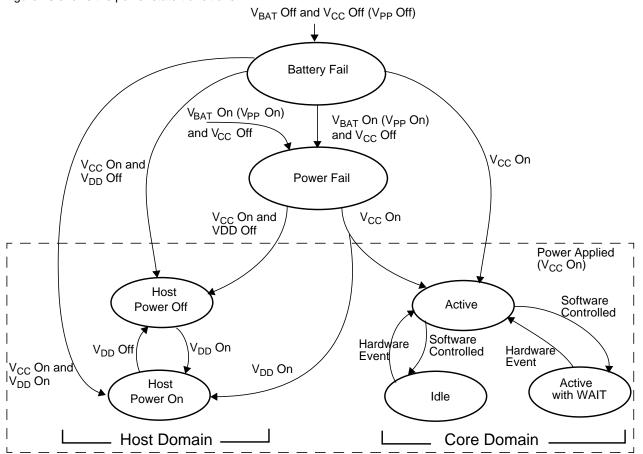

- Separate supply for Host I/F (V<sub>DD</sub>) and Embedded Controller functions (V<sub>CC</sub>)

- Backup battery input for RTC, and wake-up configuration.

- Reduced power consumption capability

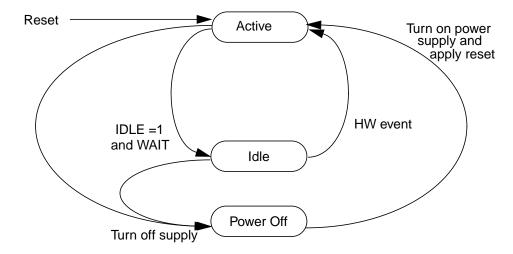

- Four power modes, switched by software or hardware

- ☐ Active mode current (TBD mA)

- □ Active mode executing WAIT

- □ Idle (15 μA)

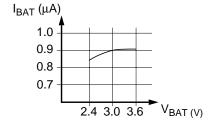

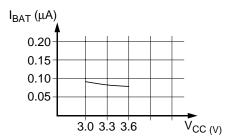

- Power off for RTC only (0.9 μA typical) from backup battery

- Automatic wake-up on system events

- Package Options

- 128-pin LQFP package

- 176-pin LQFP package for more GPIO pins, Expansion Memory use and development systems

# **Revision Record**

| Revision Date   | Status | Comments                                                            |

|-----------------|--------|---------------------------------------------------------------------|

| April 11, 00    | 0.13   | External version of Architectural Specification                     |

| December 25, 00 | 1.0    | Preliminary                                                         |

| May 1, 01       | 1.02   | Preliminary                                                         |

| May 8, 01       | 1.03   | Preliminary                                                         |

| July 19, 01     | 1.04   | Preliminary                                                         |

| October 28, 01  | 1.05   | Preliminary                                                         |

| July 2002       | 1.06   | Preliminary                                                         |

| April 2004      | 1.07   | Preliminary: All references to CSP package are removed in Rev 1.07. |

#### **Table of Contents** Embedded Controller System Features ......2 Clocking, Supply and Package Information ......4 Introduction 1.0 1.1 DOCUMENT ORGANIZATION ......23 1.2 1.2.1 1.2.2 1.2.3 INTERNAL ARCHITECTURE ......25 1.3 1.3.1 1.3.2 1.3.3 1.3.4 1.3.5 1.3.6 1.4 141 1.4.2 1.4.3 1.4.4 PROG Environment 30 1.5 Core Address Domain Memory Map ......33 1.5.1 Register Abbreviations and Access .......34 Accessing Base Memory ......35 Accessing Expansion Memory .......36 Host Address Domain Memory Map ......38 1.5.2 1.5.3 2.0 Signal/Pin Description and Configuration 2.1 BUFFER TYPES AND SIGNAL/PIN DIRECTORY .......41 2.2 ACCESS.bus (ACB1 and ACB2) Interface .......42 2.2.1 2.2.2 Analog Interface .......42 2.2.3 2.2.4 Core Bus Interface Unit (BIU) .......43 2.2.5 2.2.6 General-Purpose I/O (GPIO) and Internal Keyboard Scan .......45 2.2.7 2.2.8 2.2.9 Power and Ground .......49 2.2.10 PS/2 Interface 50 2.2.11

| Tabl | e of C | ontent  | S (Continued)                                                   |    |

|------|--------|---------|-----------------------------------------------------------------|----|

|      |        | 2.2.12  | Mobile System Wake-Up Control (MSWC)                            | 51 |

|      |        | 2.2.13  | Timers and PWM                                                  |    |

|      |        | 2.2.14  | Universal Synchronous/Asynchronous Receiver/Transmitter (USART) | 51 |

|      |        | 2.2.15  | Internal Pull-Up and Pull-Down Resistors                        | 52 |

|      | 2.3    | STRAP   | PINS                                                            | 53 |

|      |        |         | Setting the Environment                                         | 53 |

|      |        |         | Other Strap Pin Settings                                        |    |

|      |        |         | System Load on Strap Pins Strap Pin Status Register (STRPST)    |    |

|      | 0.4    | AL TEDI |                                                                 |    |

|      | 2.4    | 2.4.1   | NATE FUNCTIONS                                                  |    |

|      |        | 2.4.1   | System Configuration Registers                                  |    |

|      |        | 2.4.2   | Register Map                                                    |    |

|      |        |         | Module Configuration Register (MCFG)                            |    |

|      |        |         | External Interrupts Configuration Register (EICFG)              |    |

|      |        | 2.4.3   | GPIO with Echo Configuration                                    | 59 |

|      |        |         | Input to Output Echo Enable Register 1 and 2 (IOEE1 and IOEE2)  | 60 |

| 3.0  | Pow    | er, Res | et and Clocks                                                   |    |

|      | 3.1    | POWER   | ₹                                                               | 62 |

|      |        | 3.1.1   | Power Planes                                                    | 62 |

|      |        | 3.1.2   | Power States                                                    | 62 |

|      |        | 3.1.3   | Power Connection and Layout Guidelines                          | 63 |

|      | 3.2    | RESET   | SOURCES AND TYPES                                               | 65 |

|      |        | 3.2.1   | V <sub>PP</sub> Power-Up Reset                                  | 66 |

|      |        | 3.2.2   | V <sub>CC</sub> Power-Up Reset                                  | 66 |

|      |        | 3.2.3   | WATCHDOG Reset and Debugger Interface Reset                     |    |

|      |        | 3.2.4   | Warm Reset                                                      |    |

|      |        | 3.2.5   | Host Domain Reset                                               |    |

|      |        |         | Using RESET2 Input                                              |    |

|      |        |         | Host Domain Reset Actions                                       |    |

|      | 3.3    | CLOCK   | DOMAINS                                                         |    |

|      |        |         | LPC ClockRTC (32 KHz) Clock                                     |    |

|      |        |         | NTO (32 NTIZ) GIOCK                                             | 00 |

| 4.0  | Emb    |         | Controller Modules                                              |    |

|      | 4.1    |         | TERFACE UNIT (BIU)                                              |    |

|      |        | 4.1.1   | Features                                                        |    |

|      |        | 4.1.2   | Functional Description                                          |    |

|      |        |         | Interface                                                       |    |

|      |        |         | Static Memory and I/O Support                                   |    |

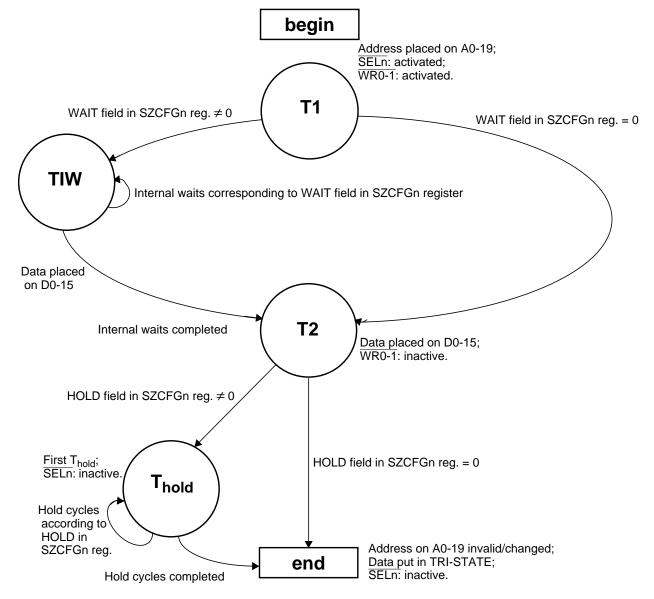

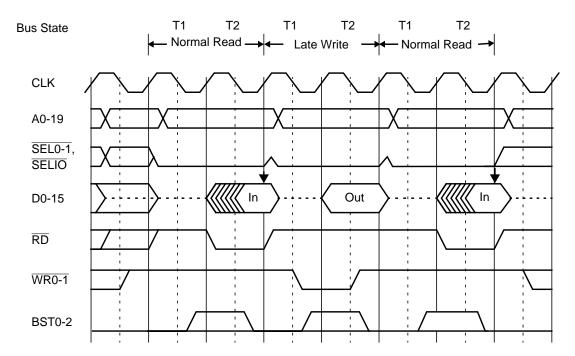

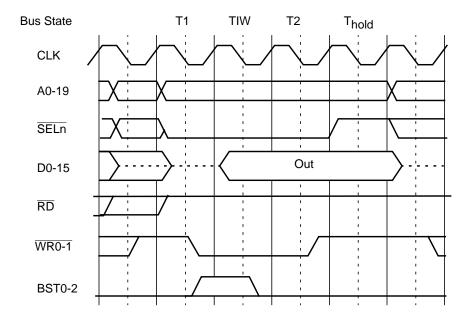

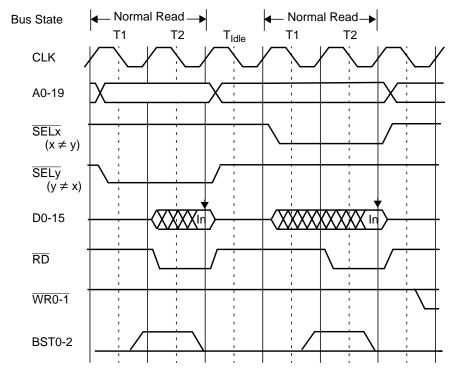

|      |        |         | Clock and Bus Cycles                                            |    |

|      |        | 4.1.3   | Clock Cycles                                                    | 71 |

|      |        |         | Optional Clock Cycles                                           | 71 |

|      |        |         | Other Clock Cycles                                              |    |

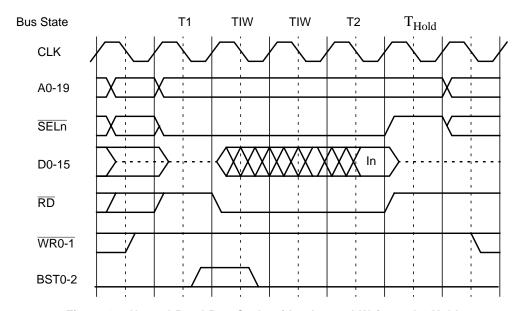

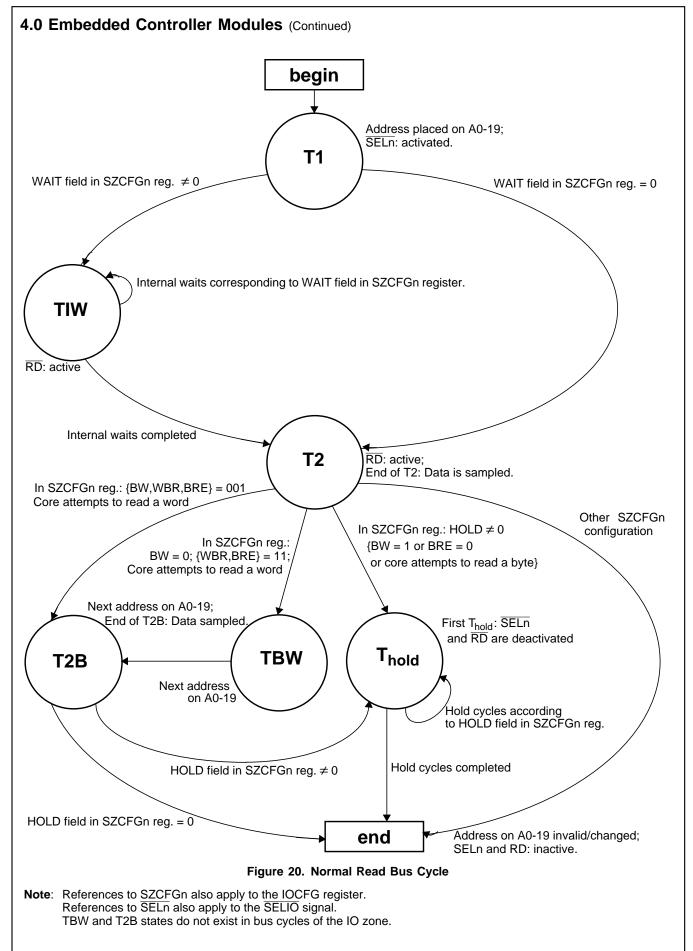

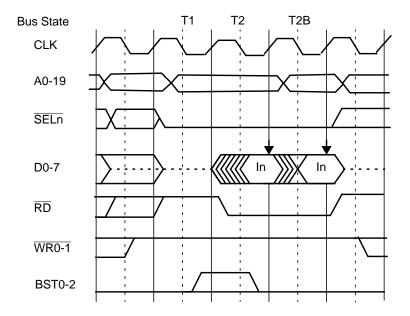

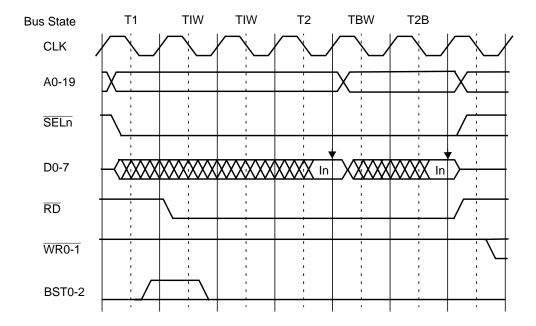

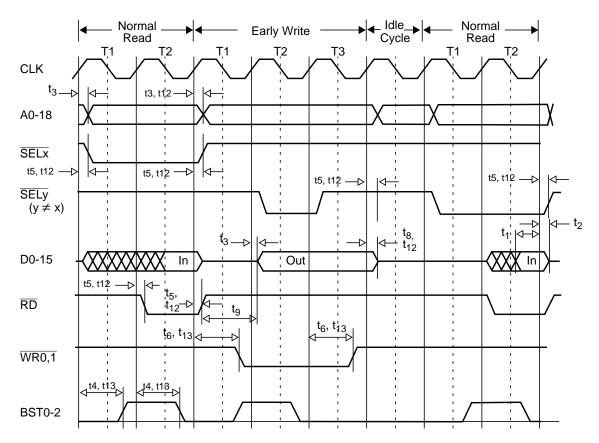

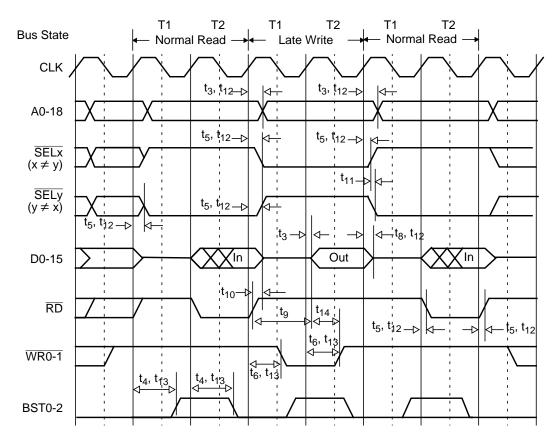

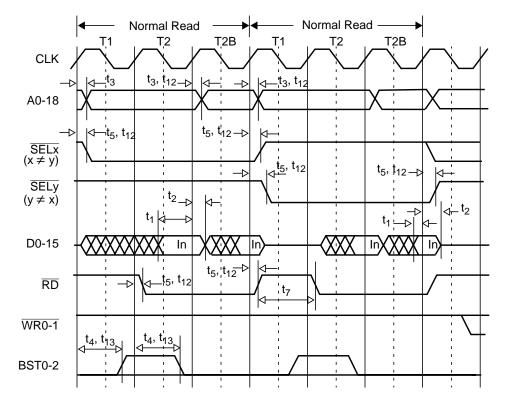

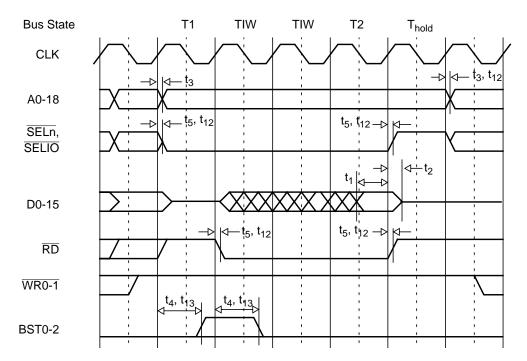

#### Table of Contents (Continued) Control Signals ......72 Early Write Bus Cycle ......72 4.1.4 4.1.5 Late Write Bus Cycle ......74 4.1.6 Normal Read Bus Cycle ......76 4.1.7 Fast Read Bus Cycle ......79 I/O Expansion Bus Cycles ......80 4.1.8 4.1.9 Development Support ......81 Bus Status Signals ......81 Core Bus Monitoring ......82 4.1.10 BIU Registers ......83 BIU Configuration Register (BCFG) ......83 I/O Zone Configuration Register (IOCFG) ......84 Static Zone Configuration Register (SZCFGn) ......85 4.1.11 Usage Hints ......86 DMA CONTROLLER (DMAC) .......87 4.2 4.2.1 4.2.2 Functional Description ......87 Channel Assignment in PC87591x ......87 4.2.3 4.2.4 Direct (Fly-By) Transfers ......88 Indirect (Memory-to-Memory) Transfers ......89 4.2.5 Bus Policy .......90 Intermittent Operation Mode .......90 Continuous Operation Mode ......90 4.2.6 Single Transfer Operation ......91 Double Buffer Operation .......91 Auto-Initialize Operation ......92 4.2.7 Software DMA Request .......92 4.2.8 DMAC Register Map ......92 Device A Address Counter Register (ADCAn) ......93 Device A Address Register (ADRAn) ......93 Device B Address Counter Register (ADCBn) .......93 Device B Address Register (ADRBn) ......93 Block Length Counter Register (BLTCn) ......94 Block Length Register (BLTRn) ......94 DMA Control Register (DMACNTLn) ......94 DMA Status Register (DMASTATn) ......96 4.2.9 4.3 INTERRUPT CONTROL UNIT (ICU) .......98 4.3.1 Features 98 Non-Maskable Interrupt (NMI) .......98 4.3.2 External NMI Inputs .......98 Non-Maskable Interrupt Processing .......98 PFAIL Input ......98 4.3.3 Maskable Interrupt Vectors ......99

# Table of Contents (Continued) Pendin

|     |       | Pending Interrupts                                                                     | 99  |

|-----|-------|----------------------------------------------------------------------------------------|-----|

|     |       | Interrupt Priorities                                                                   | 99  |

|     |       | Power-Down Modes                                                                       |     |

|     |       | External Interrupt Inputs                                                              |     |

|     |       | Interrupt Assignment                                                                   | 99  |

|     | 4.3.4 | ICU Registers                                                                          | 101 |

|     |       | ICU Register Map                                                                       | 101 |

|     |       | Interrupt Vector Register (IVCT)                                                       |     |

|     |       | NMI Status Register (NMISTAT)                                                          |     |

|     |       | Power Fail Interrupt Control and Status Register (PFAIL)                               |     |

|     |       | Interrupt Status Register 0 (ISTAT0)                                                   |     |

|     |       | Interrupt Status Register 1 (ISTAT1)                                                   |     |

|     |       | Interrupt Enable and Mask Register 0 (IENAM0)                                          |     |

|     |       | Interrupt Enable and Mask Register 1 (IENAM1) Edge Interrupt Clear Register 0 (IECLR0) |     |

|     |       | Edge Interrupt Clear Register 1 (IECLR1)                                               |     |

|     | 405   |                                                                                        |     |

|     | 4.3.5 | Usage Hints                                                                            |     |

|     |       | Initializing                                                                           |     |

|     |       | Clearing                                                                               |     |

|     |       | Nesting                                                                                |     |

| 4.4 |       | -INPUT WAKE-UP (MIWU)                                                                  |     |

|     | 4.4.1 | Features                                                                               | 105 |

|     | 4.4.2 | Operation                                                                              | 105 |

|     | 4.4.3 | MIWU Registers                                                                         | 109 |

|     |       | MIWU Register Map                                                                      | 109 |

|     |       | Edge Detection Register (WKEDG1)                                                       |     |

|     |       | Edge Detection Register (WKEDG2)                                                       |     |

|     |       | Edge Detection Register (WKEDG3)                                                       | 110 |

|     |       | Edge Detection Register (WKEDG4)                                                       |     |

|     |       | Pending Register (WKPND1)                                                              |     |

|     |       | Pending Register (WKPND2)                                                              |     |

|     |       | Pending Register (WKPND3)                                                              |     |

|     |       | Pending Register (WKPND4)                                                              |     |

|     |       | Enable Register (WKEN1)                                                                |     |

|     |       | Enable Register (WKEN2) Enable Register (WKEN3)                                        |     |

|     |       | Enable Register (WKEN3)                                                                |     |

|     |       | Pending Clear Register (WKPCL1)                                                        |     |

|     |       | Pending Clear Register (WKPCL2)                                                        |     |

|     |       | Pending Clear Register (WKPCL3)                                                        |     |

|     |       | Pending Clear Register (WKPCL4)                                                        |     |

|     | 4.4.4 | Usage Hints                                                                            |     |

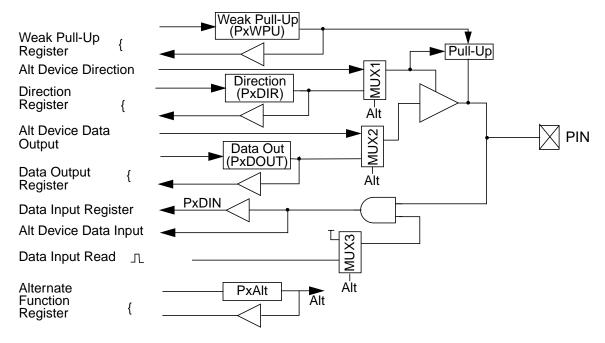

| 4.5 | GENE  | RAL-PURPOSE I/O (GPIO) PORTS                                                           | 113 |

|     | 0     | GPIO Port Functionality                                                                |     |

|     | 4.5.1 | Features                                                                               |     |

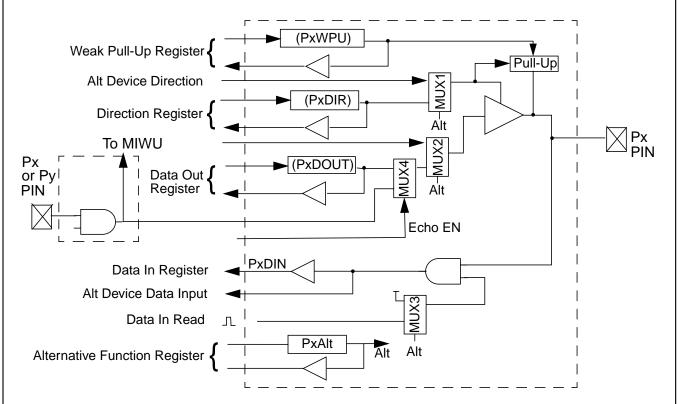

|     | 4.5.2 | GPIO Port Px                                                                           | 114 |

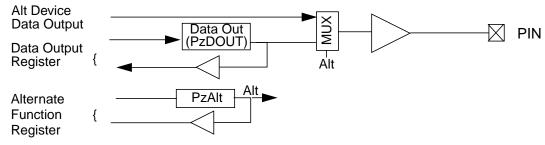

|     |       | Bidirectional Port with Alternate Function                                             |     |

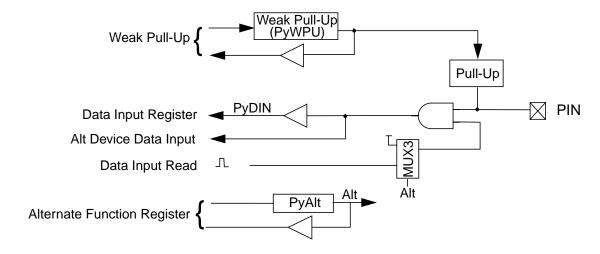

|     | 4.5.3 | GPI Port Py                                                                            |     |

|     |       | Input Only Port with Alternate Function                                                |     |

|     | 154   | •                                                                                      |     |

|     | 4.5.4 | GPO Port Pz                                                                            |     |

|     |       | Output Only Port with Alternate Function                                               | 117 |

| Table of C | Conten | ts (Continued)                                              |     |

|------------|--------|-------------------------------------------------------------|-----|

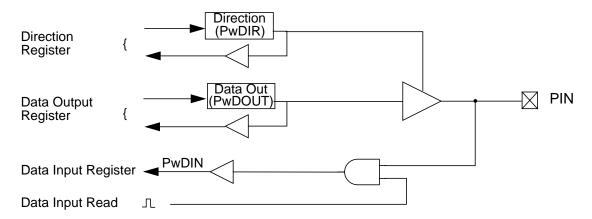

|            | 4.5.5  | GPIO Port Pw                                                | 118 |

|            |        | GPIO Port Signals Shared with Development System Signals    | 118 |

|            | 4.5.6  | GPIO Port Registers                                         |     |

|            |        | GPIO Register Map                                           |     |

|            |        | Port Alternate Function Registers (PxALT, PyALT and PzALT)  |     |

|            |        | Port Direction Registers (PxDIR and PwDIR)                  |     |

|            |        | Port Data Output Register (PxDOUT, PzDOUT and PwDOUT)       |     |

|            |        | Port Data Input Registers (PxDIN, PyDIN and PwDIN)          |     |

|            |        | Port Weak Pull-Up Registers (PxWPU, PyWPU)                  |     |

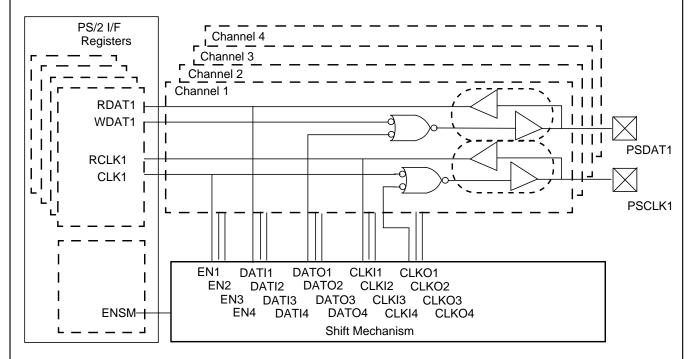

| 4.6        |        | NTERFACE                                                    |     |

|            | 4.6.1  | Features                                                    |     |

|            | 4.6.2  | General Description                                         |     |

|            | 4.6.3  | Operating With the Shift Mechanism Disabled                 |     |

|            | 4.6.4  | Operating With the Shift Mechanism Enabled                  | 125 |

|            |        | Receive Mode                                                |     |

|            |        | Transmit Mode                                               |     |

|            | 4.6.5  | PS/2 Interface Registers                                    |     |

|            |        | PS/2 Register Map                                           |     |

|            |        | PS/2 Data Register (PSDAT)                                  |     |

|            |        | PS/2 Status Register (PSTAT)  PS/2 Control Register (PSCON) |     |

|            |        | PS/2 Output Signal Register (PSOSIG)                        |     |

|            |        | PS/2 Input Signal Register (PSISIG)                         |     |

|            |        | PS/2 Interrupt Enable Register (PSIEN)                      | 133 |

| 4.7        | MULTI  | I-FUNCTION 16-BIT TIMER (MFT16)                             | 134 |

|            | 4.7.1  | Features                                                    | 134 |

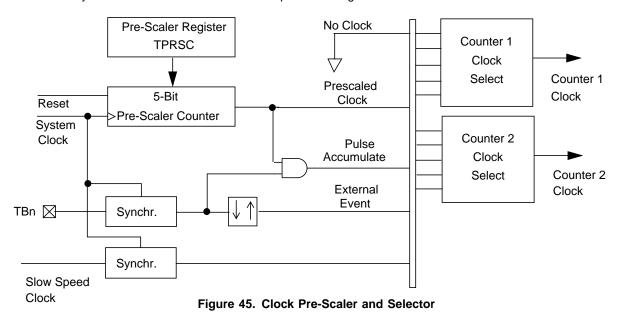

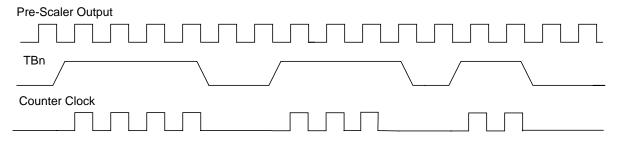

|            | 4.7.2  | Clock Source Unit                                           | 135 |

|            |        | Pre-Scaler                                                  | 135 |

|            |        | External Event Clock                                        | 135 |

|            |        | Pulse Accumulate Mode                                       |     |

|            |        | Slow-Speed Clock                                            |     |

|            | 470    | Counter Clock Source Select                                 |     |

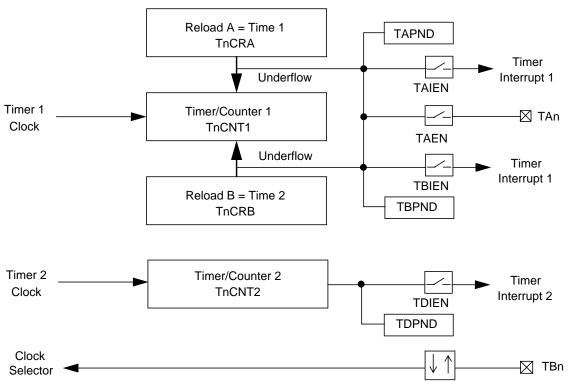

|            | 4.7.3  | Timer/Counter and Action Unit                               |     |

|            |        | Operation Modes  Mode 1, PWM and Counter                    |     |

|            |        | Mode 2, Dual Input Capture                                  |     |

|            |        | Mode 3, Dual Independent Timer                              |     |

|            |        | Mode 4, Input Capture and Timer                             |     |

|            | 4.7.4  | Timer Interrupts                                            | 140 |

|            | 4.7.5  | Timer I/O Functions                                         | 141 |

|            | 4.7.6  | Operation in Development System                             | 141 |

|            | 4.7.7  | MFT16 Registers                                             | 142 |

|            |        | MFT16 Register Map                                          |     |

|            |        | Timer/Counter Register 1 (TnCNT1)                           |     |

|            |        | Reload/Capture Register A (TnCRA)                           |     |

|            |        | Reload/Capture Register B (TnCRB)                           |     |

|            |        | Timer/Counter Register 2 (TnCNT2)                           |     |

|            |        | Clock Unit Control Register (TnCKC)                         |     |

|            |        | Timer Mode Control Register (TnCTRL)                        |     |

|            |        | ·                                                           |     |

Revision 1.07

# Table of Contents (Continued) Timer Interrupt Control Register (TnICTL) ......145 Timer Interrupt Clear Register (TnICLR) ......146 PULSE WIDTH MODULATOR (PWM) ......147 4.8 4.8.2 Cycle Time and Duty Cycle Calculation ......148 4.8.3 4.8.4 4.8.5 PWM Register Map ......148 Clock Pre-Scaler Register (PRSC) ......148 Cycle Time Register (CTR) ......149 PWM Polarity Register (PWMPOL) ......150 PWM Control Register (PWMCNT) ......150 4.9 UNIVERSAL SYNCHRONOUS/ASYNCHRONOUS RECEIVER-TRANSMITTER (USART) .. 151 4.9.1 Functional Overview .......151 4.9.2 4.9.3 4.9.4 USART Register Map ......158 Receive Data Buffer Register (URBUF) ......158 Transmit Data Buffer Register (UTBUF) ......158 Baud Rate Pre-Scaler Register (UPSR) ......158 Baud Rate Divisor Register (UBAUD) ......158 Frame Select Register (UFRS) ......159 Mode Select Register (UMDSL) ......160 Status Register (USTAT) ......161 Interrupt Control Register (UICTRL) ......162

ANALOG TO DIGITAL CONVERTER (ADC) ......170

TIMER AND WATCHDOG (TWD) .......164

4.9.5

4.10.1

4.10.2

4.10.3

4.10.4

4.11.1 4.11.2

4.11.3

4.11.4

4.11.5

4.11

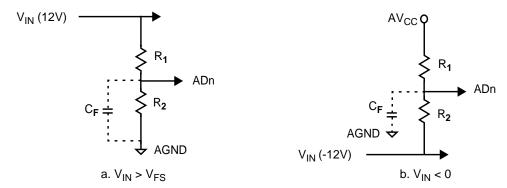

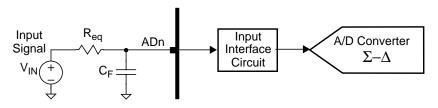

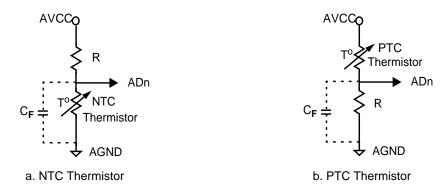

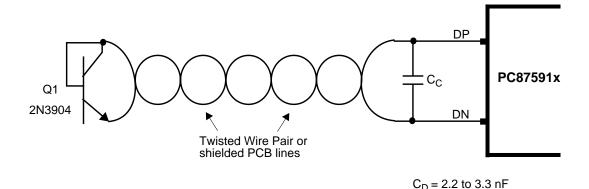

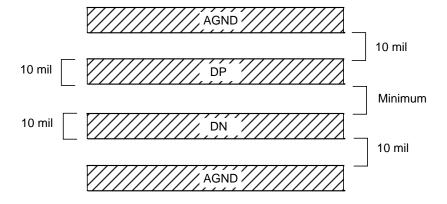

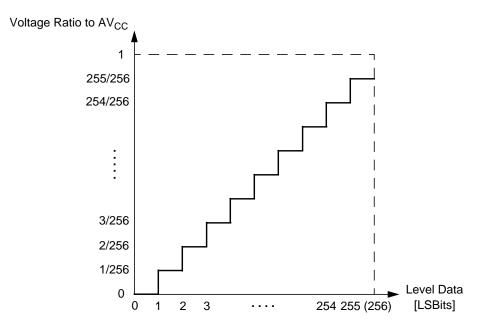

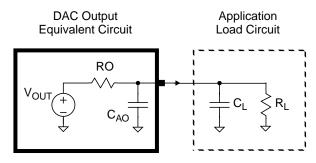

# Table of Contents (Continued) Initializing the ADC ......174 Enabling and Disabling the ADC ......174 Interrupt Structure .......175 ADC Operating Principles ......175 4.11.6 ADC Configuration Register (ADCCNF) ......179 ADC Clock Control Register (ACLKCTL) ......179 ADC Delay Control Register (ADLYCTL) ......180 Local Diode Overtemperature Limit Register (TLOCOTL) ......181 ADC Parameters Index Register (ADCPINX) ......181 ADC Parameters Data Register (ADCPD) ......181 Temperature Channel Control Register (TCHANCTL) ......182 Temperature Channel Data Buffer (TCHANDAT) ......182 Voltage Channel 1 Control Register (VCHN1CTL) ......183 Voltage Channel 1 Data Buffer (VCHN1DAT) ......184 Voltage Channel 2 Control Register (VCHN2CTL) ......184 Voltage Channel 2 Data Buffer (VCHN2DAT) ......184 Voltage Channel 3 Control Register (VCHN3CTL) ......185 Voltage Channel 3 Data Buffer (VCHN3DAT) ......185 Filtering the Noise on Voltage Input Signals ......186 Calculating the Voltage Channel Delay ......186 Thermistor-Based Temperature Measurement ......186 Calculating the Temperature Channel Delay .......188 DIGITAL TO ANALOG CONVERTER (DAC) ......190 4.12.1 4.12.2 4.12.3 Reference Voltage ......191 4.12.4 Enabling and Disabling the DAC ......192 4.12.5 DAC Register Map ......193 DAC Control Register (DACCTRL) ......193 DAC Data Channel 0-3 Registers (DACDAT0-3) ......194

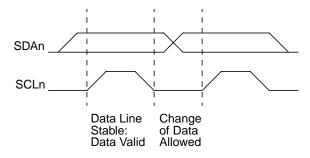

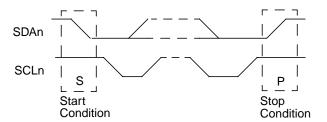

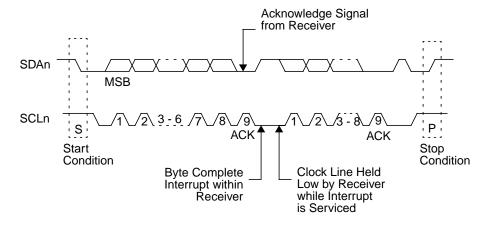

## Table of Contents (Continued) Output Voltage Accuracy ......194 Output Settling Time ......195 Filtering Noise on Output Signals ......195 ACCESS.BUS (ACB) INTERFACE ......196 4.13.2 "Acknowledge After Every Byte" Rule .......198 4.13.3 Slave Mode 201 4.13.4 4.13.5 4.13.6 4.13.7 4.13.8 ACB Register Map ......202 ACB Serial Data Register (ACBnSDA) ......202 ACB Status Register (ACBnST) ......203 ACB Control Status Register (ACBnCST) ......204 ACB Control Register 1 (ACBnCTL1) ......205 ACB Own Address Register (ACBnADDR and ACBnADDR2) ......206 ACB Control Register 2 (ACBnCTL2) ......206 ACB Control Register 3 (ACBnCTL3) ......207 4.13.9 ANALOG COMPARATORS MONITOR (ACM) ......208 4.14 Features 208 4.14.2 4.14.3 4.14.4 Sampling Delay ......210 ACM Operating Sequences ......211 ACM Registers ......212 4.14.5 ACM Register Map ......212 ACM Control and Status Register (ACMCTS) ......213 ACM Configuration Register (ACMCNF) ......214 ACM Timing Control Register (ACMTIM) ......215 Comparison Threshold Data Register (THRDAT) ......216 Comparison Result Register (CMPRES) ......216 Voltage Level Data Buffer - Input 0 through 7 (VOLDAT0-7) ......217 4.14.6 4.15 4.16.1 4.16.2 4.16.3

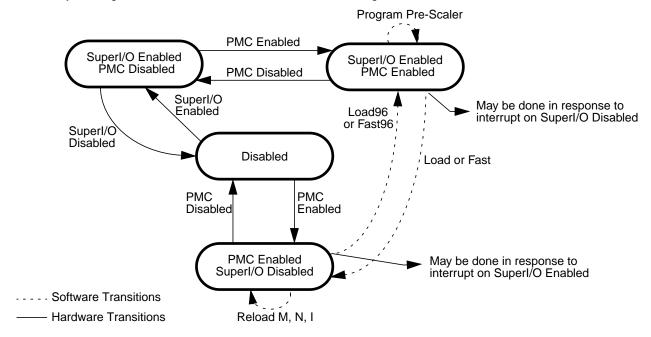

# Table of Contents (Continued) 4.16.5 4.16.6 4.16.7 Information Block Access Index Register (IBAI) ......228 Flash Core Write Protect Register 0 (FCWP0) ......229 Flash Memory Control Register (FLCR) ......230 Flash Memory Status Register (FLSR) ......231 Flash Memory Pre-Scaler Register (FLPSLR) ......231 Flash Memory Start Time Register (FLSTART) ......232 Flash Memory Transition Time Register (FLTRAN) ......232 Flash Memory Program Time Register (FLPROG) ......232 Flash Memory Page Erase Time Register (FLPERASE) ......233 Flash Memory Section Erase Time Register (FLSERASE) .......233 Flash Memory End Time Register (FLEND) ......233 Flash Memory Section Erase End Time Register (FLSEND) ......234 Flash Memory Recovery Time Register (FLRCV) ......234 POWER MANAGEMENT CONTROLLER (PMC) ......235 4.17.1 4.17.2 4.17.3 4.17.4 4.17.5 HIGH-FREQUENCY CLOCK GENERATOR (HFCG) ......239 4.18 4.18.1 4.18.2 4.18.3 PMC Enabled SuperI/O Disabled State ......240 SuperI/O Enabled State ......242 The Programmable Pre-Scaler: Core Domain Clock Generation ......242 4.18.4 4.18.5 4.18.6 4.18.7 HFCG Registers ......243 HFCG Register Map ......243 HFCG Control Register 1 (HFCGCTRL1) ......244 HFCGM Low Value Register (HFCGML) ......245 HFCGM High Value Register (HFCGMH) ......245 HFCGN Value Register (HFCGN) ......245 HFCGI Low Value Register (HFCGIL) ......246 HFCGI High Value Register (HFCGIH) ......246 HFCG Pre-Scaler Register (HFCGP) ......246 HFCG Control Register 2 (HFCGCTRL2) ......247 THE DEBUGGER INTERFACE ......248 Features 248

# Table of Contents (Continued)

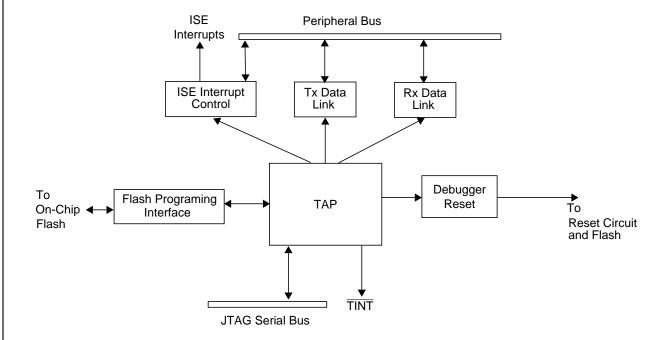

|      | 4.19.3  | Debugger Interface Functional Description                                      | 249 |

|------|---------|--------------------------------------------------------------------------------|-----|

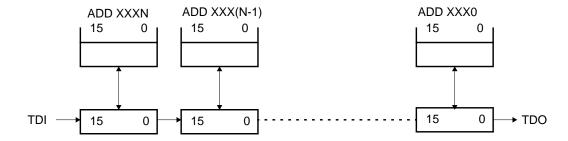

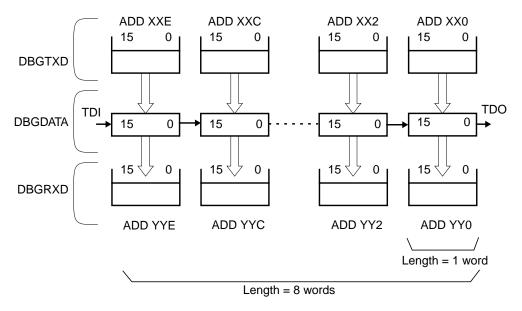

|      |         | Rx Data Link                                                                   | 249 |

|      |         | TX Data Link                                                                   | 250 |

|      |         | Debugger Reset Circuit                                                         |     |

|      |         | ISE Interrupt Control                                                          |     |

|      |         | Clock Synchronization                                                          |     |

|      | 4.19.4  | Flash Interface Functional Description                                         | 251 |

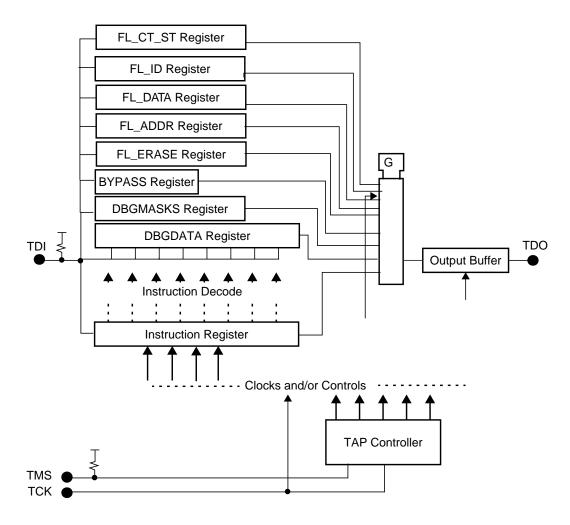

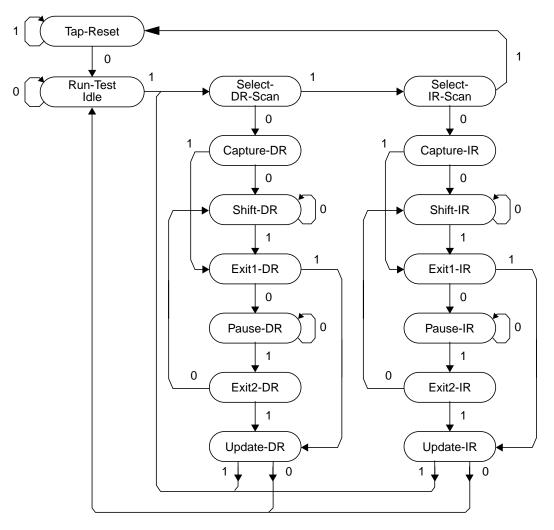

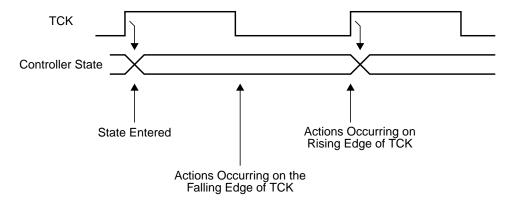

|      | 4.19.5  | Test Access Port (TAP)                                                         | 253 |

|      |         | TAP Signals                                                                    |     |

|      |         | TAP Controller                                                                 | 254 |

|      | 4.19.6  | TAP Instruction Register                                                       | 256 |

|      |         | Design and Construction                                                        |     |

|      |         | Instruction Register Operation                                                 |     |

|      |         | Instructions                                                                   |     |

|      |         | Flash Support Instructions                                                     |     |

|      | 4 40 7  | Debugger Interface Instructions                                                |     |

|      | 4.19.7  | TAP Data Registers, Debugger Interface                                         |     |

|      |         | Bit Arrangement and Mapping                                                    |     |

|      |         | Functionality in Various TAP Controller States  Debug Bypass Register (BYPASS) |     |

|      |         | Debug Data Register (DBGDATA)                                                  |     |

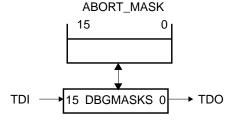

|      |         | Debug Abort Mask Register (DBGMASKS)                                           |     |

|      | 4.19.8  | TAP Data Registers, Flash Interface                                            |     |

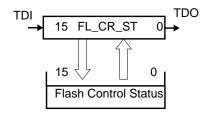

|      | 1.10.0  | Flash Control and Status Register (FL_CT_ST)                                   |     |

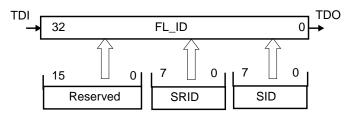

|      |         | Flash Identification Register (FL_ID)                                          |     |

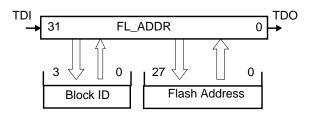

|      |         | Flash Address Register (FL_ADDR)                                               |     |

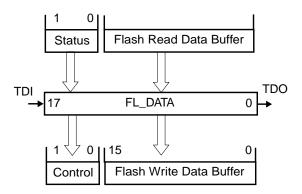

|      |         | Flash Data Register (FL_DATA)                                                  |     |

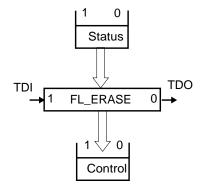

|      |         | Flash Erase Register (FL_ERASE)                                                | 266 |

|      | 4.19.9  | Core Registers, Debugger Interface                                             | 267 |

|      |         | Core Register Map                                                              | 267 |

|      |         | Debug Receive Data Registers 0, 2, 4, 6, 8, 10, 12 and 14 (DBGRXD0-14)         |     |

|      |         | Debug Receive Status Register (DBGRXST)                                        |     |

|      |         | Debug Transmit Data Registers 0, 2, 4, 6, 8, 10, 12 and 14 (DBGTXD0-14)        |     |

|      |         | Debug Transmit Lock Register (DBGTXLOC)                                        |     |

|      |         | Debug Transmit Status Register (DBGTXST)  Debug TINT Assert Register (DBGTINT) |     |

|      |         | Debug Abort Generate Register (DBGABORT)                                       |     |

|      |         | Debug ISE Source Registers A (DBGISESRCA)                                      |     |

|      | 4.19.10 | Usage Hints                                                                    |     |

| 4.20 |         | DPMENT SYSTEM SUPPORT                                                          |     |

| 4.20 |         | Features                                                                       |     |

|      | 4.20.1  |                                                                                |     |

|      | 4.20.2  | The ISE Interrupt                                                              |     |

|      | 4.20.3  | Break Line and Reset Output Interrupt                                          |     |

|      | 4.20.4  | TRIS Strap Input Pin                                                           |     |

|      | 4.20.5  | Freezing Events                                                                |     |

|      | 4.20.6  | Monitoring Activity During Development                                         | 273 |

|      |         | Bus Status Signals                                                             |     |

|      |         | Transaction Effect on the External Bus                                         |     |

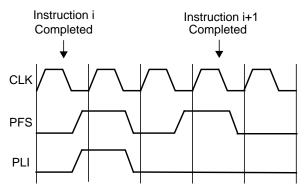

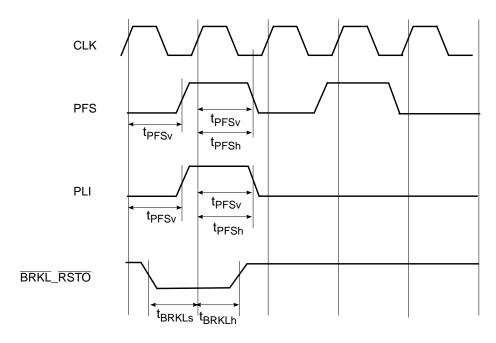

|      |         | Pipe Status Signals (PFS and PLI)                                              |     |

|      | 4.20.7  | On-Chip Hardware Breakpoint                                                    | 274 |

|      |         |                                                                                |     |

| Table | e of C                              | ontent | S (Continued)                                                                                                    |     |  |  |  |  |  |

|-------|-------------------------------------|--------|------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

|       |                                     | 4.20.8 | CR16B Development Support Registers                                                                              | 275 |  |  |  |  |  |

|       |                                     |        | Debug Configuration Register (DBGCFG)                                                                            |     |  |  |  |  |  |

|       |                                     |        | Debug Freeze Enable Register (DBGFRZEN)                                                                          |     |  |  |  |  |  |

| 5.0   | O Host Controller Interface Modules |        |                                                                                                                  |     |  |  |  |  |  |

|       | 5.1                                 |        | OARD AND MOUSE CONTROLLER INTERFACE                                                                              | 277 |  |  |  |  |  |

|       | 0.1                                 | 5.1.1  | Features                                                                                                         |     |  |  |  |  |  |

|       |                                     | 5.1.2  | General Description                                                                                              |     |  |  |  |  |  |

|       |                                     | J. 1.Z | Host Addresses                                                                                                   |     |  |  |  |  |  |

|       |                                     |        | Core Interrupts                                                                                                  |     |  |  |  |  |  |

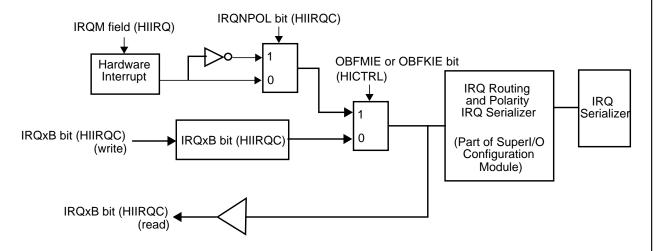

|       |                                     |        | Host Interrupts                                                                                                  |     |  |  |  |  |  |

|       |                                     |        | Keyboard/Mouse Channel (6016, 6416)                                                                              |     |  |  |  |  |  |

|       |                                     |        | Status Read                                                                                                      |     |  |  |  |  |  |

|       |                                     | 5.1.3  | Host Interface Registers                                                                                         | 280 |  |  |  |  |  |

|       |                                     |        | Host Interface Register Map                                                                                      | 280 |  |  |  |  |  |

|       |                                     |        | Data Out Buffer Register (DBBOUT, Legacy 6016)                                                                   |     |  |  |  |  |  |

|       |                                     |        | Status Register (STATUS, Legacy 6416)                                                                            |     |  |  |  |  |  |

|       |                                     |        | Data In Buffer Register (DBBIN, Legacy 6016)                                                                     |     |  |  |  |  |  |

|       |                                     |        | Command In Buffer Register (COMAND, Legacy 6416)                                                                 |     |  |  |  |  |  |

|       |                                     | 5.1.4  | Core Interface Registers                                                                                         |     |  |  |  |  |  |

|       |                                     |        | Core Interface Register Map                                                                                      |     |  |  |  |  |  |

|       |                                     |        | Host Interface Control Register (HICTRL)                                                                         |     |  |  |  |  |  |

|       |                                     |        | Host Interface IRQ Control Register (HIIRQC)                                                                     |     |  |  |  |  |  |

|       |                                     |        | Host Interface Keyboard/Mouse Status Register (HIKMST)  Host Interface Keyboard Data Out Buffer Register (HIKDO) |     |  |  |  |  |  |

|       |                                     |        | Host Interface Mouse Data Out Buffer Register (HIMDO)                                                            |     |  |  |  |  |  |

|       |                                     |        | Host Interface Keyboard/Mouse Data In Buffer Register (HIKMDI)                                                   |     |  |  |  |  |  |

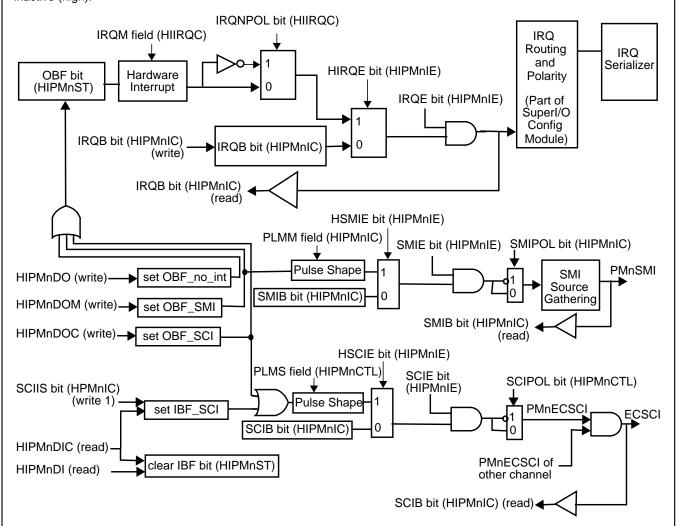

|       | 5.2                                 | POWE   | R MANAGEMENT (PM) CHANNELS                                                                                       | 285 |  |  |  |  |  |

|       |                                     | 5.2.1  | Features                                                                                                         | 285 |  |  |  |  |  |

|       |                                     | 5.2.2  | General Description                                                                                              | 286 |  |  |  |  |  |

|       |                                     |        | Host Addresses                                                                                                   | 286 |  |  |  |  |  |

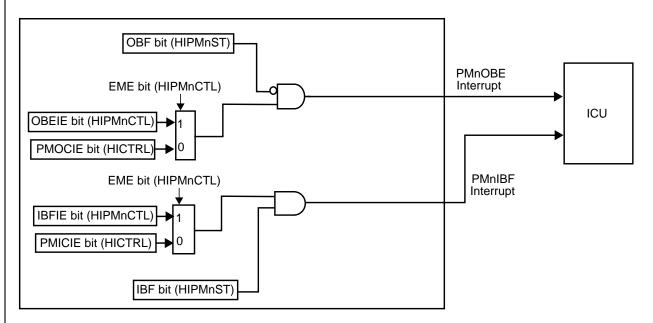

|       |                                     |        | Core Interrupts                                                                                                  | 287 |  |  |  |  |  |

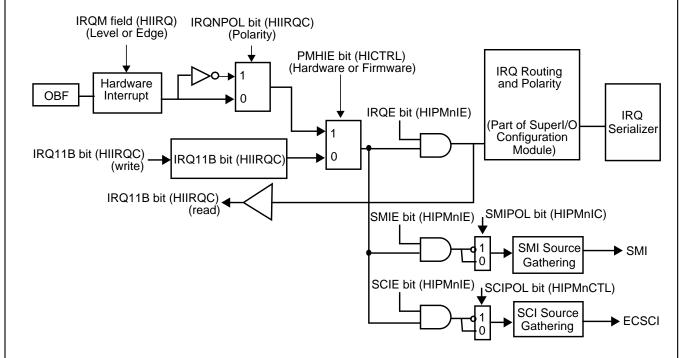

|       |                                     |        | Host Interrupt Generation Modes                                                                                  |     |  |  |  |  |  |

|       |                                     |        | Status Read                                                                                                      |     |  |  |  |  |  |

|       |                                     |        | Host Data Read from Host Interface Power Management Channel                                                      |     |  |  |  |  |  |

|       |                                     | 5.2.3  | Core PM Registers                                                                                                |     |  |  |  |  |  |

|       |                                     |        | Core PM Register Map                                                                                             |     |  |  |  |  |  |

|       |                                     |        | Host Interface PM n Status Register (HIPMnST)                                                                    |     |  |  |  |  |  |

|       |                                     |        | Host Interface PM n Data Out Buffer (HIPMnDO)  Host Interface PM n Data Out Buffer with SCI (HIPMnDOC)           |     |  |  |  |  |  |

|       |                                     |        | Host Interface PM n Data Out Buffer with SMI (HIPMnDOM)                                                          |     |  |  |  |  |  |

|       |                                     |        | Host Interface PM n Data In Buffer (HIPMnDI)                                                                     |     |  |  |  |  |  |

|       |                                     |        | Host Interface PM n Data In Buffer with SCI (HIPMnDIC)                                                           |     |  |  |  |  |  |

|       |                                     |        | Host Interface PM n Control Register (HIPMnCTL)                                                                  |     |  |  |  |  |  |

|       |                                     |        | Host Interface PM n Interrupt Control Register (HIPMnIC)                                                         |     |  |  |  |  |  |

|       |                                     |        | Host Interface PM n Interrupt Enable Register (HIPMnIE)                                                          | 296 |  |  |  |  |  |

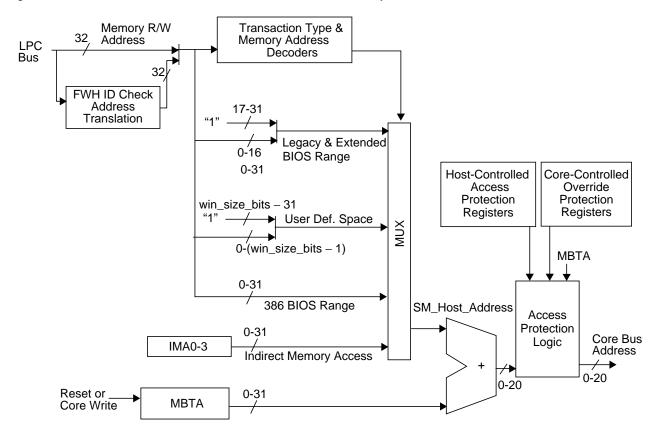

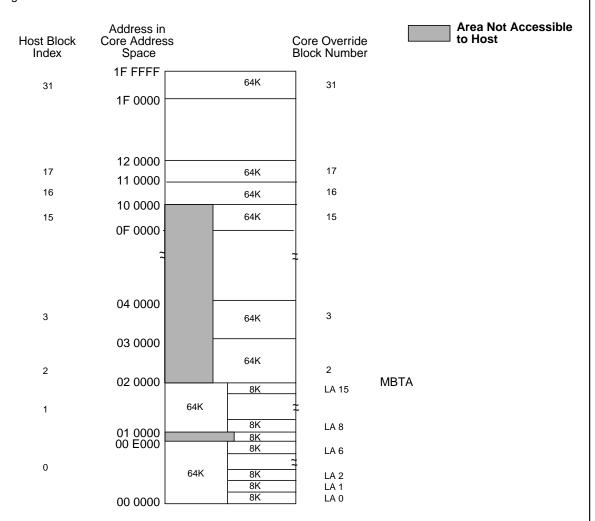

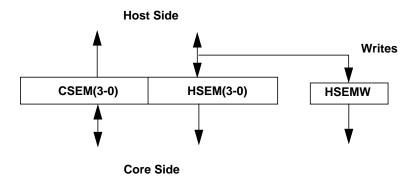

|       | 5.3                                 | SHARE  | D MEMORY AND SECURITY                                                                                            | 297 |  |  |  |  |  |

|       |                                     | 5.3.1  | Host Bus to Core Bus Access Translation                                                                          | 297 |  |  |  |  |  |

|       |                                     | 5.3.2  | Memory Mapping and Host Address Translation                                                                      | 297 |  |  |  |  |  |

|       |                                     | 5.3.3  | Indirect Memory Read and Write Transaction                                                                       | 300 |  |  |  |  |  |

# Table of Contents (Continued) 5.3.4 5.3.5 5.3.6 5.3.7 5.3.8 Shared Memory Indirect Memory Address Register 1 (SMIMA1) ......304 Shared Memory Indirect Memory Address Register 2 (SMIMA2) ......304 Shared Memory Indirect Memory Address Register 3 (SMIMA3) ......304 Shared Memory Indirect Memory Data Register (SMIMD) .......305 Shared Memory Host Status Register (SMHST) ......305 Shared Memory Host Access Protect Register 1 and 2 (SMHAP1-2) ......306 5.3.9 Shared Memory Host Semaphore Register (SMHSEM) ......308 Shared Memory Core Override Read Protect Registers 0-2 (SMCORP0-2) ..... 309 Shared Memory Core Override Write Protect Registers 0-2 (SMCOWP0-2) .... 310 Random Number Generator Control/Status Register, RNGCS (PC87591S) .... 311 5.4 5.4.1 Indirect Host I/O Address Register (IHIOA) ......314 Indirect Host Data Register (IHD) ......314 Lock SuperI/O Host Access Register (LKSIOHA) ......315 Core to SIB Modules Access Enable Register (CRSMAE) .......316 5.5 5.5.1 Features 318 5.5.2 Wake-Up Output Events ......320 5.5.3 5.5.4 Host Configuration Address Selection .......322 Host Keyboard Fast Reset ......322 GA20 Pin Functionality .......322 MSWC Host Registers ......323 5.5.5 Wake-Up Event Status Register 0 (WK STS0) ......323 Wake-Up Events Enable Register (WK\_EN0) ......324 Wake-Up Configuration Register (WK\_CFG) ......325 Wake-Up ACPI State Register (WK STATE) ......326 Wake-Up Event Routing to SMI Enable Register 0 (WK SMIEN0) .......327 Wake-Up Event Routing to IRQ Enable Register 0 (WK IRQEN0) ......328 MSWC Core Registers 328 5.5.6

| Tabl | e of ( | Content  | S (Continued)                                                       |     |

|------|--------|----------|---------------------------------------------------------------------|-----|

|      |        |          | MSWC Control Status Register 1 (MSWCTL1)                            | 329 |

|      |        |          | MSWC Control Status Register 2 (MSWCTL2)                            |     |

|      |        |          | MSWC Control Status Register 3 (MSWCTL3)                            |     |

|      |        |          | Host Configuration Base Address Low (HCFGBAL)                       | 331 |

|      |        |          | Host Configuration Base Address High (HCFGBAH)                      |     |

|      |        |          | MSWC Interrupt Enable Register 2 (MSIEN2)                           |     |

|      |        |          | MSWC Host Event Status Register 0 (MSHES0)                          |     |

|      |        |          | MSWC Host Event Interrupt Enable Register (MSHEIE0)                 |     |

|      |        | 5.5.7    | Usage Hints                                                         |     |

|      |        |          | PWUREQ Output Connection                                            |     |

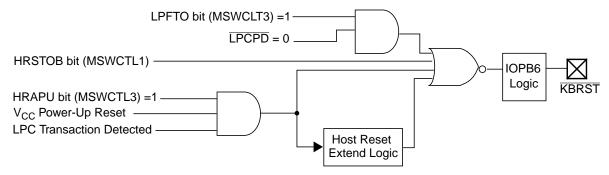

|      |        |          | RESET2 Events                                                       | 334 |

| 6.0  | Hos    | t-Contro | olled Modules and Host Interface                                    |     |

|      | 6.1    | DEVIC    | E ARCHITECTURE AND CONFIGURATION                                    | 335 |

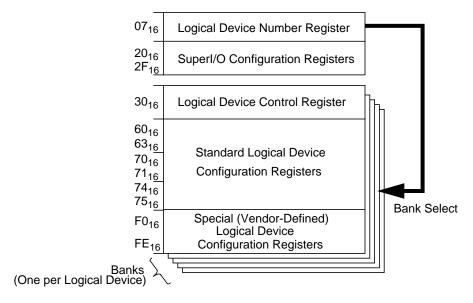

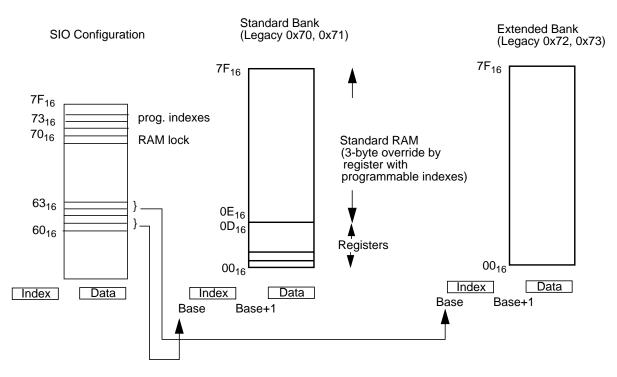

|      |        | 6.1.1    | Configuration Structure and Access                                  | 335 |

|      |        |          | The Index-Data Register Pair                                        | 335 |

|      |        |          | Banked Logical Device Registers Structure                           |     |

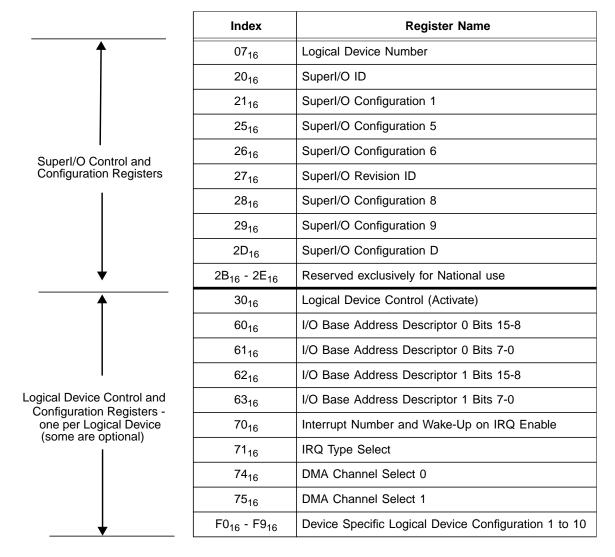

|      |        |          | Standard Logical Device Configuration Register Definitions          | 337 |

|      |        | 6.1.2    | Standard Configuration Registers                                    | 340 |

|      |        |          | SuperI/O Control and Configuration Registers                        | 340 |

|      |        |          | Logical Device Control and Configuration Registers                  |     |

|      |        |          | Control                                                             | 340 |

|      |        |          | Standard Configuration                                              |     |

|      |        |          | Special Configuration                                               |     |

|      |        | 6.1.3    | Default Configuration Setup                                         | 341 |

|      |        | 6.1.4    | Address Decoding                                                    | 341 |

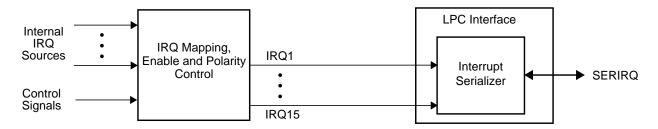

|      |        | 6.1.5    | Interrupt Serializer                                                | 342 |

|      |        | 6.1.6    | Protection                                                          | 342 |

|      |        | 6.1.7    | LPC Interface                                                       | 342 |

|      |        |          | LPC Transactions Supported                                          |     |

|      |        |          | Core Interrupt                                                      |     |

|      |        |          | CLKRUN Functionality                                                |     |

|      |        |          | LPCPD Functionality                                                 |     |

|      |        | 6.1.8    | SuperI/O Configuration Registers                                    | 343 |

|      |        |          | SuperI/O ID Register (SID)                                          |     |

|      |        |          | SuperI/O Configuration 1 Register (SIOCF1)                          |     |

|      |        |          | SuperI/O Configuration 5 Register (SIOCF5)                          |     |

|      |        |          | SuperI/O Configuration 6 Register (SIOCF6)                          |     |

|      |        |          | SuperI/O Revision ID Register (SRID)                                | 346 |

|      |        |          | SuperI/O Configuration 8 Register (SIOCF8)                          | 346 |

|      |        |          | SuperI/O Configuration 9 Register (SIOCF9)                          |     |

|      |        |          | SuperI/O Configuration D Register (SIOCFD)                          | 347 |

|      |        | 6.1.9    | Mobile System Wake-Up Control (MSWC) Configuration                  | 348 |

|      |        |          | Logical Device 4 (MSWC) Configuration                               | 348 |

|      |        | 6.1.10   | Keyboard and Mouse Controller (KBC) Configuration                   | 348 |

|      |        |          | Logical Devices 5 and 6 (Mouse and Keyboard) Configuration          |     |

|      |        | 6.1.11   | Shared Memory Configuration                                         |     |

|      |        | 0.1.11   | Logical Device 15 (0F <sub>16</sub> ) (Shared Memory) Configuration |     |

|      |        |          | Memory Range Programing                                             |     |

|      |        |          | Shared Memory Configuration Register                                |     |

|      |        |          |                                                                     |     |

# Table of Contents (Continued)

|     |        | Shared Memory Base Address High Byte Register                    | 352                |

|-----|--------|------------------------------------------------------------------|--------------------|

|     | 6.1.12 | Real Time Clock (RTC) Configuration                              |                    |

|     |        | Logical Device 16 (10 <sub>16</sub> ) RTC Configuration          |                    |

|     |        | RAM Lock Register (RLR)                                          | 353                |

|     |        | Date Of Month Alarm Register Offset (DOMAO)                      |                    |

|     |        | Month Alarm Register Offset (MONAO)                              |                    |

|     |        | Century Register Offset (CENO)                                   |                    |

|     | 6.1.13 | Power Management Interface Channel 1 Configuration               |                    |

|     |        | Logical Device 17 (11 <sub>16</sub> ) Power Management Channel 1 |                    |

|     | 6.1.14 | Power Management Interface Channel 2 Configuration               |                    |

|     |        | Logical Device 18 (12 <sub>16</sub> ) Power Management Channel 2 | 355                |

| 6.2 | REAL-1 | TIME CLOCK (RTC)                                                 | 356                |

|     | 6.2.1  | Bus Interface                                                    | 356                |

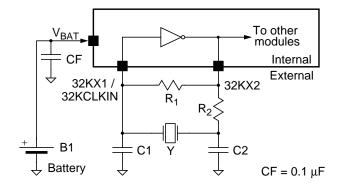

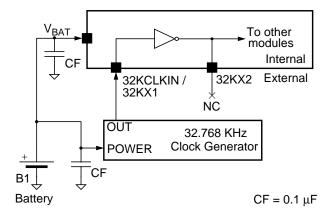

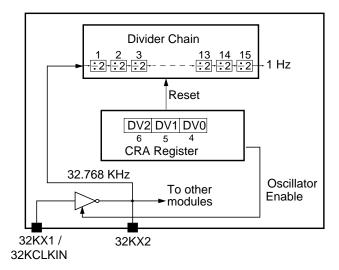

|     | 6.2.2  | RTC Clock Generation                                             | 356                |

|     | 6.2.3  | Internal Oscillator                                              | 356                |

|     | 6.2.4  | External Oscillator                                              | 357                |

|     |        | Connections                                                      | 357                |

|     |        | Signal Parameters                                                | 358                |

|     | 6.2.5  | Timing Generation                                                | 358                |

|     | 6.2.6  | Timekeeping                                                      | 358                |

|     | 6.2.7  | Updating                                                         | 359                |

|     | 6.2.8  | Alarms                                                           | 359                |

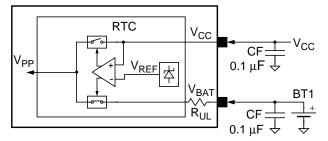

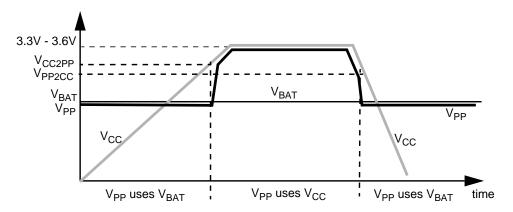

|     | 6.2.9  | Power Supply                                                     | 360                |

|     | 6.2.10 | System Bus Lockout                                               |                    |

|     | 6.2.11 | Power-Up Detection                                               |                    |

|     | 6.2.12 | Oscillator Activity                                              |                    |

|     | 6.2.13 | Interrupt Handling                                               |                    |

|     | 6.2.14 | Battery-Backed RAMs and Registers                                |                    |

|     | 6.2.15 | RTC Registers                                                    |                    |

|     | 0.2.10 | Seconds Register (SEC)                                           |                    |

|     |        | Seconds Alarm Register (SECA)                                    |                    |

|     |        | Minutes Register (MIN)                                           |                    |

|     |        | Minutes Alarm Register (MINA)                                    | 365                |

|     |        | Hours Register (HOR)                                             |                    |

|     |        | Hours Alarm Register (HORA)                                      |                    |

|     |        | Day Of Week Register (DOW)  Date Of Month Register (DOM)         |                    |

|     |        | Month Register (MON)                                             |                    |

|     |        | Year Register (YER)                                              |                    |

|     |        | RTC Control Register A (CRA)                                     | 367                |

|     |        | RTC Control Register B (CRB)                                     |                    |

|     |        | RTC Control Register C (CRC)                                     |                    |

|     |        | RTC Control Register D (CRD)                                     |                    |

|     |        | Date of Month Alarm Register (DOMA)                              |                    |

|     |        | Century Register (CEN)                                           |                    |

|     | 6.2.16 | BCD and Binary Formats                                           |                    |

|     |        |                                                                  | · <del>-</del> · · |

| Tabl | e of C | Content | S (Continued)                                                           |     |

|------|--------|---------|-------------------------------------------------------------------------|-----|

|      |        | 6.2.17  | Usage Hints                                                             | 371 |

|      |        | 6.2.18  | RTC General-Purpose RAM Map                                             | 371 |

| 7.0  | Devi   | ce Spe  | cifications                                                             |     |

|      | 7.1    | GENER   | RAL DC ELECTRICAL CHARACTERISTICS                                       | 372 |

|      |        | 7.1.1   | Recommended Operating Conditions                                        | 372 |

|      |        | 7.1.2   | Absolute Maximum Ratings                                                | 372 |

|      |        | 7.1.3   | Capacitance                                                             | 373 |

|      |        | 7.1.4   | Power Supply Current Consumption under Recommended Operating Conditions | 373 |

|      |        | 7.1.5   | Voltage Thresholds                                                      | 373 |

|      | 7.2    | DC CH   | ARACTERISTICS OF PINS BY I/O BUFFER TYPES                               | 374 |

|      |        | 7.2.1   | Input, CMOS Compatible with Schmitt Trigger                             | 374 |

|      |        | 7.2.2   | Input, PCI 3.3V                                                         | 374 |

|      |        | 7.2.3   | Input, SMBus Compatible                                                 | 374 |

|      |        | 7.2.4   | Input, TTL Compatible                                                   | 375 |

|      |        | 7.2.5   | Input, TTL Compatible with Schmitt Trigger                              | 375 |

|      |        | 7.2.6   | Output, TTL Compatible Push-Pull Buffer                                 | 375 |

|      |        | 7.2.7   | Output, Open-Drain Buffer                                               | 376 |

|      |        | 7.2.8   | Output, PCI 3.3V                                                        | 376 |

|      |        | 7.2.9   | Exceptions                                                              | 376 |

|      |        | 7.2.10  | Terminology                                                             | 376 |

|      | 7.3    | INTERN  | NAL RESISTORS                                                           | 377 |

|      |        |         | DC Test Conditions                                                      | 377 |

|      |        | 7.3.1   | Pull-Up Resistor                                                        | 377 |

|      |        | 7.3.2   | Pull-Down Resistor                                                      | 377 |

|      | 7.4    | ANALO   | G CHARACTERISTICS                                                       | 378 |

|      |        | 7.4.1   | ADC Characteristics                                                     | 378 |

|      |        |         | Voltage Measurement                                                     |     |

|      |        |         | Temperature Measurement                                                 | 380 |

|      |        | 7.4.2   | ACM Characteristics                                                     |     |

|      |        | 7.4.3   | DAC Characteristics                                                     | 381 |

|      | 7.5    | PACKA   | GE THERMAL INFORMATION                                                  | 381 |

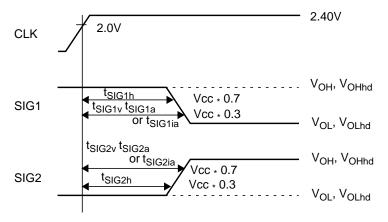

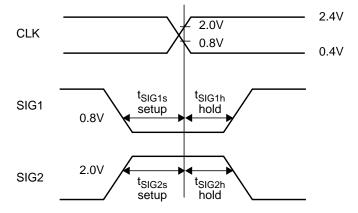

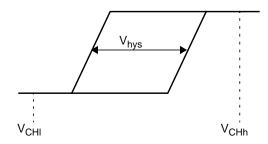

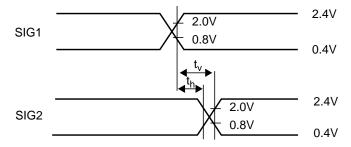

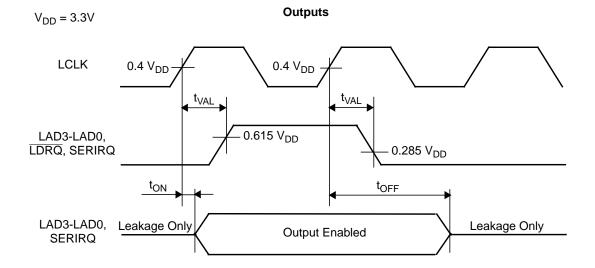

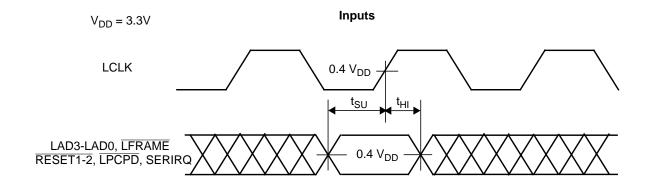

|      | 7.6    | AC ELE  | ECTRICAL CHARACTERISTICS                                                | 382 |

|      |        | 7.6.1   | AC Test Conditions                                                      | 382 |

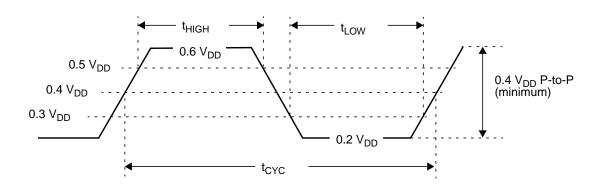

|      |        |         | Definitions                                                             | 382 |

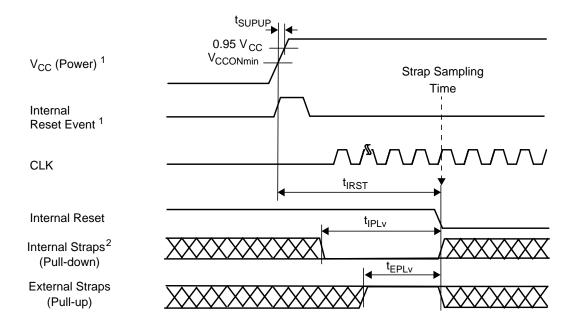

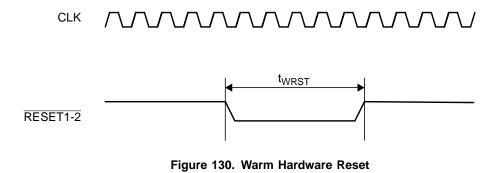

|      |        | 7.6.2   | Reset Timing                                                            | 384 |

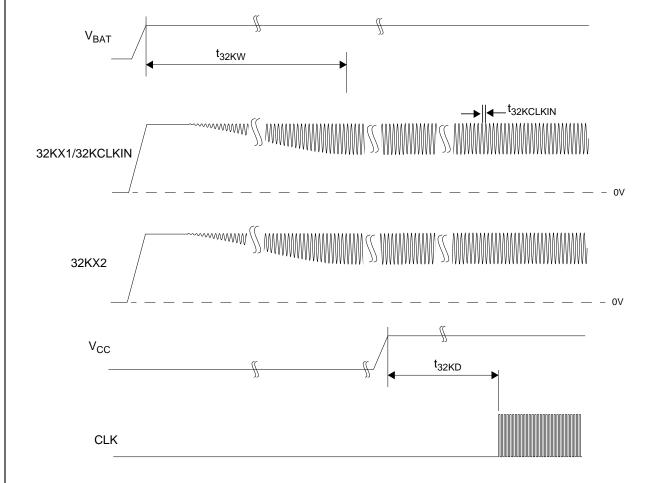

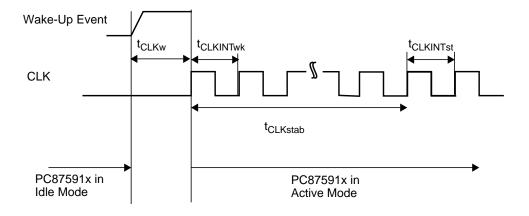

|      |        | 7.6.3   | Clock Timing                                                            | 385 |

|      |        |         | General                                                                 | 386 |

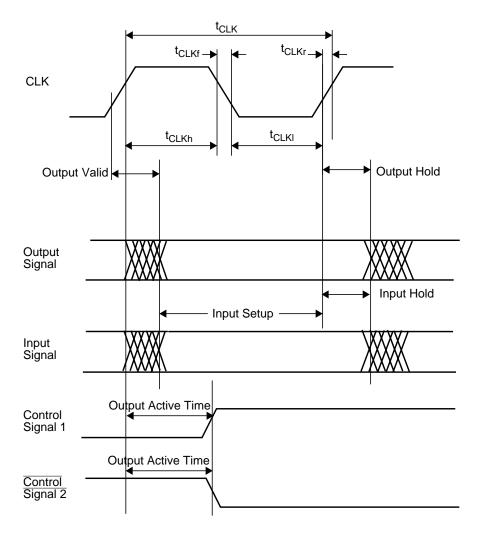

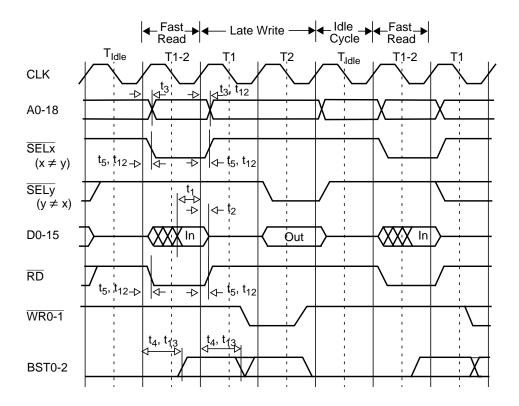

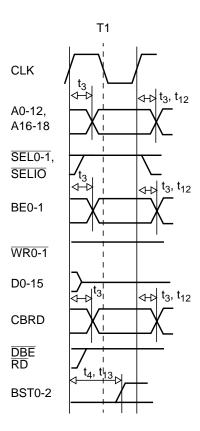

|      |        | 7.6.4   | BIU Timing                                                              | 388 |

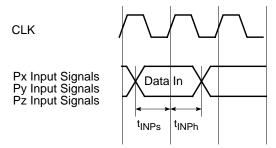

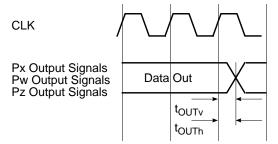

|      |        | 7.6.5   | GPIO Ports Timing                                                       |     |

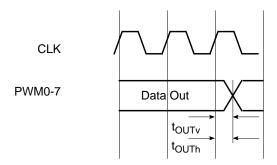

|      |        | 7.6.6   | PWM Timing                                                              | 394 |

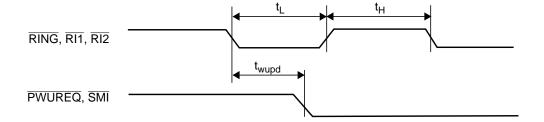

|      |        | 7.6.7   | MSWC Timing                                                             |     |

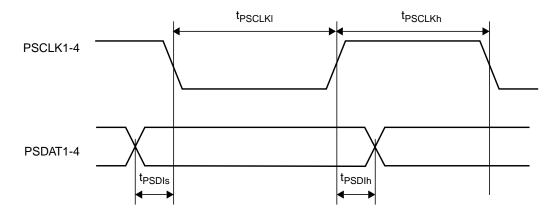

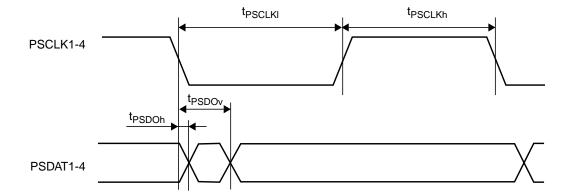

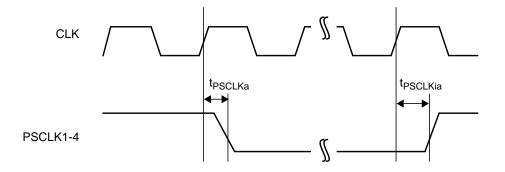

|      |        | 7.6.8   | PS/2 Interface Timing                                                   |     |

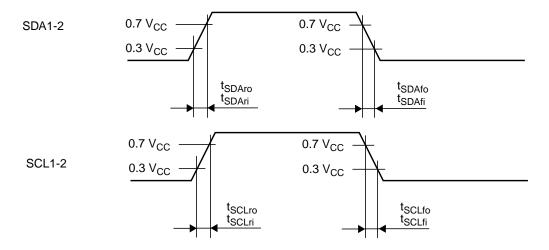

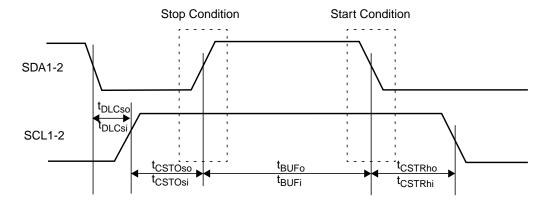

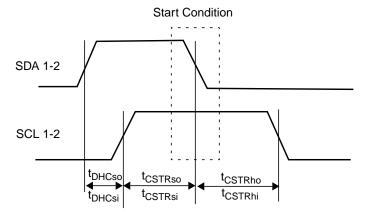

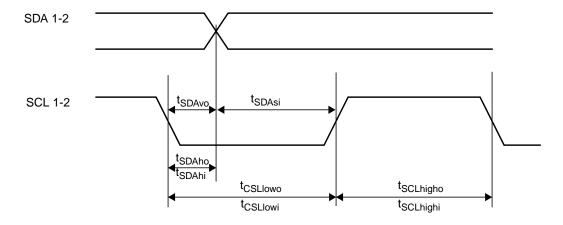

|      |        | 7.6.9   | ACCESS.bus Timing                                                       |     |

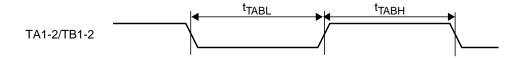

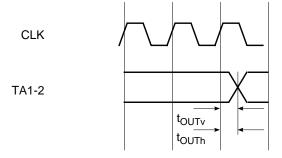

|      |        | 7.6.10  | MFT16 Timing                                                            | 399 |

| Tabl | e of C | Content | S (Continued)                                                   |     |

|------|--------|---------|-----------------------------------------------------------------|-----|

|      |        | 7.6.11  | ICU/Development Timing                                          | 400 |

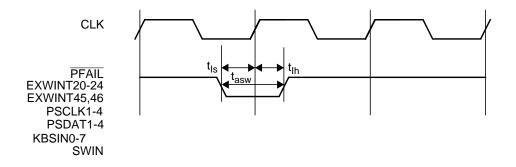

|      |        | 7.6.12  | Asynchronous Edge Detected Signals Timing                       | 401 |

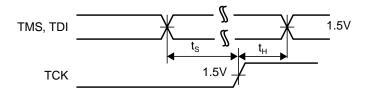

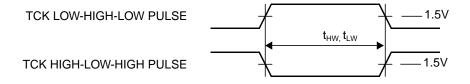

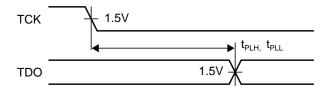

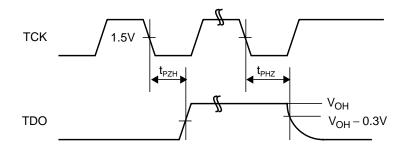

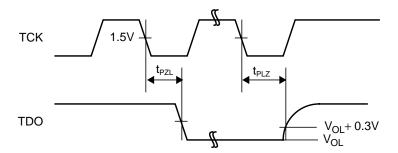

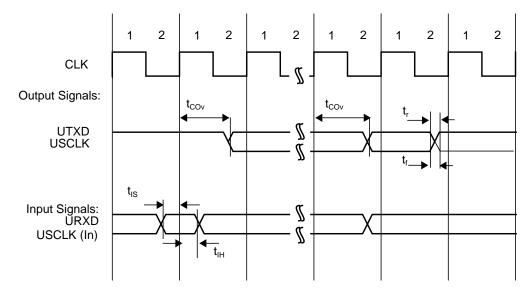

|      |        | 7.6.13  | Debugger Interface Timing                                       | 402 |

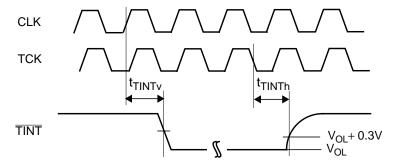

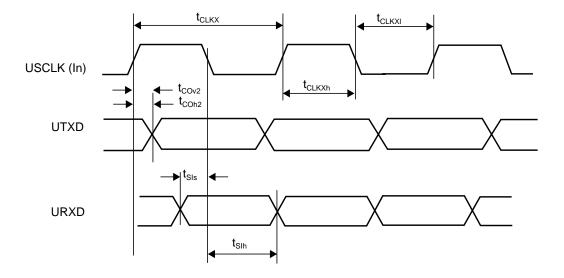

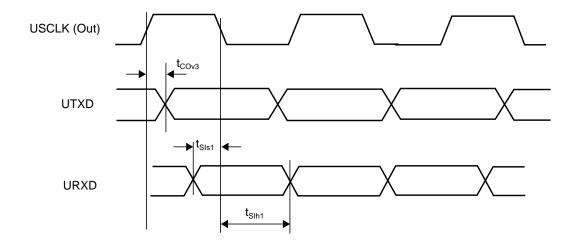

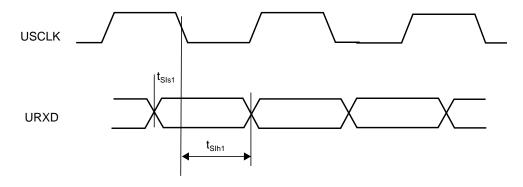

|      |        | 7.6.14  | USART Timing                                                    | 404 |

|      |        | 7.6.15  | LCLK and RESET1-2                                               | 406 |

|      |        | 7.6.16  | LPC and SERIRQ Signals                                          | 407 |

| A.   | Soft   | ware fo | r Hardware Interface                                            |     |

|      | A.1    | CORE I  | DOMAIN REGISTER LIST                                            | 408 |

|      |        | A.1.1   | Module Configuration                                            | 408 |

|      |        | A.1.2   | Bus Interface Unit (BIU)                                        | 408 |

|      |        | A.1.3   | DMA Controller                                                  | 408 |

|      |        | A.1.4   | General-Purpose I/O (GPIO) Ports                                | 409 |

|      |        | A.1.5   | PS/2 Ports                                                      | 411 |

|      |        | A.1.6   | Host Interface (KBC, PM1 and PM2Channels)                       | 411 |

|      |        | A.1.7   | Multi-Function Timer (MTF16) 1                                  | 412 |

|      |        | A.1.8   | Multi-Function Timer (MFT16) 2                                  | 412 |

|      |        | A.1.9   | Timing and WATCHDOG (TWD)                                       | 413 |

|      |        | A.1.10  | Analog to Digital Converter (ADC)                               | 413 |

|      |        | A.1.11  | Digital to Analog Converter (DAC)                               | 413 |

|      |        | A.1.12  | ACCESS.bus Interface (ACB) 1                                    | 414 |

|      |        | A.1.13  | ACCESS.bus Interface (ACB) 2                                    | 414 |

|      |        | A.1.14  | Analog Comparators Monitor (ACM)                                | 414 |

|      |        | A.1.15  | Power Management (PM)                                           | 415 |

|      |        | A.1.16  | High Frequency Clock Generator (HFCG)                           | 415 |

|      |        | A.1.17  | Development System Support                                      | 415 |

|      |        | A.1.18  | Multi-Input Wake-Up (MIWU)                                      | 415 |

|      |        | A.1.19  | Interrupt Control Unit (ICU)                                    | 416 |

|      |        | A.1.20  | Debugger Interface                                              | 416 |

|      |        | A.1.21  | Pulse Width Modulator (PWM)                                     | 417 |

|      |        | A.1.22  | Universal Synchronous/Asynchronous Receiver Transmitter (USART) | 417 |

|      |        | A.1.23  | Flash Interface                                                 | 418 |

|      |        | A.1.24  | Shared Memory Core                                              | 418 |

|      |        | A.1.25  | Core Access to SuperI/O                                         | 419 |

|      |        | A.1.26  | Mobile System Wake-Up Control (MSWC)                            | 419 |

|      | A.2    | HOST [  | DOMAIN REGISTER LIST                                            | 420 |

|      |        | A.2.1   | Configuration Registers                                         | 420 |

|      |        |         | Common SuperI/O Configuration                                   |     |

|      |        |         | Shared Memory                                                   |     |

|      |        | A.2.2   | RTC Configuration                                               |     |

|      |        | H.Z.Z   | Host Runtime Registers                                          |     |

|      |        |         | Shared Memory HostMSWC Host Registers                           |     |

|      |        |         | Host Interface (HI)                                             |     |

|      |        |         | Power Management Channel 1                                      |     |

|      |        |         |                                                                 |     |

#### Table of Contents (Continued) CORE DOMAIN REGISTER LAYOUT ......424 A.3 A.3.1 A.3.2 A.3.3 DMA Controller 424 General-Purpose I/O (GPIO) Port ......424 A.3.4 A.3.5 A.3.6 Core Interface 425 A.3.7 A.3.8 Timing and WATCHDOG (TWD) ......426 A.3.9 Analog to Digital Converter (ADC) .......426 Digital to Analog (DAC) .......427 A.3.10 A.3.11 Analog Comparators Monitor (ACM) ......427 A.3.12 Power Management (PM) .......427 A.3.13 High-Frequency Clock Generator (HFCG) ......427 A.3.14 A.3.15 Multi-Input Wake-Up (MIWU) ......427 A.3.16 A.3.17 A.3.18 Pulse with Modulator (PWM) .......429 A.3.19 A.3.20 Universal Synchronous/Asynchronous Receiver Transmitter (USART) ......429 A.3.21 A.3.22 Core Access to SuperI/O ......430 A.3.23 A.3.24 HOST DOMAIN REGISTER LAYOUT ......431 **A.4** Host Configuration Registers ......431 A.4.1 A.4.2 A.4.3 RTC Configuration .......431 Host Runtime Registers ......431 A.4.4 A.4.5 A.4.6 A.4.7 B. Software for Hardware Interface **B.1** FACTORY PARAMETERS 434 B.2

# 1.0 Introduction

#### 1.1 DOCUMENT ORGANIZATION

This document describes the PC87591x architecture and device specifications. It is organized as follows:

- Chapter 1, Introduction, provides an overview of PC87591x modules, system connections, operating modes and configuration.

- Chapter 2, Signal/Pin Description and Configuration, lists the PC87591x pins and describes their functions and multiplexing options.

- Chapter 3, Power, Reset and Clocks, describes the PC87591x power supplies, clock scheme and reset sequence.

- Chapter 4, Embedded Controller Modules, describes the modules that comprise the CompactRISC core peripherals.

- Chapter 5, Host Controller Interface Modules, describes the modules and functions that interface core operation with the host.

- Chapter 6, Host-Controlled Modules and Host Interface, defines the configuration and control functions.

- Chapter 7, Device Specifications, defines the AC, DC and analog characteristics of the PC87591x.

- Appendix A, Summary of Registers, provides a composite listing of all relevant data on core domain registers and summarizes the registers' layouts.

- Appendix B, This section includes directions for the software to handle some predetermined hardware interfaces and provides details of software-to-hardware interface conventions.

#### 1.2 GENERAL DESCRIPTION

The PC87591x is a highly integrated, embedded controller with an embedded RISC core and system functions. Targeted for a wide range of portable applications that use the Low Pin Count (LPC) interface, it also features a security system and host BIOS firmware.

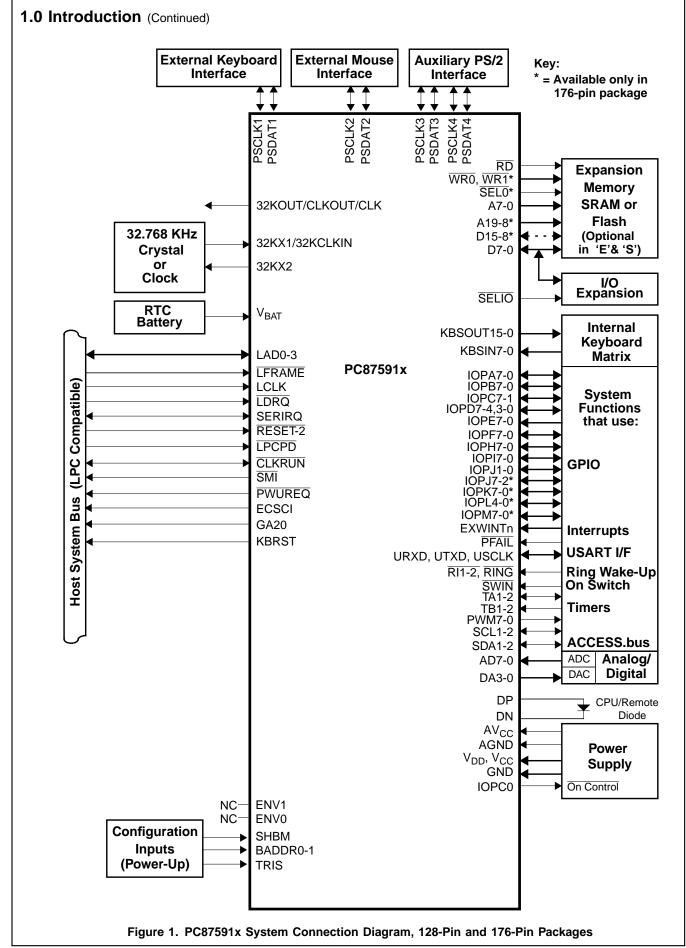

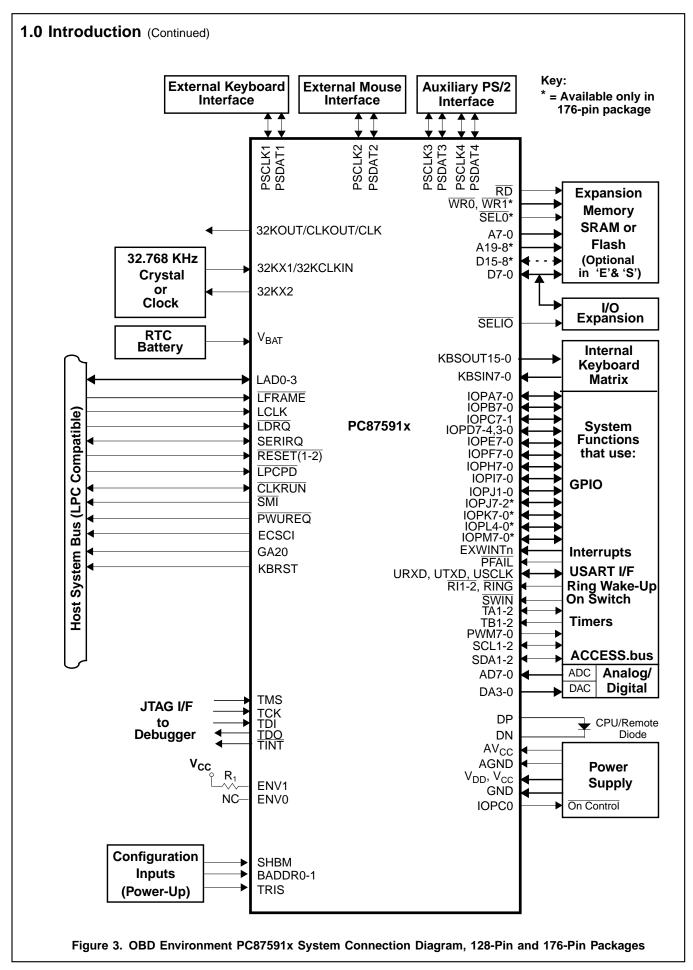

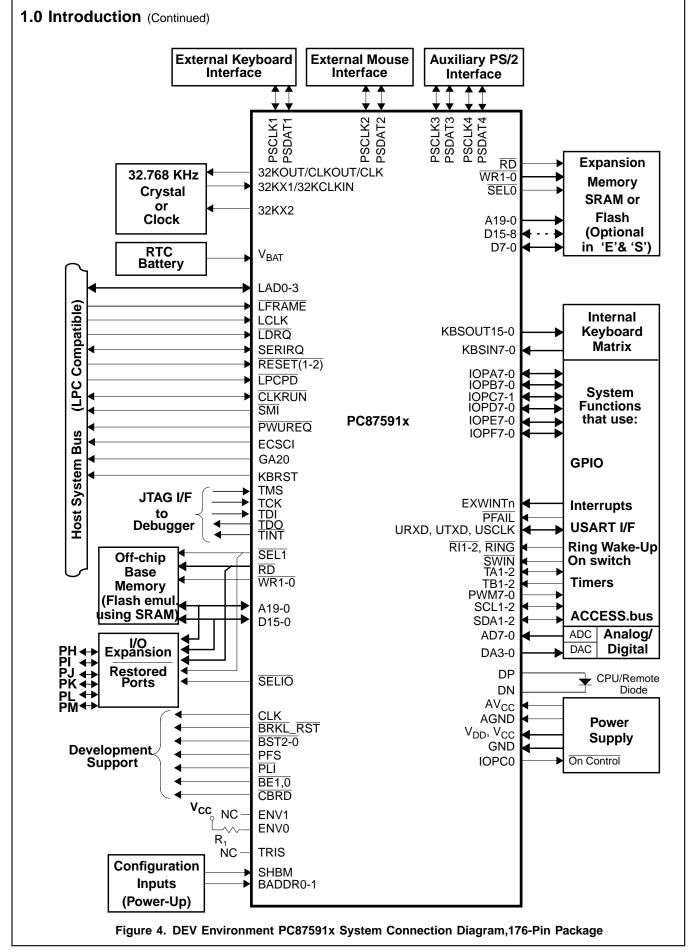

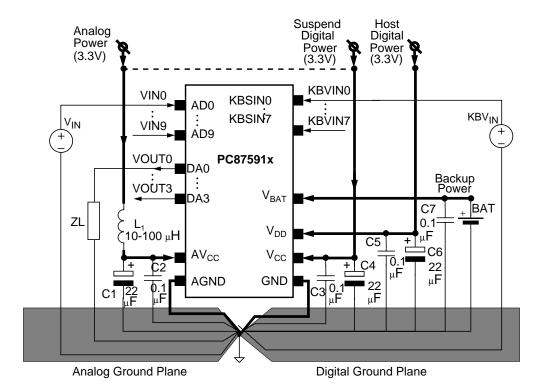

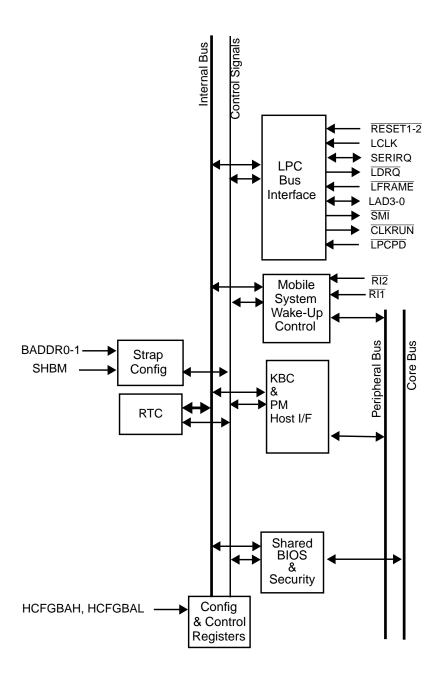

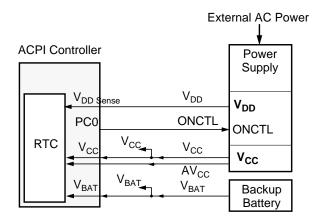

# 1.2.1 System Connections

Figure 1 shows the system connections of the PC87591x in a typical mobile PC application. The PC87591x requires little, if any, system glue elements. For a typical application, the PC87591x includes all required memory and peripherals on-chip. For more complex applications, it allows simple low-cost expansion, using its bus. Some of the features illustrated are mutually exclusive, depending on pin functions.

The major elements of the PC87591x are:

- Embedded Controller (EC) functions, which include: PS/2 devices, keyboard matrix, ACCESS.bus, timers, D/A and A/D converters and GPIO pins that can be assigned to various functions, as needed. External memory and peripheral devices may be added to extend the functionality of the on-chip resources.

- Host Processor interface based on the LPC bus and additional signals for interrupts and system power management

- Power Supplies for Host interface functions, EC and backup battery

- Clocks, using a 32.768 KHz crystal and optional clock output

- Strap inputs to initialize the PC87591x to different operation modes.

In addition to the wide range of internal peripherals, the PC87591x provides hooks so that the system can be expanded in an easy and cost-effective manner, as follows:

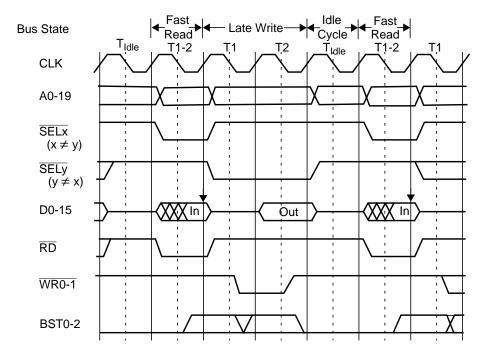

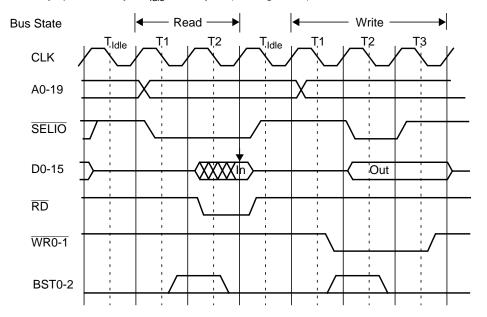

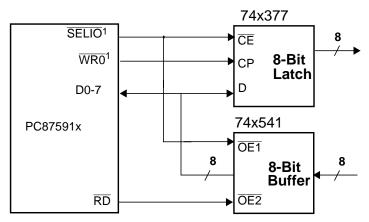

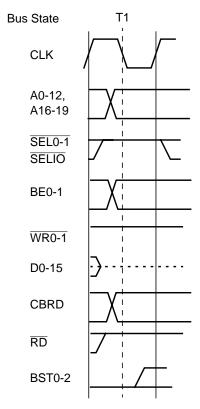

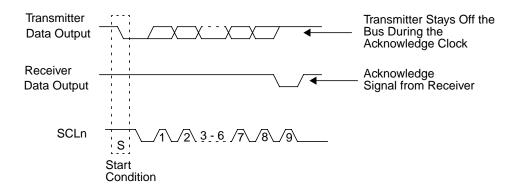

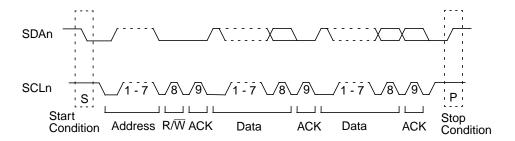

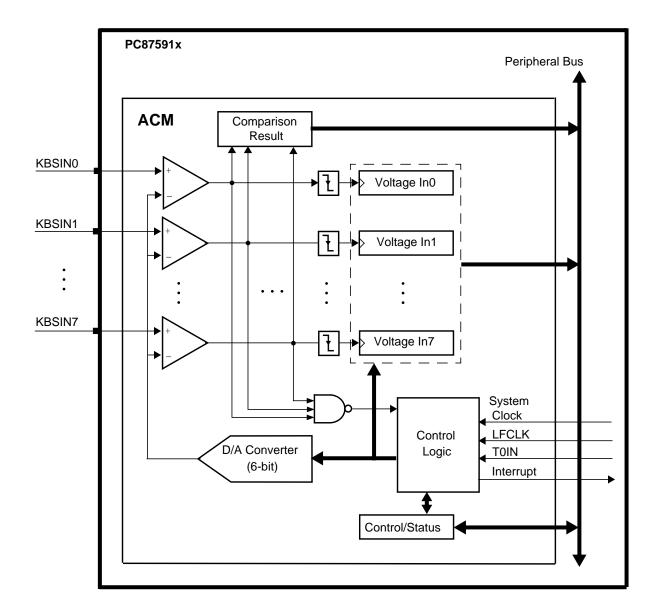

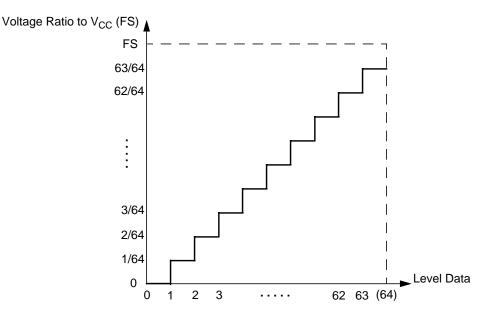

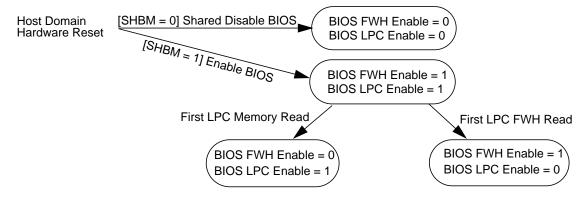

- I/O expansion to support additional I/O port pins, using low-cost, standard 74HCxx devices or ASICs