INTEGRATED CIRCUITS

Objective specification File under Integrated Circuits, IC17 1999 May 03

HILIP

### PCF50732

#### CONTENTS 14 LIMITING VALUES 15 THERMAL CHARACTERISTICS 1 **FEATURES** 16 DC CHARACTERISTICS 2 **APPLICATIONS** AC CHARACTERISTICS 17 3 GENERAL DESCRIPTION 18 FUNCTIONAL CHARACTERISTICS 4 ORDERING INFORMATION 18.1 Baseband transmit (BSI to TXI/Q) 5 QUICK REFERENCE DATA Baseband receive (RXI/Q to BSI) 18.2 6 **BLOCK DIAGRAM** 18.3 Voice band transmit (microphone to ASI) Voice band receive (ASI to earphone) 18.4 7 PINNING 18.5 Auxiliary digital-to-analog converters 8 FUNCTIONAL DESCRIPTION 18.6 Auxiliary analog-to-digital converters: 8.1 General AUXADC1, AUXADC2, AUXADC3 and Baseband and voice band reference voltages 8.2 AUXADC4 9 **BASEBAND CODEC** Typical total current consumption 18.7 18.8 Typical output loads 9.1 Baseband transmit path APPLICATION INFORMATION 9.2 Baseband receive path 19 Baseband Serial Interface (BSI) 9.3 19.1 Wake-up procedure from Sleep mode 10 VOICE BAND CODEC 19.2 Microphone input connection and test set-up 10.1 Voice band receive path 20 PACKAGE OUTLINES 10.2 Voice band transmit path 21 SOLDERING 10.3 Voice band digital circuitry 21.1 Introduction to soldering surface mount 11 AUXILIARY FUNCTIONS packages 11.1 Automatic Gain Control (AGC): AUXDAC1 21.2 Reflow soldering 21.3 11.2 Automatic Frequency Control (AFC): Wave soldering 21.4 AUXDAC2 Manual soldering 11.3 Power ramping: AUXDAC3 21.5 Suitability of surface mount IC packages for Auxiliary analog-to-digital converter (AUXADC) 11.4 wave and reflow soldering methods 12 22 CONTROL SERIAL INTERFACE (CSI) DEFINITIONS 12.1 The serial interface 23 LIFE SUPPORT APPLICATIONS 12.2 Control Serial Interface (CSI) timing characteristics 12.3 Control register block 13 VOICE BAND SIGNAL PROCESSOR (VSP)

13.1 Hardware description

- 13.2 VSP assembler language

- 13.3 Descriptions of the VSP instruction set

- 13.4 The assembler/emulator

### PCF50732

### **1 FEATURES**

- Low power and low voltage device in 0.25 micron CMOS technology; supply voltage: analog 2.7 V (typical) and digital 1.5 V (typical)

- Compatible with GSM phase 2 and DCS1800 recommendations

- Complete in-phase and quadrature component interface paths between the Digital Signal Processor (DSP) and RF circuitry

- Complete linear PCM CODEC for audio signal conversion between earphone/microphone and DSP

- Four auxiliary analog inputs for measurement purposes (e.g. battery monitoring)

- Three auxiliary analog outputs for control purposes (i.e. AFC, AGC and power ramping control)

- · Separate baseband, audio and control serial interfaces

- Voice band Signal Processor (VSP) for flexible audio data processing.

### 2 APPLICATIONS

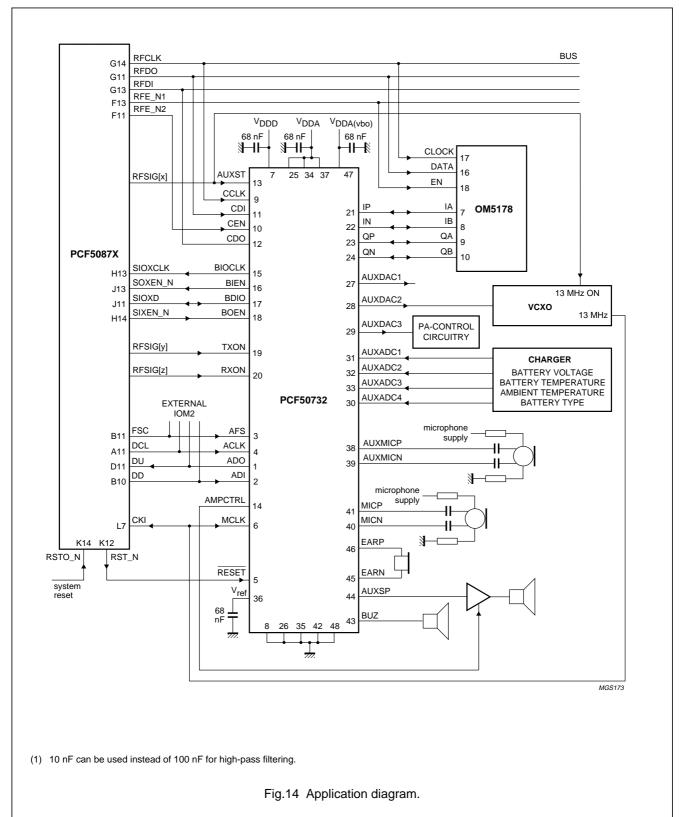

The CMOS integrated circuit PCF50732, Baseband and audio interface for GSM, is dedicated to wireless telephone handsets conforming to the GSM recommendations phases 1 and 2, DCS1800 and PCS1900.

### **3 GENERAL DESCRIPTION**

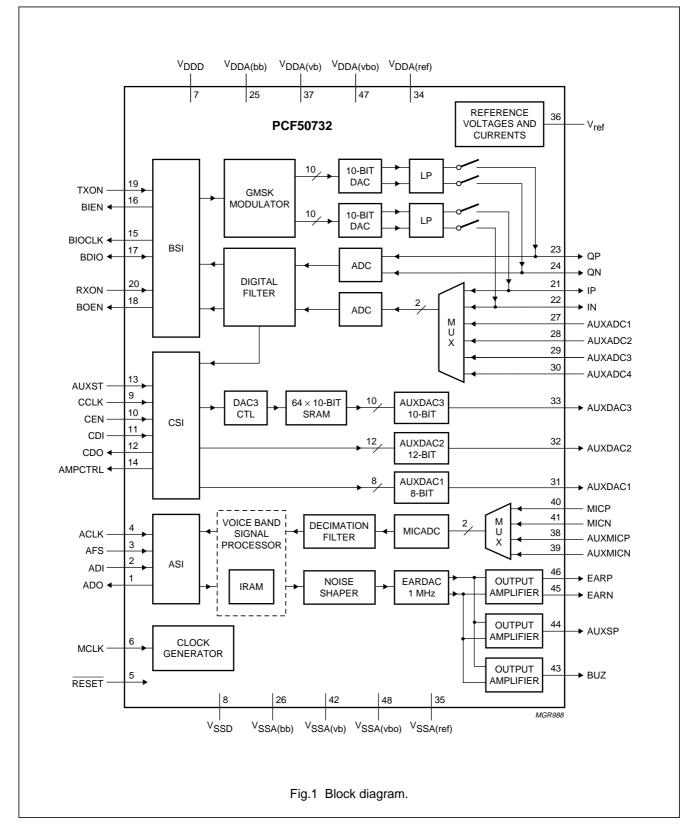

The baseband CODEC is a complete interface circuit between the RF part in a mobile communication handset and the Digital Signal Processor (DSP). It consists of three parts:

- The **receive path**, which transforms the quadrature signals from the RF (I/Q) to digital signals

- The **transmit path**, which transforms a bitstream to analog quadrature signals for the RF devices

# • The digital **Baseband Serial Interface (BSI)**, which exchanges baseband data between the PCF50732 and the digital signal processor. The interface also includes signals to power-up and power-down the baseband transmit (TX) and receive (RX) paths.

The voice band CODEC is a complete analog front-end circuit. It consists of four parts:

- The **receive path**, which converts a digital signal to an analog signal for an earpiece, an external loudspeaker or a buzzer

- The **transmit path**, which receives the analog external signal from a microphone and converts it into a digital signal

- The Voice band Signal Processor (VSP), which filters the voice band data

- The digital Audio Serial Interface (ASI), which connects the digital linear PCM signals of the receive and transmit paths to an external DSP. The voice band data is coded in 16-bit linear PCM twos complement words.

The **auxiliary Analog-to-Digital Converter (ADC)** section consists of four input channels specified for battery management applications.

The **auxiliary Digital-to-Analog Converter (DAC)** section consists of three DACs for Automatic Gain Control (AGC), for Automatic Frequency Control (AFC) and for power ramping.

The **Control Serial Interface (CSI)** is used to program a set of control registers, to store the power amplifier ramping characteristics into the dedicated RAM and to transmit auxiliary ADC values to the DSP. It also controls switches, modes and power status of the different parts of the IC.

### 4 ORDERING INFORMATION

|             |             | PACKAGE                                                                          |          |

|-------------|-------------|----------------------------------------------------------------------------------|----------|

| ITPE NOWBER | DESCRIPTION | VERSION                                                                          |          |

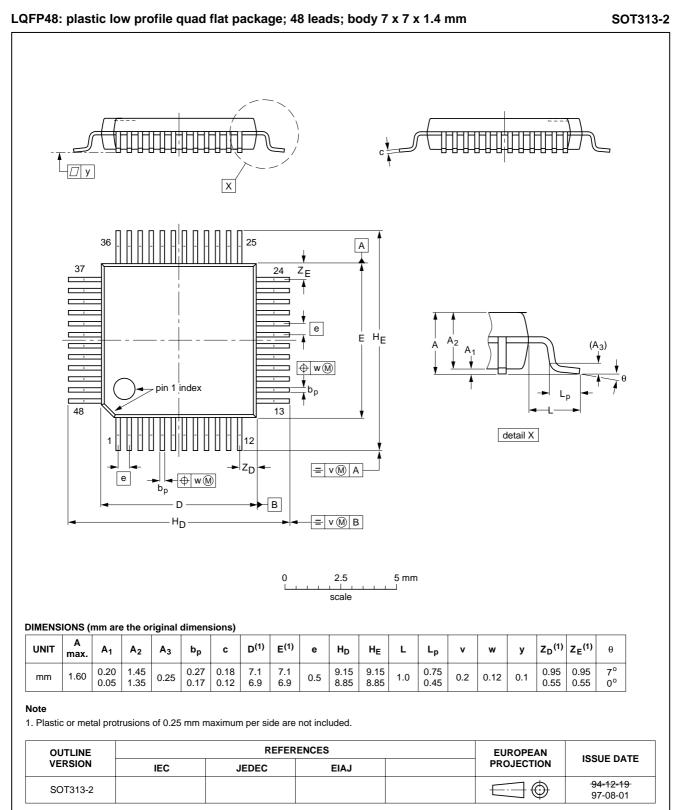

| PCF50732H   | LQFP48      | plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm | SOT313-2 |

### PCF50732

### 5 QUICK REFERENCE DATA

| SYMBOL                | PARAMETER                     | CONDITIONS                                                         | MIN. | TYP. | MAX. | UNIT |

|-----------------------|-------------------------------|--------------------------------------------------------------------|------|------|------|------|

| V <sub>DDD</sub>      | digital supply voltage        |                                                                    | 1.0  | 1.5  | 2.75 | V    |

| V <sub>DDA</sub>      | analog supply voltage         | $V_{DDA} \ge V_{DDD}$                                              | 2.5  | 2.7  | 2.75 | V    |

| I <sub>DDA</sub>      | analog supply current         | V <sub>DDD</sub> = 1.5 V; V <sub>DDA</sub> = 2.7 V;<br>RXON active | -    | 3.5  | -    | mA   |

| Pav                   | average power consumption     | V <sub>DDD</sub> = 1.5 V; V <sub>DDA</sub> = 2.7 V; note 1         | -    | 15   | -    | mW   |

| I <sub>stb(tot)</sub> | total standby current         |                                                                    | -    | 10   | -    | μA   |

| f <sub>clk</sub>      | master clock frequency        |                                                                    | -    | 13.0 | -    | MHz  |

| T <sub>amb</sub>      | operating ambient temperature |                                                                    | -40  | +27  | +85  | °C   |

Note

1. Without load on audio outputs EARP, EARN, AUXSP and BUZ.

### PCF50732

### 6 BLOCK DIAGRAM

# PCF50732

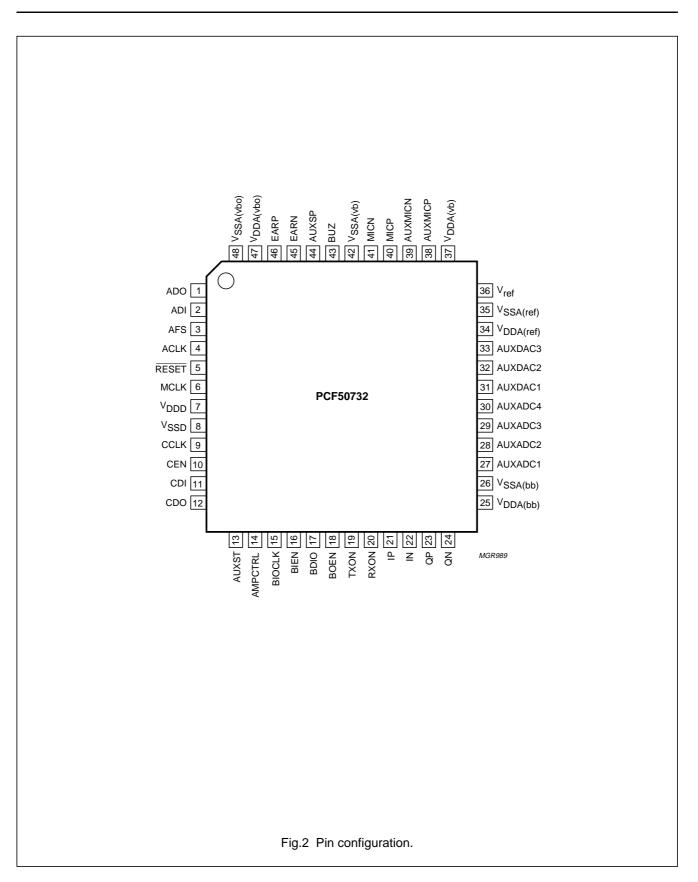

### 7 PINNING

|                      |     |                     | PIN             |                |                 |                                                                                  |  |

|----------------------|-----|---------------------|-----------------|----------------|-----------------|----------------------------------------------------------------------------------|--|

| SYMBOL               | NR. | TYPE <sup>(1)</sup> | ACTIVE<br>LEVEL | ACTIVE<br>EDGE | I <sub>DD</sub> | DESCRIPTION                                                                      |  |

| ADO                  | 1   | O/TS                | _               | _              | 1.5 mA          | audio digital interface PCM data output to DSP                                   |  |

| ADI                  | 2   | I                   | _               | _              | _               | audio digital interface PCM data input from DSP                                  |  |

| AFS                  | 3   | I                   | _               | rising         | _               | audio digital interface PCM frame synchronization signal from DSP                |  |

| ACLK                 | 4   | I                   | -               | rising         | _               | audio digital interface PCM clock signal from DSP                                |  |

| RESET                | 5   | I                   | LOW             | -              | _               | asynchronous reset input                                                         |  |

| MCLK                 | 6   | I                   | _               | rising         | _               | low-swing master clock input; $f_{clk} = 13$ MHz; integrated capacitive coupling |  |

| V <sub>DDD</sub>     | 7   | Р                   | _               | -              | _               | digital power supply                                                             |  |

| V <sub>SSD</sub>     | 8   | G                   | _               | _              | _               | digital ground                                                                   |  |

| CCLK                 | 9   | I                   | _               | falling        | _               | control bus clock input from DSP                                                 |  |

| CEN                  | 10  | I                   | LOW             | _              | _               | control bus data enable from DSP                                                 |  |

| CDI                  | 11  | I                   | _               | _              | _               | control bus data input from DSP                                                  |  |

| CDO                  | 12  | O/TS                | _               | _              | 1.5 mA          | control bus data output to DSP                                                   |  |

| AUXST                | 13  | I                   | HIGH            | -              | _               | status control signal for activation of AUXDAC1,<br>AUXDAC2 and MCLK input       |  |

| AMPCTRL              | 14  | 0                   | _               | _              | 1.5 mA          | general purpose output pin                                                       |  |

| BIOCLK               | 15  | O/TS                | _               | _              | 3 mA            | baseband interface data clock                                                    |  |

| BIEN                 | 16  | 0                   | LOW             | _              | 1.5 mA          | baseband transmit interface data enable signal                                   |  |

| BDIO                 | 17  | I/O                 | _               | _              | 1.5 mA          | baseband interface data I/O from/to DSP                                          |  |

| BOEN                 | 18  | 0                   | LOW             | _              | 1.5 mA          | baseband receive interface data enable signal                                    |  |

| TXON                 | 19  | I                   | HIGH            | _              | _               | baseband transmit path activation signal                                         |  |

| RXON                 | 20  | I                   | HIGH            | _              | _               | baseband receive path activation signal                                          |  |

| IP                   | 21  | I/O                 | _               | _              | _               | (I) baseband differential positive input/output to IF circuit                    |  |

| IN                   | 22  | I/O                 | _               | -              | _               | (I) baseband differential negative input/output to IF circuit                    |  |

| QP                   | 23  | I/O                 | _               | -              | _               | (Q) baseband differential positive input/output to IF circuit                    |  |

| QN                   | 24  | I/O                 | _               | -              | _               | (Q) baseband differential negative input/output to IF circuit                    |  |

| V <sub>DDA(bb)</sub> | 25  | Р                   | _               | _              | _               | baseband power supply (analog)                                                   |  |

| V <sub>SSA(bb)</sub> | 26  | G                   | _               | _              | _               | baseband ground (analog)                                                         |  |

| AUXADC1              | 27  | I                   | _               | _              | _               | auxiliary ADC input 1 for battery voltage measurement                            |  |

| AUXADC2              | 28  | I                   | _               | -              | _               | auxiliary ADC input 2                                                            |  |

| AUXADC3              | 29  | I                   | _               | _              | _               | auxiliary ADC input 3                                                            |  |

| AUXADC4              | 30  | I                   | _               | -              | _               | auxiliary ADC input 4                                                            |  |

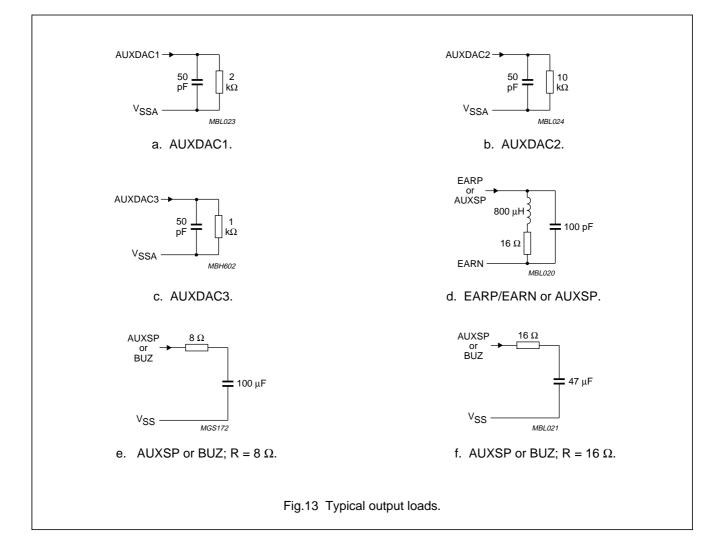

| AUXDAC1              | 31  | 0                   | _               | -              | _               | auxiliary DAC output for AGC; max. load 50 pF // 2 k $\Omega$                    |  |

| AUXDAC2              | 32  | 0                   | _               | _              | _               | auxiliary DAC output for AFC; max. load 50 pF // 10 k $\Omega$                   |  |

# PCF50732

|                       |     |                     | PIN             |                |                 |                                                                             |

|-----------------------|-----|---------------------|-----------------|----------------|-----------------|-----------------------------------------------------------------------------|

| SYMBOL                | NR. | TYPE <sup>(1)</sup> | ACTIVE<br>LEVEL | ACTIVE<br>EDGE | I <sub>DD</sub> | DESCRIPTION                                                                 |

| AUXDAC3               | 33  | 0                   | -               | -              | _               | auxiliary DAC output for power ramping; maximum load 50 pF, $\pm 600~\mu A$ |

| V <sub>DDA(ref)</sub> | 34  | Р                   | _               | _              | _               | reference voltage power supply (analog)                                     |

| V <sub>SSA(ref)</sub> | 35  | G                   | _               | -              | _               | reference voltage ground (analog)                                           |

| V <sub>ref</sub>      | 36  | I/O                 | _               | _              | _               | band gap reference voltage noise decoupling                                 |

| V <sub>DDA(vb)</sub>  | 37  | Р                   | _               | _              | _               | voice band voltage power supply                                             |

| AUXMICP               | 38  | I                   | _               | _              | _               | auxiliary microphone differential positive input                            |

| AUXMICN               | 39  | I                   | _               | _              | _               | auxiliary microphone differential negative input                            |

| MICP                  | 40  | I                   | _               | _              | _               | microphone differential positive input                                      |

| MICN                  | 41  | I                   | _               | _              | _               | microphone differential negative input                                      |

| V <sub>SSA(vb)</sub>  | 42  | G                   | _               | _              | _               | voice band ground                                                           |

| BUZ                   | 43  | 0                   | _               | _              | _               | buzzer output                                                               |

| AUXSP                 | 44  | 0                   | _               | _              | _               | auxiliary speaker output                                                    |

| EARN                  | 45  | 0                   | _               | _              | _               | earphone differential negative output                                       |

| EARP                  | 46  | 0                   | _               | _              | _               | earphone differential positive output                                       |

| V <sub>DDA(vbo)</sub> | 47  | Р                   | _               | _              | _               | voice band output buffer voltage power supply (analog)                      |

| V <sub>SSA(vbo)</sub> | 48  | G                   | _               | _              | _               | voice band output buffer ground (analog)                                    |

#### Note

1. O/TS = 3-state output.

PCF50732

### Baseband and audio interface for GSM

### 8 FUNCTIONAL DESCRIPTION

This chapter gives a brief overview of the device. The detailed functional description can be found in the following chapters:

Chapter 9 "Baseband CODEC"

Chapter 10 "Voice band CODEC"

Chapter 11 "Auxiliary functions"

Chapter 12 "Control Serial Interface (CSI)"

Chapter 13 "Voice band Signal Processor (VSP)".

#### 8.1 General

As low power consumption in mobile telephones is a very important issue, all the circuit parts in the PCF50732 can be powered-on/off either by means of the external signals AUXST, TXON or RXON, or by programming the respective register bits in the Control Serial Interface (CSI).

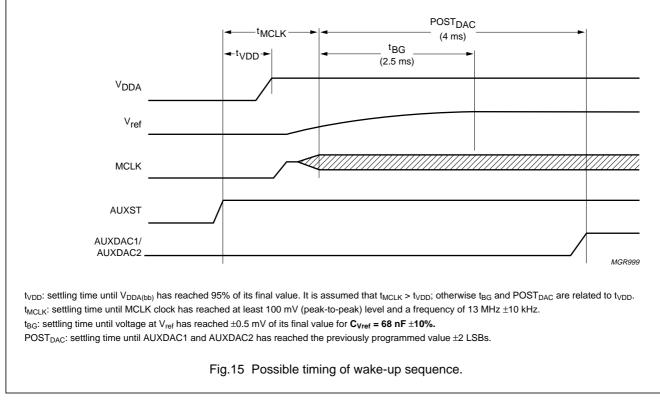

The most important signal for the digital and analog circuit functions in the PCF50732 is the DAC enable signal AUXST, which allows to activate AUXDAC1 (AGC) and AUXDAC2 (AFC), as well as the low-swing master clock input MCLK. AUXST must be active (HIGH) and  $V_{DDA}$  must be stable (see also Section 18.1) to allow the master clock to access different circuit parts after a reset (RESET active). AUXDAC1 and AUXDAC2 are only activated if their related power-on bit is set. AUXDAC1 is default off, AUXDAC2 is default on.

RESET must be active during at least 3 MCLK cycles, with AUXST active, to ensure a correct initialisation of all the digital circuitry of the PCF50732. Since RESET is asynchronous even small spikes of a few nanoseconds can cause partial resets.

For power supply noise interference reduction, a pair of power supply and ground pins are provided for the:

- Baseband analog: V<sub>DDA(bb)</sub>/V<sub>SSA(bb)</sub>

- Voice band analog: V<sub>DDA(vb)</sub>/V<sub>SSA(vb)</sub>

- Voice band output drivers: V<sub>DDA(vbo)</sub>/V<sub>SSA(vbo)</sub>

- DC reference voltages and currents: V<sub>DDA(ref)</sub>/V<sub>SSA(ref)</sub>

- Digital circuitry: V<sub>DDD</sub>/V<sub>SSD</sub>.

All V<sub>SS</sub> pins are connected internally. V<sub>DDD</sub> is the digital supply. V<sub>DDA(bb)</sub>, V<sub>DDA(vb)</sub>, V<sub>DDA(vbo)</sub>, and V<sub>DDA(ref)</sub> are analog supplies, and are referred to as V<sub>DDA</sub> throughout this document. These analog supplies must be connected externally.

#### 8.2 Baseband and voice band reference voltages

The reference voltage  $V_{ref}$  is generated on-chip by a band gap voltage reference circuit and is available at pin  $V_{ref}$ .

As  $V_{ref}$  is used as reference for most of the internal analog circuitry, noise must be kept as low as possible by connecting an external decoupling capacitor at this pin.

The voltage at V<sub>ref</sub> is buffered to generate the baseband and voice band reference voltage V<sub>ref</sub> as well as internal references for the different functions, such as the auxiliary and the transmit DACs.

### 9 BASEBAND CODEC

The baseband CODEC is a complete interface circuit between the RF part in a mobile communication handset and the digital signal processor. It consists of three parts:

- The **transmit path**, which converts a bitstream to analog quadrature signals for the RF devices

- The **receive path**, which transforms the quadrature signals of the IF chip (I/Q) to digital signals

- The digital **baseband serial interface**, which exchanges baseband data between the PCF50732 and the DSP. The interface also includes signals to power-up and power-down the baseband transmit (TX) and receive (RX) paths.

#### 9.1 Baseband transmit path

The baseband transmit path consists of three parts:

- **GMSK modulator:** generation of a Gaussian Minimum Shift Keying (GMSK) signal

- **10-bit DACs:** digital-to-analog converters for the I and Q components of the GMSK signal

- Low-pass filters: analog reconstruction low-pass filters for the output of the DACs.

The requirements of the transmit path of a GSM terminal are given by *"GSM recommendation 05.05"*:

- Phase RMS error <5°

- Phase peak error <20°</li>

- Amplitude error  $< \pm 1$  dB.

Nevertheless the performance of the PCF50732 is far better than these figures indicate; see Section 18.1.

### PCF50732

### PCF50732

### 9.1.1 GMSK MODULATOR

The input signal of the GMSK modulator is a bitstream coming from the baseband serial interface, with a sampling frequency of 270.833 kHz. Typically 148 bits are modulated during a normal burst, and 88 bits during an access burst. Using this bitstream, the GMSK modulator generates digital I and Q components as described in *"GSM recommendation 05.04"*.

This is done in three steps:

- First the incoming bitstream is differentially encoded by an EXOR operation on the actual bit and the previous bit

- 2. The instantaneous phase  $(\phi)$  is calculated using a gaussian filter with an impulse response of 4 taps

- 3. A look-up table provides the cosine (I component) and the sine values (Q component) of the phase ( $\phi$ ).

The look-up table also interpolates the signal to a 16 times higher frequency (4.333 MHz).

### 9.1.2 10-віт DACs

The two 10-bit DACs are working at a sampling rate of 4.3333 MHz. They convert the digital I and Q components of the GMSK modulator to differential analog I and Q signals.

#### 9.1.3 LOW-PASS FILTER

The analog output signals of the DACs are filtered by analog reconstruction low-pass filters.

These filters remove high frequency components of the DAC output signals and attenuate components around the 4.3333 MHz sampling frequency. The low-pass filters have a cut-off frequency of approximately 300 kHz, with very linear phase behaviour in the pass band.

### 9.2 Baseband receive path

The baseband receive path consists of two parts:

- Receive ADC: ΣΔ analog-to-digital converters

- Decimation filter: digital decimation filters for I and Q.

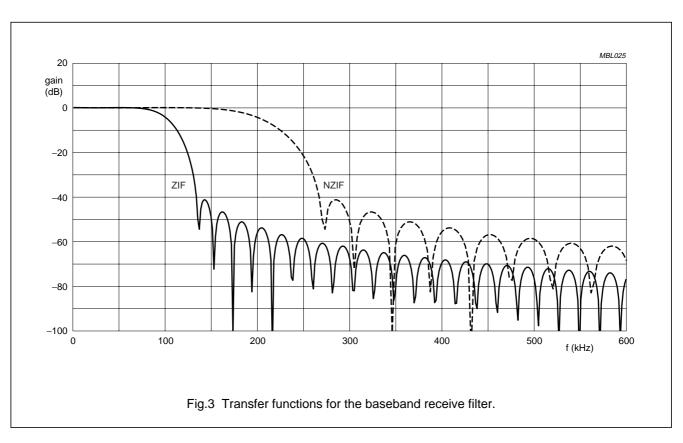

The baseband receive section can be switched between two modes of operation:

- ZIF (zero IF) mode for radio sections, which convert the receive signal down to baseband. In this mode the ADC is sampled at 6.5 MHz, the decimation filter samples down by a factor of 24 with a pass band as specified in Fig.3. The serial interface output BDIO delivers 2 × 12-bit values for I and Q components at 270.833 kHz.

- NZIF (near zero IF) mode for radio sections, which converts the receive signal down to a centre frequency of 100 kHz. In this mode the ADC is sampled at 13 MHz, the decimation filter samples down by a factor of 24 with a pass band as specified in Fig.3. The serial interface output BDIO delivers 2 × 12-bit values for I and Q components at 541.667 kHz.

### 9.2.1 RECEIVE ADC

The receive ADCs are  $\Sigma\Delta$  analog-to-digital converters that convert differential input signals into1-bit data streams with a sampling frequency of 6.5 or 13 MHz.

#### 9.2.2 DIGITAL DECIMATION FILTER

Digital filtering is required for:

- Suppression of out-of-band noise produced by the  $\Sigma\Delta$  ADC

- Decimation of the sampling rate (6.5 or 13 MHz) by 24

- System level filtering.

The digital filtering is performed by a digital FIR filter with a group delay for this running average filter of approximately 23 or 11.5  $\mu$ s respectively. The filter uses twos complement arithmetic.

### 9.3 Baseband Serial Interface (BSI)

#### 9.3.1 OVERVIEW

The digital part of the baseband consists of a receive section and a transmit section. The receive section is a FIR filter that reduces the 6.5 MHz (13 MHz for NZIF mode) bitstream from the sigma-delta converters into  $2 \times 12$ -bit values at 270.833 kHz (541.667 kHz for NZIF mode).

The transmit section converts the 270.833 kHz data stream from the DSP into a GMSK signal sampled at 4.333 MHz. The 10-bit I and Q signals are then fed into two 10-bit DACs. The power ramping signal is also generated by the transmit section with the 10-bit AUXDAC3 block.

### 9.3.2 TRANSMIT PATH BLOCK DESCRIPTION

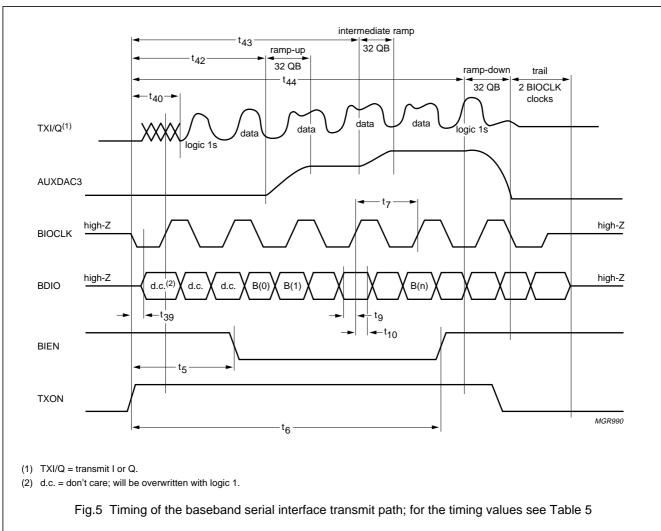

#### 9.3.2.1 Transmit serial interface

The power-up of the BSI transmit path is controlled via the TXON pin. When TXON is pulled HIGH, the transmit path recovers from power-down. The MCLK/48 = 270.833 kHz output signal BIOCLK is activated. When the BIEN0 period has elapsed the output signal BIEN goes LOW and the bits to be transmitted are clocked out of the DSP.

BIEN0 must be at least 10 quarterbits long to allow settling of the analog filters. Bits are clocked out of the DSP by the falling edge and clocked into the PCF50732 by the rising edge of BIOCLK. After the BIEN1 period has elapsed, BIEN is set HIGH again and transmission from the DSP ends. Logic 1s are modulated whenever BIEN is HIGH and the baseband transmit (BBTX) block is active. Values for BIEN0 and BIEN1 can be set in the Burst control register.

Figure 5 shows the timing for the BSI data transmission. In power-down the de-asserted value of BIOCLK is high-Z and BIEN is HIGH. Typical connection to the system DSP is defined in Table 1.

| Table 1 | Connection of BSI transmit signals to |

|---------|---------------------------------------|

|         | PCF5087X                              |

| PCF5   | 0732 | PCF5087X |     |  |

|--------|------|----------|-----|--|

| PIN    | I/O  | PIN      | I/O |  |

| TXON   | I    | RFSIG[y] | 0   |  |

| BDIO   | I/O  | SIOXD    | I/O |  |

| BIEN   | 0    | SOXEN_N  | I   |  |

| BIOCLK | 0    | SIOXCLK  | I   |  |

### PCF50732

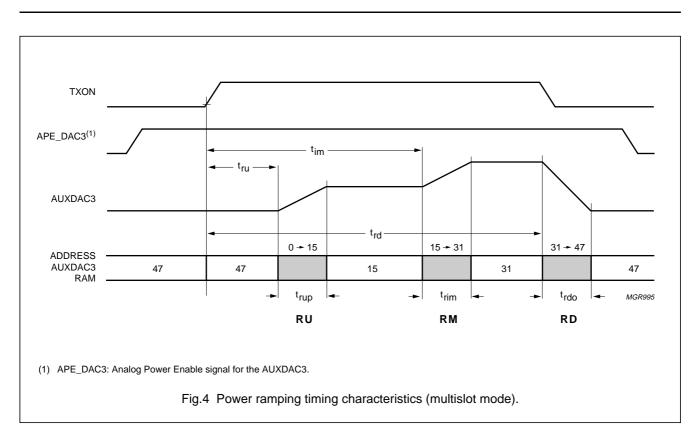

#### 9.3.2.2 Power ramping controller

The PCF50732 fully supports all multislot modes which do not require full duplex operation or more than two consecutive transmit bursts. In this specification double burst mode is used for all supported multislot modes while single burst mode supports the normal GSM modes.

The power ramping controller drives the power amplifier output envelope.

In each transmit (TX) burst one ramp-up and one ramp-down will be carried out. In multislot mode one intermediate ramp will be carried out in addition to ramp-up and ramp-down. Each ramp consists of 16 discrete step values that are sent to the DAC3. Each step's duration is 2 quarterbits which translates into 8-bit long ramps. The DAC3 output is in 3-state whenever it is powered down. The ramping step values are stored in a  $64 \times 10$ -bit RAM as shown in Table 2.

In order to initialize AUXDAC3 it is necessary to write into the RAM all 32 (or 48 in multislot mode) DAC3 output values. Filling the RAM is normally done by writing a logic 0 to the address sub-register of the Burst control register, after which 32 or 48 values, depending on multislot mode, can be written into the data sub-register of the Burst control register. Writing to the DAC3 RAM is only possible when the DAC3 is powered off.

Total number of CSI-accesses is therefore 33 for a normal burst and 49 for a double burst.

An autoincrement feature will store these data into the correct RAM positions.

The value after power-up of DAC3 will always be equal to the value of RAM location 47.

AUXDAC3 timing is controlled by the Burst control register. This contains the following sub-registers:

- The **RU register** containing the delay in number of quarterbit cycles from the assertion of TXON to the start of the power-up ramping; default value is 0

- The **RM register** containing the delay in number of quarterbit cycles from the assertion of TXON to the start of the intermediate power ramp; default value is 0. RM is only used in case of multislot mode

- The **RD register** containing the delay in number of quarterbit cycles from the assertion of TXON to the start of the power-down ramping; default value is 0

- DAC3 burst RAM address register

- DAC3 burst RAM data register

- Single/double burst mode register: normal mode or multislot mode selection flag.

After TXON goes HIGH and a time equal to RU quarterbit periods has elapsed, power ramp-up is done.

After a time period equal to RD quarterbits has elapsed power ramp-down is initiated.

The AUXDAC3 output is also shown in Fig.4.

Values for RU (ramp-up) and RD (ramp-down) can be set in the Burst control register of the control serial interface. RD must be greater than RU + 32. RU and RD range from 0 to 4000 QB (quarterbit). The register offers the possibility to enter codes up to 4095.

The GMSK modulator is active for a period of 2 clock cycles after the ramp-down or for the length of the TXON burst, whichever is longer.

Multislot (high speed switched data mode) can be selected by setting the appropriate bit in the Burst control register. In multislot mode an intermediate ramping step is done. This intermediate step is started after a time period equal to RM quarterbits has elapsed. A value for RM (intermediate ramp) is also set using the Burst control register. The following conditions must be true:

RU + 32 < RM and RM + 32 < RD.

#### Table 2 AUXDAC3 RAM contents

| RAM ADDRESS | DATA                   |  |

|-------------|------------------------|--|

| 0 to 15     | ramp-up data           |  |

| 16 to 31    | intermediate ramp data |  |

| 32 to 47    | ramp-down data         |  |

| 48 to 64    | not used               |  |

| Table 3 | Power | ramping | timing | characteristics |

|---------|-------|---------|--------|-----------------|

|         |       |         |        |                 |

| SYMBOL                                                 | VALUE            | COMMENTS <sup>(1)</sup> |

|--------------------------------------------------------|------------------|-------------------------|

| t <sub>0</sub>                                         | 12t <sub>1</sub> | one quarterbit (QB)     |

| t <sub>ru</sub>                                        | RU register      | 0 to 4000 QB            |

| t <sub>im</sub>                                        | RM register      | RU + 32 to 4000 QB      |

| t <sub>rd</sub>                                        | RD register      | RM + 32 to 4000 QB      |

| t <sub>rup</sub> , t <sub>rim</sub> , t <sub>rdo</sub> | 32t <sub>0</sub> | 8 bits; 32 QB           |

#### Note

1. QB: Quarterbit, usually referred to the time needed for one quarter of a GSM baseband bit, i.e. a frequency of  $\frac{1}{12} \times 13$  MHz.

#### 9.3.3 RECEIVER PATH BLOCK DESCRIPTION

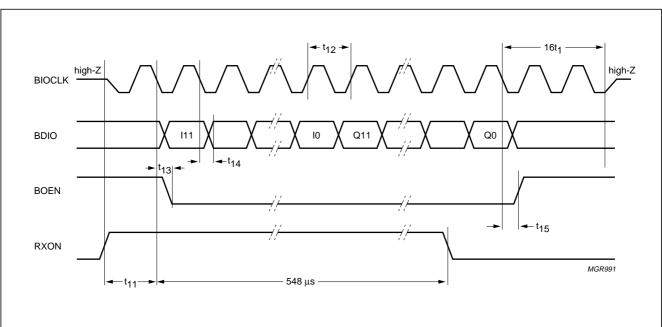

### 9.3.3.1 Receive serial interface

The baseband serial interface sends the digital signal of the receive path to a digital signal processor. It also takes the digital bitstream from the digital signal processor and transmits it via the baseband CODEC.

The baseband reception and transmission are active in bursts. A normal burst has a length of 548  $\mu$ s. The frame rate of bursts is 4.615 ms. Using a normal traffic channel, one burst for each frame is transmitted and two bursts are received. To save as much power as possible, the transmit path and the receive path of the PCF50732 are in power-up mode only during the transmission or reception bursts respectively.

The power-up of the receive section is controlled via the RXON pin or RXON bit. When RXON is driven HIGH, the receive section recovers from power-down and the output clock BIOCLK is activated. After a settling delay of 52  $\mu s$  (ZIF mode, analog circuitry + decimation filter settling time), BOEN goes LOW to transfer the first 12-bit I and Q words. The settling time is only 26  $\mu s$  in NZIF mode.

Bits are clocked out of the PCF50732 by the falling edge, and clocked into the DSP by the rising edge of BIOCLK. In normal bursts 148 I/Q pairs are read from the PCF50732.

When RXON goes LOW, the last pair of I and Q values will be sampled and transferred to the baseband processor (both I and Q components). BIOCLK stops after additional 16 BIOCLK cycles. The receive path is powered down again. In power-down the BIOCLK output is put in 3-state and the BOEN output is HIGH.

The output format is  $2 \times 12$ -bit I/Q (twos complement). Transmission occurs MSB first, I followed by Q. The serial clock signal BIOCLK will run at 6.5 MHz, or 13 MHz in the NZIF mode. Figure 6 shows the timing of the BSI data reception.

An automatic offset compensation mechanism is provided in order to achieve the required performance. This mechanism will short the receive (RX) inputs internally and measure the resulting offset value. This offset value will be subtracted from all subsequent I/Q output words. The offset inherent to the device can thereby be reduced to a few millivolts. Default value for both I- and Q-offset is zero.

PCF50732

### PCF50732

Offset compensation measurement can be done on three channels separately: baseband receive I channel, baseband receive Q channel and AUXADC channel. All AUXADC channels use the same offset compensation value. Starting an offset measurement is done by writing a logic 1 into the offset trigger register for each channel that needs calibration. If the value '7' (decimal) is written into the offset trigger register offsets will be measured for I, Q and AUXADC channels.

Offsets can also be read or written directly. Each offset measurement is implemented internally as an AUXADC measurement and takes approximately 100  $\mu$ s. Offsets from –256 up to 255 can be compensated.

Table 4

Connection of BSI receive signals to the PCF5087X

| PCF5   | 0732 | PCF5087X |     |  |

|--------|------|----------|-----|--|

| PIN    | I/O  | PIN      | I/O |  |

| RXON   |      | RFSIG[z] | 0   |  |

| BDIO   | I/O  | SIOXD    | I/O |  |

| BOEN   | 0    | SIXEN_N  | I   |  |

| BIOCLK | 0    | SIOXCLK  |     |  |

### 9.3.4 BASEBAND SERIAL INTERFACE (BSI) TIMING CHARACTERISTICS

### PCF50732

| Fig.6 | Timing of the baseban | d serial interface receiv | e path; for the tin | ning values see Table 5. |

|-------|-----------------------|---------------------------|---------------------|--------------------------|

|-------|-----------------------|---------------------------|---------------------|--------------------------|

| SYMBOL          | PARAMETER                                        | MIN.                 | TYP.                                       | MAX.           | UNIT |

|-----------------|--------------------------------------------------|----------------------|--------------------------------------------|----------------|------|

| Master cloc     | sk                                               | L                    |                                            | •              | •    |

| t <sub>1</sub>  | MCLK cycle time                                  | -                    | 76.9                                       | -              | ns   |

| t <sub>2</sub>  | MCLK LOW time                                    | 30                   | 1/2t1                                      | _              | ns   |

| t <sub>3</sub>  | MCLK HIGH time                                   | 30                   | <sup>1</sup> / <sub>2</sub> t <sub>1</sub> | -              | ns   |

| t <sub>4</sub>  | RESET LOW time                                   | 3t <sub>1</sub>      | -                                          | -              | ns   |

| Baseband        | Serial Interface (BSI) transmit path (see Fig.5) |                      | •                                          | 1              | •    |

| t <sub>5</sub>  | BIEN0 value                                      | 10                   | _                                          | 511            | QB   |

| t <sub>6</sub>  | BIEN1 value                                      | t <sub>5</sub>       | -                                          | 4000           | QB   |

| t <sub>7</sub>  | BIOCLK cycle time                                | _                    | 48t <sub>1</sub>                           | -              | ns   |

| t <sub>9</sub>  | data set-up time                                 | 20                   | -                                          | -              | ns   |

| t <sub>10</sub> | data hold time                                   | 20                   | -                                          | _              | ns   |

| t <sub>39</sub> | BIOCLK active after TXON rising edge             | _                    | -                                          | t <sub>1</sub> | ns   |

| t <sub>40</sub> | analog TX and GMSK power-up time                 | _                    | -                                          | 17.4           | QB   |

| t <sub>42</sub> | ramp-up value                                    | 0                    | -                                          | 3940           | QB   |

| t <sub>43</sub> | intermediate ramp value                          | 32 + t <sub>42</sub> | -                                          | 3980           | QB   |

| t <sub>44</sub> | ramp-down value                                  |                      |                                            |                |      |

|                 | normal mode                                      | $32 + t_{42}$        | _                                          | 4020           | QB   |

|                 | double burst mode                                | 32 + t <sub>43</sub> | _                                          | 4020           | QB   |

### **Table 5**BSI timing characteristics

### PCF50732

| SYMBOL          | PARAMETER                                       | MIN. | TYP.            | MAX. | UNIT |

|-----------------|-------------------------------------------------|------|-----------------|------|------|

| Baseband S      | Serial Interface (BSI) receive path (see Fig.6) | ·    |                 | •    | •    |

| t <sub>11</sub> | analog power-up and filter settling time        |      |                 |      |      |

|                 | ZIF mode                                        | _    | 52              | _    | μs   |

|                 | NZIF mode                                       | _    | 26              | -    | μs   |

| t <sub>12</sub> | BIOCLK cycle time                               |      |                 |      |      |

|                 | ZIF mode                                        | _    | 2t <sub>1</sub> | -    | ns   |

|                 | NZIF mode                                       | _    | t <sub>1</sub>  | _    | ns   |

| t <sub>13</sub> | BOEN LOW after falling clock edge               | _    | _               | 15   | ns   |

| t <sub>14</sub> | BIOCLK falling edge to data valid               | _    | -               | 15   | ns   |

| t <sub>15</sub> | BOEN HIGH after falling clock edge              | _    | -               | 15   | ns   |

### 10 VOICE BAND CODEC

The voice band CODEC is a complete analog front-end circuit. It consists of three parts:

- The **receive path**, which converts a digital linear PCM signal to an analog signal for an earpiece, an external loudspeaker or a buzzer

- The **transmit path**, which receives an analog signal from a microphone or an auxiliary input and converts it into a digital linear PCM signal

- The digital Audio Serial Interface (ASI), which connects the digital linear PCM signals of the receive and transmit paths to a digital signal processor.

Various functions and characteristics of the voice band CODEC can be selected by programming the corresponding control registers in the Control register block (see also Tables 11, 22, 23, 24 and 25).

#### 10.1 Voice band receive path

The voice band receive path consists of the following parts:

- · The receive part of the voice band signal processor

- NOISE SHAPER: 3rd order digital ΣΔ modulator, generates a bit stream at 1 MHz to drive the EARDAC

- EARDAC: digital-to-analog converter including low-pass filter for high frequency noise content of noise shaper

- EARAMP: amplifier for an earpiece

- AUXAMP: amplifier for an auxiliary loudspeaker

- BUZAMP: amplifier for a buzzer output.

Linearity of receiver equipment (to earpiece) at EARPGA = 0 dB and a volume control (VOLPGA and EARAMP or AUXAMP) of -12 dB, signal-to-total harmonic distortion ratio according to "GSM recommendation II.11.10 V.4.16.1".

### 10.1.1 RXVOL

RXVOL controls the volume of the voice band receive path. In conjunction with EARAMP, AUXAMP and BUZAMP it allows a gain variation from +6 to -30 dB in 64 steps; see Table 25. RXVOL also provides a mute selection of the three outputs EARP/EARN, AUXSP and BUZ respectively. At RESET the volume is automatically set to -12 dB.

#### 10.1.2 RXPGA

RXPGA controls the gain of the voice band receive path within a range of -24 to +12 dB in 64 steps for calibration purposes.

#### 10.1.3 RXFILTER

RXFILTER is a digital band-pass filter with a pass band from 300 to 3400 Hz. It is realized by a programmable structure (voice band signal processor).

#### 10.1.4 EARDAC

EARDAC is a DAC operating at a sampling frequency of 1 MHz. It converts the bitstream input to a sampled differential analog signal and low-pass filters the output signal at the same time.

### 10.1.5 EARAMP

EARAMP is an amplifier, capable of driving a standard earpiece with a minimum impedance of 8  $\Omega$  in single-ended mode or 16  $\Omega$  in differential mode.

### 10.1.6 AUXAMP

AUXAMP is an amplifier for connection to an external loudspeaker amplifier of minimum 8  $\Omega$  (hands-free car kit).

#### An 'auxiliary speaker external amplifier control' output pin (AMPCTRL) can be used to switch on/off an external amplifier (hands-free car kit). The status of AMPCTRL is programmable via the Control Serial Interface; its default value is on.

### 10.1.7 BUZAMP

BUZAMP is an amplifier for connection to an external buzzer of minimum 8  $\Omega$ . It has the same output characteristics as the AUXAMP and can hence be used as a second auxiliary output amplifier. It is switched on/off by a dedicated control bit in the Control register block.

### 10.2 Voice band transmit path

The voice band transmit path consists of the following parts:

- MICMUX: microphone input multiplexer

- MICADC: ΣΔ analog-to-digital converter

- **DECIMATOR:** decimates the incoming bit stream from 1 MHz to 40 kHz

- **TXFILTER:** band-pass filter for the digital transmit signal and down-sampling

- **TXPGA/LIM:** fine-programmable gain for calibration, limiter

- SidePGA: voice band sidetone programmable gain amplifier.

Linearity of transmitter equipment, signal-to-total harmonic distortion ratio according to *"GSM recommendation II.11.10 V.4.16.1"*.

### 10.2.1 MICMUX

MICMUX is used to select between a differential signal at pins MICP/MICN and a differential signal at pins AUXMICP/AUXMICN.

Values are specified for a standard electret microphone with a sensitivity of  $-64 \pm 3$  dB for high gain or for an external microphone with an amplifier sensitivity of  $-26 \pm 3$  dB (0 dB = 1 V/0.1 Pa = 1 V/µbar; at 1 kHz).

#### 10.2.2 MICADC

MICADC is a  $\Sigma\!\Delta$  A/D converter which generates a 1 MHz bitstream.

#### 10.2.3 DECIMATOR AND TXFILTER

The DECIMATOR is a digital filter, which performs a signal processing to a lower sampling rate at the output compared to the input.

The bitstream with a sampling frequency of 1 MHz is low-pass filtered and down-sampled to 40 kHz by a FIR filter.

A digital high-pass filter and a digital low-pass filter (both IIR filters) process the 14-bit input samples to achieve a band-pass with a pass band from 300 to 3400 Hz. These filters run on the on-chip voice band signal processor (see Fig.7). It's program is down-loaded into the instruction memory (IRAM) via the CSI (see Table 26).

The output of the TXFILTER is down-sampled to a sampling frequency of 8 kHz with a word length of 16 bits.

### 10.2.4 TXPGA

TXPGA adapts the analog signals coming from MICMUX within a range of -30 to +6 dB. It is designed for calibration purposes.

#### 10.2.5 SIDEPGA

SidePGA loops part of the voice band transmit signal back into the receive path. There are 64 gain steps from mute to +6 dB.

### 10.3 Voice band digital circuitry

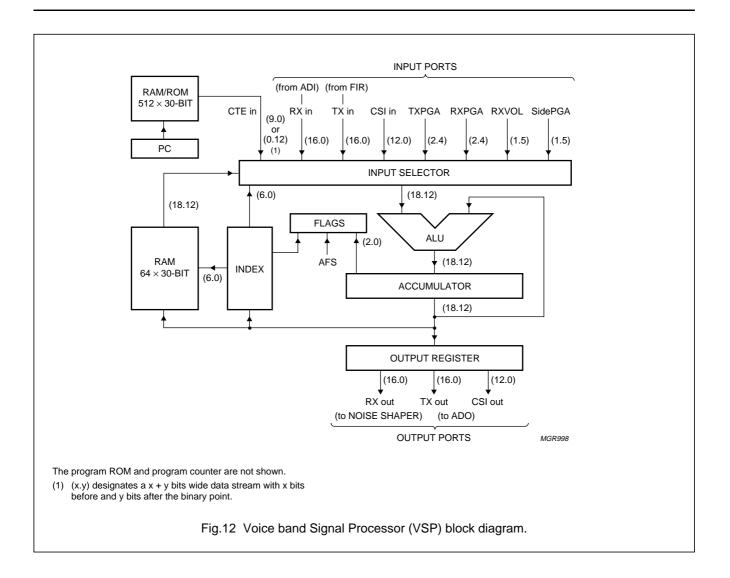

The voice band digital circuitry is responsible for converting a 16-bit PCM signal at 8 kHz sample rate to and from a 1-bit 1 MHz signal. It also contains a band-pass filter for 300 to 3400 Hz and a sidetone engine. Various volume settings are calculated inside this block. Figure 7 shows the block diagram of the voice band signal processor.

### PCF50732

#### VOICE BAND SIGNAL PROCESSOR ADI — TXPGA/LIM DECIMATOR TX BS ACLK-(transmit bitstream) ASI AFS RX/TX SidePGA ADO < 1-bit, 1 MHz FILTER 16-bit, 8 kHz NOISE RX BS RXPGA/LIM RXVOL SHAPER (receive bitstream) MGR992 RRAM IRAM Fig.7 Block diagram of the voice band signal processor.

### 10.3.1 VOLUME CONTROL BLOCK

The volume control block contains the RXPGA, SidePGA, TXPGA and both limiter blocks. The possible settings can be found in the description of the CSI block. All digital volume control blocks, i.e. RXPGA, SidePGA, and TXPGA, will allow settings from +6 to -30 dB and mute in 64 steps. However, not all combinations of settings for these blocks will be meaningful. The limiter will always clip signals with overflow to the maximum or minimum allowable value.

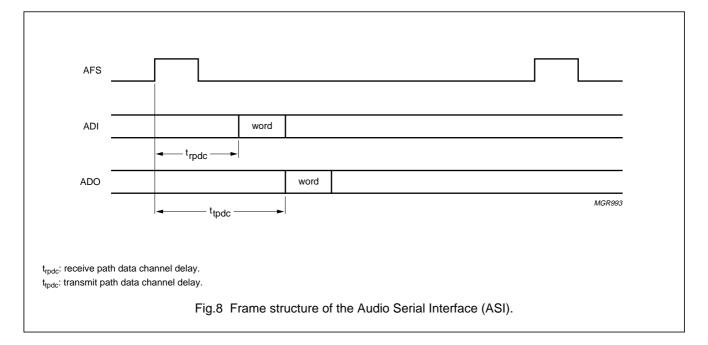

### 10.3.2 AUDIO SERIAL INTERFACE (ASI) BLOCK

The ASI is the voice band serial interface which provides the connection for the exchange of PCM data in both receive and transmit directions, between the baseband digital signal processor and the PCF50732. The data is coded in 16-bit linear PCM twos complement words.

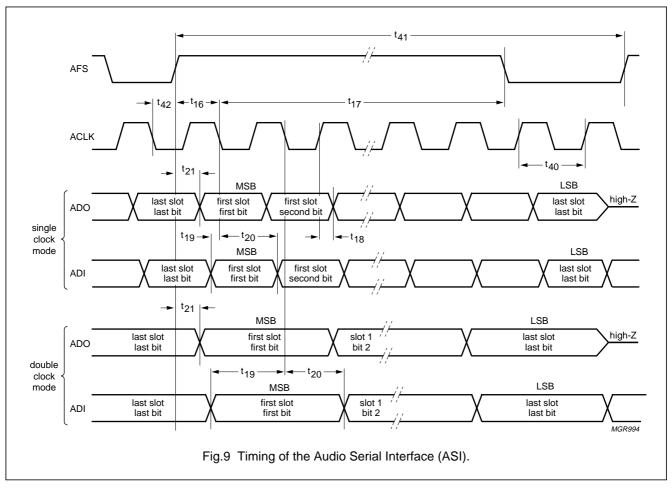

A frame start is defined by the first falling edge of ACLK after a rising AFS. This first falling edge is used to clock in the first data bit on both the baseband and the DSP device.

Data on pin ADI is clocked in (MSB first) on the falling edge of the ACLK clock. Data is clocked out (MSB first) on pin ADO on the rising edge of the ACLK clock. Pin ADO is put in 3-state after the LSB of the transmit word, independent of the length of the AFS pulse. If the channel position 0 (see Section 10.3.2.1) is selected, then the MSB must be output directly after AFS becomes a logic 1, even if no rising edge on ACLK has been given yet.

The following modes of operation are programmable: channel position and ACLK clock mode.

#### 10.3.2.1 Channel position mode

Depending on a programmable register value n (n = 0 to 15) one of 16 channels can be selected (see Table 22). The ASI can add a delay of  $16 \times n$ -bit clocks between the assertion of AFS and the start of the MSB of the PCM values. This delay is independently programmable for transmit and receive mode.

#### 10.3.2.2 ACLK clock mode

Single or double clock mode can be selected. Double clock mode implies two clock pulses per data bit and is used for communication with IOM2 compatible devices. In double clock mode data must be output on the first rising edge and be read on the last falling edge.

PCF50732

### PCF50732

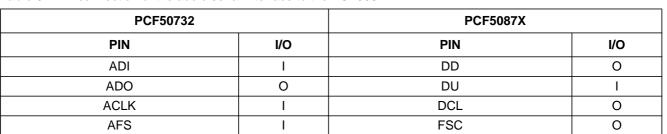

### Table 6 Pin connection of the audio serial interface to the PCF5087X

### PCF50732

10.3.2.3 Audio Serial Interface (ASI) timing characteristics

| Table 7 | ASI timing characteristics |

|---------|----------------------------|

|---------|----------------------------|

| SYMBOL          | PARAMETER                                            | MIN. | TYP. | MAX. | UNIT |

|-----------------|------------------------------------------------------|------|------|------|------|

| t <sub>16</sub> | frame sync (AFS) set-up time to falling edge of ACLK | 70   | -    | -    | ns   |

| t <sub>17</sub> | frame sync (AFS) hold time from falling edge of ACLK | 40   | -    | -    | ns   |

| t <sub>18</sub> | ACLK rising edge to data (ADO) valid                 | -30  | -    | +30  | ns   |

| t <sub>19</sub> | data (ADI) set-up time to falling edge of ACLK       | 50   | -    | -    | ns   |

| t <sub>20</sub> | data (ADI) hold time from falling edge of ACLK       | 80   | -    | -    | ns   |

| t <sub>21</sub> | first data valid (ADO) after AFS rising edge         | 0    | -    | 60   | ns   |

| t <sub>40</sub> | ACLK period                                          |      |      |      |      |

|                 | single clock mode                                    | 0.5  | -    | 7.8  | μs   |

|                 | double clock mode                                    | 0.5  | -    | 3.9  | μs   |

| t <sub>41</sub> | AFS period                                           | -    | 125  | -    | μs   |

| t <sub>42</sub> | ACLK LOW before AFS rising edge                      | 40   | -    | -    | ns   |

### PCF50732

### **11 AUXILIARY FUNCTIONS**

The auxiliary functions part consists of three digital-to-analog converters (DACs) and a 4 input analog-to-digital converter (ADC) with a 12-bit range. The DACs are for:

- Automatic Gain Control (AGC): AUXDAC1

- Automatic Frequency Control (AFC): AUXDAC2

- Power ramping: AUXDAC3.

### 11.1 Automatic Gain Control (AGC): AUXDAC1

The AUXDAC1 is an 8-bit binary coded, guaranteed monotonic digital-to-analog converter.

The status of AUXDAC1 is controlled by the signal AUXST and a power-up bit in the Power control register. The signal that switches the external VCXO can also be used to control the AUXST pin of the PCF50732. The AUXDAC1 output is floating in Power-down mode (AUXST = LOW). The input MCLK is then deactivated.

When AUXST goes HIGH, AUXDAC1 is powered-up and the converted value of the corresponding register in the control register block is available at the AUXDAC1 output pin.

If a write access to the AUXDAC1 register occurs, the DAC is activated with the new content of the DAC register (see Table 14 and 15). The AUXDAC1 must be powered-up by setting the correct bit in the Power control register. At reset AUXDAC1 is powered-down.

### 11.2 Automatic Frequency Control (AFC): AUXDAC2

The AUXDAC2 is a 12-bit binary coded, guaranteed monotonic digital-to-analog converter. This DAC is used to control the frequency of an external master clock VCXO.

The status of AUXDAC2 is controlled by the signal AUXST and a power-up bit in the Power control register. The signal that switches the external VCXO can also be used to control the AUXST pin of the PCF50732. The AUXDAC2 output is floating in Power-down mode (AUXST = LOW). When AUXST goes HIGH, AUXDAC2 is powered-up and the converted value of the corresponding register in the control register block is available at the AUXDAC2 output pin.

The default value for AUXDAC2 is 1.1 V which corresponds to a 800H code in the AUXDAC2 register. At reset AUXDAC2 is powered on.

### 11.3 Power ramping: AUXDAC3

AUXDAC3 is a 10-bit binary coded digital-to-analog converter designed for power ramping purposes. AUXDAC3 is default off. The power ramping behaviour is described in Section 9.3.2.2.

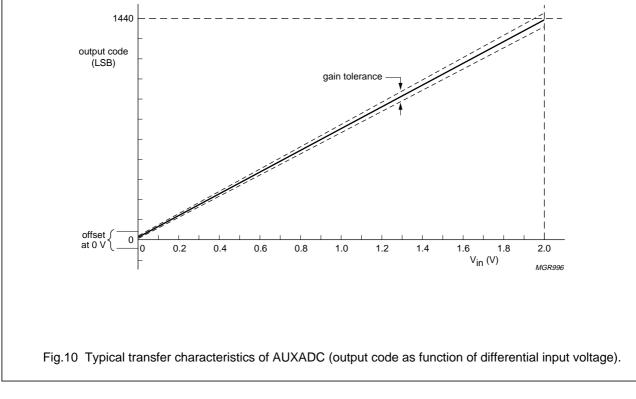

### 11.4 Auxiliary analog-to-digital converter (AUXADC)

The AUXADC is specified for voltage and temperature measurements. It contains 4 input channels required for  $\Delta T$  and  $\Delta V$  measurements, as well as battery type recognition:

- ΔT: battery temperature, ambient temperature (measured across sensor)

- ΔV: peak battery voltage, battery voltage during transmit burst.

Five 12-bit registers are available in which results of auxiliary analog-to-digital conversions can be stored. Two registers are dedicated to the input AUXADC1 and one to each of AUXADC2, AUXADC3 and AUXADC4.

The AUXADC1 input can be used for battery voltage measurement. In the AUXADC1A register the voltage during a transmit time slot can be stored. The AUXADC1B register can store the voltage during other time slots. If a read request to one of these registers is executed by loading its address into the Read request register, the actual contents of the addressed register are given to the control interface and a new measurement is performed in the next appropriate time slot.

A multiplexer connects each of the AUXADC inputs to a channel of the receive ADC depending on read access to the corresponding register.

Thus an auxiliary analog-to-digital conversion is only possible, if the baseband receive section is not in use (RXON is LOW). At each read request to one of the AUXADC registers, a flag is set in the AUXADC flag register indicating that an analog-to-digital conversion is to be performed. When one of the registers AUXADC1B, AUXADC2, AUXADC3, or AUXADC4 is being read, the baseband interface verifies that RXON is LOW, indicating that no receive burst is currently active. The baseband receive path is then powered up. After the ADC settling time has elapsed (see POST<sub>AUXADC</sub> in Chapter 18), valid data is available and stored in the corresponding register.

**Philips Semiconductors**

After conversion the corresponding bit in the AUXADC flag register is reset (see Table 18). If RXON is activated during an auxiliary analog-to-digital conversion cycle, the auxiliary conversion is interrupted and restarted when RXON returns LOW, indicating no receive burst activity.

Baseband and audio interface for GSM

When register AUXADC1A is read, a battery voltage measurement during a transmission burst is executed. The PCF50732 waits for a rising edge of TXON, and powers up the receive path. After the settling time of the ADC added to the programmed AUXADC conversion delay (in 48 MCLK cycles) has elapsed, valid data is available and stored in the AUXADC1A register.

PCF50732

### PCF50732

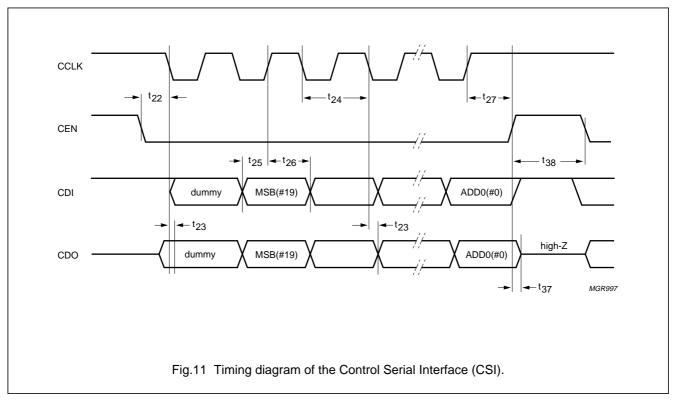

### 12 CONTROL SERIAL INTERFACE (CSI)

The Control Serial Interface block is used to set and read the status bits inside the PCF50732. It is also used to read data from the auxiliary ADCs and to write data into the auxiliary DACs. Finally, the block is used to write the power ramping curve into a  $64 \times 10$ -bit static RAM. It should be noted that only 48 of the 64 addresses can be accessed; see Table 2.

### 12.1 The serial interface

A 4-line bidirectional serial interface is used to control the circuit. It allows access to each register of the control register block (read and/or write). The 4 lines are:

- Data in (CDI)

- Data out (CDO)

- Clock (CCLK)

- Enable (CEN).

Table 8 lists the normal connections to the PCF5087X.

The data sent to or from the device is loaded in bursts framed by CEN. Clock edges and data bits are ignored until CEN goes active (LOW). Each data word consists of 21 bits that comprises a 4-bit device address, a 4-bit register address, a 12-bit data word and a dummy bit; see Table 9. The 21 bits are transmitted with MSB first. Figure 5 shows the valid timing for data transmission on the control interface.

Data is read in from the CDI pin on the rising edge of the CCLK clock and output on CDO on the falling edge of the CCLK clock. Data is written into the registers on the rising edge of CEN.

If the device address is equal to the chip address, the programmed information on CDI (DB11 to DB00) is loaded into the addressed register (RA3 to RA0) when CEN returns inactive HIGH.

The dummy bit in front is needed for compatibility with older baseband devices.

Reading a register is accomplished by writing the address of the required register into the read request register. The next time CEN goes LOW, the requested data will be shifted out, together with the register and device address.

| Table 8 | Pin connection of the CSI to the PCF5087X |

|---------|-------------------------------------------|

|         |                                           |

| PCF5073 | 32  | PCF5087X |     |  |  |  |  |

|---------|-----|----------|-----|--|--|--|--|

| PIN     | I/O | PIN      | I/O |  |  |  |  |

| CDI     | I   | RFDO     | 0   |  |  |  |  |

| CDO     | 0   | RFDI     | I   |  |  |  |  |

| CCLK    | I   | RFCLK    | 0   |  |  |  |  |

| CEN     | I   | RFE_N2   | 0   |  |  |  |  |

**Table 9**Bit mapping of the 21-bit words

| BIT      | CONTENT      | DESCRIPTION                                                         |

|----------|--------------|---------------------------------------------------------------------|

| 00 to 03 | ADD0 to ADD3 | device address; for the<br>PCF50732 this is '1001'<br>(= 9 decimal) |

| 04 to 07 | RA0 to RA3   | register address                                                    |

| 08 to 19 | DB00 to DB11 | data value                                                          |

| 20       | dummy        | don't care                                                          |

### PCF50732

### 12.2 Control Serial Interface (CSI) timing characteristics

**Table 10** CSI timing characteristicsFor the timing diagram see Fig.11.

| SYMBOL          | PARAMETER                               | MIN. | MAX. | UNIT |

|-----------------|-----------------------------------------|------|------|------|

| t <sub>22</sub> | CEN set-up time                         | 20   | _    | ns   |

| t <sub>23</sub> | CDO data valid after falling clock edge | _    | 50   | ns   |

| t <sub>24</sub> | CCLK cycle time                         | 100  | _    | ns   |

| t <sub>25</sub> | data set-up time to rising edge of CCLK | 20   | _    | ns   |

| t <sub>26</sub> | data hold time from rising edge of CCLK | 30   | -    | ns   |

| t <sub>27</sub> | CEN hold time                           | 30   | _    | ns   |

| t <sub>37</sub> | CDO 3-state after CEN HIGH              | _    | 30   | ns   |

| t <sub>38</sub> | CEN HIGH time                           | 50   | _    | ns   |

### PCF50732

### 12.3 Control register block

This section describes the different registers that are implemented in the PCF50732. An overview is given in Table 11. Tables 12 to 29 describe all the registers of the PCF50732.

Table 11

Control register block overview

| ADDRESS | ACCESS | REGISTER NAME                                  |

|---------|--------|------------------------------------------------|

| 0000    | W      | Read request register                          |

| 0001    | R/W    | AUXDAC1 (AGC) value register                   |

| 0010    | R/W    | AUXDAC2 (AFC) value register                   |

| 0011    | R/W    | Burst control register                         |

| 0100    | R/W    | AUXADC control register                        |

| 0101    | R      | AUXADC channel 1 register A (AUXADC1A); note 1 |

| 0110    | R      | AUXADC channel 1 register B (AUXADC1B); note 1 |

| 0111    | R      | AUXADC channel 2 register (AUXADC2); note 1    |

| 1000    | R      | AUXADC channel 3 register (AUXADC3); note 1    |

| 1001    | R      | AUXADC channel 4 register (AUXADC4); note 1    |

| 1010    | R/W    | Voice band control register                    |

| 1011    | R/W    | Voice band volume register                     |

| 1100    | R/W    | Power control register                         |

| 1101    | R/W    | RAM interface register                         |

| 1110    | R/W    | Baseband receive control register              |

| 1111    | R/W    | Test mode register; note 2                     |

#### Notes

- 1. See description in Section 11.4.

- 2. Do not use this register.

### 12.3.1 READ REQUEST REGISTER

#### Table 12 Read request register

X = don't care during a read/or write access.

| ADDRESS | REGISTER NAME         | VALUE |    |   |   |    |    |    |    |    |    |    |    |

|---------|-----------------------|-------|----|---|---|----|----|----|----|----|----|----|----|

|         | REGISTER NAME         | 11    | 10 | 9 | 8 | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| 0000    | Read request register | Х     | Х  | Х | Х | r3 | r2 | r1 | r0 | s3 | s2 | s1 | s0 |

### Table 13 Read request registers value description

| VALUE OF              | SYMBOL   | DESCRIPTION                                                                                                                                                                                         |

|-----------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read request register | r3 to r0 | Address of the register to be read.                                                                                                                                                                 |

|                       | s3 to s0 | Subaddress that might be needed. The subaddress bits are right aligned, meaning that the subaddress always starts with bit 's0' (LSB); e.g. in case of two subaddress bits, 's1' and 's0' are used. |

### PCF50732

### 12.3.2 AUXDAC1 (AGC) VALUE AND AUXDAC2 (AFC) VALUE REGISTERS

#### Table 14 Registers overview

X = don't care during a read/or write access.

| ADDR. | REGISTER NAME                | VALUE |     |    |    |    |    |    |    |    |    |    |    |

|-------|------------------------------|-------|-----|----|----|----|----|----|----|----|----|----|----|

|       |                              | 11    | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| 0001  | AUXDAC1 (AGC) value register | Х     | X   | Х  | Х  | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| 0010  | AUXDAC2 (AFC) value register | b11   | b10 | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| VALUE OF                     | SYMBOL    | DESCRIPTION                                                                             |

|------------------------------|-----------|-----------------------------------------------------------------------------------------|

| AUXDAC1 (AGC) value register | b7 to b0  | input value to the 8-bit AUXDAC1 (fed directly into the DAC); the default value is 85H  |

| AUXDAC2 (AFC) value register | b11 to b0 | input value to the 8-bit AUXDAC2 (fed directly into the DAC); the default value is 800H |

#### 12.3.3 BURST CONTROL REGISTER

The Burst control register controls the timing of the transmit burst (TX-burst). The 'lo'-registers contain the lower 8 bits, the 'hi'-registers the upper 4 bits of a 12-bit delay value. Therefore, each register has a programmable range from 0 to 4095. Not all combinations of values might make sense e.g. ramp-down before ramp-up.

#### Table 16 Burst control register (address 001 and subaddresses)

X = don't care during a read/or write access.

|                                         |            | SUBAD      | DRESS             | 5                 | VALUE |    |    |    |     |     |    |    |  |  |

|-----------------------------------------|------------|------------|-------------------|-------------------|-------|----|----|----|-----|-----|----|----|--|--|

| FUNCTION                                | 11<br>(s3) | 10<br>(s2) | 9<br>(s1)         | 8<br>(s0)         | 7     | 6  | 5  | 4  | 3   | 2   | 1  | 0  |  |  |

| RU-lo                                   | 0          | 0          | 0                 | 0                 | b7    | b6 | b5 | b4 | b3  | b2  | b1 | b0 |  |  |

| RU-hi                                   | 0          | 0          | 0                 | 1                 | x     | Х  | Х  | X  | b11 | b10 | b9 | b8 |  |  |

| RM-lo                                   | 0          | 0          | 1                 | 0                 | b7    | b6 | b5 | b4 | b3  | b2  | b1 | b0 |  |  |

| RM-hi                                   | 0          | 0          | 1                 | 1                 | X     | Х  | Х  | X  | b11 | b10 | b9 | b8 |  |  |

| RD-lo                                   | 0          | 1          | 0                 | 0                 | b7    | b6 | b5 | b4 | b3  | b2  | b1 | b0 |  |  |

| RD-hi                                   | 0          | 1          | 0                 | 1                 | X     | Х  | Х  | X  | b11 | b10 | b9 | b8 |  |  |

| BIEN0-lo                                | 0          | 1          | 1                 | 0                 | b7    | b6 | b5 | b4 | b3  | b2  | b1 | b0 |  |  |

| BIEN0-hi                                | 0          | 1          | 1                 | 1                 | X     | Х  | X  | X  | b11 | b10 | b9 | b8 |  |  |

| BIEN1-lo                                | 1          | 0          | 0                 | 0                 | b7    | b6 | b5 | b4 | b3  | b2  | b1 | b0 |  |  |

| BIEN1-hi                                | 1          | 0          | 0                 | 1                 | X     | Х  | Х  | X  | b11 | b10 | b9 | b8 |  |  |

| Single/double burst mode <sup>(1)</sup> | 1          | 0          | 1                 | 0                 | Х     | Х  | Х  | Х  | Х   | Х   | Х  | b0 |  |  |

| DAC3 burst RAM address <sup>(1)</sup>   | 1          | 0          | 1                 | 1                 | Х     | Х  | a5 | a4 | a3  | a2  | a1 | a0 |  |  |

| DAC3 burst RAM data <sup>(1)</sup>      | 1          | 1          | d9 <sup>(2)</sup> | d8 <sup>(2)</sup> | d7    | d6 | d5 | d4 | d3  | d2  | d1 | d0 |  |  |

### Notes

1. The programming is described in Section 9.3.2.2.

2. The subaddress positions bit 9 (s1) and bit 8 (s0) do not apply to the DAC3 burst RAM data register.

# PCF50732

| Table 17 Burst control registers value description |

|----------------------------------------------------|

|----------------------------------------------------|

| VALUE OF | DESCRIPTION                                                                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RU       | Value RU, consisting of RU-lo (least significant byte) and RU-hi (most significant byte), is the delay measured in quarterbits ( $1_{12}$ MCLK) between the rising edge of TXON and the start of the ramp-up on AUXDAC3. After this delay, the first 16 values of the AUXDAC3 RAM are sent to AUXDAC3. Shifting out is done at $1_{24}$ MCLK. |

| RM       | Value RM, consisting of RM-lo (least significant byte) and RM-hi (most significant byte), is the delay measured in quarterbits between the rising edge of TXON and the start of the intermediate ramp in a double burst ramp. The RM value is only used in multislot mode. RM must be greater than RU + 32.                                   |

| RD       | Value RD, consisting of RD-lo (least significant byte) and RD-hi (most significant byte), is the delay measured in quarterbits between the rising edge of TXON and the start of the ramp-down on AUXDAC3. RD must be greater than RU + 32, or in case of multislot mode, greater than RM + 32.                                                |

| BIEN0    | Value BIEN0, consisting of BIEN0-lo (least significant byte) and BIEN0-hi (most significant byte), is the delay measured in quarterbits between the rising edge of TXON and the falling edge of BIEN.                                                                                                                                         |

| BIEN1    | Value BIEN1, consisting of BIEN1-lo (least significant byte) and BIEN1-hi (most significant byte), is the delay measured in quarterbits between the rising edge of TXON and the rising edge of BIEN. BIEN1 must be greater than BIEN0.                                                                                                        |

### 12.3.4 AUXADC CONTROL REGISTER

Table 18 AUXADC control register (address 0100 and subaddresses)

X = don't care during a read/or write access.

|                                        | SUB        | ADDR       | ESS       | VALUE                                               |     |      |          |           |         |           |    |         |  |  |

|----------------------------------------|------------|------------|-----------|-----------------------------------------------------|-----|------|----------|-----------|---------|-----------|----|---------|--|--|

| FUNCTION                               | 11<br>(s2) | 10<br>(s1) | 9<br>(s0) | 8                                                   | 8 7 |      | 5        | 4         | 3       | 2         | 1  | 0       |  |  |

| AUXADC conversion delay value register | 0          | 0          | 0         | X X b6 b5 b4 b3 b2 b1                               |     |      |          |           |         |           | b0 |         |  |  |

| AUXADC flag register                   | 0          | 0          | 1         | X Qoff loff auxoff flag 4 flag 3 flag 2 flag 1B fla |     |      |          |           |         |           |    | flag 1A |  |  |

| AUXADC offset value register           | 1          | 0          | 0         | 9-bit signed offset compensation value              |     |      |          |           |         |           |    |         |  |  |

| I channel offset value register        | 1          | 0          | 1         |                                                     |     | 9-bi | t signed | offset co | ompensa | ation val | ue |         |  |  |

| Q channel offset value register        | 1          | 1          | 0         | 9-bit signed offset compensation value              |     |      |          |           |         |           |    |         |  |  |

| Offset trigger register                | 1          | 1          | 1         | X X X X X X Q-off I-off A                           |     |      |          |           |         |           |    | Aux     |  |  |

PCF50732

| Table 19 AUX | XADC control register | s value description |

|--------------|-----------------------|---------------------|

|--------------|-----------------------|---------------------|

| VALUE OF                               | DESCRIPTION                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| AUXADC conversion delay value register | The 7-bit value (b6 to b0) denotes the delay measured in 48MCLK units between the rising edge of TXON and the conversion on AUXADC1A. The normal power-on settling time is added to this delay. Default value is 0. |  |  |  |  |  |  |  |  |  |

| AUXADC flag register                   | The AUXADC flag register returns the status of the AUXADC converters. If an auxiliary A/D conversion is pending, the flag of the corresponding AUXADC will be set. The flag register is read only.                  |  |  |  |  |  |  |  |  |  |

| AUXADC offset value register           | The offset value registers contain signed 9-bit offset compensation values. These                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| I channel offset value register        | values are subtracted automatically from all baseband receive (BBRX) and AUXADC                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Q channel offset value register        | measurements to compensate for offset errors. The compensation values can be<br>read and written and have a default value of 0. It can also be measured by the device                                               |  |  |  |  |  |  |  |  |  |

| Offset trigger register                | itself.                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|                                        | A write to the Offset trigger register will trigger an offset measurement for each of the channels (Q-off, I-off or AUXADC) selected.                                                                               |  |  |  |  |  |  |  |  |  |

|                                        | Offset measurements are special cases of AUXADC measurements and are done sequentially. Each calibration measurement takes approximately 100 $\mu$ s. The Offset trigger register is write only.                    |  |  |  |  |  |  |  |  |  |

### 12.3.5 AUXADC REGISTERS

### Table 20 AUXADC registers overview

| ADDR. | REGISTER NAME                          | VALUE |     |    |    |    |    |    |    |    |    |    |    |  |  |

|-------|----------------------------------------|-------|-----|----|----|----|----|----|----|----|----|----|----|--|--|

| ADDR. | REGISTER NAME                          | 11    | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

| 0101  | AUXADC channel 1 register A (AUXADC1A) |       |     |    |    |    |    |    |    |    |    |    |    |  |  |

| 0110  | AUXADC channel 1 register B (AUXADC1B) |       |     |    |    |    |    |    |    |    |    |    |    |  |  |

| 0111  | AUXADC channel 2 register (AUXADC2)    | b11   | b10 | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |  |  |

| 1000  | AUXADC channel 3 register (AUXADC3)    |       |     |    |    |    |    |    |    |    |    |    |    |  |  |

| 1001  | AUXADC channel 4 register (AUXADC4)    |       |     |    |    |    |    |    |    |    |    |    |    |  |  |

Table 21 AUXADC registers value description

| VALUE OF | DESCRIPTION                                                                                    |

|----------|------------------------------------------------------------------------------------------------|

| AUXADC1A | 12-bit result of the A/D conversion on AUXADC channel 1, measured during a transmission burst  |

| AUXADC1B | 12-bit result of the A/D conversion on AUXADC channel 1, measured outside a transmission burst |

| AUXADC2  | 12-bit result of the A/D conversion on AUXADC channel 2                                        |

| AUXADC3  | 12-bit result of the A/D conversion on AUXADC channel 3                                        |

| AUXADC4  | 12-bit result of the A/D conversion on AUXADC channel 4                                        |

### PCF50732

12.3.6 VOICE BAND CONTROL REGISTER

The Voice band control register is used to control the following functionality of the voice band CODEC:

- Analog input source: microphone (MICAMP) or auxiliary (AUXMIC) input

- Analog output device: earphone (EARAMP), auxiliary (AUXAMP) or buzzer (BUZAMP) output; this register allows individual control of all three output amplifiers

- EARAMP output mode: single-ended (EARP) or differential (EARN/EARP). This selects the input source for the EARAMP-N amplifier. In single-ended mode EARAMP-N will be at V<sub>ref</sub>, in differential mode it will carry the output signal

- General purpose output pin: AMPCTRL

- Receive and transmit path delay values

- ASI clock mode

- TX gain boost (MICHI).

### Table 22 Voice band control register (address 1010 and subaddresses)

X = don't care during a read/or write access.

|                            | SUE        |            |           |            | V         | ALU    | E           |          |   |   |   |                       |                                    |

|----------------------------|------------|------------|-----------|------------|-----------|--------|-------------|----------|---|---|---|-----------------------|------------------------------------|

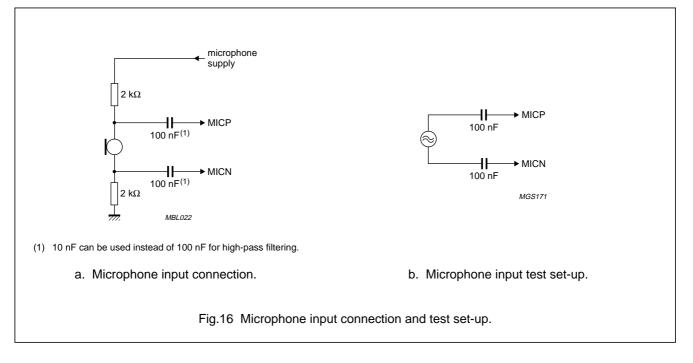

| FUNCTION                   | 11<br>(s2) | 10<br>(s1) | 9<br>(s0) | 8          | 8 7 6 5 4 |        | 4           | 3        | 2 | 1 | 0 | FUNCTION SETTING      |                                    |