### 查询PCI1211供应商

# 捷多邦,专业PCB打样工厂,24小时**PC制业**GGU/PGE PC CARD CONTROLLERS

SCPS033A - OCTOBER 1998

- PC 98/99 Compliant

- PCI Bus Power Management Interface Specification 1.0 Compliant

- Advanced Configuration and Power Interface (ACPI) 1.0 Compliant

- Fully Compatible With the Intel<sup>™</sup> 430TX (Mobile Triton II) Chipset

- PCI Local Bus Specification Revision 2.2 Compliant

- 1997 PC Card<sup>™</sup> Standard Compliant

- 3.3-V Core Logic With Universal PCI Interfaces Compatible With 3.3-V and 5-V PCI Signaling Environments

- Mix-and-Match 5-V/3.3-V PC Card16 Cards and 3.3-V CardBus Cards

- Supports a Single PC Card or CardBus Slot With Hot Insertion and Removal

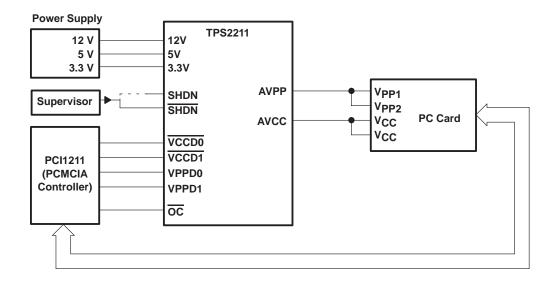

- Provides Interface to Parallel Single-Slot PC Card Power-Interface Switches like the TI<sup>™</sup> TPS2211

- Supports Burst Transfers to Maximize Data Throughput on the PCI Bus and the CardBus Bus

- Supports Parallel PCI Interrupts, Parallel ISA IRQ and Parallel PCI Interrupts, Serial ISA IRQ With Parallel PCI Interrupts, and Serial ISA IRQ and PCI Interrupts

- Pin-to-Pin Compatible with PCI1210

- Serial EEPROM Interface for Loading Subsystem ID and Subsystem Vendor ID

- Pipelined Architecture Allows Greater Than 130M-Bytes-Per-Second Throughput From CardBus to PCI and From PCI to CardBus

- Supports Up to Five General-Purpose I/Os

- Five PCI Memory Windows and Two I/O Windows Available to the PC Card16 Socket

- Two I/O Windows and Two Memory Windows Available to the CardBus Socket

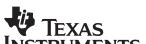

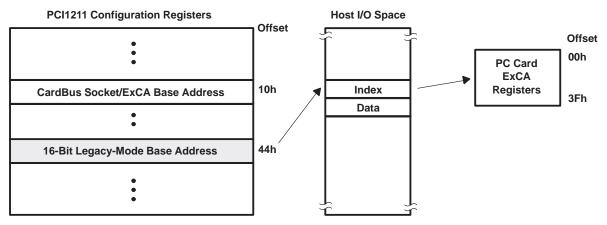

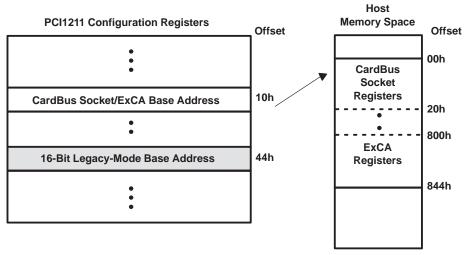

- Exchangeable Card Architecture (ExCA) Compatible Registers Are Mapped in Memory and I/O Space

- Intel 82365SL-DF Register Compatible

- Supports Distributed DMA (DDMA) and PC/PCI DMA

- Supports 16-Bit DMA on the PC Card Socket

- Supports Ring Indicate, SUSPEND, PCI CLKRUN, and CardBus CCLKRUN

- Supports PCI Bus Lock (LOCK)

- LED Activity Pin

- Advanced Submicron, Low-Power CMOS

Technology

- Choice of Surface-Mount Packaging:

PGE Low-Profile Plastic Quad Flat Package (LQFP)

- GGU High Density Ball Grid Array (BGA)

#### Table of Contents

| Table of                                             | coments                                   |

|------------------------------------------------------|-------------------------------------------|

| Description 2                                        | PC Card Controller Programming Model      |

| System Block Diagram                                 | PCI Configuration Registers               |

| Terminal Assignments 4                               | ExCA Compatibility Registers              |

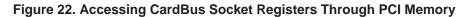

| Signal Name/Terminal Assignments                     | CardBus Socket Registers 104              |

| Terminal Functions 11                                | Distributed DMA (DDMA) Registers 112      |

| Power Supply Sequencing 21                           | Absolute Maximum Ratings 118              |

| I/O Characteristics 21                               | Recommended Operating Conditions          |

| Clamping Voltages 21                                 | Electrical Characteristics                |

| Peripheral Component Interconnect (PCI) Interface 22 | PCI Clock/Reset Timing Requirements       |

| PC Card Applications 23                              | PCI Timing Requirements 121               |

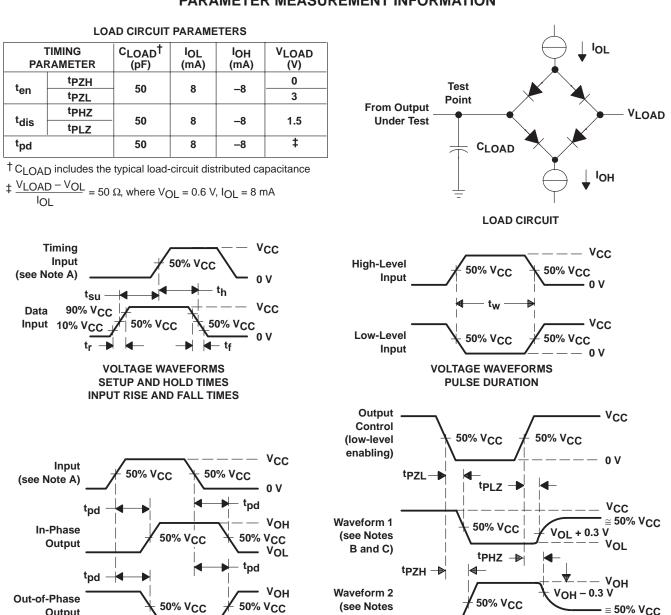

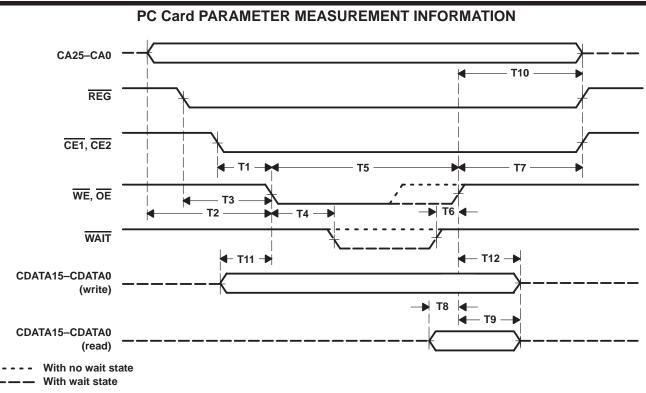

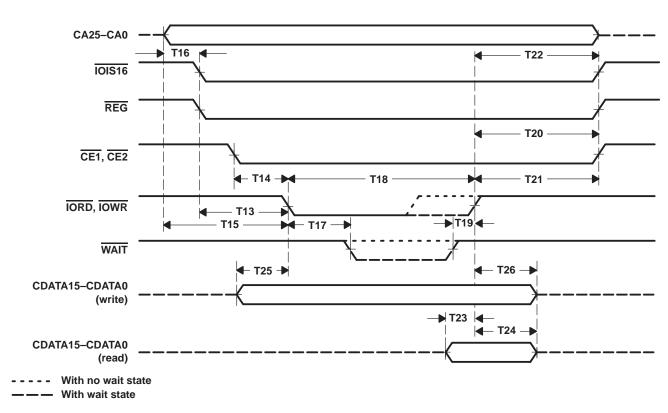

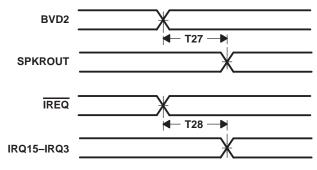

| Serial Bus Interface                                 | Parameter Measurement Information         |

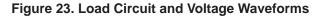

| Programmable Interrupt Subsystem                     | PCI Bus Parameter Measurement Information |

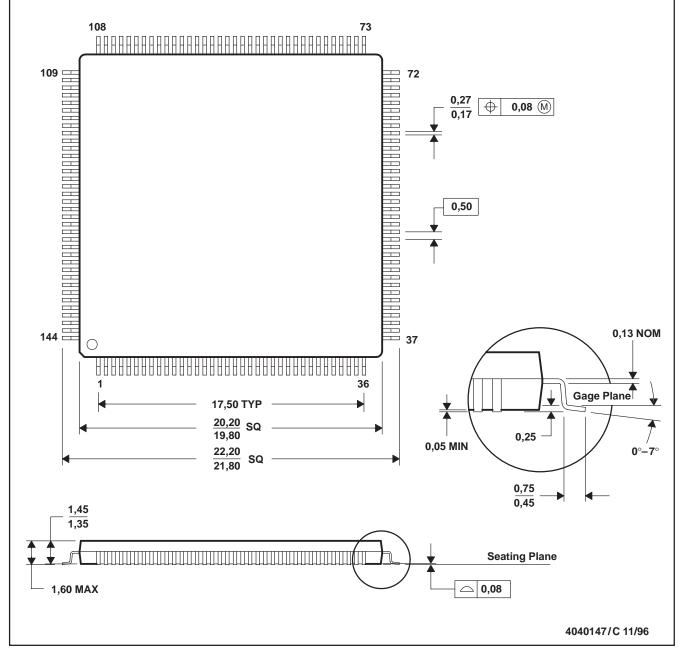

| Power Management Overview                            | Mechanical Data                           |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Intel is a trademark of Intel Corporation. PC Card is a trademark of Personal Computer Memory Card International Association (PCMCIA).

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include lesting of all parameters.

SCPS033A – OCTOBER 1998

### description

The Texas Instruments PCI1211 is a high-performance PCI-to-PC Card controller that supports a single PC Card socket compliant with the 1995 PC Card Standard. The PCI1211 provides a rich feature set that makes it the best choice for bridging between PCI and PC Cards in both notebook and desktop computers. The 1997 PC Card Standard retains the 16-bit PC Card specification defined in PCMCIA Release 2.2, and defines the new 32-bit PC Card, CardBus, capable of full 32-bit data transfers at 33 MHz. The PCI1211 supports both 16-bit and CardBus PC Cards, powered at 5 V or 3.3 V, as required.

The PCI1211 is compliant with the *PCI Local Bus Specification, Revision 2.2*, and its PCI interface can act as either a PCI master device or a PCI slave device. The PCI bus mastering is initiated during 16-bit PC Card direct memory access (DMA) transfers or CardBus PC Card bridging transactions. The PCI1211 is also compliant with the latest *PCI Bus Power Management Interface Specification, Revision 1.0*.

All card signals are internally buffered to allow hot insertion and removal without external buffering. The PCI1211 is register compatible with the Intel 82365SL-DF ExCA controller. The PCI1211 internal data path logic allows the host to access 8-, 16-, and 32-bit cards using full 32-bit PCI cycles for maximum performance. Independent buffering and a pipeline architecture provide an unsurpassed performance level with sustained bursting. The PCI1211 can also be programmed to accept fast posted writes to improve system-bus utilization.

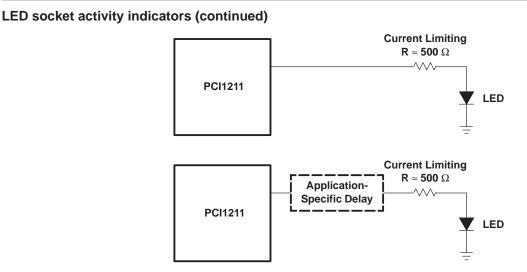

Multiple system-interrupt signaling options are provided, including: parallel PCI, parallel ISA, serialized ISA, and serialized PCI. Furthermore, general-purpose inputs and outputs are provided for the board designer to implement sideband functions. Many other features are designed into the PCI1211, such as socket activity light-emitting diode (LED) output, that are discussed in detail throughout the design specification.

An advanced complementary metal-oxide semiconductor (CMOS) process achieves low system-power consumption while operating at PCI clock rates up to 33 MHz. Several low-power modes enable the host power management system to further reduce power consumption.

Unused PCI1211 inputs must be pulled up using a 43 k $\Omega$  resistor.

SCPS033A - OCTOBER 1998

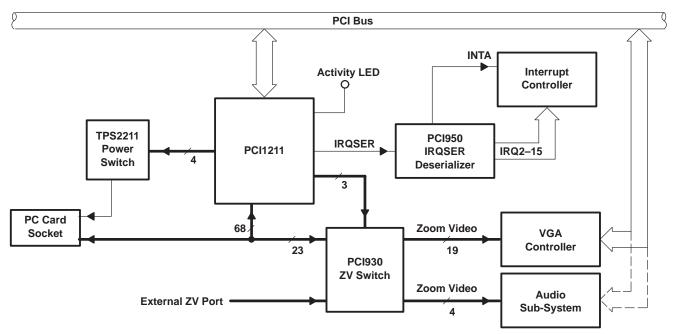

### system block diagram

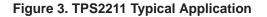

A simplified system block diagram using the PCI1211 is provided below. The PCI950 IRQ deserializer and the PCI930 zoomed video (ZV) switch are optional functions that can be used when the system requires that capability.

The PCI interface includes all address/data and control signals for PCI protocol. The 68-pin PC Card interface includes all address/data and control signals for CardBus and 16-bit (R2) protocols. When ZV is enabled (in 16-bit PC Card mode) 23 of the 68 signals are redefined to support the ZV protocol.

The interrupt interface includes terminals for parallel PCI, parallel ISA, and serialized PCI and ISA signaling. Other miscellaneous system interface terminals are available on the PCI1211 that include:

- Programmable multifunction terminals

- SUSPEND, RI\_OUT/PME (power management control signal)

- SPKROUT

NOTE: The PC Card interface is 68 pins for CardBus and 16-bit PC Cards. In ZV mode 23 pins are used for routing the ZV signals to the VGA controller.

SCPS033A - OCTOBER 1998

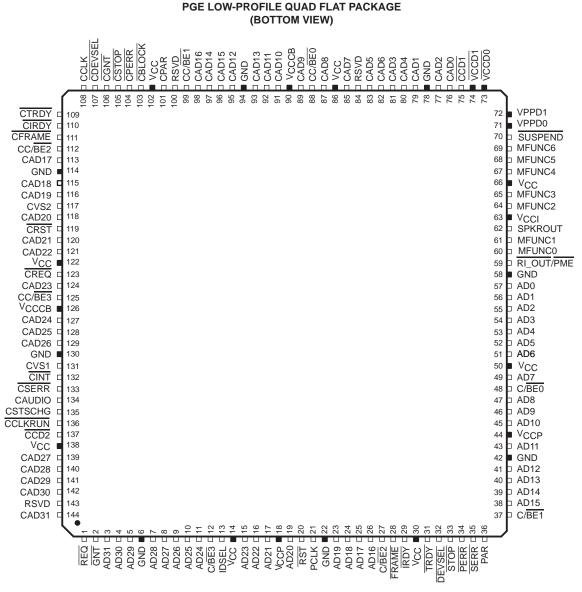

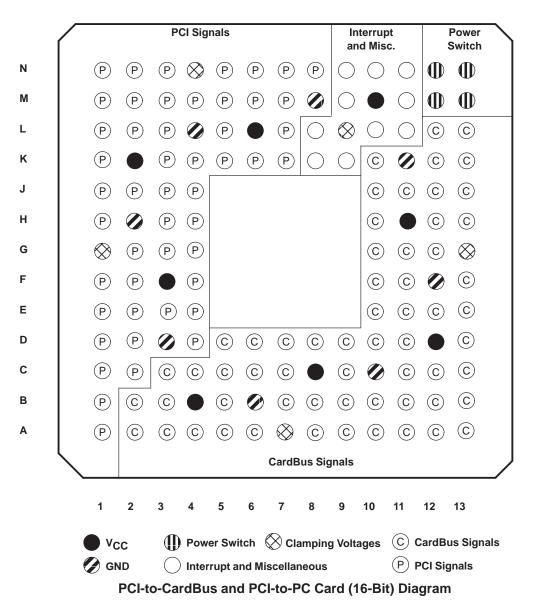

### terminal assignments

PCI-to-CardBus Pin Diagram

SCPS033A - OCTOBER 1998

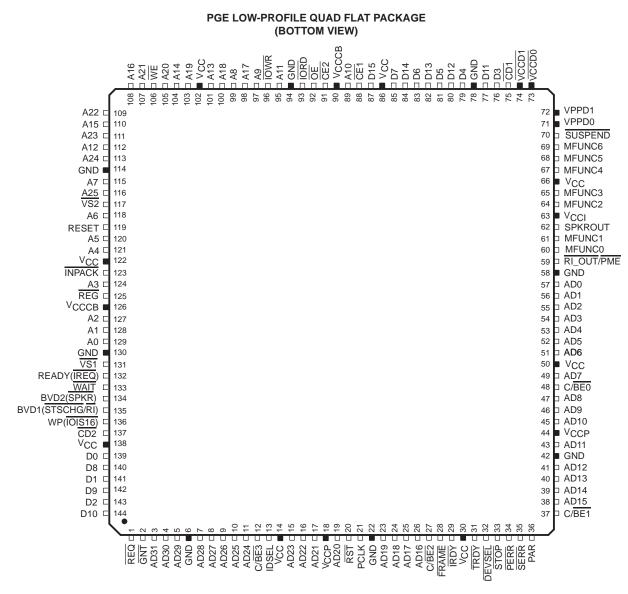

terminal assignments (continued)

PCI-to-PC Card (16-Bit) Diagram

SCPS033A - OCTOBER 1998

### terminal assignments (continued)

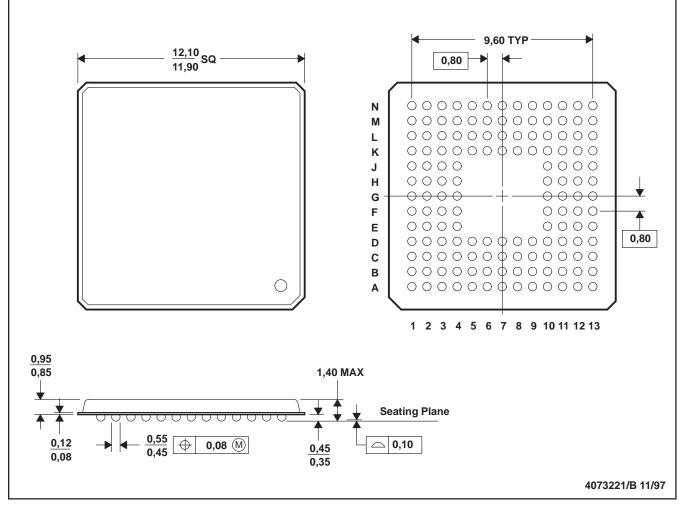

#### GGU BALL GRID ARRAY PACKAGE (BOTTOM VIEW)

### signal names and terminal assignments

Signal names and their terminal assignments are shown in Table 1 through Table 4. Table 1 and Table 2 show the terminal assignments for the CardBus PC Card, and Table 3 and Table 4 show the terminal assignments for the 16-bit PC Card. Table 2 and Table 4 show the CardBus PC Card and the 16-bit PC Card terminals sorted alphanumerically by the signal name and its associated terminal number.

SCPS033A - OCTOBER 1998

|     |     | Table 1. Ca | rdBus | PC C | ard Signal Nam | ies – S | orted | by BGA Termi | nal Nu | ımber <sup>†</sup> |             |

|-----|-----|-------------|-------|------|----------------|---------|-------|--------------|--------|--------------------|-------------|

| PIN | NO. |             | PIN   | NO.  |                | PIN     | NO.   |              | PIN    | NO.                |             |

| GGU | PGE | SIGNAL NAME | GGU   | PGE  | SIGNAL NAME    | GGU     | PGE   | SIGNAL NAME  | GGU    | PGE                | SIGNAL NAME |

| A1  | 1   | REQ         | C11   | 106  | CGNT           | G10     | 92    | CAD11        | L4     | 42                 | GND         |

| A2  | 143 | RSVD        | C12   | 105  | CSTOP          | G11     | 91    | CAD10        | L5     | 46                 | AD9         |

| A3  | 140 | CAD28       | C13   | 104  | CPERR          | G12     | 89    | CAD9         | L6     | 50                 | Vcc         |

| A4  | 137 | CCD2        | D1    | 8    | AD27           | G13     | 90    | VCCCB        | L7     | 55                 | AD2         |

| A5  | 133 | CSERR       | D2    | 7    | AD28           | H1      | 21    | PCLK         | L8     | 59                 | RI_OUT/PME  |

| A6  | 129 | CAD26       | D3    | 6    | GND            | H2      | 22    | GND          | L9     | 63                 | VCCI        |

| A7  | 126 | VCCCB       | D4    | 5    | AD29           | H3      | 23    | AD19         | L10    | 67                 | MFUNC4      |

| A8  | 124 | CAD23       | D5    | 136  | CCLKRUN        | H4      | 24    | AD18         | L11    | 70                 | SUSPEND     |

| A9  | 120 | CAD21       | D6    | 132  | CINT           | H10     | 85    | CAD7         | L12    | 75                 | CCD1        |

| A10 | 116 | CAD19       | D7    | 128  | CAD25          | H11     | 86    | VCC          | L13    | 76                 | CAD0        |

| A11 | 112 | CC/BE2      | D8    | 121  | CAD22          | H12     | 87    | CAD8         | M1     | 35                 | SERR        |

| A12 | 110 | CIRDY       | D9    | 117  | CVS2           | H13     | 88    | CC/BE0       | M2     | 36                 | PAR         |

| A13 | 109 | CTRDY       | D10   | 113  | CAD17          | J1      | 25    | AD17         | M3     | 39                 | AD14        |

| B1  | 2   | GNT         | D11   | 103  | CBLOCK         | J2      | 26    | AD16         | M4     | 43                 | AD11        |

| B2  | 144 | CAD31       | D12   | 102  | VCC            | J3      | 27    | C/BE2        | M5     | 47                 | AD8         |

| B3  | 141 | CAD29       | D13   | 101  | CPAR           | J4      | 28    | FRAME        | M6     | 51                 | AD6         |

| B4  | 138 | VCC         | E1    | 12   | C/BE3          | J10     | 81    | CAD3         | M7     | 53                 | AD4         |

| B5  | 134 | CAUDIO      | E2    | 11   | AD24           | J11     | 82    | CAD6         | M8     | 58                 | GND         |

| B6  | 130 | GND         | E3    | 10   | AD25           | J12     | 83    | CAD5         | M9     | 62                 | SPKROUT     |

| B7  | 125 | CC/BE3      | E4    | 9    | AD26           | J13     | 84    | RSVD         | M10    | 66                 | VCC         |

| B8  | 123 | CREQ        | E10   | 100  | RSVD           | K1      | 29    | IRDY         | M11    | 69                 | MFUNC6      |

| B9  | 119 | CRST        | E11   | 99   | CC/BE1         | K2      | 30    | VCC          | M12    | 72                 | VPPD1       |

| B10 | 115 | CAD18       | E12   | 98   | CAD16          | K3      | 31    | TRDY         | M13    | 74                 | VCCD1       |

| B11 | 111 | CFRAME      | E13   | 97   | CAD14          | K4      | 41    | AD12         | N1     | 37                 | C/BE1       |

| B12 | 108 | CCLK        | F1    | 16   | AD22           | K5      | 45    | AD10         | N2     | 38                 | AD15        |

| B13 | 107 | CDEVSEL     | F2    | 15   | AD23           | K6      | 49    | AD7          | N3     | 40                 | AD13        |

| C1  | 4   | AD30        | F3    | 14   | VCC            | K7      | 56    | AD1          | N4     | 44                 | VCCP        |

| C2  | 3   | AD31        | F4    | 13   | IDSEL          | K8      | 60    | MFUNC0       | N5     | 48                 | C/BE0       |

| C3  | 142 | CAD30       | F10   | 96   | CAD15          | K9      | 64    | MFUNC2       | N6     | 52                 | AD5         |

| C4  | 139 | CAD27       | F11   | 95   | CAD12          | K10     | 77    | CAD2         | N7     | 54                 | AD3         |

| C5  | 135 | CSTSCHG     | F12   | 94   | GND            | K11     | 78    | GND          | N8     | 57                 | AD0         |

| C6  | 131 | CVS1        | F13   | 93   | CAD13          | K12     | 79    | CAD1         | N9     | 61                 | MFUNC1      |

| C7  | 127 | CAD24       | G1    | 18   | VCCP           | K13     | 80    | CAD4         | N10    | 65                 | MFUNC3      |

| C8  | 122 | VCC         | G2    | 17   | AD21           | L1      | 32    | DEVSEL       | N11    | 68                 | MFUNC5      |

| C9  | 118 | CAD20       | G3    | 19   | AD20           | L2      | 33    | STOP         | N12    | 71                 | VPPD0       |

| C10 | 114 | GND         | G4    | 20   | RST            | L3      | 34    | PERR         | N13    | 73                 | VCCD0       |

<sup>†</sup> The PGE (LQFP) pin numbers are shown also.

SCPS033A - OCTOBER 1998

|             | PIN | NO. |             | PIN | NO. |             | PIN | NO. |                 | PIN | NO. |

|-------------|-----|-----|-------------|-----|-----|-------------|-----|-----|-----------------|-----|-----|

| SIGNAL NAME | PGE | GGU | SIGNAL NAME | PGE | GGU | SIGNAL NAME | PGE | GGU | SIGNAL NAME     | PGE | GGU |

| AD0         | 57  | N8  | CAD0        | 76  | L13 | CC/BE2      | 112 | A11 | MFUNC2          | 64  | K9  |

| AD1         | 56  | K7  | CAD1        | 79  | K12 | CC/BE3      | 125 | B7  | MFUNC3          | 65  | N10 |

| AD2         | 55  | L7  | CAD2        | 77  | K10 | CCLK        | 108 | B12 | MFUNC4          | 67  | L10 |

| AD3         | 54  | N7  | CAD3        | 81  | J10 | CCD1        | 75  | L12 | MFUNC5          | 68  | N11 |

| AD4         | 53  | M7  | CAD4        | 80  | K13 | CCD2        | 137 | A4  | MFUNC6          | 69  | M11 |

| AD5         | 52  | N6  | CAD5        | 83  | J12 | CCLKRUN     | 136 | D5  | PAR             | 36  | M2  |

| AD6         | 51  | M6  | CAD6        | 82  | J11 | CDEVSEL     | 107 | B13 | PCLK            | 21  | H1  |

| AD7         | 49  | K6  | CAD7        | 85  | H10 | CFRAME      | 111 | B11 | PERR            | 34  | L3  |

| AD8         | 47  | M5  | CAD8        | 87  | H12 | CGNT        | 106 | C11 | REQ             | 1   | A1  |

| AD9         | 46  | L5  | CAD9        | 89  | G12 | CINT        | 132 | D6  | RI_OUT/PME      | 59  | L8  |

| AD10        | 45  | K5  | CAD10       | 91  | G11 | CIRDY       | 110 | A12 | RST             | 20  | G4  |

| AD11        | 43  | M4  | CAD11       | 92  | G10 | CPAR        | 101 | D13 | SERR            | 35  | M1  |

| AD12        | 41  | K4  | CAD12       | 95  | F11 | CPERR       | 104 | C13 | RSVD            | 84  | E10 |

| AD13        | 40  | N3  | CAD13       | 93  | F13 | CREQ        | 123 | B8  | RSVD            | 100 | J13 |

| AD14        | 39  | M3  | CAD14       | 97  | E13 | CRST        | 119 | B9  | RSVD            | 143 | A2  |

| AD15        | 38  | N2  | CAD15       | 96  | F10 | CSERR       | 133 | A5  | SPKROUT         | 62  | M9  |

| AD16        | 26  | J2  | CAD16       | 98  | E12 | CSTOP       | 105 | C12 | STOP            | 33  | L2  |

| AD17        | 25  | J1  | CAD17       | 113 | D10 | CSTSCHG     | 135 | C5  | SUSPEND         | 70  | L11 |

| AD18        | 24  | H4  | CAD18       | 115 | B10 | CTRDY       | 109 | A13 | TRDY            | 31  | K3  |

| AD19        | 23  | H3  | CAD19       | 116 | A10 | CVS1        | 131 | C6  | VCC             | 14  | F3  |

| AD20        | 19  | G3  | CAD20       | 118 | C9  | CVS2        | 117 | D9  | VCC             | 30  | K2  |

| AD21        | 17  | G2  | CAD21       | 120 | A9  | DEVSEL      | 32  | L1  | V <sub>CC</sub> | 50  | L6  |

| AD22        | 16  | F1  | CAD22       | 121 | D8  | FRAME       | 28  | J4  | VCC             | 66  | M10 |

| AD23        | 15  | F2  | CAD23       | 124 | A8  | GND         | 6   | D3  | VCC             | 86  | H11 |

| AD24        | 11  | E2  | CAD24       | 127 | C7  | GND         | 22  | H2  | VCC             | 102 | D12 |

| AD25        | 10  | E3  | CAD25       | 128 | D7  | GND         | 42  | L4  | Vcc             | 122 | C8  |

| AD26        | 9   | E4  | CAD26       | 129 | A6  | GND         | 58  | M8  | V <sub>CC</sub> | 138 | B4  |

| AD27        | 8   | D1  | CAD27       | 139 | C4  | GND         | 78  | K11 | VCCCB           | 90  | G13 |

| AD28        | 7   | D2  | CAD28       | 140 | A3  | GND         | 94  | F12 | VCCCB           | 126 | A7  |

| AD29        | 5   | D4  | CAD29       | 141 | B3  | GND         | 114 | C10 | VCCD0           | 73  | N13 |

| AD30        | 4   | C1  | CAD30       | 142 | C3  | GND         | 130 | B6  | VCCD1           | 74  | M13 |

| AD31        | 3   | C2  | CAD31       | 144 | B2  | GNT         | 2   | B1  | VCCI            | 63  | L9  |

| C/BE0       | 48  | N5  | CAUDIO      | 134 | B5  | IDSEL       | 13  | F4  | VCCP            | 18  | G1  |

| C/BE1       | 37  | N1  | CBLOCK      | 103 | D11 | IRDY        | 29  | K1  | VCCP            | 44  | N4  |

| C/BE2       | 27  | J3  | CC/BE0      | 88  | H13 | MFUNC0      | 60  | K8  | VPPD0           | 71  | N12 |

| C/BE3       | 12  | E1  | CC/BE1      | 99  | E11 | MFUNC1      | 61  | N9  | VPPD1           | 72  | M12 |

## Table 2. CardBus PC Card Signal Names – Sorted Alphabetically

SCPS033A - OCTOBER 1998

|     |     | Table 3. 16     | -Bit P | C Car | d Signal Name | es – So | orted b | oy BGA Termin | al Nur | nber† |                 |

|-----|-----|-----------------|--------|-------|---------------|---------|---------|---------------|--------|-------|-----------------|

| PIN | NO. |                 | PIN    | NO.   |               | PIN     | NO.     |               | PIN    | NO.   |                 |

| GGU | PGE | SIGNAL NAME     | GGU    | PGE   | SIGNAL NAME   | GGU     | PGE     | SIGNAL NAME   | GGU    | PGE   | SIGNAL NAME     |

| A1  | 1   | REQ             | C11    | 106   | WE            | G10     | 92      | OE            | L4     | 42    | GND             |

| A2  | 143 | D2              | C12    | 105   | A20           | G11     | 91      | CE2           | L5     | 46    | AD9             |

| A3  | 140 | D8              | C13    | 104   | A14           | G12     | 89      | A10           | L6     | 50    | V <sub>CC</sub> |

| A4  | 137 | CD2             | D1     | 8     | AD27          | G13     | 90      | VCCCB         | L7     | 55    | AD2             |

| A5  | 133 | WAIT            | D2     | 7     | AD28          | H1      | 21      | PCLK          | L8     | 59    | RI_OUT/PME      |

| A6  | 129 | A0              | D3     | 6     | GND           | H2      | 22      | GND           | L9     | 63    | VCCI            |

| A7  | 126 | VCCCB           | D4     | 5     | AD29          | H3      | 23      | AD19          | L10    | 67    | MFUNC4          |

| A8  | 124 | A3              | D5     | 136   | WP(IOIS16)    | H4      | 24      | AD18          | L11    | 70    | SUSPEND         |

| A9  | 120 | A5              | D6     | 132   | READY(IREQ)   | H10     | 85      | D7            | L12    | 75    | CD1             |

| A10 | 116 | A25             | D7     | 128   | A1            | H11     | 86      | VCC           | L13    | 76    | D3              |

| A11 | 112 | A12             | D8     | 121   | A4            | H12     | 87      | D15           | M1     | 35    | SERR            |

| A12 | 110 | A15             | D9     | 117   | VS2           | H13     | 88      | CE1           | M2     | 36    | PAR             |

| A13 | 109 | A22             | D10    | 113   | A24           | J1      | 25      | AD17          | M3     | 39    | AD14            |

| B1  | 2   | GNT             | D11    | 103   | A19           | J2      | 26      | AD16          | M4     | 43    | AD11            |

| B2  | 144 | D10             | D12    | 102   | VCC           | J3      | 27      | C/BE2         | M5     | 47    | AD8             |

| B3  | 141 | D1              | D13    | 101   | A13           | J4      | 28      | FRAME         | M6     | 51    | AD6             |

| B4  | 138 | VCC             | E1     | 12    | C/BE3         | J10     | 81      | D5            | M7     | 53    | AD4             |

| B5  | 134 | BVD2(SPKR)      | E2     | 11    | AD24          | J11     | 82      | D13           | M8     | 58    | GND             |

| B6  | 130 | GND             | E3     | 10    | AD25          | J12     | 83      | D6            | M9     | 62    | SPKROUT         |

| B7  | 125 | REG             | E4     | 9     | AD26          | J13     | 84      | D14           | M10    | 66    | V <sub>CC</sub> |

| B8  | 123 | INPACK          | E10    | 100   | A18           | K1      | 29      | IRDY          | M11    | 69    | MFUNC6          |

| B9  | 119 | RESET           | E11    | 99    | A8            | K2      | 30      | VCC           | M12    | 72    | VPPD1           |

| B10 | 115 | A7              | E12    | 98    | A17           | K3      | 31      | TRDY          | M13    | 74    | VCCD1           |

| B11 | 111 | A23             | E13    | 97    | A9            | K4      | 41      | AD12          | N1     | 37    | C/BE1           |

| B12 | 108 | A16             | F1     | 16    | AD22          | K5      | 45      | AD10          | N2     | 38    | AD15            |

| B13 | 107 | A21             | F2     | 15    | AD23          | K6      | 49      | AD7           | N3     | 40    | AD13            |

| C1  | 4   | AD30            | F3     | 14    | VCC           | K7      | 56      | AD1           | N4     | 44    | VCCP            |

| C2  | 3   | AD31            | F4     | 13    | IDSEL         | K8      | 60      | MFUNC0        | N5     | 48    | C/BE0           |

| C3  | 142 | D9              | F10    | 96    | IOWR          | K9      | 64      | MFUNC2        | N6     | 52    | AD5             |

| C4  | 139 | D0              | F11    | 95    | A11           | K10     | 77      | D11           | N7     | 54    | AD3             |

| C5  | 135 | BVD1(STSCHG/RI) | F12    | 94    | GND           | K11     | 78      | GND           | N8     | 57    | AD0             |

| C6  | 131 | VS1             | F13    | 93    | IORD          | K12     | 79      | D4            | N9     | 61    | MFUNC1          |

| C7  | 127 | A2              | G1     | 18    | VCCP          | K13     | 80      | D12           | N10    | 65    | MFUNC3          |

| C8  | 122 | VCC             | G2     | 17    | AD21          | L1      | 32      | DEVSEL        | N11    | 68    | MFUNC5          |

| C9  | 118 | A6              | G3     | 19    | AD20          | L2      | 33      | STOP          | N12    | 71    | VPPD0           |

| C10 | 114 | GND             | G4     | 20    | RST           | L3      | 34      | PERR          | N13    | 73    | VCCD0           |

#### 0 read by DCA To Table 2 46 Bit DC Card Sig . . . . .

<sup>†</sup> The PGE (LQFP) pin numbers are shown also.

SCPS033A - OCTOBER 1998

|             |     | Tab | le 4. 16-Bit PC 0 | Card S | ignal | Names – Sorte | ed Alp | habet | ically           |     |     |

|-------------|-----|-----|-------------------|--------|-------|---------------|--------|-------|------------------|-----|-----|

|             | PIN | NO. |                   | PIN    | NO.   |               | PIN    | NO.   |                  | PIN | NO. |

| SIGNAL NAME | PGE | GGU | SIGNAL NAME       | PGE    | GGU   | SIGNAL NAME   | PGE    | GGU   | SIGNAL NAME      | PGE | GGU |

| A0          | 129 | A6  | AD10              | 45     | K5    | D4            | 79     | K12   | PAR              | 36  | M2  |

| A1          | 128 | D7  | AD11              | 43     | M4    | D5            | 81     | J10   | PCLK             | 21  | H1  |

| A2          | 127 | C7  | AD12              | 41     | K4    | D6            | 83     | J12   | PERR             | 34  | L3  |

| A3          | 124 | A8  | AD13              | 40     | N3    | D7            | 85     | H10   | REQ              | 1   | A1  |

| A4          | 121 | D8  | AD14              | 39     | M3    | D8            | 140    | A3    | READY(IREQ)      | 132 | D6  |

| A5          | 120 | A9  | AD15              | 38     | N2    | D9            | 142    | C3    | REG              | 125 | B7  |

| A6          | 118 | C9  | AD16              | 26     | J2    | D10           | 144    | B2    | RESET            | 119 | B9  |

| A7          | 115 | B10 | AD17              | 25     | J1    | D11           | 77     | K10   | RI_OUT/PME       | 59  | L8  |

| A8          | 99  | E11 | AD18              | 24     | H4    | D12           | 80     | K13   | RST              | 20  | G4  |

| A9          | 97  | E13 | AD19              | 23     | H3    | D13           | 82     | J11   | SERR             | 35  | M1  |

| A10         | 89  | G12 | AD20              | 19     | G3    | D14           | 84     | J13   | SPKROUT          | 62  | M9  |

| A11         | 95  | F11 | AD21              | 17     | G2    | D15           | 87     | H12   | STOP             | 33  | L2  |

| A12         | 112 | A11 | AD22              | 16     | F1    | DEVSEL        | 32     | L1    | SUSPEND          | 70  | L11 |

| A13         | 101 | D13 | AD23              | 15     | F2    | FRAME         | 28     | J4    | TRDY             | 31  | K3  |

| A14         | 104 | C13 | AD24              | 11     | E2    | GND           | 6      | D3    | VCC              | 14  | F3  |

| A15         | 110 | A12 | AD25              | 10     | E3    | GND           | 22     | H2    | VCC              | 30  | K2  |

| A16         | 108 | B12 | AD26              | 9      | E4    | GND           | 42     | L4    | VCC              | 50  | L6  |

| A17         | 98  | E12 | AD27              | 8      | D1    | GND           | 58     | M8    | Vcc              | 66  | M10 |

| A18         | 100 | E10 | AD28              | 7      | D2    | GND           | 78     | K11   | VCC              | 86  | H11 |

| A19         | 103 | D11 | AD29              | 5      | D4    | GND           | 94     | F12   | Vcc              | 102 | D12 |

| A20         | 105 | C12 | AD30              | 4      | C1    | GND           | 114    | C10   | VCC              | 122 | C8  |

| A21         | 107 | B13 | AD31              | 3      | C2    | GND           | 130    | B6    | Vcc              | 138 | B4  |

| A22         | 109 | A13 | BVD1(STSCHG/RI)   | 135    | C5    | GNT           | 2      | B1    | VCCCB            | 90  | G13 |

| A23         | 111 | B11 | BVD2(SPKR)        | 134    | B5    | IDSEL         | 13     | F4    | VCCCB            | 126 | A7  |

| A24         | 113 | D10 | C/BE0             | 48     | N5    | INPACK        | 123    | B8    | VCCD0            | 73  | N13 |

| A25         | 116 | A10 | C/BE1             | 37     | N1    | IORD          | 93     | F13   | VCCD1            | 74  | M13 |

| AD0         | 57  | N8  | C/BE2             | 27     | J3    | IOWR          | 96     | F10   | VCCI             | 63  | L9  |

| AD1         | 56  | K7  | C/BE3             | 12     | E1    | IRDY          | 29     | K1    | VCCP             | 18  | G1  |

| AD2         | 55  | L7  | CD1               | 75     | L12   | MFUNC0        | 60     | K8    | V <sub>CCP</sub> | 44  | N4  |

| AD3         | 54  | N7  | CD2               | 137    | A4    | MFUNC1        | 61     | N9    | VPPD0            | 71  | N12 |

| AD4         | 53  | M7  | CE1               | 88     | H13   | MFUNC2        | 64     | K9    | VPPD1            | 72  | M12 |

| AD5         | 52  | N6  | CE2               | 91     | G11   | MFUNC3        | 65     | N10   | VS1              | 131 | C6  |

| AD6         | 51  | M6  | D0                | 139    | C4    | MFUNC4        | 67     | L10   | VS2              | 117 | D9  |

| AD7         | 49  | K6  | D1                | 141    | B3    | MFUNC5        | 68     | N11   | WAIT             | 133 | A5  |

| AD8         | 47  | M5  | D2                | 143    | A2    | MFUNC6        | 69     | M11   | WE               | 106 | C11 |

| AD9         | 46  | L5  | D3                | 76     | L13   | OE            | 92     | G10   | WP(IOIS16)       | 136 | D5  |

SCPS033A - OCTOBER 1998

### **Terminal Functions**

The terminals are grouped in tables by functionality, such as PCI system function, power-supply function, etc. The terminal numbers are also listed for convenient reference. Terminal numbers are shown for both the PGE LQF package and the GGU ball grid array package.

### power supply

|                  | TERMINAL                             | -                                    | FUNCTION                                                                                      |  |  |  |

|------------------|--------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| NAME             | PGE NUMBER                           | GGU NUMBER                           | FONCTION                                                                                      |  |  |  |

| GND              | 6, 22, 42, 58, 78, 94, 114, 130      | B6, C10, D3, F12, H2, K11, L4,<br>M8 | Device ground terminals                                                                       |  |  |  |

| Vcc              | 14, 30, 50, 66, 86, 102, 122,<br>138 | B4, C8, D12, F3, H11, K2, L6,<br>M10 | Power supply terminal for core logic (3.3 V)                                                  |  |  |  |

| VCCCB            | 90, 126                              | A7, G13                              | Clamping voltage for PC Card interface. Indicates card signaling environment of 5 V or 3.3 V. |  |  |  |

| VCCI             | 63                                   | L9                                   | Clamping voltage for multifunction terminals (5 V or 3.3 V)                                   |  |  |  |

| V <sub>CCP</sub> | 18, 44                               | G1, N4                               | Clamping voltage for PCI signaling (5 V or 3.3 V)                                             |  |  |  |

### PC Card power switch

| TE             | TERMINAL      |              | RMINAL |                                                                               | RMINAL |  | RMINAL |  |  |  |  |  | I/O |  |

|----------------|---------------|--------------|--------|-------------------------------------------------------------------------------|--------|--|--------|--|--|--|--|--|-----|--|

| NAME           | PIN NU<br>PGE | IMBER<br>GGU | TYPE   | FUNCTION                                                                      |        |  |        |  |  |  |  |  |     |  |

| VCCD0<br>VCCD1 | 73<br>74      | N13<br>M13   |        | Logic controls to the TPS2211 PC Card power interface switch to control AVCC. |        |  |        |  |  |  |  |  |     |  |

| VPPD0<br>VPPD1 | 71<br>72      | N12<br>M12   | 0      | Logic controls to the TPS2211 PC Card power interface switch to control AVPP. |        |  |        |  |  |  |  |  |     |  |

## PCI system

| TE   | RMINAL |       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|--------|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | PIN NU | IMBER | I/O<br>TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | PGE    | GGU   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PCLK | 21     | H1    | Ι           | PCI bus clock. PCLK provides timing for all transactions on the PCI bus. All PCI signals are sampled at the rising edge of PCLK.                                                                                                                                                                                                                                                                                                                                                                     |

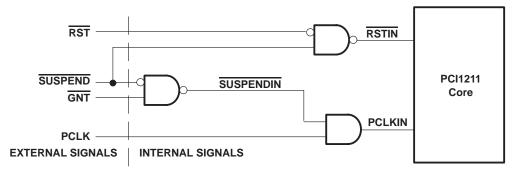

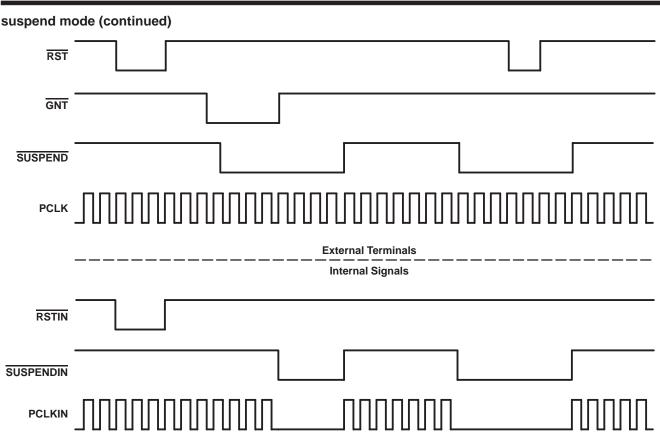

| RST  | 20     | G4    | I           | PCI reset. When the PCI bus reset is asserted, RST causes the PCI1211 to place all output buffers in a high-impedance state and reset all internal registers. When RST is asserted, the device is completely nonfunctional. After RST is deasserted, the PCI1211 is in its default state.<br>When SUSPEND and RST are asserted, the device is protected from RST clearing the internal registers. All outputs are placed in a high-impedance state, but the contents of the registers are preserved. |

SCPS033A - OCTOBER 1998

## **Terminal Functions (Continued)**

## PCI address and data

| TE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RMINAL                                                                                                                                      |                                                                                                                                                        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PIN NU                                                                                                                                      | JMBER                                                                                                                                                  | I/O<br>TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PGE                                                                                                                                         | GGU                                                                                                                                                    |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AD31<br>AD30<br>AD29<br>AD28<br>AD27<br>AD26<br>AD25<br>AD24<br>AD23<br>AD22<br>AD21<br>AD20<br>AD19<br>AD19<br>AD18<br>AD17<br>AD16<br>AD15<br>AD14<br>AD13<br>AD14<br>AD13<br>AD12<br>AD11<br>AD10<br>AD9<br>AD8<br>AD7<br>AD6<br>AD5<br>AD4<br>AD5<br>AD4<br>AD3<br>AD2<br>AD1<br>AD2<br>AD1<br>AD2<br>AD1<br>AD10<br>AD9<br>AD8<br>AD7<br>AD6<br>AD1<br>AD10<br>AD9<br>AD8<br>AD7<br>AD10<br>AD10<br>AD11<br>AD10<br>AD10<br>AD11<br>AD10<br>AD11<br>AD10<br>AD11<br>AD10<br>AD11<br>AD10<br>AD11<br>AD10<br>AD11<br>AD10<br>AD11<br>AD10<br>AD11<br>AD11 | $\begin{array}{c}3\\4\\5\\7\\8\\9\\10\\11\\15\\16\\17\\9\\23\\24\\25\\26\\39\\40\\41\\35\\46\\47\\9\\51\\52\\53\\54\\55\\56\\57\end{array}$ | $\begin{array}{c} C2\\ C1\\ D4\\ D2\\ D1\\ E4\\ E3\\ E2\\ F1\\ G2\\ G3\\ H4\\ J1\\ J2\\ N3\\ K4\\ K5\\ L5\\ K6\\ M6\\ N7\\ L7\\ K7\\ N8\\ \end{array}$ | 1/0         | PCI address/data bus. These signals make up the multiplexed PCI address and data bus on the primary interface. During the address phase of a primary bus PCI cycle, AD31–AD0 contain a 32-bit address or other destination information. During the data phase, AD31–AD0 contain data.                                                                                                                                                                                                                   |

| C/ <u>BE3</u><br>C/ <u>BE2</u><br>C/ <u>BE1</u><br>C/BE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12<br>27<br>37<br>48                                                                                                                        | E1<br>J3<br>N1<br>N5                                                                                                                                   | I/O         | PCI bus commands and byte enables. These signals are multiplexed on the same PCI terminals. During the address phase of a primary bus PCI cycle, C/BE3–C/BE0 define the bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte paths of the full 32-bit data bus carry meaningful data. C/BE0 applies to byte 0 (AD7–AD0), C/BE1 applies to byte 1 (AD15–AD8), C/BE2 applies to byte 2 (AD23–AD16), and C/BE3 applies to byte 3 (AD31–AD24). |

| PAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36                                                                                                                                          | M2                                                                                                                                                     | I/O         | PCI bus parity. In <u>all PCI bus</u> read and write cycles, the PCI1211 calculates even parity across the AD31–AD0 and C/BE3–C/BE0 buses. As an initiator during PCI cycles, the PCI1211 outputs this parity indicator with a one-PCLK delay. As a target during PCI cycles, the calculated parity is compared to the initiator's parity indicator. A compare error results in the assertion of a parity error (PERR).                                                                                 |

SCPS033A - OCTOBER 1998

## **Terminal Functions (Continued)**

## PCI interface control

| TER    | TERMINAL |       |             |                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|----------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | PIN NU   | JMBER | I/O<br>TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                             |

| NAME   | PGE      | GGU   |             |                                                                                                                                                                                                                                                                                                                                                                                      |

| DEVSEL | 32       | L1    | I/O         | PCI device select. The PCI1211 asserts DEVSEL to claim a PCI cycle as the target device. As a PCI initiator on the bus, the PCI1211 monitors DEVSEL until a target responds. If no target responds before timeout occurs, the PCI1211 terminates the cycle with an initiator abort.                                                                                                  |

| FRAME  | 28       | J4    | I/O         | PCI cycle frame. FRAME is driven by the initiator of a bus cycle. FRAME is asserted to indicate that a bus transaction is beginning, and data transfers continue while this signal is asserted. When FRAME is deasserted, the PCI bus transaction is in the final data phase.                                                                                                        |

| GNT    | 2        | B1    | I           | PCI bus grant. GNT is driven by the PCI bus arbiter to grant the PCI1211 access to the PCI bus after the current data transaction has completed. GNT may or may not follow a PCI bus request, depending on the PCI bus parking algorithm.                                                                                                                                            |

| IDSEL  | 13       | F4    | I           | Initialization device select. IDSEL selects the PCI1211 during configuration space accesses. IDSEL can be connected to one of the upper 24 PCI address lines on the PCI bus.                                                                                                                                                                                                         |

| IRDY   | 29       | K1    | I/O         | PCI initiator ready. IRDY indicates the PCI bus initiator's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of PCLK where both IRDY and TRDY are asserted. Until IRDY and TRDY are both sampled asserted, wait states are inserted.                                                                                        |

| PERR   | 34       | L3    | I/O         | PCI parity error indicator. PERR is driven by a PCI device to indicate that calculated parity does not match PAR when PERR is enabled through bit 6 of the command register.                                                                                                                                                                                                         |

| REQ    | 1        | A1    | 0           | PCI bus request. REQ is asserted by the PCI1211 to request access to the PCI bus as an initiator.                                                                                                                                                                                                                                                                                    |

| SERR   | 35       | M1    | 0           | PCI system error. SERR is an output that is pulsed from the PCI1211 when enabled through the command register indicating a system error has occurred. The PCI1211 need not be the target of the PCI cycle to assert this signal. When SERR is enabled in the control register, this signal also pulses, indicating that an address parity error has occurred on a CardBus interface. |

| STOP   | 33       | L2    | I/O         | PCI cycle stop signal. STOP is driven by a PCI target to request the initiator to stop the current PCI bus transaction. STOP is used for target disconnects and is commonly asserted by target devices that do not support burst data transfers.                                                                                                                                     |

| TRDY   | 31       | K3    | I/O         | PCI target ready. TRDY indicates the primary bus target's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of PCLK when both IRDY and TRDY are asserted. Until both IRDY and TRDY are asserted, wait states are inserted.                                                                                                   |

SCPS033A - OCTOBER 1998

## **Terminal Functions (Continued)**

## multifunction and miscellaneous pins

| TERM       | TERMINAL      |              |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|---------------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | PIN NU<br>PGE | JMBER<br>GGU | I/O<br>TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

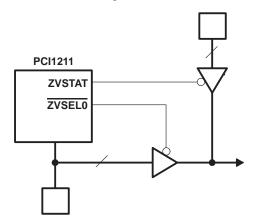

| MFUNC0     | 60            | К8           | I/O         | Multifunction Terminal 0. MFUNC0 can be configured as parallel PCI interrupt INTA, GPI0, GPO0, GPE, socket activity LED output, ZV output select, CardBus audio PWM, or a parallel IRQ. Refer to the <i>multifunction routing register</i> description on page 61 for configuration details.                                                                                                                                                                                                                                                                                                                                                                                                          |

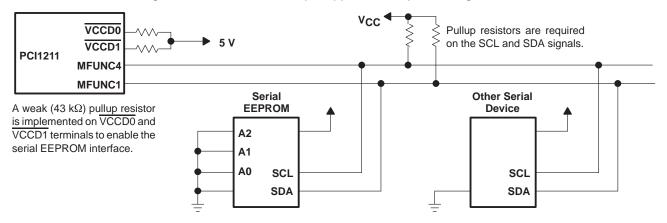

| MFUNC1     | 61            | N9           | I/O         | Multifunction Terminal 1. MFUNC1 can be configured as GPI1, GPO1, GPE, socket activity LED output, ZV output select, CardBus audio PWM, or a parallel IRQ. Refer to the <i>multifunction routing register</i> description on page 61 for configuration details.<br>Serial Data (SDA). When the serial bus mode is implemented by pulling up the SCA and SCL terminals, the MFUNC1 terminal provides the SDA signaling. The two-pin serial interface is used to load the subsystem identification and other register defaults from an EEPROM after a PCI reset. Refer to the <i>serial bus interface protocol</i> description on page 30 for details on other serial bus applications.                 |

| MFUNC2     | 64            | K9           | I/O         | Multifunction Terminal 2. MFUNC2 can be configured as PC/PCI DMA Request, GPI2, GPO2, socket activity LED output, ZV output select, CardBus audio PWM, GPE, RI_OUT, or a parallel IRQ. Refer to the <i>multifunction routing register</i> description on page 61 for configuration details.                                                                                                                                                                                                                                                                                                                                                                                                           |

| MFUNC3     | 65            | N10          | I/O         | Multifunction Terminal 3. MFUNC3 can be configured as a parallel IRQ or the serialized interrupt signal IRQSER. Refer to the <i>multifunction routing register</i> description on page 61 for configuration details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MFUNC4     | 67            | L10          | I/O         | Multifunction Terminal 4. MFUNC4 can be configured as PCI LOCK, GPI3, GPO3, socket activity LED, RI_OUT output, ZV output select, CardBus audio PWM, GPE, or a parallel IRQ. Refer to the <i>multifunction routing register</i> description on page 61 for configuration details.<br>Serial Clock (SCL). When the serial bus mode is implemented by pulling the SDA and SCL terminals, the MFUNC4 terminal provides the SCL signaling. The two-pin serial interface is used to load the subsystem identification and other register defaults from an EEPROM after a PCI reset. Refer to the <i>serial bus interface protocol</i> description on page 30 for details on other serial bus applications. |

| MFUNC5     | 68            | N11          | I/O         | Multifunction Terminal 5. MFUNC5 can be configured as PC/PCI DMA Grant, GPI4, GPO4, socket activity LED output, ZV output select, CardBus audio PWM, GPE, or a parallel IRQ. Refer to the <i>multifunction routing register</i> description on page 61 for configuration details.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MFUNC6     | 69            | M11          | I/O         | Multifunction Terminal 6. MFUNC6 can be configured as a PCI CLKRUN or a parallel IRQ. Refer to the <i>multifunction routing register</i> description on page 61 for configuration details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

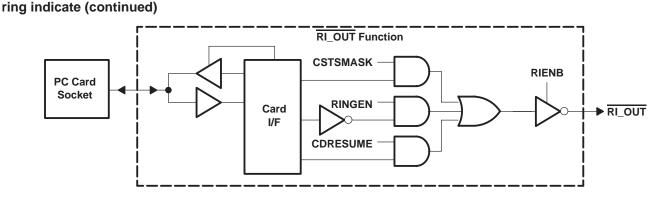

| RI_OUT/PME | 59            | L8           | 0           | $\frac{\text{Ring}}{\text{PME}}$ Indicate Out and Power Management Event Output. Provides output for either $\overline{\text{RI}_{OUT}}$ or $\overline{\text{PME}}$ signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SUSPEND    | 70            | L11          | I           | Suspend. $\overline{\text{SUSPEND}}$ is used to protect the internal registers from clearing when the $\overline{\text{RST}}$ signal is asserted. See <i>suspend mode</i> on page 39 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

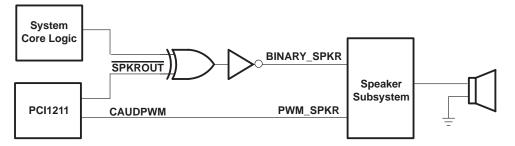

| SPKROUT    | 62            | M9           | ο           | Speaker output. SPKROUT is the output to the host system that can carry SPKR or CAUDIO through the PCI1211 from the PC Card interface. SPKROUT is driven as the exclusive-OR combination of card SPKR//CAUDIO inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

SCPS033A - OCTOBER 1998

## **Terminal Functions (Continued)**

The address and data and interface control terminals for the 16-bit PC Card are shown in the following two tables.

### 16-bit PC Card address and data

| Т                                                                                                                                                                        | ERMINAL                                                                                                                                                                       | -                                                                                                                                                                    |             |                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------|

|                                                                                                                                                                          | PIN NU                                                                                                                                                                        | IMBER                                                                                                                                                                | I/O<br>TYPE | FUNCTION                                                                        |

| NAME                                                                                                                                                                     | PGE                                                                                                                                                                           | GGU                                                                                                                                                                  | IIFE        |                                                                                 |

| A25<br>A24<br>A23<br>A22<br>A21<br>A20<br>A19<br>A18<br>A17<br>A16<br>A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | 116<br>113<br>111<br>109<br>107<br>105<br>103<br>100<br>98<br>108<br>110<br>104<br>101<br>112<br>95<br>89<br>97<br>99<br>115<br>118<br>120<br>121<br>124<br>127<br>128<br>129 | A10<br>D10<br>B11<br>A13<br>C12<br>D11<br>E10<br>E12<br>B12<br>A12<br>C13<br>D13<br>A11<br>F11<br>G12<br>E13<br>E11<br>B10<br>C9<br>A9<br>D8<br>A8<br>C7<br>D7<br>A6 | 0           | PC Card address. 16-bit PC Card address lines. A25 is the most-significant bit. |

| D15<br>D14<br>D13<br>D12<br>D11<br>D10<br>D9<br>D8<br>D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0                                                                       | 87<br>84<br>82<br>80<br>77<br>144<br>142<br>140<br>85<br>83<br>81<br>79<br>76<br>143<br>141<br>139                                                                            | H12<br>J13<br>J11<br>K13<br>K10<br>B2<br>C3<br>A3<br>H10<br>J12<br>J10<br>K12<br>L13<br>A2<br>B3<br>C4                                                               | I/O         | PC Card data. 16-bit PC Card data lines. D15 is the most-significant bit.       |

SCPS033A - OCTOBER 1998

## **Terminal Functions (Continued)**

## 16-bit PC Card interface control

| TERMINAL            |           |            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------------|-----------|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                | PIN NU    | JMBER      | I/O<br>TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | PGE       | GGU        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| BVD1<br>(STSCHG/RI) | 135       | C5         | I           | Battery voltage detect 1. BVD1 is generated by 16-bit memory PC Cards that include batteries.<br>BVD1 is used with BVD2 as an indication of the condition of the batteries on a memory PC Card.<br>Both BVD1 and BVD2 are kept high when the battery is good. When BVD2 is low and BVD1 is high,<br>the battery is weak and should be replaced. When BVD1 is low, the battery is no longer serviceable<br>and the data in the memory PC Card is lost. See <i>ExCA card status-change interrupt configuration</i><br><i>register</i> on page 89 for enable bits. See <i>ExCA card status-change register</i> on page 88 and the<br><i>ExCA interface status register</i> on page 85 for the status bits for this signal.<br>Status change. STSCHG is used to alert the system to a change in the READY, write protect, or |  |

|                     |           |            |             | battery voltage dead condition of a 16-bit I/O PC Card.<br>Ring indicate. $\overline{RI}$ is used by 16-bit modem cards to indicate a ring detection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| BVD2<br>(SPKR)      | 134       | B5         | I           | <ul> <li>Ring indicate. RI is used by 16-bit modem cards to indicate a ring detection.</li> <li>Battery voltage detect 2. BVD2 is generated by 16-bit memory PC Cards that include batteries.</li> <li>BVD2 is used with BVD1 as an indication of the condition of the batteries on a memory PC Card.</li> <li>Both BVD1 and BVD2 are high when the battery is good. When BVD2 is low and BVD1 is high, the battery is weak and should be replaced. When BVD1 is low, the battery is no longer serviceable and the data in the memory PC Card is lost. See <i>ExCA card status-change interrupt configuration register</i> on page 89 for enable bits. See <i>ExCA card status-change register</i> on page 88 and the <i>interface status register</i> on page 85 for the status bits for this signal.</li> </ul>        |  |

|                     |           |            |             | Speaker. SPKR is an optional binary audio signal available only when the card and socket have<br>been configured for the 16-bit I/O interface. The audio signals from cards A and B are combined<br>by the PCI1211 and are output on SPKROUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                     |           |            |             | DMA request. BVD2 can be used as the DMA request signal during DMA operations to a 16-bit PC Card that supports DMA. The PC Card asserts BVD2 to indicate a request for a DMA operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| CD1<br>CD2          | 75<br>137 | L12<br>A4  | I           | PC Card detect 1 and PC Card detect 2. CD1 and CD2 are internally connected to ground on the PC Card. When a PC Card is inserted into a socket, CD1 and CD2 are pulled low. For signal status, see <i>interface status register</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| CE1<br>CE2          | 88<br>91  | H13<br>G11 | 0           | Card enable 1 and card enable 2. CE1 and CE2 enable even- and odd-numbered address bytes. CE1 enables even-numbered address bytes, and CE2 enables odd-numbered address bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| INPACK              | 123       | B8         | I           | Input acknowledge. INPACK is asserted by the PC Card when it can respond to an I/O read cycle at the current address.<br>DMA request. INPACK can be used as the DMA request signal during DMA operations from a 16-bit PC Card that supports DMA. If used as a strobe, the PC Card asserts this signal to indicate a request for a DMA operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| ĪORD                | 93        | F13        | 0           | I/O read. IORD is asserted by the PCI1211 to enable 16-bit I/O PC Card data output during host I/O read cycles.<br>DMA write. IORD is used as the DMA write strobe during DMA operations from a 16-bit PC Card that supports DMA. The PCI1211 asserts IORD during DMA transfers from the PC Card to host memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| IOWR                | 96        | F10        | 0           | I/O write. IOWR is driven low by the PCI1211 to strobe write data into 16-bit I/O PC Cards during host I/O write cycles.<br>DMA read. IOWR is used as the DMA write strobe during DMA operations from a 16-bit PC Card that supports DMA. The PCI1211 asserts IOWR during transfers from host memory to the PC Card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| ŌĒ                  | 92        | G10        | 0           | Output enable. $\overline{\text{OE}}$ is driven low by the PCI1211 to enable 16-bit memory PC Card data output during host memory read cycles.<br>DMA terminal count. $\overline{\text{OE}}$ is used as terminal count (TC) during DMA operations to a 16-bit PC Card that supports DMA. The PCI1211 asserts $\overline{\text{OE}}$ to indicate TC for a DMA write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

SCPS033A - OCTOBER 1998

## **Terminal Functions (Continued)**

# 16-bit PC Card interface control (continued)

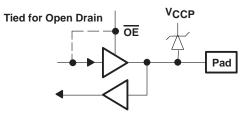

| TERMINAL        |            |              |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |