- PCI Power Management Compliant

- ACPI 1.0 Compliant

- Supports PCI Local Bus Specification 2.1 and PCI-to-PCI Bridge Specification 1.0

- 3.3-V Core Logic With Universal PCI Interfaces Compatible With 3.3-V and 5-V PCI Signaling Environments

- Supports Two 32-Bit, 33-MHz PCI Buses

- Provides Internal Arbitration for Up to Six Secondary Bus Masters With Programmable Control

- Provides Six Secondary PCI Bus Clock Outputs

- Supports Burst Transfers to Maximize Data Throughput on Both PCI Buses

- Provides Two Extension Windows

- EEPROM Interface for Loading Texas Instruments (TI™) Subsystem ID and Subsystem Vendor ID

- Four Primary and Four Secondary General-Purpose I/Os

- Secondary Positive Decode

- Independent Read and Write Buffers for Each Direction

- Predictable Latency: Compliant With PCI Local Bus Specification 2.1

- External Arbiter Option

- Provides Concurrent Operation

- Serial IRQ Bridging

- Propagates Bus Locking

- Supports PCI Clock Run

- Secondary Bus Driven Low During Reset

- Docking Connect Detects

- PCI Local Bus Specification 2.0-Compliant Device Optimization

- Advanced Submicron, Low-Power CMOS Technology

- Provides VGA/Palette Memory and I/O, and Subtractive Decoding Options

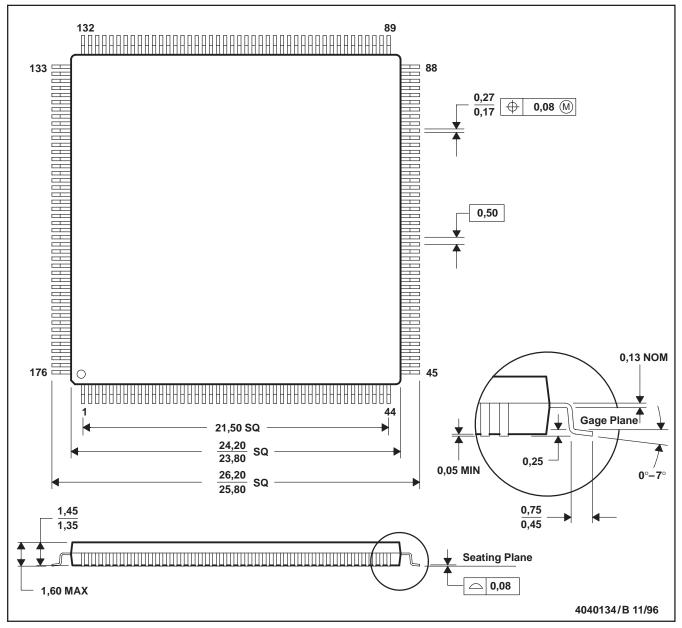

- Packaged in 176-Pin Plastic Quad Flatpack

## Table of Contents

| Description                            | Extension Registers                                   |

|----------------------------------------|-------------------------------------------------------|

| Functional Block Diagram               | Absolute Maximum Ratings 65                           |

| Terminal Assignments                   | Recommended Operating Conditions                      |

| Signal Name/Terminal Number Sort Table | Recommended Operating Conditions for PCI Interface 65 |

| Terminal Functions 5                   | Electrical Characteristics                            |

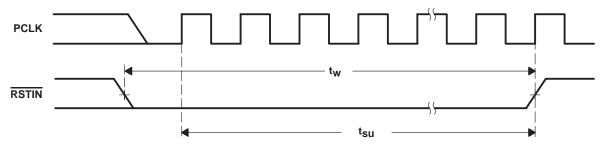

| Architecture 10                        | PCI Clock/Reset Timing Requirements                   |

| Introduction to the PCI2031            | PCI Timing Requirements                               |

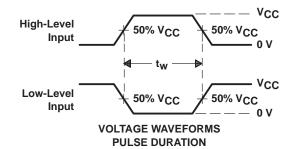

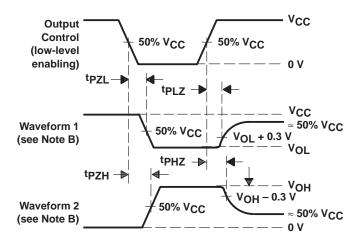

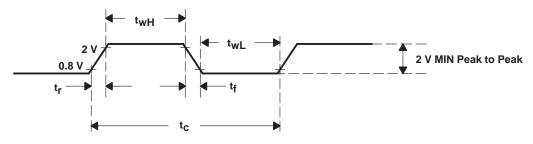

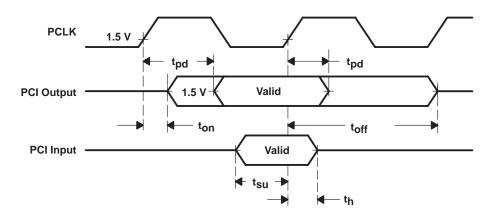

| PCI Commands                           | Parameter Measurement Information 67                  |

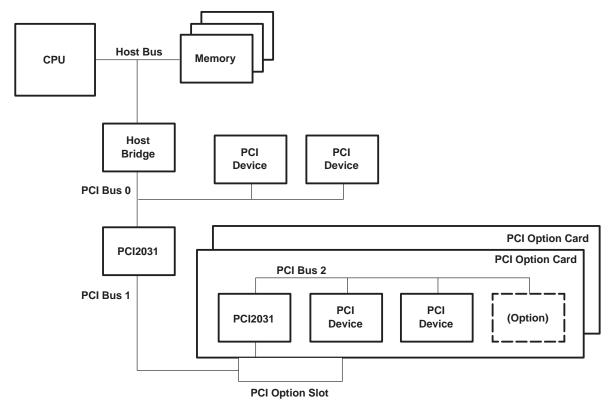

| Typical Applications                   | PCI Bus Parameter Measurement Information             |

| Bridge Configuration Header            | Mechanical Data                                       |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

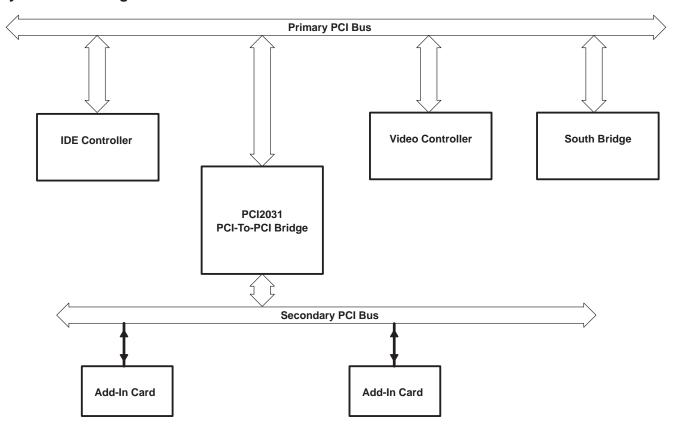

### description

The TI PCI2031 PCI-to-PCI bridge provides a high-performance connection path between two peripheral component interconnect (PCI) buses. Transactions can occur between a master on one PCI bus and a target on another PCI bus. The bridge supports burst-mode transfers to maximize data throughput, and the two bus traffic paths through the bridge act independently.

The PCI2031 bridge is compliant with the PCI Local Bus Specification 2.1, and can be used to overcome the electrical loading limit of ten devices per PCI bus by creating hierarchical buses. Furthermore, add-in cards requiring multiple PCI devices can use the bridge to overcome the electrical loading limit of one PCI device per slot.

The PCI2031 bridge is also compliant with the PCI-to-PCI Bridge Specification 1.0, and implements many additional features that make it an ideal solution for bridging two PCI buses. It can be configured for subtractive decoding, and negative decoding can be disabled on the secondary interface. Two extension windows are also included for special decoding purposes. The serial- and parallel-port addresses can also be programmed for positive decoding on the primary interface. The bridge implements many other features, listed above, that add performance and flexibility.

An advanced CMOS process is utilized to achieve low system-power consumption while operating at PCI clock rates up to 33 MHz.

### system block diagram

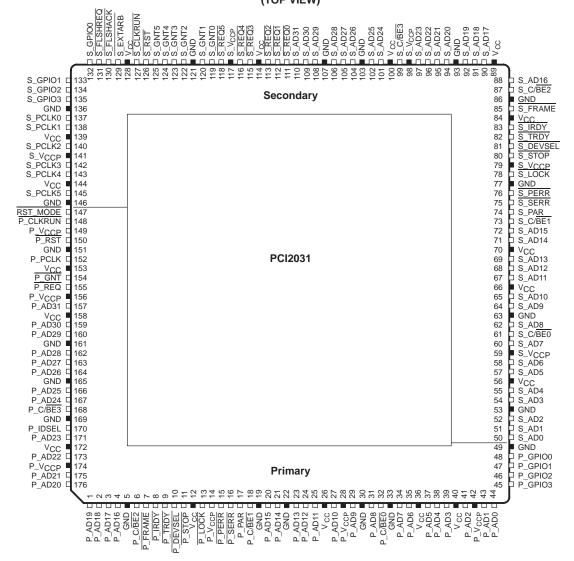

## terminal assignments

#### PGF PACKAGE (TOP VIEW)

**Table 1. Signal Names Sorted by Terminal Number**

| NO. | SIGNAL NAME      | NO. | SIGNAL NAME        | NO. | SIGNAL NAME        | NO. | SIGNAL NAME        |

|-----|------------------|-----|--------------------|-----|--------------------|-----|--------------------|

| 1   | P_AD19           | 45  | P_GPIO3            | 89  | VCC                | 133 | S_GPIO1            |

| 2   | P_AD18           | 46  | P_GPIO2            | 90  | S_AD17             | 134 | S_GPIO2            |

| 3   | P_AD17           | 47  | P_GPIO1            | 91  | S_AD18             | 135 | S_GPIO3            |

| 4   | P_AD16           | 48  | P_GPIO0            | 92  | S_AD19             | 136 | GND                |

| 5   | GND              | 49  | GND                | 93  | GND                | 137 | S_PCLK0            |

| 6   | P_C/BE2          | 50  | S_AD0              | 94  | S_AD20             | 138 | S_PCLK1            |

| 7   | P_FRAME          | 51  | S_AD1              | 95  | S_AD21             | 139 | VCC                |

| 8   | P_IRDY           | 52  | S_AD2              | 96  | S_AD22             | 140 | S_PCLK2            |

| 9   | P_TRDY           | 53  | GND                | 97  | S_AD23             | 141 | S_V <sub>CCP</sub> |

| 10  | P_DEVSEL         | 54  | S_AD3              | 98  | S_V <sub>CCP</sub> | 142 | S_PCLK3            |

| 11  | P_STOP           | 55  | S_AD4              | 99  | S_C/BE3            | 143 | S_PCLK4            |

| 12  | V <sub>C</sub> C | 56  | VCC                | 100 | VCC                | 144 | VCC                |

| 13  | P_LOCK           | 57  | S_AD5              | 101 | S_AD24             | 145 | S_PCLK5            |

| 14  | P_VCCP           | 58  | S_AD6              | 102 | S_AD25             | 146 | GND                |

| 15  | P_PERR           | 59  | S_V <sub>CCP</sub> | 103 | GND                | 147 | RST_MODE           |

| 16  | P_SERR           | 60  | S_AD7              | 104 | S_AD26             | 148 | P_CLKRUN           |

| 17  | P_PAR            | 61  | S_C/BE0            | 105 | S_AD27             | 149 | P_VCCP             |

| 18  | P_C/BE1          | 62  | S_AD8              | 106 | S_AD28             | 150 | P_RST              |

| 19  | GND              | 63  | GND                | 107 | GND                | 151 | GND                |

| 20  | P_AD15           | 64  | S_AD9              | 108 | S_AD29             | 152 | P_PCLK             |

| 21  | P_AD14           | 65  | S_AD10             | 109 | S_AD30             | 153 | VCC                |

| 22  | GND              | 66  | V <sub>CC</sub>    | 110 | S_AD31             | 154 | P_GNT              |

| 23  | P_AD13           | 67  | S_AD11             | 111 | S_REQ0             | 155 | P_REQ              |

| 24  | P_AD12           | 68  | S_AD12             | 112 | S_REQ1             | 156 | P_VCCP             |

| 25  | P_AD11           | 69  | S_AD13             | 113 | S_REQ2             | 157 | P_AD31             |

| 26  | VCC              | 70  | VCC                | 114 | VCC                | 158 | VCC                |

| 27  | P_AD10           | 71  | S_AD14             | 115 | S_REQ3             | 159 | P_AD30             |

| 28  | P_VCCP           | 72  | S_AD15             | 116 | S_REQ4             | 160 | P_AD29             |

| 29  | P_AD9            | 73  | S_C/BE1            | 117 | S_V <sub>CCP</sub> | 161 | GND                |

| 30  | GND              | 74  | S_PAR              | 118 | S_REQ5             | 162 | P_AD28             |

| 31  | P_AD8            | 75  | S_SERR             | 119 | S_GNT0             | 163 | P_AD27             |

| 32  | P_C/BE0          | 76  | S_PERR             | 120 | S_GNT1             | 164 | P_AD26             |

| 33  | GND              | 77  | GND                | 121 | GND                | 165 | GND                |

| 34  | P_AD7            | 78  | S_LOCK             | 122 | S_GNT2             | 166 | P_AD25             |

| 35  | P_AD6            | 79  | S_VCCP             | 123 | S_GNT3             | 167 | P_AD24             |

| 36  | VCC              | 80  | S_STOP             | 124 | S_GNT4             | 168 | P_C/BE3            |

| 37  | P_AD5            | 81  | S_DEVSEL           | 125 | S_GNT5             | 169 | GND                |

| 38  | P_AD4            | 82  | S_TRDY             | 126 | S_RST              | 170 | P_IDSEL            |

| 39  | P_AD3            | 83  | S_IRDY             | 127 | S_CLKRUN           | 171 | P_AD23             |

| 40  | VCC              | 84  | VCC                | 128 | VCC                | 172 | VCC                |

| 41  | P_AD2            | 85  | S_FRAME            | 129 | S_EXTARB           | 173 | P_AD22             |

| 42  | P_VCCP           | 86  | GND                | 130 | S_FLSHACK          | 174 | P_VCCP             |

| 43  | P_AD1            | 87  | S_C/BE2            | 131 | S_FLSHREQ          | 175 | P_AD21             |

| 44  | P_AD00           | 88  | S_AD16             | 132 | S_GPIO0            | 176 | P_AD20             |

## **Terminal Functions**

# primary PCI system

| TERMI | NAL | I/O  | FUNCTION                                                                                                                                                                                                                                                                                                               |

|-------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                               |

| P_CLK | 152 | I    | Primary PCI bus clock. P_CLK provides timing for all transactions on the primary PCI bus. All primary PCI signals are sampled at rising edge of P_CLK.                                                                                                                                                                 |

| P_RST | 150 | Ι    | PCI reset. When the primary PCI bus reset is asserted, PRST causes the bridge to 3-state all output buffers and reset all internal registers. When asserted, the device is completely nonfunctional. During PRST, the secondary interface is driven low. After PRST is deasserted, the bridge is in its default state. |

# primary PCI address and data

| TERMINA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | \L                                                                                                                                                                                                   | I/O  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NO.                                                                                                                                                                                                  | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| P_AD31 P_AD30 P_AD29 P_AD28 P_AD27 P_AD26 P_AD25 P_AD24 P_AD23 P_AD22 P_AD21 P_AD20 P_AD19 P_AD18 P_AD15 P_AD15 P_AD14 P_AD13 P_AD12 P_AD11 P_AD10 P_AD9 P_AD8 P_AD9 P_AD8 P_AD9 P_AD8 P_AD9 P_AD9 P_AD8 P_AD9 P_AD9 P_AD8 P_AD9 | 157<br>159<br>160<br>162<br>163<br>164<br>166<br>167<br>171<br>173<br>175<br>176<br>1<br>2<br>3<br>4<br>20<br>21<br>23<br>24<br>25<br>27<br>29<br>31<br>34<br>35<br>37<br>38<br>39<br>41<br>43<br>44 | I/O  | Primary address/data bus. These signals make up the multiplexed PCI address and data bus on the primary interface. During the address phase of a primary bus PCI cycle, P_AD31–P_AD0 contain a 32-bit address or other destination information. During the data phase, P_AD31–P_AD0 contain data.                                                                                                                                                                                                                                       |  |  |  |  |

| P_C/ <u>BE3</u><br>P_C/ <u>BE2</u><br>P_C/ <u>BE1</u><br>P_C/ <u>BE0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                 | 168<br>6<br>18<br>32                                                                                                                                                                                 | I/O  | Primary bus commands and byte enables. These signals are multiplexed on the same PCI terminals. During the address phase of a primary bus PCI cycle, P_C/BE3-P_C/BE0 define the bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte paths of the full 32-bit data bus carry meaningful data. P_C/BE0 applies to byte 0 (P_AD7-P_AD0), P_C/BE1 applies to byte 1 (P_AD15-P_AD8), P_C/BE2 applies to byte 2 (P_AD23-P_AD16), and P_C/BE3 applies to byte 3 (P_AD31-P_AD24). |  |  |  |  |

| P_CLKRUN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 148                                                                                                                                                                                                  | I/O  | Primary PCI bus clock run. P_CLKRUN is used by the central resource to request permission to stop the PCI clock or to slow it down.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

# primary PCI interface control

| TERMINAL                                 |                      | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|------------------------------------------|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                     | NO.                  | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| P_DEVSEL                                 | 10                   | I/O  | Primary device select. The bridge asserts P_DEVSEL to claim a PCI cycle as the target device. As a PCI initiator on the primary bus, the bridge monitors P_DEVSEL until a target responds. If no target responds before time-out occurs, then the bridge terminates the cycle with an initiator abort.                                                                                                            |  |  |

| P_FRAME                                  | 7                    | I/O  | Primary cycle frame. P_FRAME is driven by the initiator of a primary bus cycle. P_FRAME is asserted to indicate that a bus transaction is beginning, and data transfers continue while this signal is asserted. When P_FRAME is deasserted, the primary bus transaction is in the final data phase.                                                                                                               |  |  |

| P_GNT                                    | 154                  | I    | Primary bus grant to bridge. P_GNT is driven by the primary PCI bus arbiter to grant the bridge access to the primary PCI bus after the current data transaction has completed. P_GNT may or may not follow a primary bus request, depending on the primary bus parking algorithm.                                                                                                                                |  |  |

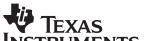

| P_GPIO0<br>P_GPIO1<br>P_GPIO2<br>P_GPIO3 | 48<br>47<br>46<br>45 | I/O  | Primary bus general-purpose I/O terminals. These terminals are provided for general input/output use in system design.                                                                                                                                                                                                                                                                                            |  |  |

| P_IDSEL                                  | 170                  | ı    | Initialization device select. P_IDSEL selects the bridge during configuration space accesses. P_IDSEL can be connected to one of the upper 24 PCI address lines on the primary PCI bus.  Note: There is no IDSEL signal interfacing the secondary PCI bus; thus, the entire configuration space of the bridge can only be accessed from the primary bus.                                                          |  |  |

| P_IRDY                                   | 8                    | I/O  | Primary initiator ready. P_IRDY indicates the primary bus initiator's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of P_CLK where both P_IRDY and P_TRDY are asserted. Until P_IRDY and P_TRDY are both sampled asserted, wait states are inserted.                                                                                                  |  |  |

| P_LOCK                                   | 13                   | I/O  | Primary PCI bus lock. P_LOCK is used to lock the primary bus and gain exclusive access as an initiator.                                                                                                                                                                                                                                                                                                           |  |  |

| P_PAR                                    | 17                   | I/O  | Primary parity. In all primary bus read and write cycles, the bridge calculates even parity across the P_AD and P_C/BE buses. As an initiator during PCI write cycles, the bridge outputs this parity indicator with a one-P_CLK delay. As a target during PCI read cycles, the calculated parity is compared to the initiator's parity indicator; a misdemeanor can result in a parity error assertion (P_PERR). |  |  |

| P_PERR                                   | 15                   | I/O  | Primary parity error indicator. P_PERR is driven by a primary bus PCI device to indicate that calculated parity does not match P_PAR when P_PERR is enabled through bit 6 of the command register.                                                                                                                                                                                                                |  |  |

| P_REQ                                    | 155                  | 0    | Primary PCI bus request. P_REQ is asserted by the bridge to request access to the primary PCI bus as an initiator.                                                                                                                                                                                                                                                                                                |  |  |

| P_SERR                                   | 16                   | 0    | Primary system error. Output pulsed from the bridge when enabled through the command register indicating a system error has occurred. The bridge need not be the target of the primary PCI cycle to assert P_SERR. When bit 6 is enabled in the bridge control register, P_SERR pulses, indicating that a system error has occurred on one of the subordinate buses downstream from the bridge.                   |  |  |

| P_STOP                                   | 11                   | I/O  | Primary cycle stop signal. P_STOP is driven by a PCI target to request the initiator to stop the current primary bus transaction. P_STOP is used for target disconnects and is commonly asserted by target devices that do not support burst data transfers.                                                                                                                                                      |  |  |

| RST_MODE                                 | 147                  | I    | If RST_MODE is asserted during P_RST, it causes S_RST to be asserted and the secondary clocks to be turned off.                                                                                                                                                                                                                                                                                                   |  |  |

| P_TRDY                                   | 9                    | I/O  | Primary target ready. P_TRDY indicates the primary bus target's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of P_CLK where both P_IRDY and P_TRDY are asserted. Until both P_IRDY and P_TRDY are asserted.                                                                                                                                          |  |  |

# secondary PCI system

| TERMINA                                                        | AL.                                    | I/O  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------|----------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                           | NO.                                    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                |

| S_PCLK5<br>S_PCLK4<br>S_PCLK3<br>S_PCLK2<br>S_PCLK1<br>S_PCLK0 | 145<br>143<br>142<br>140<br>138<br>137 | 0    | Secondary PCI bus clock. Provides timing for all transactions on the secondary PCI bus. All secondary PCI signals are sampled at the rising edge of S_CLK5–S_CLK0.                                                                                                                                                                                                      |

| S_CLKRUN                                                       | 127                                    | I/O  | Secondary PCI bus clock run. S_CLKRUN is output by the bridge to indicate that S_PCLKn is to be stopped.  S_CLKRUN is driven by secondary bus PCI devices to request that S_PCLKn be stopped.                                                                                                                                                                           |

| S_EXTARB                                                       | 129                                    | I    | Secondary external arbiter enable. When $\overline{S\_EXTARB}$ is asserted, the secondary external arbiter is enabled. When the external arbiter is enabled, $\overline{S\_REQ0}$ is reconfigured as a secondary bus grant input to the bridge and $\overline{S\_GNT0}$ is reconfigured as a secondary bus master request to the external arbiter on the secondary bus. |

| S_RST                                                          | 126                                    | 0    | Secondary PCI reset. S_RST is a logical OR of P_RST and the state of the secondary bus reset bit of the bridge control register. S_RST is asynchronous with respect to the state of the secondary interface CLK signal.                                                                                                                                                 |

# secondary PCI address and data

| TERMINA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AL                                                                                                                                                                                                   | 1/0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NO.                                                                                                                                                                                                  | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| S_AD31 S_AD30 S_AD29 S_AD28 S_AD27 S_AD26 S_AD25 S_AD24 S_AD23 S_AD22 S_AD21 S_AD20 S_AD19 S_AD18 S_AD17 S_AD16 S_AD15 S_AD15 S_AD14 S_AD13 S_AD12 S_AD11 S_AD10 S_AD10 S_AD10 S_AD10 S_AD10 S_AD10 S_AD10 S_AD11 S_ | 110<br>109<br>108<br>106<br>105<br>104<br>102<br>101<br>97<br>96<br>95<br>94<br>92<br>91<br>90<br>88<br>72<br>71<br>69<br>68<br>67<br>65<br>64<br>62<br>60<br>58<br>57<br>55<br>54<br>52<br>51<br>50 | I/O  | Secondary address/data bus. These signals make up the multiplexed PCI address and data bus on the secondary interface. During the address phase of a secondary bus PCI cycle, S_AD31–S_AD0 contain a 32-bit address or other destination information. During the data phase, S_AD31–S_AD0 contain data.                                                                                                                                                                                                                                            |

| S_C/ <u>BE3</u><br>S_C/ <u>BE2</u><br>S_C/ <u>BE1</u><br>S_C/BE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 99<br>87<br>73<br>61                                                                                                                                                                                 | I/O  | Secondary bus commands and byte enables. These signals are <u>multiplexed on</u> the same PCI terminals. During the address phase of a secondary bus PCI cycle, S_C/BE3-S_C/BE0 define the bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte paths of the full 32-bit data bus carry meaningful data. S_C/BE0 applies to byte 0 (S_AD7-S_AD0), S_C/BE1 applies to byte 1 (S_AD15-S_AD8), S_C/BE2 applies to byte 2 (S_AD23-S_AD16), and S_C/BE3 applies to byte 3 (S_AD31-S_AD24). |

| S_DEVSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81                                                                                                                                                                                                   | I/O  | Secondary device select. The bridge asserts S_DEVSEL to claim a PCI cycle as the target device. As a PCI initiator on the secondary bus, the bridge monitors S_DEVSEL until a target responds. If no target responds before timeout occurs, then the bridge terminates the cycle with an initiator abort.                                                                                                                                                                                                                                          |

| S_FRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85                                                                                                                                                                                                   | I/O  | Secondary cycle frame. SFRAME is driven by the initiator of a secondary bus cycle. SFRAME is asserted to indicate that a bus transaction is beginning and data transfers continue while SFRAME is asserted. When SFRAME is deasserted, the secondary bus transaction is in the final data phase.                                                                                                                                                                                                                                                   |

| S_GNT5<br>S_GNT4<br>S_GNT3<br>S_GNT2<br>S_GNT1<br>S_GNT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 125<br>124<br>123<br>122<br>120<br>119                                                                                                                                                               | 0    | Secondary bus grant to the bridge. The bridge provides internal arbitration and these signals are used to grant potential secondary PCI bus masters access to the bus. Seven potential initiators (including the bridge) can be located on the secondary PCI bus.  When the internal arbiter is disabled, \$\overline{S_GNT0}\$ is reconfigured as an external secondary bus request signal for the bridge.                                                                                                                                        |

# secondary PCI interface control

| TERMINA                                                  | \L                                     | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------|----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                     | NO.                                    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                               |

| S_GPIO0<br>S_GPIO1<br>S_GPIO2<br>S_GPIO3                 | 132<br>133<br>134<br>135               | I/O  | Secondary general-purpose I/O terminals. These terminals are provided for general-purpose input/output use in system design.                                                                                                                                                                                                                                                                                           |

| S_IRDY                                                   | 83                                     | I/O  | Secondary initiator ready. S_IRDY indicates the secondary bus initiator's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of S_PCLKn where both S_IRDY and S_TRDY are asserted; until S_IRDY and S_TRDY are asserted, wait states are inserted.                                                                                                              |

| S_LOCK                                                   | 78                                     | I/O  | Secondary lock S_LOCK is used to lock the secondary bus and gain exclusive access as an initiator.                                                                                                                                                                                                                                                                                                                     |

| S_PAR                                                    | 74                                     | I/O  | Secondary parity. In all secondary bus read and write cycles, the bridge calculates even parity across the S_AD and S_C/BE buses. As an initiator during PCI write cycles, the bridge outputs this parity indicator with a one-S_PCLKn delay. As a target during PCI read cycles, the calculated parity is compared to the initiator's parity indicator. A miscompare can result in a parity error assertion (S_PERR). |

| S_PERR                                                   | 76                                     | I/O  | Secondary parity error indicator. S_PERR is driven by a secondary bus PCI device to indicate that calculated parity does not match S_PAR when enabled through the command register.                                                                                                                                                                                                                                    |

| S_REQ5<br>S_REQ4<br>S_REQ3<br>S_REQ2<br>S_REQ1<br>S_REQ0 | 118<br>116<br>115<br>113<br>112<br>111 | ı    | Secondary PCI bus request signals. The bridge provides internal arbitration, and these signals are used as inputs from secondary PCI bus initiators requesting the bus. Seven potential initiators (including the bridge) can be located on the secondary PCI bus.                                                                                                                                                     |

| S_REQ0                                                   | 111                                    |      | When the internal arbiter is disabled, S_REQ0 is reconfigured as an external secondary bus grant for the bridge.                                                                                                                                                                                                                                                                                                       |

| S_SERR                                                   | 75                                     | I    | Secondary system error. S_SERR is passed through the primary interface by the bridge if enabled through the bridge control register. S_SERR is never asserted by the bridge.                                                                                                                                                                                                                                           |

| S_STOP                                                   | 80                                     | I/O  | Secondary cycle stop signal. S_STOP is driven by a PCI target to request the initiator to stop the current secondary bus transaction. S_STOP is used for target disconnects and is commonly asserted by target devices that do not support burst data transfers.                                                                                                                                                       |

| S_TRDY                                                   | 82                                     | I/O  | Secondary target ready. S_TRDY indicates the secondary bus target's ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of S_PCLKn where both S_IRDY and S_TRDY are asserted; until S_IRDY and S_TRDY are asserted.                                                                                                                                              |

| S_FLSHREQ                                                | 131                                    | I    | Flush request. When S_FLSHREQ is asserted, it signals a request to the PCI2031 to suspend internal write posting. When the bridge is ready to suspend internal write posting, it responds by asserting S_FLSHACK. S_FLSHACK remains asserted until the write posting buffers are empty.                                                                                                                                |

| S_FLSHACK                                                | 130                                    | 0    | Flush acknowledge. S_FLSHACK is asserted by the PCI2031 to indicate that the internal write posting is suspended. S_FLSHACK remains asserted until the write posting buffers are empty.                                                                                                                                                                                                                                |

## power supply

|        | TERMINAL                                                                               | FUNCTION                                                                                                                   |

|--------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.                                                                                    | FUNCTION                                                                                                                   |

| GND    | 5, 19, 22, 30, 33, 49, 53, 63, 77, 86, 93, 103, 107, 121, 136, 146, 151, 161, 165, 169 | Device ground terminals                                                                                                    |

| VCC    | 12, 26, 36, 40, 56, 66, 70, 84, 89, 100, 114, 128, 139, 144, 153, 158, 172             | Power-supply terminal for core logic (3.3 V)                                                                               |

| P_VCCP | 14, 28, 42, 149, 156, 174                                                              | Primary bus-signaling environment supply. $P_V_{CCP}$ is used in protection circuitry on primary bus I/O signals.          |

| S_VCCP | 59, 79, 98, 117, 141                                                                   | Secondary bus-signaling environment supply. S_V <sub>CCP</sub> is used in protection circuitry on primary bus I/O signals. |

SCPS017A - DECEMBER 1997 - REVISED JANUARY 1998

#### architecture

This section provides an overview of the PCI2031 PCI-to-PCI bridge features and functionality. Detailed descriptions of the bridge's internal registers and extension registers are also provided.

#### introduction to the PCI2031

The PCI2031 is a bridge between two PCI buses, and is compliant with both the PCI Local Bus Specification 2.1 and the PCI-to-PCI Bridge Specification 1.0. The bridge supports two 32-bit PCI buses operating at a maximum of 33 MHz. The primary and secondary buses operate independently in either a 3.3-V or 5-V signaling environment. The core logic of the bridge, however, is powered at 3.3 V to reduce power consumption.

Host software interacts with the bridge through internal registers. These internal registers provide the standard PCI status and control for both the primary and secondary buses. There are many vendor-specific features included in the bridge that exist in the TI extension register set. The PCI configuration header of the bridge is only accessible from the primary PCI interface.

The bridge provides internal arbitration for the six possible secondary bus masters, and provides each with a dedicated active low request/grant pair (REQ/GNT). The arbiter features a two-tier rotational scheme with the PCI2031 bridge defaulting to the highest priority tier. The bus parking scheme is also configurable and can be set to either park grant (GNT) on the bridge or on the last mastering device.

Upon system power up, power-on self-test (POST) software configures the bridge according to the devices that exist on subordinate buses, and enables performance-enhancing features of the PCI2031. In a typical system, this is the only communication with the bridge's internal register set.

#### serial EEPROM interface

The PCI2031 uses a serial EEPROM interface for loading the bridge's subsystem vendor ID register and subsystem ID register from an EEPROM after a reset on the primary bus. This interface also loads the slot number register, the device mask register, and the device-type register after a primary reset. The PCI2031 can trap accesses to the subsystem vendor ID register and subsystem ID register of devices sitting on its secondary bus, based on the settings of these two registers.

While the EEPROM is loading data into the PCI2031 subsystem vendor ID register and slot number register, all configuration read accesses to these registers are retried. All configuration reads to registers 2Ch and 40h of devices (0–7) behind the bridge are also retried. The interface uses general-purpose I/O terminals S\_GPIO0 for the clock and S\_GPIO1 for data.

The device-type register represents up to six devices on the secondary bus of the PCI2031. Each bit in this register corresponds to one device. During the address phase of a type 1 configuration cycle, if the value of bit 0 of the device-type register is 1, it implies that the device corresponding to device number 00000 (see bits AD15–AD11 in Figure 2 on page 13) is a CardBus controller. If the value of bit 0 is 0, it indicates that the device is a standard PCI device. Bit 1 in the device-type register corresponds to device number 00001, bit 2 corresponds to device number 00010, bit 3 corresponds to device number 00011, and so on.

The device-type and device mask registers control configuration read accesses to a device's subsystem vendor ID register. See *device mask register* and *device-type register*.

SCPS017A - DECEMBER 1997 - REVISED JANUARY 1998

The PCI2031 reads data from the serial EEPROM starting at address 00000000. The slave address of the serial EEPROM must be at 10100000 for the PCI2031 to see it. The PCI2031 then reads seven bytes of data from the EEPROM. The PCI2031 reads the data in the following order:

- 1. High byte of the subsystem ID

- 2. Low byte of the subsystem ID

- 3. High byte of the subsystem vendor ID.

- 4. Low byte of the subsystem vendor ID

- 5. Device mask

- 6. Device type

- 7. Slot number

The only register that is not programmed in the serial EEPROM is the chassis number register.

#### **PCI** commands

The bridge responds as a PCI target device to PCI bus cycles based on the decoding of each address phase and internal register settings. Table 2 lists the valid PCI bus cycles and their encoding on the command/byte enables (C/BE) bus during the address phase of a bus cycle.

| C/BE3-C/BE0 | COMMAND                     |

|-------------|-----------------------------|

| 0000        | Interrupt acknowledge       |

| 0001        | Special cycle               |

| 0010        | I/O read                    |

| 0011        | I/O write                   |

| 0100        | Reserved                    |

| 0101        | Reserved                    |

| 0110        | Memory read                 |

| 0111        | Memory write                |

| 1000        | Reserved                    |

| 1001        | Reserved                    |

| 1010        | Configuration read          |

| 1011        | Configuration write         |

| 1100        | Memory read multiple        |

| 1101        | Dual address cycle          |

| 1110        | Memory read line            |

| 1111        | Memory write and invalidate |

**Table 2. PCI Command Definition**

The bridge never responds as a PCI target to the interrupt acknowledge, special cycle, dual address cycle, or reserved commands. The bridge does, however, initiate special cycles on both interfaces when a type 1 configuration cycle issues the special cycle request. The remaining PCI commands address either memory, I/O, or configuration space. The bridge accepts PCI cycles by asserting DEVSEL as a medium-speed device, i.e., DEVSEL is asserted two clock cycles after the address phase.

#### configuration cycles

PCI Local Bus Specification 2.1 defines two types of PCI configuration read and write cycles: type 0 and type 1. The bridge decodes each type differently. Type 0 configuration cycles are intended for devices on the primary bus, while type 1 configuration cycles are intended for devices at some hierarchically subordinate bus. The difference between these two types of cycles is the encoding of the primary PCI ( $P_AD$ ) bus during the address phase of the cycle. The  $P_AD$  bus encoding during the address phase of a type 0 configuration cycle is shown in Figure 1. The 6-bit register number field represents an 8-bit address with the two lower bits masked to 0, indicating a double-word boundary. This results in a 256-byte configuration address space per function per device. Individual byte accesses may be selected within a word by using the  $P_C/\overline{BE}$  signals during the data phase of the cycle.

| 1 31     | 1 | 10 8            | 7 2                | 1 | 0 |

|----------|---|-----------------|--------------------|---|---|

| Reserved |   | Function number | Register<br>number | 0 | 0 |

Figure 1. PCI AD31-AD0 During Address Phase of a Type 0 Configuration Cycle

### configuration cycles (continued)

The bridge claims only type 0 configuration cycles when its P\_IDSEL terminal is asserted during the address phase of the cycle and the PCI function number encoded in the cycle is 0. If the function number is 1 or greater, the bridge does not recognize the configuration command. In this case, the bridge does not assert DEVSEL and the configuration transaction results in a master abort. The bridge services valid type 0 configuration read or write cycles by accessing internal registers from the configuration header (see Table 3).

Because type 1 configuration cycles are issued to devices on subordinate buses, the bridge claims type 1 cycles based on the bus number of the destination bus. The P\_AD bus encoding during the address phase of a type 1 cycle is shown in Figure 2. The device number and bus number fields define the destination bus and device for the cycle.

| 31 24    | 23 16      | 15 11            | 10 8            | 7 2                | 1 | 0 |

|----------|------------|------------------|-----------------|--------------------|---|---|

| Reserved | Bus number | Device<br>number | Function number | Register<br>number | 0 | 1 |

Figure 2. PCI AD31-AD0 During Address Phase of a Type 1 Configuration Cycle

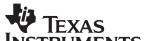

Several bridge configuration registers shown in Table 3 are significant when decoding and claiming type 1 configuration cycles. The destination bus number encoded on the P\_AD bus is compared to the values programmed in the bridge configuration registers 18h, 19h, and 1Ah, which are the primary bus number, secondary bus number, and subordinate bus number registers, respectively. These registers default to 00h and are programmed by host software to reflect the bus hierarchy in the system (seeFigure 3 for an example of a system bus hierarchy and how the PCI2031 bus number registers would be programmed in this case).

Figure 3. Bus Hierarchy and Numbering

### special cycle generation

The bridge is designed to generate special cycles on both buses through a type 1 cycle conversion. During a type 1 configuration cycle, if the bus number field matches the bridge's secondary bus number, the device number field is 1Fh, and the function number field is 07h, the bridge generates a special cycle on the secondary bus with a message that matches the type 1 configuration cycle data. If the bus number is a subordinate bus and not the secondary, then the bridge passes the type 1 special cycle request through to the secondary interface along with the proper message.

Special cycles are never passed through the bridge. Type 1 configuration cycles with a special cycle request can propagate in both directions.

#### PCI Local Bus Specification 2.1 compliance

The most significant additions to the PCI Local Bus Specification 2.1 are the latency requirements placed on PCI peripherals. Minimum response times are specified for a PCI device to respond with valid data. These requirements are intended to improve throughput and reduce latencies on the PCI bus. The PCI2031 bridge is fully compliant with these guidelines.

Other additions to revision 2.1 of the PCI specification include the subsystem ID and subsystem vendor ID registers in the PCI configuration header. The PCI2031 bridge includes these features, as well.

#### PCI clock run feature

The PCI2031 supports the PCI clock run protocol as defined in the PCI Mobile Design Guide, Revision 1.0. When the system's central resource signals to the system that it wants to stop the PCI clock (PCLK) by driving the primary clock run ( $\overline{P_CLKRUN}$ ) signal high, the bridge either signals that it is OK to stop the PCI clock by leaving  $\overline{P_CLKRUN}$  deasserted (high), or signals to the system to keep the clock running by driving  $\overline{P_CLKRUN}$  low.

The PCI2031 clock run control register provides a clock run enable bit for the primary bus and a separate clock run enable bit for the secondary bus. The bridge's P\_CLKRUN and secondary clock run (S\_CLKRUN) feature are enabled by setting bits 3 and 1, respectively, in the clock run control register. Bit 2 of the clock run control register allows software to enable the bridge's keep clock running mode to prevent the system from stopping the PCI clock. There are two conditions for restarting the secondary clock: a downstream transaction restarts the secondary clock; on the secondary, if S\_CLKRUN is asserted, the secondary clock is restarted.

There are two clock run modes supported on the secondary bus. The bridge can be configured to stop the secondary PCI clock only in response to a request from the primary bus to stop the clock, or it can be configured to stop the secondary clock whenever the secondary bus is idle and there are no transaction requests from the primary bus, regardless of the primary clock (see *clock run control register*).

### bus arbitration

The PCI2031 implements bus request  $(\overline{P_REQ})$  and bus grant  $(\overline{P_GNT})$  terminals for primary PCI bus arbitration. Six secondary bus requests and six secondary bus grants are provided on the secondary of the PCI2031. Seven potential initiators, including the bridge, can be located on the secondary bus. The PCI2031 provides a two-tier arbitration scheme on the secondary bus for priority bus-master handling.

The two-tier arbitration scheme improves performance in systems in which master devices do not all require the same bandwidth. Any master that requires frequent use of the bus can be programmed to be in the higher priority tier.

#### primary bus arbitration

The PCI2031, acting as an initiator on the primary bus, asserts  $\overline{P}_REQ$  when forwarding transactions upstream to the primary bus. In the upstream direction, as long as a posted write data or a delayed transaction request is in the queue, the PCI2031 keeps  $\overline{P}_REQ$  asserted. If a target disconnect, a target retry, or a target abort is received in response to a transaction initiated on the primary bus by the PCI2031, the device deasserts  $\overline{P}_REQ$  for two PCI clock cycles.

### primary bus arbitration (continued)

When the primary bus arbiter asserts  $\overline{P\_GNT}$  in response to a  $\overline{P\_REQ}$  from the PCl2031, the device initiates a transaction on the primary bus during the next PCl clock cycle.

When  $\overline{P_REQ}$  is not asserted and the primary bus arbiter asserts  $\overline{P_RONT}$  to the PCI2031, the device responds by parking the P\_AD31-P\_AD0 bus, the C/BE3-C/BE0 bus, and primary parity (P\_PAR) by driving them to valid logic levels. If the PCI2031 is parking the primary bus and wants to initiate a transaction on the primary, it can start the transaction on the next PCI clock by asserting the primary cycle frame (P\_FRAME) while P\_GNT is still asserted. If P\_GNT is deasserted, the bridge must rearbitrate for the bus to initiate a transaction.

### internal secondary bus arbitration

Bit 6 of the secondary clock/arbiter disable register at configuration offset 6Ch controls the state of the internal secondary arbiter. By default, the PCI2031 internal secondary bus arbiter is enabled (bit 6 is 0). The internal arbiter can be disabled by setting bit 6 to 1. The PCI2031 provides six secondary bus request terminals and six secondary bus grant terminals. Including the bridge itself, there are a total of seven potential secondary bus masters. These request and grant signals are connected to the internal arbiter. When an external arbiter is implemented, S\_REQ5-S\_REQ1 and S\_GNT5-S\_GNT1 are 3-stated.

#### external secondary bus arbitration

An external secondary bus arbiter can be used instead of the PCI2031 internal bus arbiter. When using an external arbiter, the PCI2031 internal arbiter should be disabled either by using the secondary external arbiter enable (S\_EXTARB) input, or by setting bit 6 of the secondary clock/arbiter disable register (at offset 6Ch) to 1.

When an external secondary bus arbiter is used, the PCI2031 internally reconfigures the  $\overline{S_REQ0}$  and  $\overline{S_GNT0}$  signals so that  $\overline{S_REQ0}$  becomes the secondary bus master grant for the bridge and  $\overline{S_GNT0}$  becomes the secondary bus master request for the PCI2031. This is done because  $S_REQ0$  is an input and can thus be used to provide the grant input to the bridge, and  $\overline{S_GNT0}$  is an output and can thus provide the request output from the bridge.

When an external arbiter is used, all unused secondary bus grant outputs ( $\overline{S\_GNT5}-\overline{S\_GNT1}$ ) are 3-stated. Any unused secondary bus request inputs ( $\overline{S\_REQ5}-\overline{S\_REQ1}$ ) should be pulled high to prevent the inputs from oscillating.

#### decode options

The PCI2031 supports positive, subtractive, and negative decoding. Positive decoding is a method of address decoding in which a device responds only to accesses within an assigned address range. Negative decoding is a method of address decoding in which a device responds only to accesses outside of an assigned address range. Subtractive decoding is a method of address decoding in which a device responds to accesses not claimed by any other devices on the bus. Subtractive decoding can be enabled on the primary bus or the secondary bus.

#### extension windows with programmable decoding

The PCI2031 provides two programmable 32-bit extension windows. Each window can be programmed to be a prefetchable memory window, a nonprefetchable memory window, or an I/O window. The TI extension memory windows have a 4K-byte granularity, and the I/O windows have a double-word granularity. These extension windows can be positively decoded either on the primary bus or on the secondary bus.

The standard PCI-to-PCI bridge memory and I/O windows specified by the PCI-to-PCI Bridge Specification 1.0 have a 1M-byte and 4K-byte granularity, respectively (see *memory base register* and *I/O base register*). The TI extension windows provide smaller granularity for memory and I/O windows. The extension windows' granularity matches the requirements of CardBus card windows, which also have 4K-byte granularity for memory windows and double-word granularity for I/O windows. When a CardBus I/O card is sitting behind the bridge, the smaller double-word I/O window granularity with the extension windows allows a smaller I/O window than the 4K-byte window with the standard I/O base and limit registers.

#### extension windows with programmable decoding (continued)

A common I/O base address for popular sound cards is 300h–303h. Using the TI extension windows and configuring the base I/O address for 300h establishes a 4-byte I/O address window from 300h–303h for communicating with the sound card. Using the bridge's standard I/O base register requires a minimum 4K-byte window of memory.

The extension windows can be excluded from the primary bus decoding, thus creating a hole in a primary window address range.

#### system error handling

The PCI2031 can be configured to signal a system error (SERR) for a variety of conditions. The SERR control and status registers, configuration offset 60h and 61h, respectively, provide individual SERR control/status bits for each condition for which the bridge can signal SERR. These individual bits enable SERR reporting for both downstream and upstream transactions.

With the exception of the master retry timeout and address parity errors, SERR is signaled on the primary bus for the following conditions, only if the corresponding bit in the SERR control register is set and the SERR enable bit in the command register (configuration offset 04h, bit 8) is set. The system error signal (bit 14) in the primary status register is set whenever the PCI2031 signals SERR.

Whenever the PCl2031 signals SERR on the primary bus, bit 14 in its status register gets set. Whenever the PCl2031 detects SERR on the secondary bus, bit 14 in the secondary status register gets set (see *status register* and *secondary status register*).