# PCI 9030

# *SMARTarget*<sup>™</sup> *I/O Accelerator*

# SMARTarget Technology Performance Features

- PCI v2.2 compliant 32-bit 33MHz Target Interface Chip enabling PCI Burst Transfers up to 132Mbytes/second.

- Up to 60MHz Local Bus operation enabling burst transfers up to 240Mbytes/second

- PCI Target Read Ahead Mode

- PCI Target Programmable Burst

- PCI Target Delayed Write

- Posted Memory Writes

#### **Flexibility Features**

- Programmable 32-bit Local Bus operates up to 60MHz

- Supports 5 PCI to Local Address spaces

- Nine Programmable GPIOs

- Four programmable Chip selects

- CompactPCI Hot Swap Ready

- Big/Little Endian Conversion

- Interrupt Generator

- PCI v1.1 Power Management.

- 3.3V, 5V Tolerant PCI Signaling

- ■3.3V CMOS device in 180-pin µBGA or 176-pin PQFP

- JTAG

As PCI evolves in today's complex systems, PLX continues to provide market leading, high performance 32-bit PCI solutions. In this tradition, PLX is offering the PCI 9030 SMARTarget I/O Accelerator.

There are many ways to do a PCI target design. Many PCI chip and core designs only attempt to implement the minimum PCI v2.1 bus interface signaling and call it complete. This leaves the burden of connectivity, performance and system compatibility on the designer. Only the PCI 9030 has SMARTarget technology, a set of advanced features which go far beyond the minimum to provide the best possible performance and flexibility to simplify the design. A basic target design is one thing, but a SMARTarget design is much more.

The PCI 9030 brings PLX's industry leading experience in the world of PCI designs to you in a way that is simple and convenient to use. The PCI 9030 is the perfect solution for applications such as:

### Migrating Legacy Designs to PCI

Whether you are migrating an ISA or other older design to PCI, or upgrading your current PCI target design, the PCI 9030 with SMARTarget technology provides the fastest and easiest route to PCI. The PCI 9030 has the industry's most flexible local bus which allows for multiple interface options to a wide variety of memory and I/O devices. Combine that with fully tested, compatible PCI v2.2 compliance, and your design risk is virtually zero.

### CompactPCI Hot Swap Designs

Building upon PLX's experience in CompactPCI, the PCI 9030 is the industry's first CompactPCI Hot Swap Ready Target device. This allows all of your CompactPCI I/O board designs to be compatible with both traditional CompactPCI and the new Hot Swap system designs.

#### **Smaller Form Factor Designs**

The PCI 9030 offers a 180-pin  $\mu$ BGA packaging option. Where space is a consideration, this ultra-thin, dime-sized package is an ideal solution. This allows for flexibility in real estate sensitive designs such as PMC or PC-MIP Mezzanine cards, and PCMCIA PC-Cards.

# PCI 9030 SMARTarget I/O Accelerator

Only the PCI 9030 has SMARTarget technology, a set of advanced features which go far beyond the minimum to provide the best possible performance and flexibility to simplify the design. A basic target design is one thing, but a SMARTarget design is much more.

- PCI Target Programmable Burst. The PCI 9030 may be programmed for several burst lengths, including unlimited burst. This allows for maximum transfer rates on both the PCI and local bus.

- PCI Target Delayed Write. The PCI 9030 supports PCI Target Delayed Write mode where the PCI Target Write data is postponed in the PCI Target Write FIFO to allow uninterrupted burst transactions

- Posted Memory Writes. A PCI memory write can be posted to the PCI 9030 for later transfer to the Local bus. This allows for maximum PCI performance and avoids potential deadlock situations.

# SMARTarget Flexibility Features

- Programmable Local Bus operates up to 60MHz and supports both nonmultiplexed and multiplexed 32-bit address/data protocol, and Dynamic Local Bus width control allowing slave accesses of 8-,16- or 32-bit devices.

- Supports 5 PCI to Local Address spaces. These spaces (Space 0,1,2,3 and Expansion ROM Spaces) allow a PCI Bus Master to access the local memory spaces with individually programmable wait states, bus width, and burst capabilities.

- The PCI 9030 has 9 programmable General Purpose I/Os which may be used for a variety of purposes.

- Four programmable Chip selects eliminate decode logic.

- CompactPCI Hot Swap Ready

- Supports Automatic on-the-fly Big Endian and Little Endian conversion for all operations and data types.

- Interrupt Generator can assert PCI interrupts from external and internal sources.

- Fully supports the Vital Product Data (VPD) PCI v2.2 extension including New Capabilities Structure. Provides an alternate access method for user or system defined parameters or configuration data.

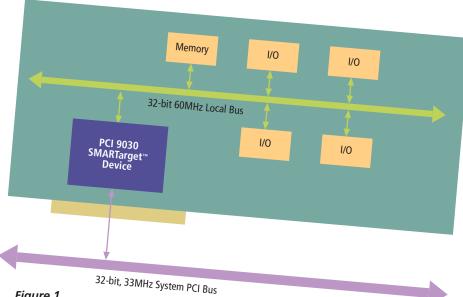

Figure 1. Typical PCI Target Adapter Card

SMARTarget Performance Features:

- PCI v2.2 Compliant 32-bit, 33MHz Target Interface Chip enabling PCI Burst Transfers up to 132Mbytes/second.

- Up to 60MHz Local Bus operation enabling burst transfers up to 240Mbytes/second

- PCI Target Read Ahead Mode. The PCI 9030 will prefetch a programmable amount of data from the local bus. The prefetched data can then be burst transferred on the PCI bus from the PCI 9030 internal PCI Target Read FIFO. The prefetch size can be programmed to match the PCI master burst length or can be used as PCI Target Read Ahead mode data. This feature allows for increased bandwidth and reduced read latency.

on the Local bus. This allows for a higher throughput for conditions in which the PCI clock frequency is slower than the Local clock frequency or when Local bus bursting is desirable.

■ PCI Power Management supports both D0, D3hot and D3cold power states.

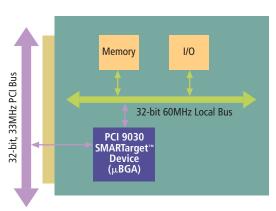

Figure 3.

PMC Card

- 3.3V, 5V Tolerant PCI Signaling enables universal PCI adapters

- 3.3V CMOS device in space saving 180 pin µBGA or 176-PQFP

# PCI 9030 Applications PCI Target Adapter Card

The PCI 9030 can be used in a wide variety of applications in networking, telecom, imaging, industrial and storage. The PCI 9030 simplifies migration of legacy designs to PCI by providing a convenient off-theshelf solution that can enable you to have your prototypes operational in as little as one week. At the same time, the PCI 9030's built in SMARTarget performance features guarantee you will meet or beat your performance goals. In addition, SMARTarget flexibility features such as 3.3V and 5V tolerant I/O buffers and local bus operation up to 60MHz, enable you to connect a wide variety of memory and I/O devices. With SMARTarget in action, PCI Target Adapter designs have never been simpler. Figure 1 shows a typical PCI Target adapter card.

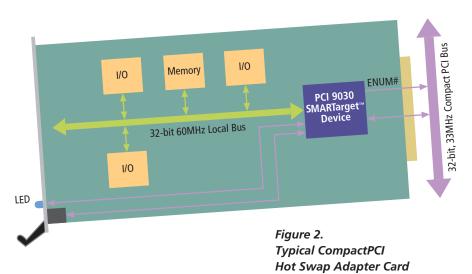

# **CompactPCI Hot Swap Adapter Card**

Hot Swap capability is a requirement for

today's CompactPCI systems. The PCI 9030 provides an excellent solution because it is the industry's first Hot Swap Ready Target chip. SMARTarget Technology will ensure a high performance Hot Swap implementation. The PCI 9030 is a PICMG v2.1 Hot Swap Ready target device including the following features:

- PCI specification v2.1 or better

- Tolerant of Vcc from early power

- Tolerant of asynchronous reset

- Tolerant of precharge voltage

- Has limited I/O pin leakage at precharge voltage

- Incorporates the Hot Swap Control/Status Register (HS\_CSR)

- Incorporates an Extended Capability Pointer (ECP) mechanism

- Incorporates added resources for software control of ENUM#, the ejector switch, and the status LED which indicates to the user insertion /removal

- Precharge BIOS internal to the PCI 9030

- Early power support internal to the PCI 9030

Figure 2 shows a typical Compact PCI Hot Swap adapter card.

### **Small Form Factor PCI Designs**

In the real estate conscious world of PMC, PC-MIP, and PCMCIA PC-Cards, the PCI 9030's attractive packaging options are the perfect solution.

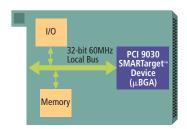

SMARTarget Flexibility features such as

GPIO's and Programmable Chip selects save additional valuable board space. The PCI 9030 enables a whole new generation of mini form factor PCI cards. This is shown in figure 3 and 4:

#### Additional Features

- ■5V Tolerant Operation The PCI 9030 requires 3.3 Vcc. It provides 3.3V signaling with 5V I/O tolerance on the PCI and Local Buses.

- Serial EEPROM Interface-Contains an interface for an optional serial EEPROM that can be used to load configuration information.

- Clocks-The Local Bus runs from a local bus clock and asserts the necessary internal clocks. This clock runs asynchronously to the PCI clock. The PCI 9030 provides a PCI Buffered clock which can be used as a local bus clock if desired.

Figure 4.

PCMCIA PC-CARD

#### **Development Tool Support**

As any good designer knows, development tools are just as important as the chips themselves. That is why PLX provides a complete PCI development environment to speed your time to market. The PCI 9030 is supported with a complete Reference Design Kit (RDK) with software debug support, and a hardware development kit (HDK) CD-ROM. These tools provide the easiest PCI target prototyping platform available. With the PLX PCI development environment you can have your hardware and software prototypes running in as little as one week.

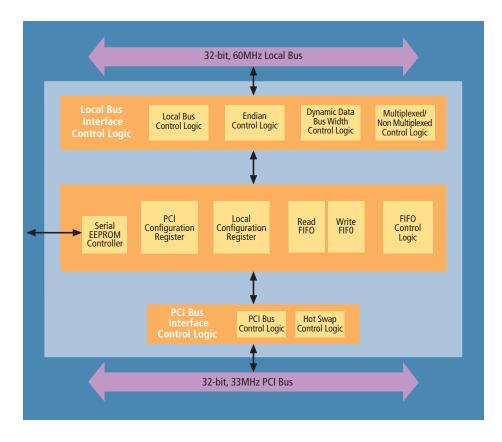

#### PLX PCI 9030 Block Diagram

PLX Technology, Inc. 390 Potrero Ave. Sunnyvale, CA 94085 USA Tel: 1–800–759–3735

Fax: 1-408-774-2169 Email: info@plxtech.com Web Site: www.plxtech.com

#### **Product Ordering Information**

| Part Number             | Description                                |

|-------------------------|--------------------------------------------|

| Tare Number             | Description                                |

| PCI 9030-AA60PI         | PCI SMARTarget I/O Accelerator (PQFP)      |

| PCI 9030-AA60BI         | PCI SMARTarget I/O Accelerator (μBGA)      |

| PCI 9030RDK-LITE        | PCI 9030 Reference Design kit              |

| CompactPCI 9030RDK-LITE | CompactPCI 9030 Reference Design Kit       |

| HDK Collection CD-ROM   | Hardware Development Kit Collection CD-ROM |

| Host-SDK                | Windows Host Side Software Development Kit |

See PLX web site for latest version and product support information.