# DATA SHEET

# **PCK2510S**

50-150 MHz 1:10 SDRAM clock driver

**Product specification**

1999 Dec 13

## 50-150 MHz 1:10 SDRAM clock driver

**PCK2510S**

#### **FEATURES**

- Phase-Locked Loop Clock distribution for PC100/PC133 SDRAM applications

- Spread Spectrum clock compatible

- Operating frequency 50 to 150 MHz

- (t<sub>phase error</sub> jitter) at 100 to 133 MHz = ±50 ps

- Jitter (peak-peak) at 100 to 133 MHz =  $\pm$  80 ps

- Jitter (cycle-cycle) at 100 to 133 MHz = 65 ps

- Pin-to-pin skew < 200 ps

- Available in plastic 24-Pin TSSOP

- Distributes one clock input to one bank of ten outputs

- External Feedback (FBIN) terminal Is used to synchronize the outputs to the clock input

- On-Chip series damping resistors

- No external RC network required

- Operates at 3.3 V

#### **DESCRIPTION**

The PCK2510S is a high-performance, low-skew, low-jitter, phase-locked loop (PLL) clock driver. It uses a PLL to precisely align, in both frequency and phase, the feedback (FBOUT) output to the clock (CLK) input signal. It is specifically designed for use with synchronous DRAMs. The PCK2510S operates at 3.3 V  $\rm V_{CC}$  and is input compatible with both 2.5 V and 3.3 V input voltage ranges. It also provides integrated series damping resistors that make it ideal for driving point-to-point loads.

One bank of ten outputs provides ten low-skew, low-jitter copies of CLK. Output signal duty cycles are adjusted to 50 percent,

independent of the duty cycle at CLK. All outputs can be enabled or disabled via a single output enable input. When the G input is high, the outputs switch in phase and frequency with CLK; when the G input is low, the outputs are disabled to the logic-low state.

Unlike many products containing PLLs, the PCK2510S does not require external RC networks. The loop filter for the PLL is included on-chip, minimizing component count, board space, and cost.

Because it is based on PLL circuitry, the PCK2510S requires a stabilization time to achieve phase lock of the feedback signal to the reference signal. This stabilization time is required, following power up and application of a fixed-frequency, fixed-phase signal at CLK, and following any changes to the PLL reference. The PLL can be bypassed for test purposes by strapping  $\mbox{AV}_{\mbox{CC}}$  to ground.

The PCK2510S is characterized for operation from  $0^{\circ}$ C to +70°C.

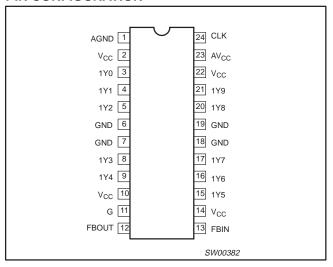

#### **PIN CONFIGURATION**

## **ORDERING INFORMATION**

| PACKAGES             | TEMPERATURE RANGE | ORDER CODE  | DRAWING NUMBER |  |

|----------------------|-------------------|-------------|----------------|--|

| 24-Pin Plastic TSSOP | 0°C to +70°C      | PCK2510S PW | SOT355-1       |  |

# 50-150 MHz 1:10 SDRAM clock driver

PCK2510S

# **PIN DESCRIPTIONS**

| PIN NUMBER                           | SYMBOL           | TYPE | NAME, FUNCTION, and DIRECTION                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                    | AGND             | GND  | Analog ground. AGND provides the ground reference for the analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                       |

| 2, 10, 14, 22                        | V <sub>CC</sub>  | PWR  | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3, 4, 5, 8, 9,<br>15, 16, 17, 20, 21 | 1Y (0–9)         | OUT  | Clock outputs. These outputs provide low-skew copies of CLK. Output bank 1Y (0–9) is enabled via the G input. These outputs can be disabled to a logic-low state by de-asserting the G control input. Each output has an integrated 25 $\Omega$ series-damping resistor.                                                                                                                                                                                          |

| 6, 7, 18, 19                         | GND              | GND  | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11                                   | G                | IN   | Output bank enable. G is the output enable for outputs 1Y (0–9). When G is LOW, outputs 1Y (0–9) are disabled to a logic LOW state. When G is HIGH, all outputs 1Y (0–9) are enabled and switch at the same frequency as CLK.                                                                                                                                                                                                                                     |

| 12                                   | FBOUT            | OUT  | Feedback output. FBOUT is dedicated for external feedback. It switches at the same frequency as CLK. When externally wired to FBIN, FBOUT completes the feedback loop of the PLL. FBOUT has an integrated 25 $\Omega$ series-damping resistor.                                                                                                                                                                                                                    |

| 13                                   | FBIN             | IN   | Feedback input. FBIN provides the feedback signal to the internal PLL. FBIN must be hard-wired to FBOUT to complete the PLL. The integrated PLL synchronizes CLK and FBIN so that there is nominally zero phase error between CLK and FBIN.                                                                                                                                                                                                                       |

| 23                                   | AV <sub>CC</sub> | PWR  | Analog power supply. $AV_{CC}$ provides the power reference for the analog circuitry. In addition, $AV_{CC}$ can be used to bypass the PLL for test purposes. When $AV_{CC}$ is strapped to ground, PLL is bypassed and CLK is buffered directly to the device outputs.                                                                                                                                                                                           |

| 24                                   | CLK              | IN   | Clock input. CLK provides the clock signal to be distributed by the PCK2510S clock driver. CLK is used to provide the reference signal to the integrated PLL that generates the clock output signals. CLK must have a fixed frequency and fixed phase for the PLL to obtain phase lock. Once the circuit is powered up and a valid CLK signal is applied, a stabilization time is required for the PLL to phase lock the feedback signal to its reference signal. |

# **FUNCTION TABLE**

| INP | JTS | OUTPUTS  |       |  |  |

|-----|-----|----------|-------|--|--|

| G   | CLK | 1Y (0–9) | FBOUT |  |  |

| Х   | L   | L        | L     |  |  |

| L   | Н   | L        | Н     |  |  |

| Н   | Н   | Н        | Н     |  |  |

# 50-150 MHz 1:10 SDRAM clock driver

**PCK2510S**

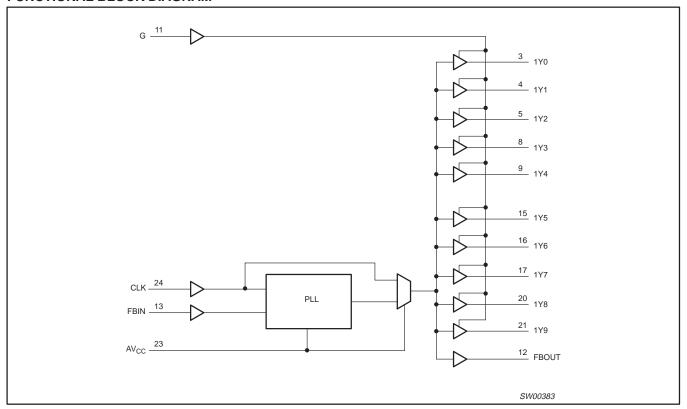

#### **FUNCTIONAL BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS 1,3**

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL           | PARAMETER                        | CONDITION                   | LI   | LIMITS                  |      |  |

|------------------|----------------------------------|-----------------------------|------|-------------------------|------|--|

| STWIBUL          | PARAMETER                        | CONDITION                   | MIN  | MAX                     | UNIT |  |

| AV <sub>CC</sub> | Supply voltage range             | Note 2                      |      | < V <sub>CC</sub> + 0.7 | V    |  |

| V <sub>CC</sub>  | Supply voltage range             |                             | -0.5 | +4.6                    | V    |  |

| I <sub>IK</sub>  | Input clamp current              | V <sub>1</sub> < 0          |      | -50                     | mA   |  |

| VI               | Input voltage range              | Note 3                      | -0.5 | 6.5                     | V    |  |

| I <sub>OK</sub>  | Output clamp current             | $V_O > V_{CC}$ or $V_O < 0$ |      | ±50                     | mA   |  |

| V <sub>O</sub>   | Output voltage range             | Notes 3, 4                  | -0.5 | V <sub>CC</sub> + 0.5   | V    |  |

| I <sub>O</sub>   | DC output source or sink current | $V_O = 0$ to $V_{CC}$       |      | ±50                     | mA   |  |

| T <sub>STG</sub> | Storage temperature range        |                             | -65  | +150                    | °C   |  |

| P <sub>TOT</sub> | Power dissipation per package    |                             |      | 700                     | mW   |  |

#### NOTES

- 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. AV<sub>CC</sub> must not exceed V<sub>CC</sub>

- 3. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

- 4. This value is limited to 4.6 V maximum.

# 50-150 MHz 1:10 SDRAM clock driver

**PCK2510S**

### RECOMMENDED OPERATING CONDITIONS<sup>1</sup>

| SYMBOL                             | PARAMETER                                       | CONDITIONS | LIM | UNIT            |      |

|------------------------------------|-------------------------------------------------|------------|-----|-----------------|------|

| STWIBOL                            | PARAINETER                                      | CONDITIONS | MIN | MAX             | UNII |

| V <sub>CC</sub> , AV <sub>CC</sub> | Supply voltage                                  |            | 3   | 3.6             | V    |

| V <sub>IH</sub>                    | HIGH level input voltage                        |            | 2   |                 | V    |

| V <sub>IL</sub>                    | LOW level input voltage                         |            | 0   | 0.8             | V    |

| VI                                 | Input voltage                                   |            | 0   | V <sub>CC</sub> | V    |

| T <sub>amb</sub>                   | Operating ambient temperature range in free air |            | 0   | +70             | °C   |

#### NOTE:

## **ELECTRICAL CHARACTERISTICS**

Over recommended operating free-air temperature range (unless otherwise noted)

| SYMBOL             | DADAMETED                               | Т                                      | EST CONDITIONS                                                                  |                       |     | UNIT |    |  |  |

|--------------------|-----------------------------------------|----------------------------------------|---------------------------------------------------------------------------------|-----------------------|-----|------|----|--|--|

| STINIBUL           | PARAMETER                               | AV <sub>CC</sub> , V <sub>CC</sub> (V) | OTHER                                                                           | MIN                   | TYP | MAX  |    |  |  |

| V <sub>IK</sub>    | Input clamp voltage                     | 3                                      | $I_{I} = -18 \text{ mA}$                                                        |                       |     | -1.2 | V  |  |  |

|                    |                                         | MIN to MAX                             | I <sub>OH</sub> = - 100 μA                                                      | V <sub>CC</sub> - 0.2 |     |      |    |  |  |

| $V_{OH}$           | HIGH level output voltage               | 3                                      | I <sub>OH</sub> = - 12 mA                                                       | 2.1                   |     |      | ٧  |  |  |

|                    |                                         | 3                                      | $I_{OH} = -6 \text{ mA}$                                                        | 2.4                   |     |      | 1  |  |  |

|                    |                                         | MIN to MAX                             | I <sub>OL</sub> = 100 μA                                                        | -                     |     | 0.2  |    |  |  |

| V <sub>OL</sub> LC | LOW level output voltage                | 3                                      | I <sub>OL</sub> = 12 mA                                                         | -                     |     | 0.8  | ٧  |  |  |

|                    |                                         | 3                                      | I <sub>OL</sub> = 6 mA                                                          | -                     |     | 0.55 | 1  |  |  |

| l <sub>l</sub>     | Input current                           | 3.6                                    | $V_I = V_{CC}$ or GND                                                           |                       |     | ±5   | μΑ |  |  |

| Icc                | Quiescent supply current                | 3.6                                    | $V_I = V_{CC}$ or GND;<br>$I_O = 0$ , outputs: LOW or HIGH                      |                       |     | 10   | μА |  |  |

| I <sub>CCA</sub>   | AV <sub>CC</sub> power supply current   | $AV_{CC} = 3.3$                        |                                                                                 |                       | 30  | 50   | μΑ |  |  |

| Δl <sub>CC</sub>   | Additional supply current per input pin | 3.3 to 3.6                             | One input at V <sub>CC</sub> – 0.6 V;<br>other inputs at V <sub>CC</sub> or GND |                       |     | 500  | μА |  |  |

| Cl                 | Input capacitance                       | 3.3                                    | $V_I = V_{CC}$ or GND                                                           |                       | 2.8 |      | pF |  |  |

| Co                 | Output capacitance                      | 3.3                                    | V <sub>O</sub> = V <sub>CC</sub> or GND                                         |                       | 5.4 |      | pF |  |  |

## **TIMING REQUIREMENTS**

Over recommended ranges of supply voltage and operating free-air temperature

| SYMBOL           | PARAMETER                       | MIN | MAX | UNIT |

|------------------|---------------------------------|-----|-----|------|

| f <sub>CLK</sub> | Clock frequency                 | 50  | 150 | MHz  |

|                  | Input clock duty cycle          | 40  | 60  | %    |

|                  | Stabilization time <sup>1</sup> |     | 1   | ms   |

#### NOTE

<sup>1.</sup> Unused inputs must be held high or low to prevent them from floating.

<sup>1.</sup> Time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal. For phase lock to be obtained, a fixed-frequency, fixed-phase reference signal must be present at CLK. Until phase lock is obtained, the specifications for propagation delay, skew, and jitter parameters given in the switching characteristics table are not applicable.

# 50-150 MHz 1:10 SDRAM clock driver

**PCK2510S**

#### **SWITCHING CHARACTERISTICS**

Over recommended ranges of supply voltage and operating free-air temperature;  $C_L = 30 \text{ pF}^1$

| PARAMETER                                      | FROM                              | то              | V <sub>CC</sub> , A | $V_{CC}$ , $AV_{CC}$ = 3.3 V $\pm 0.3$ V |     |      |  |  |

|------------------------------------------------|-----------------------------------|-----------------|---------------------|------------------------------------------|-----|------|--|--|

| PARAMETER                                      | (INPUT)/CONDITION                 | (OUTPUT)        | MIN                 | TYP                                      | MAX | UNIT |  |  |

| <b>.</b> 2                                     | CLKIN↑ = 100 MHz to 133 MHz       | FBIN↑           | -100                |                                          | 100 | ps   |  |  |

| <sup>t</sup> phase error <sup>2</sup>          | CLKIN↑ = 66 MHz                   | FBIN↑           | -125                |                                          | 125 | ps   |  |  |

| t <sub>phase error</sub> – jitter <sup>3</sup> | CLKIN↑ = 100 MHz to 133 MHz FBIN↑ |                 | -50                 |                                          | 50  | ps   |  |  |

| t <sub>SK(0)</sub>                             | Any Y or FBOUT                    | Any Y or FBOUT  |                     |                                          | 200 | ps   |  |  |

| jitter <sub>(peak-peak)</sub>                  | CLKIN = 100 MHz to 133 MHz        | Any Y or FBOUT  | -80                 |                                          | 80  | 200  |  |  |

| jitter (cycle-cycle)                           | CERTIN = 100 MINZ to 133 MINZ     | Ally 1 of FBOOT |                     | 65                                       |     | ps   |  |  |

| Duty cycle reference                           | F(CLKIN > 60 MHz)                 | Any Y or FBOUT  | 47                  |                                          | 53  | %    |  |  |

| t <sub>r</sub>                                 | $V_0 = 0.4 \text{ V to 2 V}$      | Any Y or FBOUT  | 2.5                 |                                          | 1   | V/ns |  |  |

| t <sub>f</sub>                                 | V <sub>O</sub> = 0.4 V to 2 V     | Any Y or FBOUT  | 2.5                 |                                          | 1   | V/ns |  |  |

#### NOTES:

- 1. These parameters are not production tested.

- 2. This is considered as static phase error.

- 3. Phase error does not include jitter. (t<sub>phase error</sub> = static phase error jitter<sub>(cycle-cycle)</sub>)

- 4. The  $t_{SK(0)}$  specification is only valid for equal loading of all outputs.

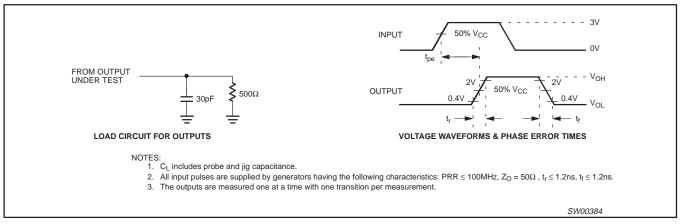

## PARAMETER MEASUREMENT INFORMATION

Figure 1. Load Circuit and Voltage Waveforms

# 50-150 MHz 1:10 SDRAM clock driver

# PCK2510S

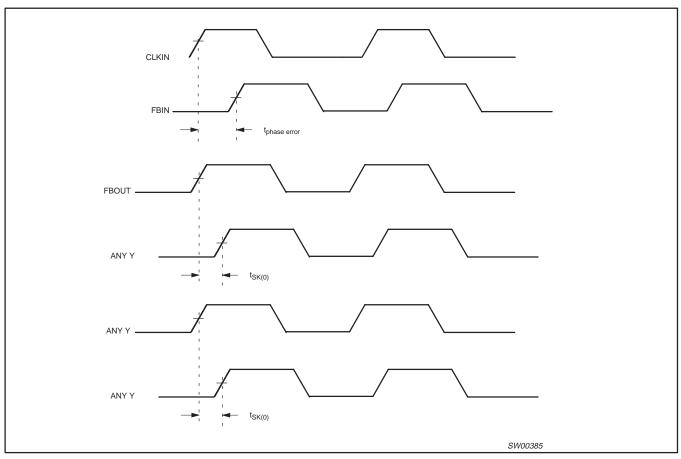

Figure 2. Phase Error and Skew Calculations

# 50-100 MHz 1:10 SDRAM clock driver

PCK2510S

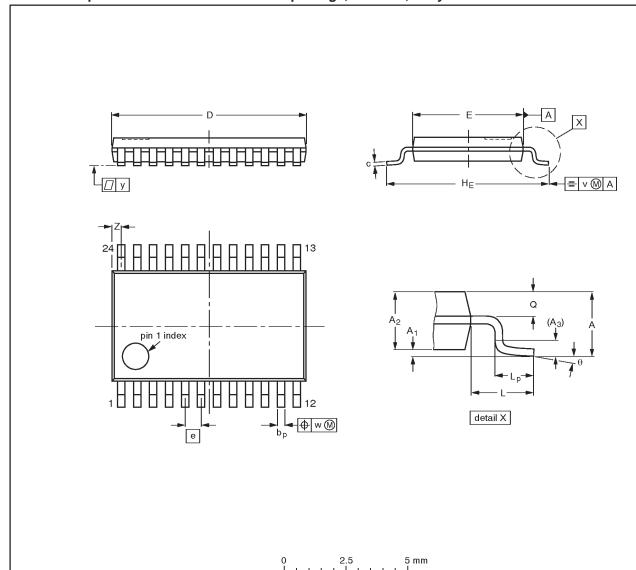

TSSOP24: plastic thin shrink small outline package; 24 leads; body width 4.4 mm

SOT355-1

# DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | Α1           | A <sub>2</sub> | A <sub>3</sub> | рb           | С          | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L   | Lp           | Ø          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|--------------|----------------|----------------|--------------|------------|------------------|------------------|------|------------|-----|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 1.10      | 0.15<br>0.05 | 0.95<br>0.80   | 0.25           | 0.30<br>0.19 | 0.2<br>0.1 | 7.9<br>7.7       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.5<br>0.2       | 8°<br>0° |

scale

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER    | RENCES | EUROPEAN ISSUE DAT |                                   |  |  |

|----------|-----|----------|--------|--------------------|-----------------------------------|--|--|

| VERSION  | IEC | JEDEC    | EIAJ   | PROJECTION ISSUE   |                                   |  |  |

| SOT355-1 |     | MO-153AD |        |                    | <del>-93-06-16-</del><br>95-02-04 |  |  |

# 50-100 MHz 1:10 SDRAM clock driver

PCK2510S

# **NOTES**

# 50-100 MHz 1:10 SDRAM clock driver

**PCK2510S**

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                              |

|---------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development.  Specification may change in any manner without notice.                                                                                                          |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date.  Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                        |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

**Limiting values definition** — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381

© Copyright Philips Electronics North America Corporation 1999 All rights reserved. Printed in U.S.A.

Date of release: 12-99

Document order number: 9397 750 06707

Let's make things better.