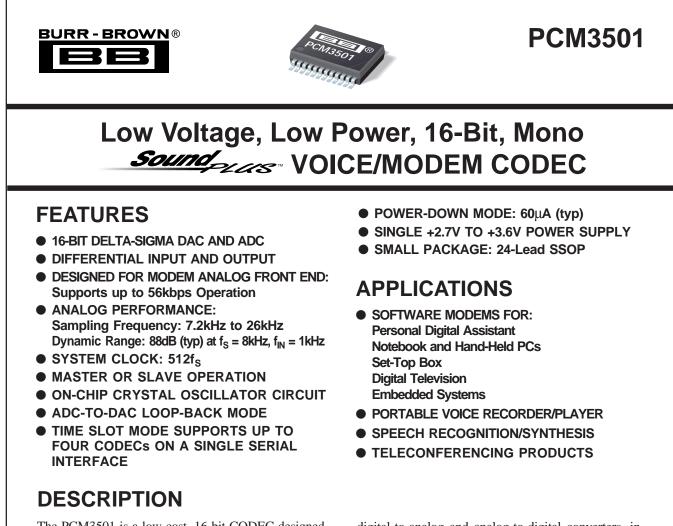

The PCM3501 is a low cost, 16-bit CODEC designed for modem Analog Front End (AFE) and speech processing applications. The PCM3500's low power operation from +2.7V to +3.6V power supplies, along with an integrated power-down mode, make it ideal for portable applications.

The PCM3501 integrates all of the functions needed for a modem or voice CODEC, including delta-sigma

digital-to-analog and analog-to-digital converters, input anti-aliasing filter, digital high-pass filter for DC blocking, and an output low-pass filter. The synchronous serial interface provides for a simple, or glue-free interface to popular DSP and RISC processors. The serial interface also supports Time Division Multiplexing (TDM), allowing up to four CODECs to share a single 4-wire serial bus.

## SPECIFICATIONS

All specifications at  $T_A = +25$  °C,  $V_{DD} = V_{CC} = 3.3$ V,  $f_S = 8$ kHz, and nominal system clock (XTI) = 512 $f_S$ , and differntial input and output mode, unless otherwise noted. Measurement band is 100Hz to 0.425 $f_S$ .

|                                                     |                                                     |                       | PCM3501E            |                       |         |

|-----------------------------------------------------|-----------------------------------------------------|-----------------------|---------------------|-----------------------|---------|

| PARAMETER                                           | CONDITIONS                                          | MIN                   | TYP                 | MAX                   | UNITS   |

| RESOLUTION                                          |                                                     |                       | 16                  |                       | Bits    |

| DATA FORMAT                                         |                                                     |                       |                     |                       |         |

| Serial Data Interface Format                        |                                                     |                       | DSP Format          |                       |         |

| Serial Data Bit Length                              |                                                     |                       | 16                  |                       | Bits    |

| Serial Data Format                                  |                                                     | MSB-Firs              | t, Binary Two's     | Complement            |         |

| Sampling Frequency, f <sub>S</sub>                  | ADC and DAC                                         | 7.2                   | 8                   | 26                    | kHz     |

| System Clock Frequency, 512f <sub>S</sub>           |                                                     | 3.686                 | 4.096               | 13.312                | MHz     |

| DIGITAL INPUT/OUTPUT                                |                                                     |                       |                     |                       |         |

| Logic Family                                        |                                                     |                       | CMOS                |                       |         |

| Input Logic Level: V <sub>IH</sub> <sup>(1)</sup>   |                                                     | 0.7 • V <sub>DD</sub> |                     |                       | VDC     |

| $V_{\rm IL}^{(1)}$                                  |                                                     | - 00                  |                     | 0.3 • V <sub>DD</sub> | VDC     |

| Input Logic Current: I <sub>IN</sub> <sup>(2)</sup> |                                                     |                       |                     | ±1                    | μA      |

| I <sub>IN</sub> <sup>(3)</sup>                      |                                                     |                       |                     | 100                   | μA      |

| Output Logic Level: V <sub>OH</sub> <sup>(4)</sup>  | $I_{OUT} = -1mA$                                    | V <sub>DD</sub> - 0.3 |                     |                       | VDC     |

| V <sub>OL</sub> <sup>(4)</sup>                      | $I_{OUT} = +1mA$                                    | 00                    |                     | 0.3                   | VDC     |

| REFERENCE                                           |                                                     |                       |                     |                       |         |

| Voltage Common: V <sub>COM</sub>                    | $V_{IN} = BPZ, V_{OUT} = BPZ$                       |                       | 0.5V <sub>CC</sub>  |                       | V       |

| $V_{COM}$ Load Impedance: $R_{COM}^{(5)}$           | $v_{\rm IN} = Drz, v_{\rm OUT} = Drz$               | 100                   | 0.5 V CC            |                       | v<br>kΩ |

|                                                     |                                                     |                       |                     |                       | N32     |

|                                                     |                                                     | 1                     |                     |                       |         |

| DC ACCURACY                                         | $\mathcal{M} = \mathcal{M} + \mathcal{M}$           |                       | 1.01/               |                       | 1/      |

| Input Voltage (Differential)                        | $V_{IN} = V_{IN} + - V_{IN} -$                      |                       | 1.2V <sub>CC</sub>  | . –                   | Vp-p    |

| Gain Error                                          |                                                     |                       | <u>+2</u>           | ±5                    | % of FS |

| Offset Error                                        | HPF OFF                                             |                       | ±2                  |                       | % of FS |

| Input Resistance                                    |                                                     |                       | 50                  |                       | kΩ      |

| AC ACCURACY <sup>(6)</sup>                          |                                                     |                       |                     |                       |         |

| THD+N                                               | $f_{IN} = 1 \text{kHz}, V_{IN} = -0.5 \text{dB}$    |                       | -85                 | -80                   | dB      |

| Dynamic Range                                       |                                                     | 82                    | 88                  |                       | dB      |

| Signal-to-Noise Ratio                               |                                                     | 82                    | 88                  |                       | dB      |

| Crosstalk                                           | DAC Channel Idle, 0dB Input                         | 78                    | 82                  |                       | dB      |

| Passband Ripple                                     | HPF ON, 0.0002f <sub>s</sub> to 0.425f <sub>s</sub> |                       | ±0.05               |                       | dB      |

| 5 11 011                                            | HPF OFF, 0f <sub>s</sub> to 0.425f <sub>s</sub>     |                       | ±0.05               |                       | dB      |

| Roll-Off                                            | HPF ON, at 0.00002f <sub>S</sub>                    |                       | -3                  |                       | dB      |

|                                                     | HPF ON, at 0.56fs                                   |                       | -30                 |                       | dB      |

| Stopband Rejection                                  | $0.58f_{S}$ to $f_{S}$                              |                       | -65                 |                       | dB      |

| Group Delay                                         |                                                     |                       | 18/f <sub>S</sub>   | 4m                    | sec     |

| DAC CHARACTERISTICS                                 |                                                     |                       | 1                   |                       |         |

|                                                     | ., ., .,                                            |                       | ( ) (               |                       | .,      |

| Output Voltage (Differential)                       | $V_{OUT} = V_{OUT} + - V_{OUT} -$                   |                       | 1.2 V <sub>CC</sub> | . =                   | Vp-p    |

| Gain Error                                          |                                                     |                       | ±1                  | ±5                    | % of FS |

| Offset Error                                        |                                                     | 10                    | ±1                  |                       | % of FS |

| Load Resistance                                     |                                                     | 10                    |                     |                       | kΩ      |

| AC ACCURACY <sup>(6)</sup>                          |                                                     |                       |                     |                       |         |

| THD+N                                               | $f_{IN} = 1kHz, V_{OUT} = 0dB$                      |                       | -90                 | -82                   | dB      |

| Dynamic Range                                       |                                                     | 84                    | 92                  |                       | dB      |

| Signal-to-Noise Ratio                               |                                                     | 84                    | 94                  |                       | dB      |

| Crosstalk                                           | ADC Channel Idle, -0.5dB Input                      | 84                    | 92                  |                       | dB      |

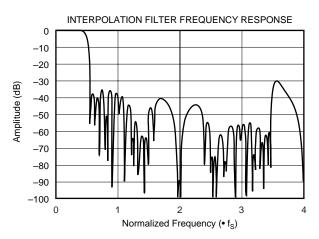

| Passband Ripple                                     | 0f <sub>S</sub> to 0.425f <sub>S</sub>              |                       | ±0.4                |                       | dB      |

| Group Delay                                         |                                                     |                       | 12/f <sub>S</sub>   | 4m                    | sec     |

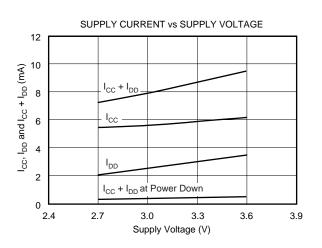

| POWER SUPPLY REQUIREMENTS                           |                                                     |                       | -                   |                       | a ana 1 |

| Voltage Range                                       | V <sub>CC</sub> , V <sub>DD</sub>                   | 2.7                   | 3.3                 | 3.6                   | VDC     |

| Supply Current in operation mode                    | $V_{CC} = V_{DD} = 3.3V$                            |                       | 9                   | 12                    | mA      |

| Total Supply Current in Power-Down Mode             | $V_{CC} = V_{DD} = 3.3V$ , XTI Stopped              |                       | 60                  |                       | μA      |

| Total Power Dissipation                             | $V_{CC} = V_{DD} = 3.3V$                            |                       | 30                  | 40                    | mW      |

|                                                     |                                                     |                       | 1                   | ~~ '                  |         |

| Operating                                           |                                                     | -25                   |                     | +85                   | °C<br>℃ |

| Storage<br>Thermal Resistance, $\theta_{IA}$        | 24 pin SSOD                                         | -55                   | 100                 | +125                  |         |

|                                                     | 24-pin SSOP                                         | 1                     | 100                 | I I                   | °C/W    |

NOTES: (1) Pins 6, 7, 8, 9, 10, 15, 17, 18, 19, 20 (M/S, TSC, BCK, FS, DIN, SCKIO, XTI, HPFD, LOOP,  $\overrightarrow{\text{PDWN}}$ ). (2) Pins 8, 9, 10, 15, 17 (BCK, FS, DIN, SCKIO, XTI (Schmitt-Trigger input). (3) Pins 6, 7, 18, 19, 20 (M/S, TSC, HPFD, LOOP,  $\overrightarrow{\text{PDWN}}$ ; (Schmitt-Trigger input with internal pull-down). (4) Pins 8, 9, 11, 12, 15, 16 (BCK, FS, DOUT, FSO, SCKIO, XTO). (5) If V<sub>COM</sub> load impedance (R<sub>COM</sub>) is lower than 100k $\Omega$ , the user needs to connect external resistors to AGND and V<sub>CC</sub> with resistance of R<sub>COM</sub>/10 or lower. (6) f<sub>IN</sub> = 1kHz, Audio Precision System II, RMS mode with 3.4kHz LPF, 100Hz HPF.

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, $+V_{DD}$ , $+V_{CC}^{(1)}$                     |                 |

|-----------------------------------------------------------------|-----------------|

| Supply Voltage Differences <sup>(2)</sup>                       |                 |

| GND Voltage Differences <sup>(3)</sup><br>Digital Input Voltage |                 |

| Input Current (any pins except supply)                          | ±10mA           |

| Power Dissipation                                               | 300mW           |

| Operating Temperature Range                                     | –25°C to +85°C  |

| Storage Temperature                                             | –55°C to +125°C |

| Junction Temperature                                            | 150°C           |

| Lead Temperature (soldering, 5s)                                | +260°C          |

| (reflow, 10s)                                                   | +235°C          |

NOTES: (1)  $V_{CC}$ ,  $V_{DD}$ . (2) Among  $V_{CC}$ ,  $V_{DD}$ . (3) Among AGND, DGND.

#### PACKAGE/ORDERING INFORMATION

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT  | PACKAGE      | PACKAGE<br>DRAWING<br>NUMBER | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(1)</sup> | TRANSPORT<br>MEDIA |

|----------|--------------|------------------------------|-----------------------------------|--------------------|-----------------------------------|--------------------|

| PCM3501E | 24-Lead SSOP | 338                          | −25°C to +85°C                    | PCM3501E           | PCM3501E                          | Rails              |

| "        | "            | "                            | "                                 | "                  | PCM3501E/2K                       | Tape and Reel      |

NOTE: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /2K indicates 2000 devices per reel). Ordering 2,000 pieces of "PCM3501E/2K" will get a single 2000-piece Tape and Reel.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

### **PIN CONFIGURATION**

Top View

|    | O PCM350           | 01                |    |

|----|--------------------|-------------------|----|

| 1  | V <sub>COM</sub>   | V <sub>cc</sub>   | 24 |

| 2  | V <sub>REF</sub> 1 | AGND              | 23 |

| 3  | V <sub>REF</sub> 2 | V <sub>OUT+</sub> | 22 |

| 4  | V <sub>IN+</sub>   | V <sub>OUT-</sub> | 21 |

| 5  | V <sub>IN-</sub>   | PDWN              | 20 |

| 6  | M/S                | LOOP              | 19 |

| 7  | TSC                | HPFD              | 18 |

| 8  | BCK                | ХТІ               | 17 |

| 9  | FS                 | хто               | 16 |

| 10 | DIN                | SCKIO             | 15 |

| 11 | DOUT               | DGND              | 14 |

| 12 | FSO                | $V_{DD}$          | 13 |

SSOP

#### **PIN ASSIGNMENTS**

| PIN | NAME               | I/O | DESCRIPTION                                                                                                                                                                                                        |

|-----|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>COM</sub>   | OUT | Common-Mode Voltage (0.5V <sub>CC)</sub> . This pin should be connected to ground through a capacitor.                                                                                                             |

| 2   | V <sub>REF</sub> 1 | _   | Decouple Pin for Reference Voltage 1 (0.99V <sub>CC</sub> ). This pin should be connected to ground through a capacitor.                                                                                           |

| 3   | V <sub>REF</sub> 2 | —   | Decouple Pin for Reference Voltage 2 (0.2V <sub>CC</sub> ). This pin should be connected to ground through a capacitor.                                                                                            |

| 4   | V <sub>IN+</sub>   | IN  | Non-Inverting input to on-chip AFE.                                                                                                                                                                                |

| 5   | V <sub>IN-</sub>   | IN  | Inverting input to on-chip AFE.                                                                                                                                                                                    |

| 6   | M/S                | IN  | Master/Slave Select. This pin is used to determine the operating mode for the serial interface. A logic '0' on this pin selects the Slave Mode. A logic '1' on this pin selects the Master Mode. <sup>(2)</sup>    |

| 7   | TSC                | IN  | Time Slot Mode Control. This pin is used to select the time slot operating mode. A logic '0' on this pin disables Time Slot Mode. A logic '1' on this pin enables Time Slot Mode. <sup>(2)</sup>                   |

| 8   | BCK                | I/O | Bit Clock. This pin serves as the bit (or shift) clock for the serial interface. This pin is an input in Slave Mode and an output in Master Mode. <sup>(1)</sup>                                                   |

| 9   | FS                 | I/O | Frame Sync. This pin serves as the frame synchronization clock for the serial interface. This pin is an input in Slave Mode and an output in Master Mode. <sup>(1)</sup>                                           |

| 10  | DIN                | IN  | Serial Data Input. This pin is used to write 16-bit data to the DAC. <sup>(1)</sup>                                                                                                                                |

| 11  | DOUT               | OUT | Serial Data Output. The ADC outputs 16-bit data on this pin. <sup>(3)</sup>                                                                                                                                        |

| 12  | FSO                | OUT | Frame Sync Output. Active only when Time Slot Mode is enabled. This pin is set to a high impedance state when Time Slot mode is disabled (TSC = 0).                                                                |

| 13  | $V_{DD}$           | —   | Digital Power Supply. Used to power the digital section of the ADC and DAC, as well as the serial interface and mode control logic. This pin is not internally connected to V <sub>CC</sub> .                      |

| 14  | DGND               | _   | Digital Ground. Internally connected through the substrate to analog ground.                                                                                                                                       |

| 15  | SCKIO              | I/O | System Clock Input/Output. This pin is a system clock output when using the crystal oscillator or XTI as the system clock input; when XTI is connected to ground, this pin is a system clock input. <sup>(1)</sup> |

| 16  | хто                | OUT | Crystal Oscillator Output.                                                                                                                                                                                         |

| 17  | XTI                | IN  | Crystal Oscillator Input or an External System Clock Input.                                                                                                                                                        |

| 18  | HPFD               | IN  | High-Pass Filter Disable. When this pin is set to a logic '1', the HPF function in the ADC is disabled. <sup>(2)</sup>                                                                                             |

| 19  | LOOP               | IN  | ADC-to-DAC Loop-Back Control. When this pin is set to logic '1', the ADC data is fed to the DAC input. <sup>(2)</sup>                                                                                              |

| 20  | PDWN               | IN  | Power Down and Reset Control. When this pin is logic '0', Power-Down Mode is enabled. The PCM3500 is reset on the rising edge of this signal. <sup>(2)</sup>                                                       |

| 21  | V <sub>OUT-</sub>  | OUT | Inverting output.                                                                                                                                                                                                  |

| 22  | V <sub>OUT+</sub>  | OUT | Non-inverting output.                                                                                                                                                                                              |

| 23  | AGND               | —   | Analog Ground. This is the ground for the internal analog circuitry.                                                                                                                                               |

| 24  | V <sub>CC</sub>    | —   | Analog Power Supply. Used to power the analog circuitry of the ADC and DAC.                                                                                                                                        |

NOTES: (1) Schmitt-Trigger input. (2) Schmitt-Trigger input with an internal pull-down resistor. (3) Tri-state output in Time Slot Mode.

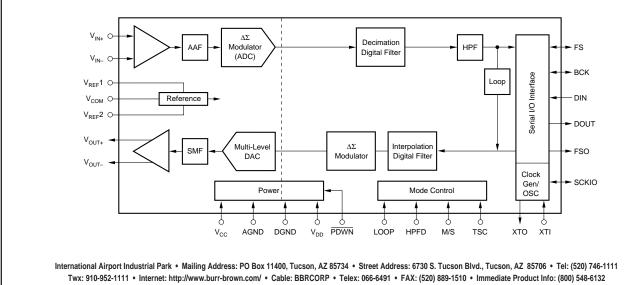

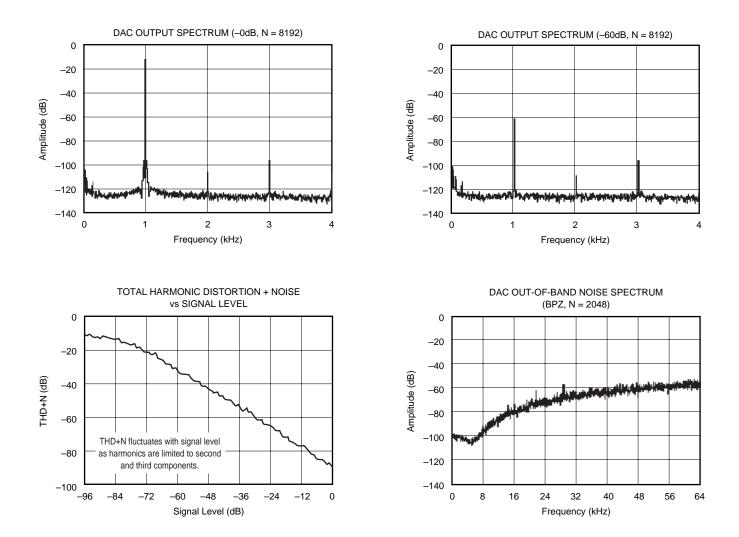

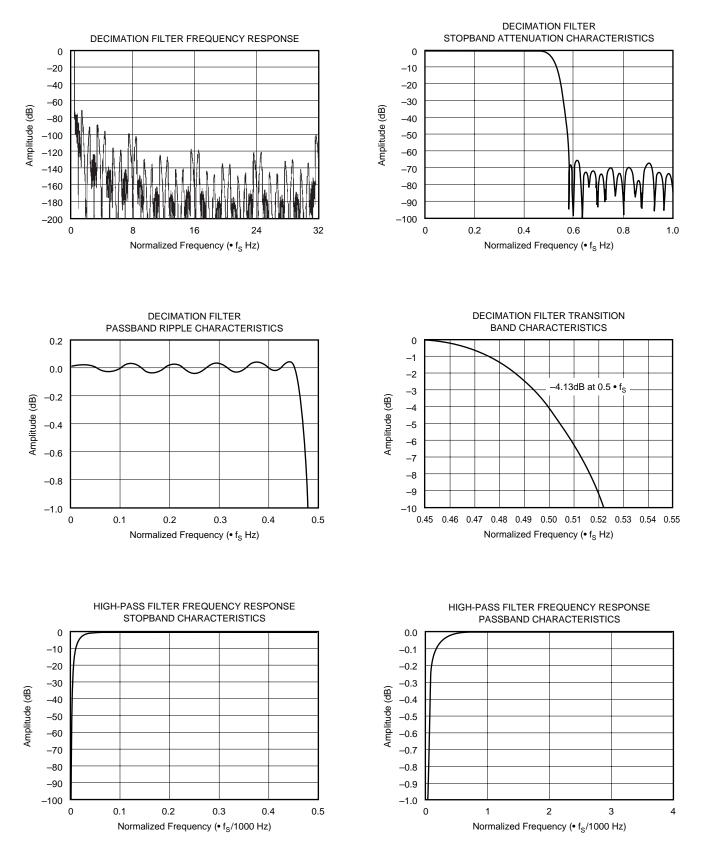

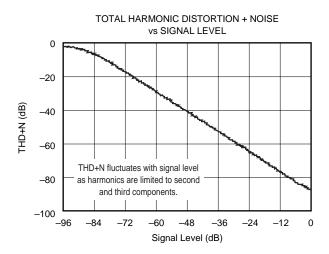

## **TYPICAL PERFORMANCE CURVES**

DAC SECTION

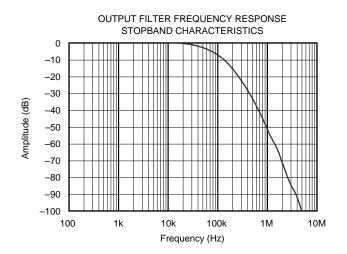

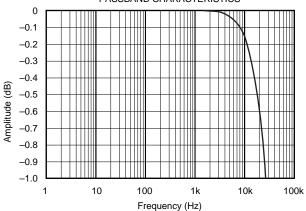

**DIGITAL FILTER**

ANALOG FILTER

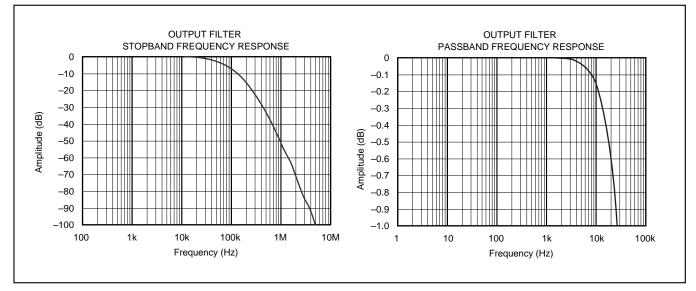

OUTPUT FILTER FREQUENCY RESPONSE PASSBAND CHARACTERISTICS

$T_A = +25^{\circ}C$ ,  $V_{CC} = V_{DD} = +3.3V$ ,  $f_S = 8kHz$ , and  $f_{SIGNAL} = 1kHz$ , unless otherwise specified.

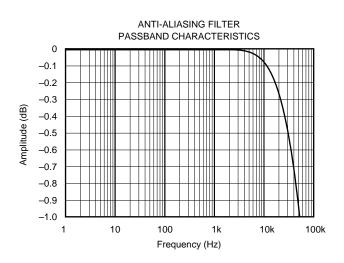

### DAC SECTION DAC OUTPUT SPECTRA

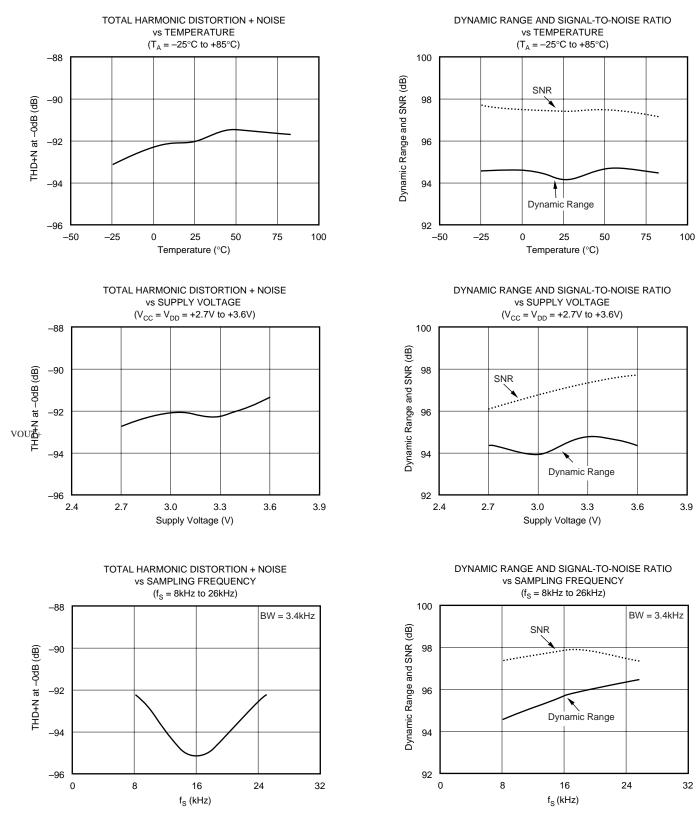

## DAC SECTION

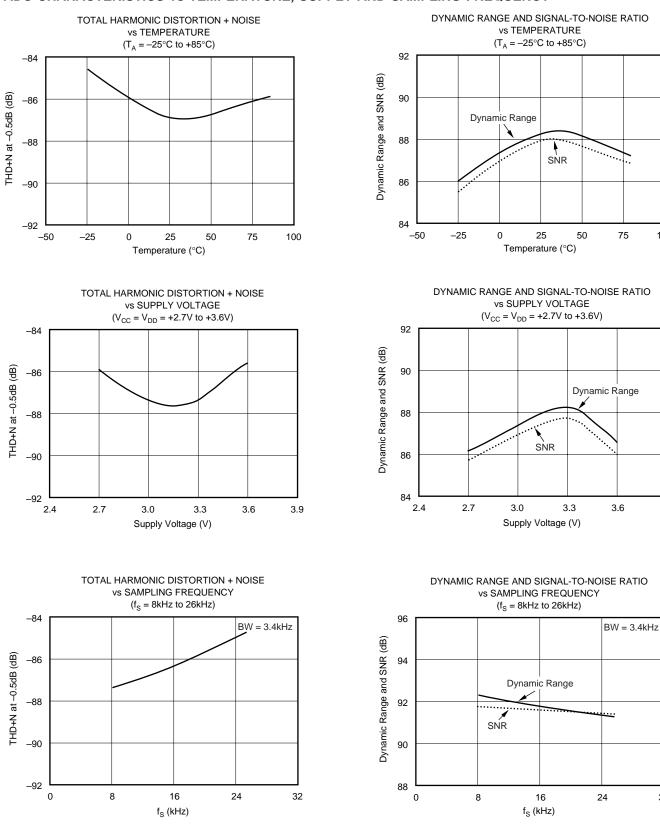

### DAC CHARACTERISTICS vs TEMPERATURE, SUPPLY, AND SAMPLING FREQUENCY

### **TYPICAL PERFORMANCE CURVES**

ADC SECTION

**DIGITAL FILTER**

BURR - BROWN

$T_A = +25^{\circ}C$ ,  $V_{CC} = V_{DD} = +3.3V$ ,  $f_S = 8kHz$ , and  $f_{SIGNAL} = 1kHz$ , unless otherwise specified.

ADC SECTION

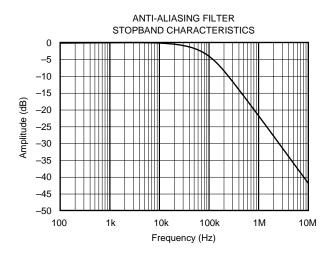

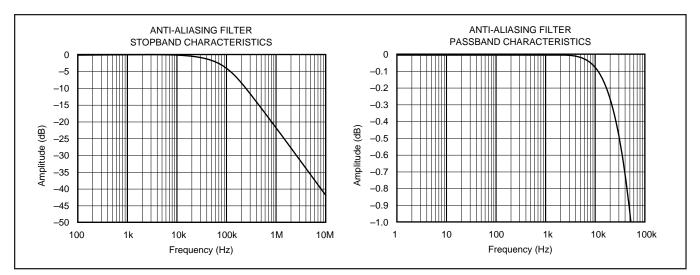

ANALOG FILTER

#### ADC OUTPUT SPECTRA

OUTPUT SPECTRUM (-60dB, N = 8192)  $(T_A = 25^{\circ}C, V_{CC} = V_{DD} = 3.3V, f_S = 8kHz, f_{SIGNAL} = 1kHz)$ 0 -20 -40 Amplitude (dB) -60 -80 -100 -120 -140 3 0 1 2 4 Frequency(kHz)

$T_A = +25^{\circ}C$ ,  $V_{CC} = V_{DD} = +3.3V$ ,  $f_S = 8kHz$ , and  $f_{SIGNAL} = 1kHz$ , unless otherwise specified.

# ADC SECTION

### ADC CHARACTERISTICS vs TEMPERATURE, SUPPLY AND SAMPLING FREQUENCY

100

39

32

$T_{A} = +25^{\circ}C, \ V_{CC} = V_{DD} = +3.3V, \ f_{S} = 8kHz, \ and \ f_{SIGNAL} = 1kHz, \ unless \ otherwise \ specified.$

### SUPPLY CURRENT vs SUPPLY VOLTAGE AND SAMPLING FREQUENCY

### SYSTEM CLOCK AND RESET/ POWER DOWN

### SYSTEM CLOCK INPUT AND OUTPUT

The PCM3501 requires a system clock for operating the digital filters and delta-sigma data converters.

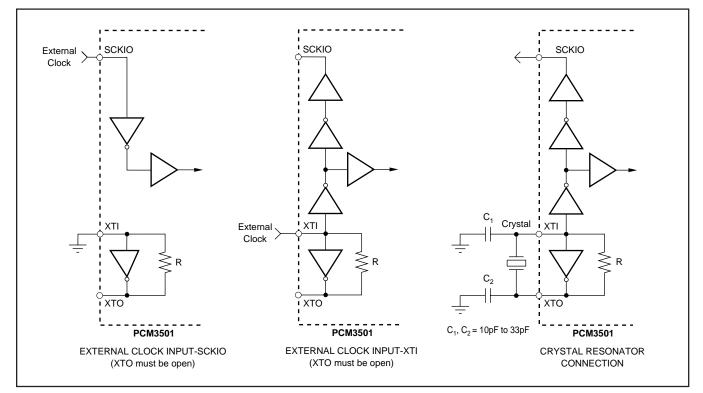

The system clock may be supplied from an external master clock or generated using the on-chip crystal oscillator circuit. Figure 1 shows the required connections for external and crystal clock operation. The system clock must operate at 512 times the sampling frequency,  $f_s$ , with sampling frequencies from 7.2kHz to 26kHz. This gives an effective system clock frequency range of 3.6864MHz to 13.312MHz.

Table I shows system clock frequencies for common sampling frequencies.

For external clock operation, XTI (pin 17) or SCKIO (pin 15) is driven by a master clock source. If SCKIO is used as the system clock input, then XTI must be connected to ground.

| SAMPLING FREQUENCY (kHz) | SYSTEM CLOCK FREQUENCY (MHz) |

|--------------------------|------------------------------|

| 8                        | 4.096                        |

| 11.025                   | 5.6448                       |

| 16                       | 8.192                        |

| 22.05                    | 11.2896                      |

| 24                       | 12.288                       |

TABLE I. System Clock Frequencies for Common Sampling Frequencies.

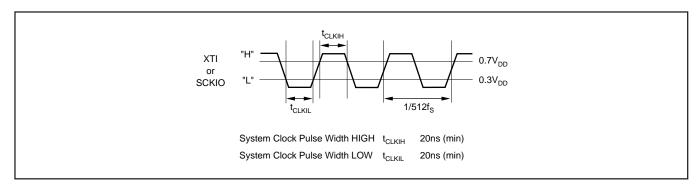

For either case, XTO (pin 16) should be left open. The system clock source should be free of noise and exhibit low phase jitter in order to obtain optimal dynamic performance from the PCM3501. Figure 2 shows the system clock timing requirements associated with an external master clock.

For crystal oscillator operation, a crystal is connected between XTI (pin 17) and XTO (pin 16), along with the necessary load capacitors (10pF to 33pF per pin, as shown in Figure 1). A fundamental-mode, parallel resonant crystal is required.

FIGURE 1. System Clock Generation.

FIGURE 2. External System Clock Timing Requirements.

#### **Reset and Power Down**

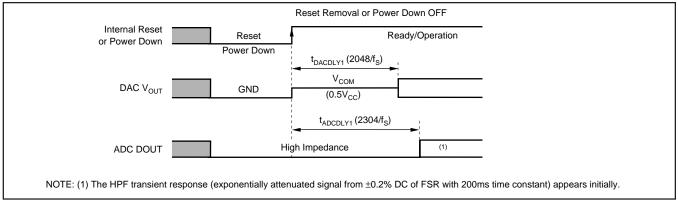

The PCM3501 supports power-on reset, external reset, and power-down operations. Power-on reset is performed by internal circuitry automatically at power up, while the external reset is initiated using the PDWN input (pin 20).

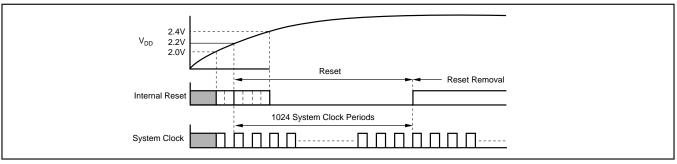

Power-on reset occurs when power and system clock are initially applied to the PCM3501. The internal reset circuitry requires that the system clock be active at power up, with at least three system clock cycles occurring prior to  $V_{DD} = 2.2V$ . When  $V_{DD}$  exceeds 2.2V, the power-on reset comparator enables the initialization sequence, which requires 1024 system clock periods for completion. During the initialization sequence, the DAC output is forced to AGND, and the ADC output is forced to a high impedance state. After the initialization sequence has completed, the DAC and ADC outputs experience a delay before they output a valid signal or data. Refer to Figures 3 and 5 for power-on reset and post-reset delay timing.

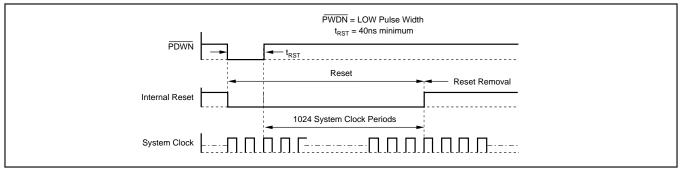

External reset is performed by first setting  $\overline{PDWN} = 0^{\circ}$  and then setting  $\overline{PDWN} = 1^{\circ}$ . The LOW to HIGH transition on

PDWN causes the reset initialization sequence to start. During the initialization sequence, the DAC output is forced to AGND, and the ADC output is forced to a high impedance state. After the initialization sequence has completed, the DAC and ADC outputs experience a delay before they output a valid signal or data. Refer to Figures 4 and 5 for external reset and post-reset delay timing.

Power-down mode is enabled by setting  $\overline{PDWN} = '0'$ . During power-down mode, minimum current is drawn when the system clock is removed, resulting in 60µA (typical) power supply current. The  $\overline{PDWN}$  input includes an internal pull-down resistor, which places the PCM3501 in powerdown mode at power-up if the  $\overline{PDWN}$  pin is left unconnected. Ideally, the  $\overline{PDWN}$  input should be driven by active logic in order to control reset and power-down operation. If the  $\overline{PDWN}$  pin is to be unused in the system application, it should be connected to  $V_{DD}$  to enable normal operation. By setting  $\overline{PDWN} = '1'$  when exiting power-down mode, the PCM3501 will initiate an external reset as described earlier in this section.

FIGURE 3. Power-On Reset Timing.

FIGURE 4. External Reset Timing.

FIGURE 5. DAC and ADC Output for Reset and Power Down.

#### SERIAL INTERFACE

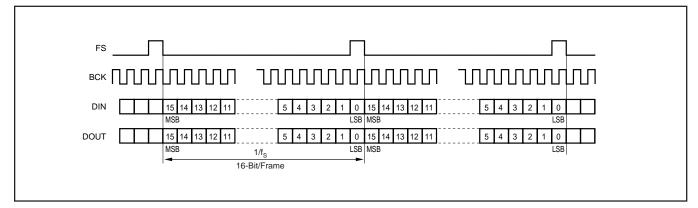

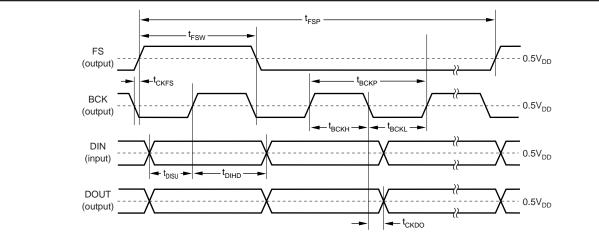

The serial interface of the PCM3501 is a 4-wire synchronous serial port. It includes FS (pin 9), BCK (pin 8), DIN (pin 10) and DOUT (pin 11). FS is the frame synchronization clock, BCK is the serial bit or shift clock, DIN is the serial data input for the DAC, and DOUT is the serial data output for the ADC.

The frame sync, FS, operates at the sampling frequency  $(f_S)$ . The bit clock, BCK, operates at  $16f_S$  for normal operation. DIN and DOUT also operate at the bit clock rate. Both FS and BCK must be synchronous with the system clock (guaranteed in Master Mode). Data for DIN is clocked into the serial interface on the rising edge of BCK, while data for DOUT is clocked out of the serial interface on the falling edge of BCK.

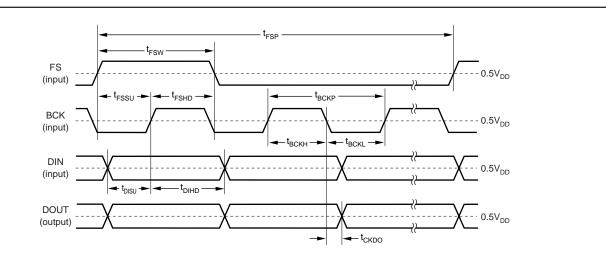

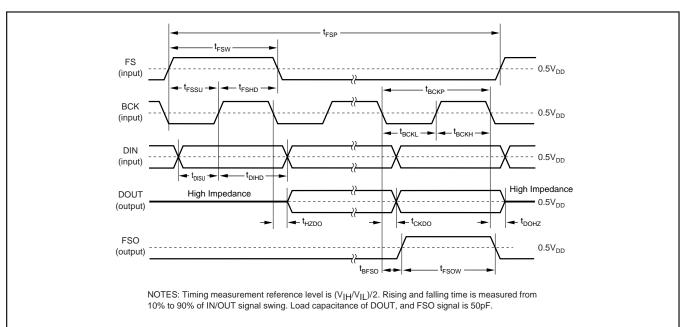

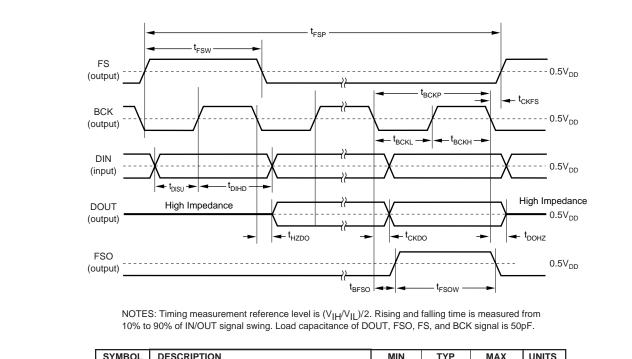

Figure 6 shows the serial interface format for the PCM3501. The serial data for DIN and DOUT must be in Binary Two's Complement, MSB-first format. Figures 7 and 8 show the timing specifications for the serial interface when used in Slave and Master Modes.

FIGURE 6. Serial Interface Format.

| SYMBOL            | DESCRIPTION                         | MIN                    | ТҮР               | MAX                    | UNITS |

|-------------------|-------------------------------------|------------------------|-------------------|------------------------|-------|

| t <sub>BCKP</sub> | BCK Period                          | 2400                   |                   |                        | ns    |

| t <sub>BCKH</sub> | BCK Pulse Width HIGH                | 800                    |                   |                        | ns    |

| t <sub>BCKL</sub> | BCK Pulse Width LOW                 | 800                    |                   |                        | ns    |

| t <sub>FSW</sub>  | FS Pulse Width HIGH                 | t <sub>BCKP</sub> – 60 | t <sub>BCKP</sub> | t <sub>BCKP</sub> + 60 | ns    |

| t <sub>FSP</sub>  | FS Period                           |                        | 1/f <sub>S</sub>  |                        |       |

| t <sub>FSSU</sub> | FS Set Up Time to BCK Rising Edge   | 60                     |                   |                        | ns    |

| t <sub>FSHD</sub> | FS Hold Time to BCK Rising Edge     | 60                     |                   |                        | ns    |

| t <sub>DISU</sub> | DIN Set Up Time to BCK Rising Edge  | 60                     |                   |                        | ns    |

| t <sub>DIHD</sub> | DIN Hold Time to BCK Rising Edge    | 60                     |                   |                        | ns    |

| t <sub>CKDO</sub> | Delay Time BCK Falling Edge to DOUT | 0                      |                   | 80                     | ns    |

| t <sub>R</sub>    | Rising Time of All Signals          |                        |                   | 30                     | ns    |

| t <sub>F</sub>    | Falling Time of All Signals         |                        |                   | 30                     | ns    |

FIGURE 7. Serial Interface Timing for Slave Mode.

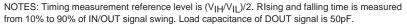

NOTES: Timing measurement reference level is ( $V_{IH}/V_{IL}$ )/2. Rising and falling time is measured from 10% to 90% of IN/OUT signal swing. Load capacitance of DOUT, FS, BCK signal is 50pF.

| SYMBOL            | DESCRIPTION                         | MIN                    | TYP               | MAX                    | UNITS |

|-------------------|-------------------------------------|------------------------|-------------------|------------------------|-------|

| t <sub>BCKP</sub> | BCK Period                          | 2400                   |                   | 16000                  | ns    |

| t <sub>BCKH</sub> | BCK Pulse Width HIGH                | 1200                   |                   | 8000                   | ns    |

| t <sub>BCKL</sub> | BCK Pulse Width LOW                 | 1200                   |                   | 8000                   | ns    |

| t <sub>CKFS</sub> | Delay Time BCK Falling Edge to FS   | - 40                   |                   | 40                     | ns    |

| t <sub>FSW</sub>  | FS Pulse Width HIGH                 | t <sub>BCKP</sub> – 60 | t <sub>BCKP</sub> | t <sub>BCKP</sub> + 60 | ns    |

| t <sub>FSP</sub>  | FS Period                           |                        | 1/f <sub>S</sub>  |                        |       |

| t <sub>DISU</sub> | DIN Set Up Time to BCK Rising Edge  | 60                     |                   |                        | ns    |

| t <sub>DIHD</sub> | DIN Hold Time to BCK Rising Edge    | 60                     |                   |                        | ns    |

| t <sub>CKDO</sub> | Delay Time BCK Falling Edge to DOUT | 0                      |                   | 80                     | ns    |

| t <sub>R</sub>    | Rising Time of All Signals          |                        |                   | 30                     | ns    |

| t <sub>F</sub>    | Falling Time of All Signals         |                        |                   | 30                     | ns    |

FIGURE 8. Serial Interface Timing for Master Mode.

FIGURE 9. Slave and Master Mode Connections.

#### **MASTER/SLAVE OPERATION**

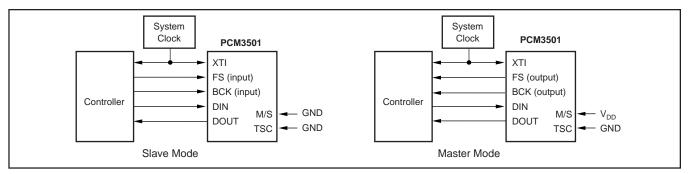

The serial interface supports both Slave and Master Mode operation. The mode is selected by the M/S input (pin 6). Table II shows mode and pin settings corresponding to the M/S input selection. Figure 9 shows connections for Slave and Master mode operation.

| M/S (PIN 6) | SERIAL<br>INTERFACE<br>MODE | FS (PIN) | BCK (PIN 8) |

|-------------|-----------------------------|----------|-------------|

| 0           | Slave                       | Input    | Input       |

| 1           | Master                      | Output   | Output      |

TABLE II. Master/Slave Mode Selection.

### **Slave Mode Operation**

In Slave Mode, the FS and BCK pins are inputs to the PCM3501. Both FS and BCK should be derived from the system clock signal (XTI or SCKIO) to ensure proper synchronization. Slave Mode is best suited for applications where the DSP or controller is capable of generating the FS, BCK, and system clocks using an on-chip serial port and/or timing generator.

#### **Master Mode Operation**

In Master Mode operation, both FS and BCK are clock outputs generated by the PCM3501 from the system clock input (XTI, SCKIO, or a crystal). In Master Mode, the timing and phase relationships between system clock, FS, and BCK are managed internally to provide optimal synchronization.

#### SYNCHRONIZATION REQUIREMENTS

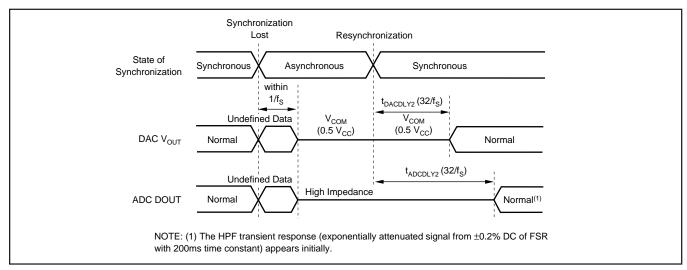

The PCM3501 requires that FS and BCK be synchronous with the system clock. Internal circuitry is included to detect a loss of synchronization between FS and the system clock input. If the phase relationship between FS and the system clock varies more than  $\pm$  1.5 BCK periods, the PCM3501 will detect a loss of synchronization. Upon detection, the DAC output is forced to 0.5V<sub>CC</sub> and the DOUT pin is forced to a high impedance state. This occurs within one sampling clock (FS) period of initial detection. Figure 10 shows the loss of synchronization operation and the DAC and ADC output delays associated with it.

#### TIME SLOT OPERATION

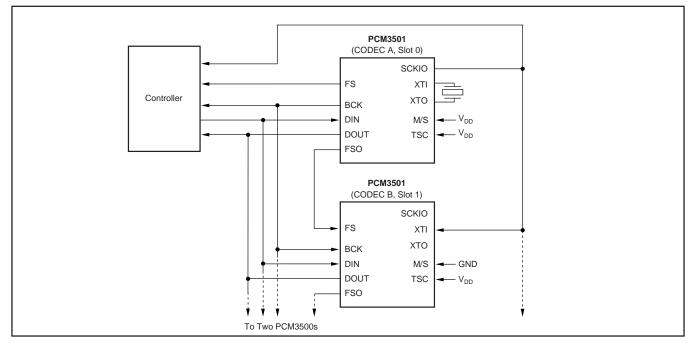

The PCM3501 serial interface supports Time Division Multiplexing (TDM) using the Time Slot Mode. Up to four PCM3501s may be connected on the same 4-wire serial interface bus. This is useful for system applications that require multiple modem or voice channels. Figure 11 shows examples of Time Slot Mode connections.

Time Slot Mode defines a 64-bit long frame, composed of four time slots. Each slot is 16 bits long and corresponds to one of four CODECs. The FS pin on the first PCM3501 (CODEC A, Slot 0) is used as the master frame sync, and operates at the sampling frequency,  $f_S$ . The bit clock, BCK, operates at 64 $f_S$ . DIN and DOUT of each CODEC also operate at 64 $f_S$ . Figure 12 shows the operation of the Time Slot Mode.

Time Slot operation is enabled or disabled using the TSC input (pin 7). The state of the TSC pin is updated at poweron reset, or on the rising edge of PWDN input (if using external reset or power-down mode). A forced reset is required when changing from Slave to Master Mode, or visa versa, in real time.

FIGURE 10. Loss of Synchronization Operation and Timing.

FIGURE 11. Time Slot Mode Connections.

|          | CODEC A         | CODEC B         | CODEC C         | CODEC D         |

|----------|-----------------|-----------------|-----------------|-----------------|

| FS       | Slot 0, 16 Bits | Slot 1, 16 Bits | Slot 2, 16 Bits | Slot 3, 16 Bits |

|          |                 |                 |                 |                 |

| BCK      | ╶╢║║╌╌┨║║╌╌╌┨║  | ] []] [] []]    | MJ              | UU <u>4</u> U   |

| S (A)    | Π               |                 |                 | Г_              |

| O (A)    |                 |                 |                 |                 |

| S (B)    |                 |                 |                 |                 |

| O (B)    |                 | ļ               |                 |                 |

| S (C)    |                 | ,               |                 |                 |

| <b>-</b> |                 |                 |                 |                 |

|          |                 |                 | J               |                 |

| S (D)    |                 |                 |                 |                 |

| O (D)    |                 |                 |                 |                 |

| DIN      |                 |                 |                 |                 |

| IT (A)   | MSB LSB         |                 | High Impedance  |                 |

|          |                 |                 | High Imp        | L               |

| т (в)    | [               |                 |                 |                 |

| т (С)    | High Imped      | ance            |                 | High Impedance  |

| T (D)    |                 | High Impedance  |                 |                 |

| T (D)    |                 |                 |                 |                 |

FIGURE 12. Time Slot Mode Operation.

Table III shows the TSC pin settings and corresponding mode selections. When Time Slot Mode is enabled, FSO (pin 12) is used as a frame sync output, which is connected to the FS input of the next PCM3501 in the Time Slot sequence. Figures 13 and 14 provide detailed timing for Time Slot Mode operation.

| TSC (PIN 7) | TIME SLOT MODE                            |

|-------------|-------------------------------------------|

| 0           | Time Slot Mode Disabled, Normal Operation |

| 1           | Time Slot Operation Enable                |

TABLE III. Time Slot Mode Selection.

#### ADC-TO-DAC LOOP BACK

The PCM3501 includes a Loop-Back Mode, which directly feeds the ADC data to the DAC input. This mode is designed for diagnostic testing and system adjustment. Loop-Back Mode is enabled and disabled using the LOOP input (pin 19). Table IV shows the LOOP pin settings and corresponding mode selections. The serial interface continues to operate in Loop-Back Mode, allowing the host to read the ADC data at the DOUT pin.

| LOOP (PIN 19) | LOOP-BACK MODE                            |

|---------------|-------------------------------------------|

| 0             | Loop-Back Mode Disabled, Normal Operation |

| 1             | Loop-Back Mode Enabled                    |

TABLE IV. Loop-Back Mode Selection.

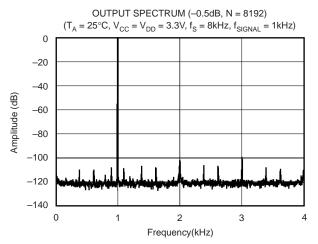

#### **HIGH-PASS FILTER**

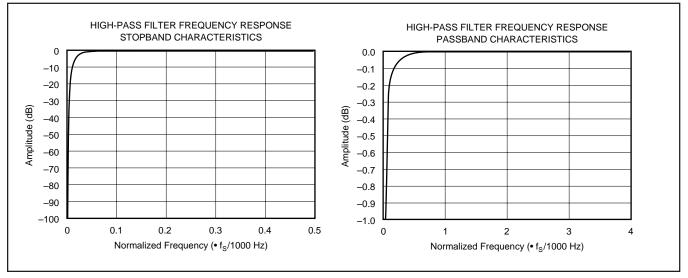

The PCM3501 includes a digital high-pass filter in the ADC which may be used to remove the DC offset created by the analog front-end (AFE) section. The high-pass filter response is shown in Figure 15. The high-pass filter may be enabled or disabled using the HPFD input (pin 18). Table V shows the HPFD pin settings and corresponding mode selections.

| HPFD (PIN 18) | HIGH-PASS FILTER MODE |  |  |  |  |

|---------------|-----------------------|--|--|--|--|

| 0             | High-Pass Filter On   |  |  |  |  |

| 1             | High-Pass Filter Off  |  |  |  |  |

TABLE V. High-Pass Filter Mode Selection.

| SYMBOL            | DESCRIPTION                                  | MIN             | ТҮР               | MAX                    | UNITS |

|-------------------|----------------------------------------------|-----------------|-------------------|------------------------|-------|

| t <sub>BCKP</sub> | BCK Period                                   | 600             |                   |                        | ns    |

| t <sub>BCKH</sub> | BCK Pulse Width HIGH                         | 200             |                   |                        | ns    |

| t <sub>BCKL</sub> | BCK Pulse Width LOW                          | 200             |                   |                        | ns    |

| t <sub>FSW</sub>  | FS Pulse Width HIGH                          | $t_{BCKP} - 60$ | t <sub>BCKP</sub> | t <sub>BCKP</sub> + 60 | ns    |

| t <sub>FSP</sub>  | FS Period                                    |                 | 1/f <sub>S</sub>  |                        |       |

| t <sub>FSSU</sub> | FS Set Up TIme to BCK Rising Edge            | 60              |                   |                        | ns    |

| t <sub>FSHD</sub> | FS Hold Time to BCK Rising Edge              | 60              |                   |                        | ns    |

| t <sub>DISU</sub> | DIN Set Up Time to BCK Rising Edge           | 60              |                   |                        | ns    |

| t <sub>DIHD</sub> | DIN Hold Time to BCK Rising Edge             | 60              |                   |                        | ns    |

| t <sub>CKDO</sub> | Delay Time BCK Falling Edge to DOUT          | 0               |                   | 80                     | ns    |

| t <sub>HZDO</sub> | Delay Time BCK Falling Edge to DOUT Active   |                 | 20                |                        | ns    |

| t <sub>DOHZ</sub> | Delay Time BCK Falling Edge to DOUT Inactive |                 | 19.5              |                        | ns    |

| t <sub>FSOW</sub> | FSO Pulse Width HIGH                         | $t_{BCKP} - 60$ | t <sub>BCKP</sub> | t <sub>BCKP</sub> + 60 | ns    |

| t <sub>BFSO</sub> | Delay Time BCK Falling Edge to FSO           | 0               |                   | 80                     | ns    |

| t <sub>R</sub>    | Rising Time of All Signals                   |                 |                   | 30                     | ns    |

| t <sub>F</sub>    | Falling Time of All Signals                  |                 |                   | 30                     | ns    |

FIGURE 13. Serial Interface Timing for Time Slot Mode Operation (Slave Mode).

| SYMBOL            | DESCRIPTION                                  | MIN                    | TYP               | MAX                    | UNITS |

|-------------------|----------------------------------------------|------------------------|-------------------|------------------------|-------|

| t <sub>BCKP</sub> | BCK Period                                   | 600                    |                   | 4000                   | ns    |

| t <sub>BCKH</sub> | BCK Pulse Width HIGH                         | 300                    |                   | 2000                   | ns    |

| t <sub>BCKL</sub> | BCK Pulse Width LOW                          | 300                    |                   | 2000                   | ns    |

| t <sub>CKFS</sub> | Delay Time BCK Falling Edge to FS            | -40                    |                   | 40                     | ns    |

| t <sub>FSW</sub>  | FS Pulse Width HIGH                          | t <sub>BCKP</sub> – 60 | t <sub>BCKP</sub> | t <sub>BCKP</sub> + 60 | ns    |

| t <sub>FSP</sub>  | FS Period                                    |                        | 1/f <sub>S</sub>  |                        |       |

| t <sub>DISU</sub> | DIN Set Up Time to BCK Rising Edge           | 60                     |                   |                        | ns    |

| t <sub>DIHD</sub> | DIN Hold Time to BCK Rising Edge             | 60                     |                   |                        | ns    |

| t <sub>CKDO</sub> | Delay Time BCK Falling Edge to DOUT          | 0                      |                   | 80                     | ns    |

| t <sub>HZDO</sub> | Delay Time BCK Falling Edge to DOUT Active   |                        | 20                |                        | ns    |

| t <sub>DOHZ</sub> | Delay Time BCK Falling Edge to DOUT Inactive |                        | 19.5              |                        | ns    |

| t <sub>FSOW</sub> | FSO Pulse Width HIGH                         | t <sub>BCKP</sub> – 60 | t <sub>BCKP</sub> | t <sub>BCKP</sub> + 60 | ns    |

| t <sub>BFSO</sub> | Delay Time BCK Falling Edge to FSO           | 0                      |                   | 80                     | ns    |

| t <sub>R</sub>    | Rising Time of All Signals                   |                        |                   | 30                     | ns    |

| t <sub>F</sub>    | Falling Time of All Signals                  |                        |                   | 30                     | ns    |

FIGURE 14. Serial Interface Timing for Time Slot Mode Operation (Master Mode).

FIGURE 15. High-Pass Filter Response.

## **APPLICATIONS INFORMATION**

### **BASIC CIRCUIT CONNECTIONS**

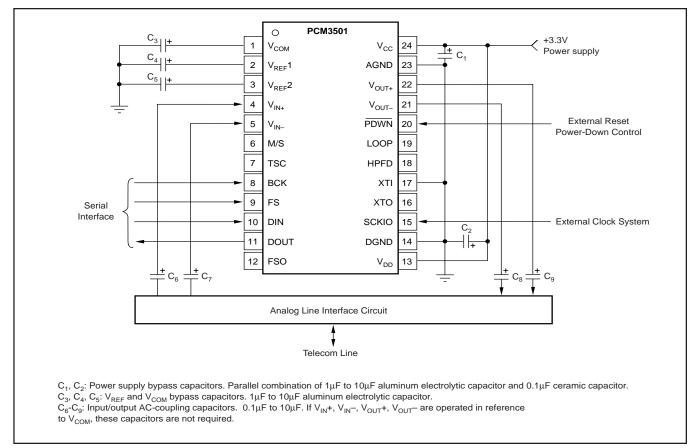

The basic connection diagram for the PCM3501 is shown in Figure 16. Included are the required power supply bypass and reference decoupling capacitors. The DAC output,  $V_{OUT}$ , and the ADC input,  $V_{IN}$ , should be AC-coupled to external circuitry.

#### **Reference Pin Connections**

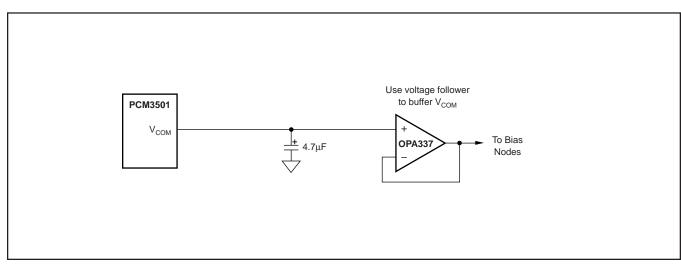

The  $V_{COM}$  voltage is used internally to bias the input and output amplifier stages of the PCM3501. It is brought out

unbuffered on pin 1 for decoupling. A  $1\mu$ F to  $10\mu$ F aluminum electrolytic or tantalum capacitor is recommended for decoupling purposes. This capacitor should be located as close as possible to pin 1.

The V<sub>COM</sub> voltage is typically equal to V<sub>CC</sub>/2, and may be used to bias external input and output circuitry. However, since the V<sub>COM</sub> pin is not a buffered output, it must drive a high impedance load to avoid excessive loading. Buffering the V<sub>COM</sub> pin with an external op amp configured as a voltage follower is recommended when driving multiple bias nodes. Figure 17 shows an example of using V<sub>COM</sub> with external circuitry.

FIGURE 16. Basic Connection Diagram.

FIGURE 17. Using  $V_{COM}$  to Bias External Circuitry.

$V_{REF}1$  (pin 2) and  $V_{REF}2$  (pin 3) are reference voltages used by the delta-sigma modulators. They are brought out strictly for decoupling purposes.  $V_{REF}1$  and  $V_{REF}2$  are not to be used to bias external circuits. A 1µF to 10µF aluminum electrolytic or tantalum capacitor is recommended for decoupling on each pin. These capacitors should be located as close as possible to pins 2 and 3.

#### **Power Supplies and Grounding**

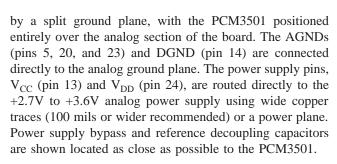

$V_{CC}$  (pin 24) and  $V_{DD}$  (pin 13) should be connected directly to the +2.7V to +3.6V analog power supply, as shown in Figure 16. The AGNDs (pins 5, 21, and 23) and DGND (pin 14) should be connected directly to the analog ground. Power supply bypass capacitors should be located as close to the power supply pins as possible in order to ensure a low impedance connection. A combination of a 10µF aluminum electrolytic or tantalum capacitor in parallel with a 0.1µF ceramic capacitor is recommended for both  $V_{CC}$  and  $V_{DD}$ .

$V_{DD}$  and  $V_{CC}$  should not be connected to separate digital and analog power supplies. This can lead to an SCR latch-up condition, which can cause either degraded device performance or catastrophic failures.

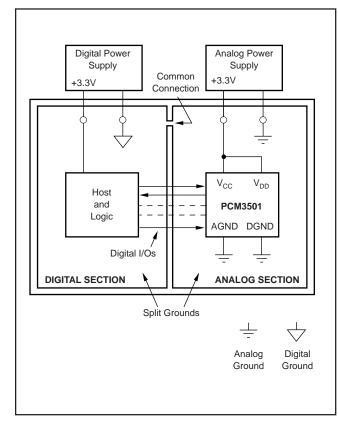

#### PCB LAYOUT GUIDELINES

The recommended PCB layout technique is shown in Figure 18. The analog and digital section of the board are separated

The PCM3501 is oriented so that the digital pins are facing the ground plane split. Digital connections should be made as short and direct as possible to limit high frequency radiation and coupling. Series resistors (from  $20\Omega$  to  $100\Omega$ ) may be put in series with the system clock, FS, BCK, and FSO lines to reduce or eliminate overshoot on clock edges, further reducing radiated emissions. The split ground plane should be connected at one point by a trace, wire, or ferrite bead. Often the board will be designed to have several jumper points for the common ground connection, so that the best performance can be derived through experimentation.

An alternative technique, using a single power supply or battery, is shown in Figure 19. This technique is more suitable for portable applications.

FIGURE 18. Recommended PCB Layout Technique.

FIGURE 19. PCB Layout Using a Single-Supply or Battery.

#### OUTPUT FILTER CIRCUITS FOR THE DAC

The PCM3501's DAC uses delta-sigma conversion techniques. It uses oversampling and noise shaping to improve in-band ( $f = f_S/2$ ) signal-to-noise performance at the expense of increased out-of-band noise. The DAC output must be low-pass filtered to attenuate the out-of-band noise to a reasonable level.

The PCM3501 includes a low-pass filter in the on-chip output amplifier circuit. The frequency response for this filter is shown in Figure 20. Although this filter helps to lower the out-of-band noise, it is not adequate for many applications. This is especially true for applications where the sampling frequency is below 16kHz, since the out-of-band noise above  $f_S/2$  is in the audio spectrum. An external filter circuit, either passive or active, is required to provide additional attenuation of the out-of-band noise. The low-pass filter order will be dependent upon the out-of-band

noise requirements for a particular system. Generally, a 2ndorder or better low-pass circuit will be required, with the cut-off frequency set to  $f_8/2$  or less.

Burr-Brown Application Bulletin AB-034 provides information for designing both Multiple Feedback and Sallen-Key active filter circuits using software available from Burr-Brown's web site. Another excellent reference for both passive and active filter design is the "*Electronic Filter Design Handbook, Third Edition*" by Williams and Taylor, published by McGraw-Hill.

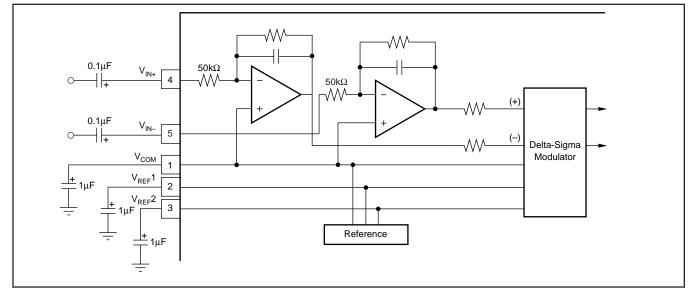

#### ON-CHIP ANALOG FRONT END FOR THE ADC

The PCM3501 A/D converter includes a fully differential input delta-sigma modulator. In order to simplify external circuitry, an analog front end (AFE) circuit has been included on the PCM3501 just prior to the modulator. The AFE circuit is shown in Figure 21.

FIGURE 20. DAC Output Amplifier Filter Response.

FIGURE 21. On-Chip AFE Circuit for the ADC.

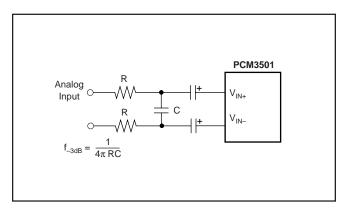

The AFE circuit consists of a buffer/filter for each input of the converter. The frequency response for the filter is shown in Figure 22. Since the delta-sigma modulator oversamples the input at  $64f_S$ , the anti-alias filter requirements are relaxed, with only a single-pole filter being required. If an application requires further band limiting of the input signal, a simple RC filter at the inputs can be used, as shown in Figure 23.

FIGURE 23. Optional External Low-Pass Filter for the ADC.

## THEORY OF OPERATION

### ADC SECTION

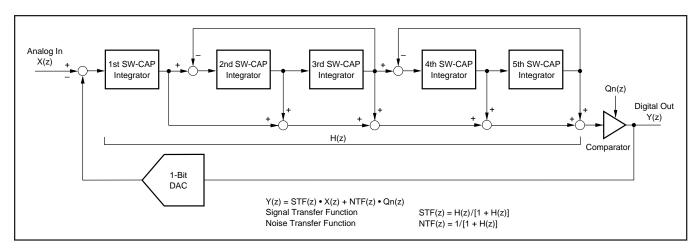

The PCM3501 A/D converter consists of two reference circuits, differential input buffer, a fully differential 5thorder delta-sigma modulator, a decimation filter (including digital high pass), and a serial interface circuit. The block diagram on the front page of this data sheet illustrates the architecture of the ADC section, Figure 21 shows the input buffers, and Figure 24 illustrates the architecture of the 5thorder delta-sigma modulator and transfer functions.

An internal reference circuit with three external capacitors provides all reference voltages which are required by the ADC, which defines the full-scale range for the converter. The internal input buffers save the design, space and extra parts needed for external circuitry required by many deltasigma converters. The internal full-differential signal processing architecture provides a wide dynamic range and excellent power supply rejection performance. The input signal is sampled at a 64x oversampling rate, eliminating the need for a sample-and-hold circuit, and simplifying antialias filtering requirements. The 5th-order delta-sigma noise

FIGURE 22. Anti-Alias Filter Frequency Response.

FIGURE 24. Simplified 5th-Order Delta-Sigma Modulator.

shaper consists of five integrators which use a switchedcapacitor topology, a comparator, and a feedback loop consisting of a one-bit DAC. The delta-sigma modulator shapes the quantization noise, shifting it out of the audio band in the frequency domain. The high order of the modulator enables it to randomize the modulator outputs, reducing idle tone levels.

The  $64f_S$  one-bit data stream from the modulator is converted to  $1f_S$ , 16-bit data words by the decimation filter, which also acts as a low-pass filter to remove the shaped quantization noise. The DC components can be removed by a high-pass filter function contained within the decimation filter.

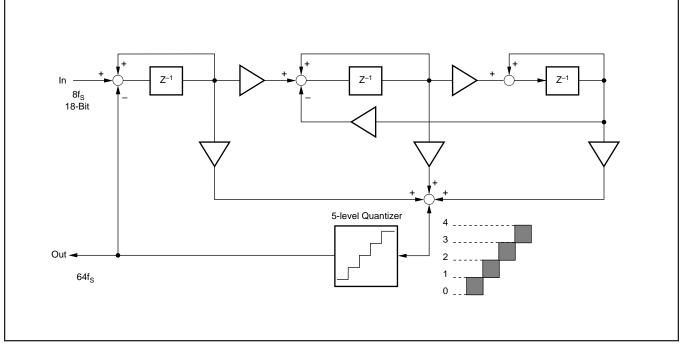

#### DAC SECTION

The delta-sigma DAC section of PCM3501 is based on a 5level amplitude quantizer and a 3rd-order noise shaper. This section converts the oversampled input data to 5-level deltasigma format. A block diagram of the 5-level delta-sigma modulator is shown in Figure 25. This 5-level delta-sigma modulator has the advantage of stability and clock jitter sensitivity over the typical one-bit (2 level) delta-sigma modulator. The combined oversampling rate of the deltasigma modulator and the internal 8x interpolation filter is  $64f_S$  for a  $512f_S$  system clock.

FIGURE 25. 5-Level Delta-Sigma Modulator Block Digram.

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com