SBAS057A – JANUARY 1996 – REVISED MAY 2007

# **Sound** DIGITAL-TO-ANALOG CONVERTER With Programmable PLL

## **FEATURES**

- ACCEPTS 16-, 20-, OR 24-BIT INPUT DATA

- COMPLETE STEREO DAC: Includes Digital Filter and Output Amp

- DYNAMIC RANGE: 94dB

- MULTIPLE SAMPLING FREQUENCIES: 16kHz, 22.05kHz, 24kHz

32kHz, 44.1kHz, 48kHz

64kHz, 88.2kHz, 96kHz

- PROGRAMMABLE PLL CIRCUIT: 256f<sub>s</sub>/384f<sub>s</sub> from 27MHz Master Clock

- NORMAL OR I<sup>2</sup>S<sup>™</sup> DATA INPUT FORMATS

- SELECTABLE FUNCTIONS: Soft Mute Digital Attenuator (256 Steps) Digital De-emphasis

- OUTPUT MODE: Left, Right, Mono, Mute

## DESCRIPTION

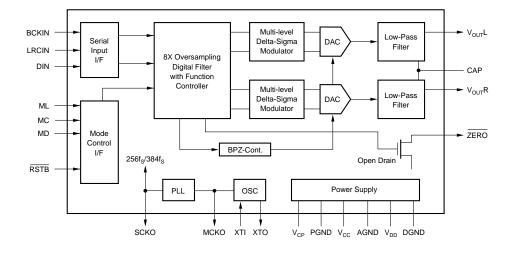

The PCM1723 is a complete, low-cost, stereo audio digital-to-analog converter (DAC) with a phase-locked loop (PLL) circuit included. The PLL derives either a 256f<sub>S</sub> or 384f<sub>S</sub> system clock from an external 27MHz reference frequency. The DAC contains a 3rd-order delta-sigma ( $\Delta\Sigma$ ) modulator, a digital interpolation filter, and an analog output amplifier. The PCM1723 can accept 16-, 20-, or 24-bit input data in either normal or I<sup>2</sup>S formats.

The digital filter performs an 8X interpolation function and includes selectable features such as soft mute, digital attenuation and digital de-emphasis. The PLL can be programmed for sampling at standard digital audio frequencies as well as one-half and double sampling frequencies.

The PCM1723 is ideal for applications which combine compressed audio and video data such as DVD, DVD-ROM, set-top boxes and MPEG sound cards.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SoundPLUS is a trademark of Texas Instruments.

I<sup>2</sup>S is a trademark of NXP Semiconductors.

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Power Supply Voltage                            |                                   |

|-------------------------------------------------|-----------------------------------|

| +V <sub>CC</sub> to +V <sub>DD</sub> Difference | ±0.1V                             |

| Input Logic Voltage                             | –0.3V to (V <sub>DD</sub> + 0.3V) |

| Input Current (except power supply)             | ±10mA                             |

| Power Dissipation                               | 530mW                             |

| Operating Temperature Range                     | –25°C to +85°C                    |

| Storage Temperature                             | –55°C to +125°C                   |

| Lead Temperature (soldering, 5s)                | +260°C                            |

| Thermal Resistance, $\theta_{JA}$               | +70°C/W                           |

NOTE: (1) Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

### PACKAGE INFORMATION<sup>(1)</sup>

| PRODUCT  | PACKAGE     | PACKAGE<br>DESIGNATOR |

|----------|-------------|-----------------------|

| PCM1723E | 24-Pin SSOP | DB                    |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI web site at www.ti.com

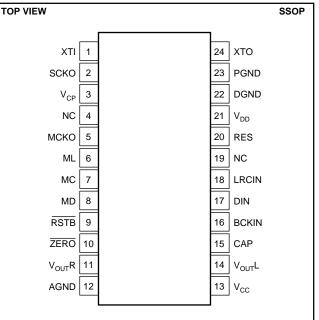

### PIN CONFIGURATION

#### **PIN ASSIGNMENTS**

| PIN               | NAME               | TYPE | FUNCTION                                                                                                        |

|-------------------|--------------------|------|-----------------------------------------------------------------------------------------------------------------|

| 1                 | XTI                | IN   | Master Clock Input.                                                                                             |

| 2                 | SCKO               | OUT  | System Clock Out. This output is $256f_S$ or $384f_S$ .                                                         |

|                   |                    |      | system clock generated by the internal PLL.                                                                     |

| 3                 | V <sub>CP</sub>    | PWR  | PLL Power Supply (+5V).                                                                                         |

| 4                 | NC                 | N/A  | No connection.                                                                                                  |

| 5                 | MCKO               | Out  | Buffered clock output of crystal oscillator.                                                                    |

| 6(1)              | ML                 | IN   | Latch for serial control data.                                                                                  |

| 7 <sup>(1)</sup>  | MC                 | IN   | Clock for serial control data.                                                                                  |

| 8(1)              | MD                 | IN   | Data for serial control.                                                                                        |

| 9(1)              | RSTB               | IN   | Reset Input. When this pin is low, the digital filters and modulators are held in reset.                        |

| 10                | ZERO               | OUT  | Zero Data Flag. This pin is low when the input data is continuously zero for more than 65, 535 cycles of BCKIN. |

| 11                | V <sub>OUT</sub> R | OUT  | Right Channel Analog Output.                                                                                    |

| 12                | AGND               | GND  | Analog Ground.                                                                                                  |

| 13                | V <sub>CC</sub>    | PWR  | Analog Power Supply (+5V).                                                                                      |

| 14                | V <sub>OUT</sub> L | OUT  | Left Channel Analog Output.                                                                                     |

| 15                | CAP                |      | Common pin for analog output amplifiers.                                                                        |

| 16 <sup>(2)</sup> | BCKIN              | IN   | Bit clock for clocking in the audio data.                                                                       |

| 17(2)             | DIN                | IN   | Serial audio data input.                                                                                        |

| 18(2)             | LRCIN              | IN   | Left/Right Word Clock. Frequency is equal to f <sub>s</sub> .                                                   |

| 19                | NC                 | N/A  | No connection.                                                                                                  |

| 20                | RES                | N/A  | Reserved for factory use, do not connect.                                                                       |

| 21                | V <sub>DD</sub>    | PWR  | Analog Power Supply (+5V).                                                                                      |

| 22                | DGND               | GND  | Digital Ground.                                                                                                 |

| 23                | PGND               | GND  | PLL Ground.                                                                                                     |

| 24                | хто                | Out  | Crystal oscillator output.                                                                                      |

NOTES: (1) Schmitt trigger input with internal pull-up resistors. (2) Schmitt triger input.

# **ELECTRICAL CHARACTERISTICS**

All specifications at +25°C, +V<sub>CC</sub> = +V<sub>DD</sub> = +V<sub>CP</sub> = +5V,  $f_S$  = 44.1kHz, and 16-bit input data, SYSCLK = 384 $f_S$ , unless otherwise noted.

|                                                    |                                       |                       | PCM1723                              |            |                      |  |  |  |

|----------------------------------------------------|---------------------------------------|-----------------------|--------------------------------------|------------|----------------------|--|--|--|

| PARAMETER                                          | CONDITIONS                            | MIN                   | TYP                                  | MAX        | UNITS                |  |  |  |

| RESOLUTION                                         |                                       | 16                    |                                      |            | Bits                 |  |  |  |

| DATA FORMAT                                        |                                       |                       |                                      |            |                      |  |  |  |

| Audio Data Interface Format                        |                                       | Star                  | ndard/I <sup>2</sup> S Select        | able       |                      |  |  |  |

| Data Bit Length                                    |                                       | 16                    | 6/20/24 Selectat                     | ble        |                      |  |  |  |

| Audio Data Format                                  |                                       | MSB First,            | Binary Two's C                       | Complement |                      |  |  |  |

| Sampling Frequency (f <sub>S</sub> )               | Standard f <sub>S</sub>               | 32                    | 44.1                                 | 48         | kHz                  |  |  |  |

| -                                                  | One-half fs                           | 16                    | 22.05                                | 24         | kHz                  |  |  |  |

|                                                    | Double f <sub>S</sub>                 | 64                    | 88.2                                 | 96         | kHz                  |  |  |  |

| PLL PERFORMANCE                                    |                                       |                       |                                      |            |                      |  |  |  |

| Master Clock Input Frequency <sup>(4)</sup>        |                                       | 26.73                 | 27                                   | 27.27      | MHz                  |  |  |  |

| Master Clock Output Frequency                      |                                       | 4.096                 |                                      | 36.864     | MHz                  |  |  |  |

| Generated SYSCLK Frequency                         |                                       | 4.000                 | 256f <sub>S</sub> /384f <sub>S</sub> | 00.004     | IVIT IZ              |  |  |  |

|                                                    | L = 2mA                               | V 04                  | 2001 <sub>S</sub> /0041 <sub>S</sub> |            | VDC                  |  |  |  |

| Output Logic Level V <sub>OH</sub>                 | $I_{OH} = 2mA$                        | V <sub>DD</sub> - 0.4 |                                      | 0.5        |                      |  |  |  |

| (MCKO, SCKO) V <sub>OL</sub>                       | I <sub>OL</sub> = 4mA<br>Stondard Dov |                       |                                      | 0.5        | VDC                  |  |  |  |

| Generated SYSCLK Jitter                            | Standard Dev                          |                       | ±150                                 |            | ps                   |  |  |  |

| Generated SYSCLK Transient <sup>(1)</sup>          | $f_M = 27MHz$                         |                       |                                      | 20         | ms                   |  |  |  |

| Power-Up Time                                      | To Programmed Frequency               |                       | 15                                   | 30         | ms                   |  |  |  |

| Generated SYSCLK Duty Cycle                        | $f_M = 27MHz, C_L = 15pF$             | 40                    | 50                                   | 60         | %                    |  |  |  |

| DIGITAL INPUT LOGIC LEVEL                          |                                       |                       | TTL                                  |            |                      |  |  |  |

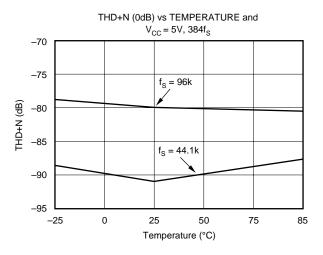

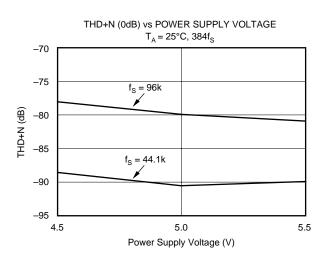

| DYNAMIC PERFORMANCE <sup>(2)</sup>                 |                                       |                       |                                      |            |                      |  |  |  |

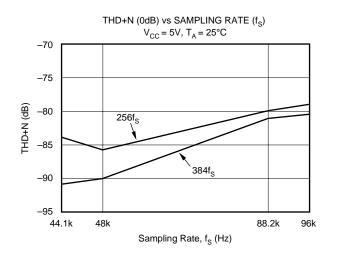

| THD+N at f <sub>S</sub> (0dB)                      | fs = 44.1kHz                          |                       | -89                                  | -80        | dB                   |  |  |  |

| 5.( )                                              | fs = 96kHz                            |                       | -87                                  |            | dB                   |  |  |  |

| THD+N at -60dB                                     | fs = 44.1kHz                          |                       | -31                                  |            | dB                   |  |  |  |

|                                                    | fs = 96 kHz                           |                       | -29                                  |            | dB                   |  |  |  |

| Dynamic Range (EIAJ Method)                        | fs = 44.1 kHz                         | 90                    | 94                                   |            | dB                   |  |  |  |

| Dynamic Range (EIAo Method)                        | fs = 96  kHz                          | 30                    | 91                                   |            | dB                   |  |  |  |

|                                                    |                                       | 00                    |                                      |            | -                    |  |  |  |

| Signal-to-Noise Ratio <sup>(3)</sup> (EIAJ Method) | fs = 44.1kHz                          | 90                    | 96                                   |            | dB                   |  |  |  |

| Ohannal Cananatian                                 | fs = 96kHz                            | 00                    | 95                                   |            | dB                   |  |  |  |

| Channel Separation                                 | fs = 44.1kHz                          | 88                    | 93                                   |            | dB                   |  |  |  |

| DC ACCURACY                                        |                                       |                       |                                      |            |                      |  |  |  |

| Gain Error                                         |                                       |                       | ±1.0                                 | ±3.0       | % of FSF             |  |  |  |

| Gain Mismatch, Channel-to-Channel                  |                                       |                       | ±1.0                                 | ±2.0       | % of FSF             |  |  |  |

| Bipolar Zero Error                                 | $V_{OUT} = V_{CC}/2$ at BPZ           |                       | ±30                                  |            | mV                   |  |  |  |

| ANALOG OUTPUT                                      |                                       |                       |                                      |            |                      |  |  |  |

| Output Voltage                                     | Full Scale (-0dB)                     |                       | 0.62 x V <sub>CC</sub>               |            | V <sub>PP</sub>      |  |  |  |

| Center Voltage                                     |                                       |                       | V <sub>CC</sub> /2                   |            | V <sub>DC</sub>      |  |  |  |

| Load Impedance                                     | AC Load                               | 5                     | 00-                                  |            | kΩ                   |  |  |  |

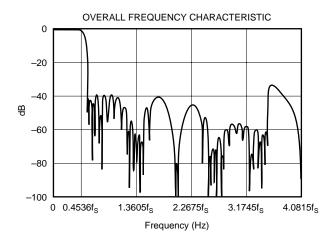

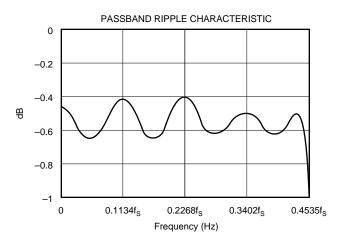

| DIGITAL FILTER PERFORMANCE                         |                                       |                       |                                      |            |                      |  |  |  |

| Passband                                           |                                       |                       |                                      | 0.445      | f <sub>S</sub>       |  |  |  |

| Stop Band                                          |                                       | 0.555                 |                                      | 0.110      |                      |  |  |  |

| Passband Ripple                                    |                                       | 0.000                 |                                      | ±0.17      | f <sub>s</sub><br>dB |  |  |  |

| Stop Band Attenuation                              |                                       | 25                    |                                      |            |                      |  |  |  |

| •                                                  |                                       | -35                   | 44 405 #                             |            | dB                   |  |  |  |

| Delay Time                                         |                                       |                       | 11.125/f <sub>S</sub>                | 0          | sec                  |  |  |  |

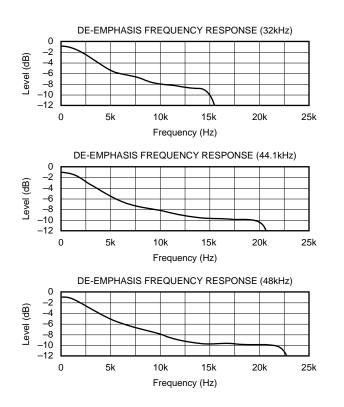

| De-emphasis Error                                  |                                       | -0.2                  |                                      | +0.55      | dB                   |  |  |  |

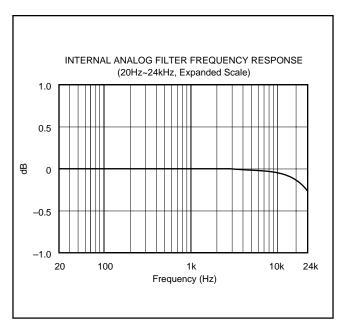

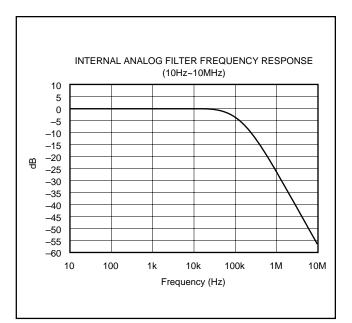

| INTERNAL ANALOG FILTER                             |                                       |                       |                                      |            |                      |  |  |  |

| -3dB Bandwidth                                     |                                       |                       | 100                                  |            | kHz                  |  |  |  |

| Passband Response                                  | f = 20kHz                             |                       | -0.16                                |            | dB                   |  |  |  |

| POWER SUPPLY REQUIREMENTS                          |                                       |                       |                                      |            |                      |  |  |  |

| Voltage Range                                      | $V_{CC} = V_{DD} = V_{CP}$            | 4.5                   | 5                                    | 5.5        | VDC                  |  |  |  |

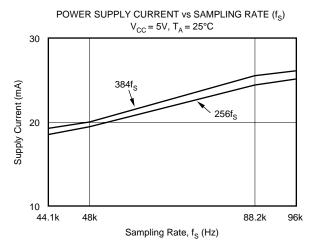

| Supply Current: $I_{CC} + I_{DD} + I_{CP}$         | $f_{S} = 44.1 \text{kHz}$             | ч. <b>о</b>           | 20                                   | 24         | mA                   |  |  |  |

|                                                    | 15 - 77. 1112                         |                       | 20                                   |            |                      |  |  |  |

|                                                    |                                       |                       |                                      |            | ~~                   |  |  |  |

| Operating                                          |                                       | -25                   |                                      | +85        | °C                   |  |  |  |

| Storage                                            | 1                                     | -55                   | 1                                    | +100       | °C                   |  |  |  |

NOTES: (1) Sysclk transient is the maximum frequency lock time when the PLL frequency is changed.

(2) Dynamic performance specs are tested with 20kHz low pass filter and THD+N specs are tested with 30kHz LPF, 400Hz HPF, Average-Mode. (3) SNR is tested at Infinite Zero Detection off.

(4) PLL evaluations tested with 1ns maximum jitter on the 27MHz input clock.

# **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ ,  $V_{CC} = V_{DD} = V_{CP} = +5V$ ,  $f_S = 44.1$ kHz, 16-bit input data, 384 $f_S$ , unless otherwise noted. Measurement bandwidth is 20kHz.

#### DYNAMIC PERFORMANCE

# **TYPICAL CHARACTERISTICS (Cont.)**

At T\_A = +25°C, V\_S = +5V, R\_L = 44.1kHz, and  $f_{SYS}$  = 384f\_S, unless otherwise noted.

#### DIGITAL FILTER

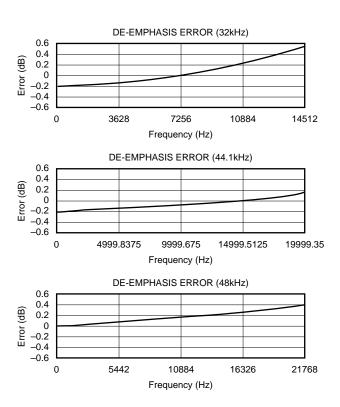

#### **TYPICAL CONNECTION DIAGRAM**

Figure 1 illustrates the typical connection diagram for the PCM1723 in an MPEG-2 application. The 27MHz master video clock ( $f_M$ ) drives XTI (pin 1) of the PCM1723. A programmable system clock is generated by the PCM1723 PLL, with SCKO used to drive the MPEG-2 decoder system clock input. The standard audio signals (data, bit clock, and word clock) are generated in the decoder from the PCM1723 system clock, providing synchronization of audio and video signals.

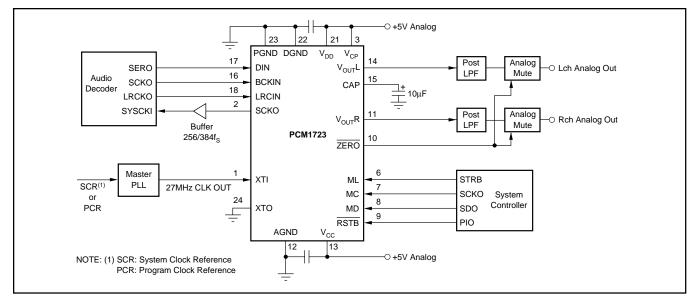

#### PLL CIRCUIT

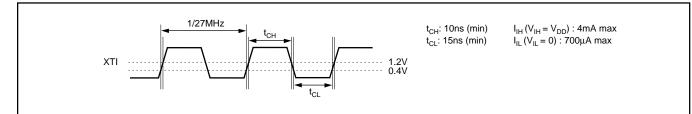

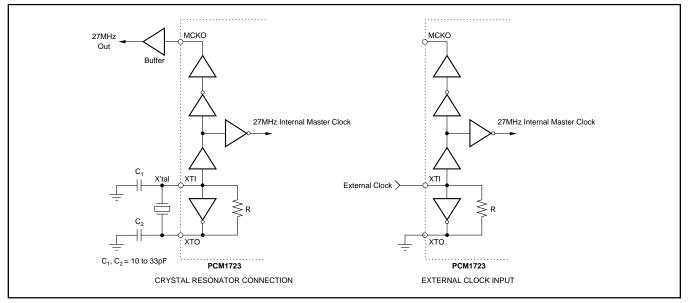

The PCM1723 has a programmable internal PLL circuit, as shown in Figure 2. The PLL is designed to accept a 27MHz master clock or crystal oscillator and generate all internal system clocks required to operate the digital filter and  $\Delta\Sigma$  modulator, either at 256f<sub>s</sub> or 384f<sub>s</sub>. If an external master clock is used, XTO must be connected to GND. In both cases, the signal amplitude on XTI must satisfy the specification described in Figure 3. Therefore, careful C1 and C2 determination is required to keep this specification satisfied when

FIGURE 1. Connection Diagram for External Master Clock in a Typical MPEG-2 Application.

FIGURE 2. PLL Block Diagram.

FIGURE 3. XTI Input Timing.

FIGURE 4. System Clock Connection.

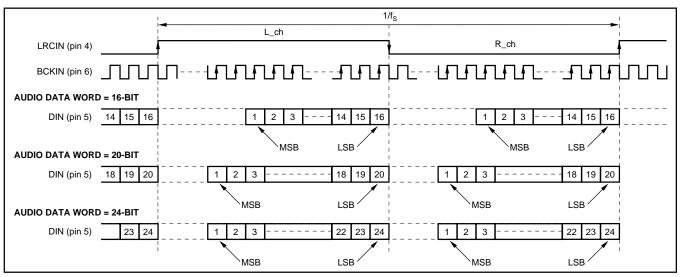

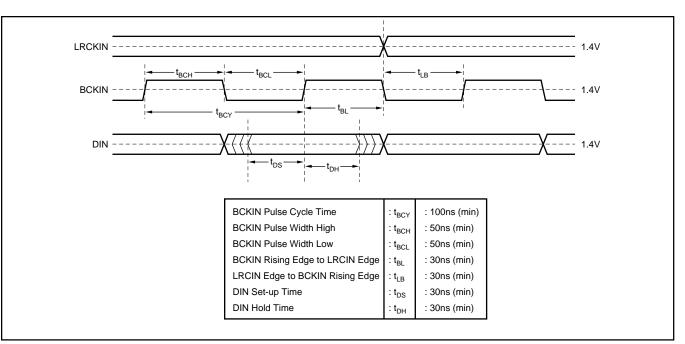

FIGURE 5. Normal Data Input Timing.

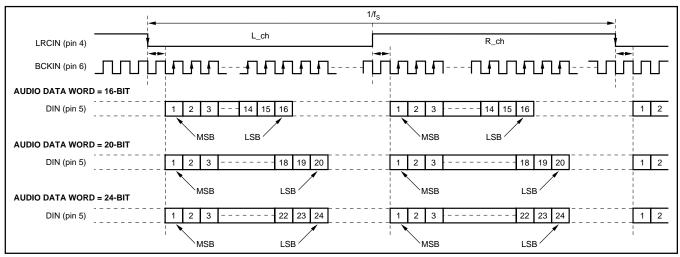

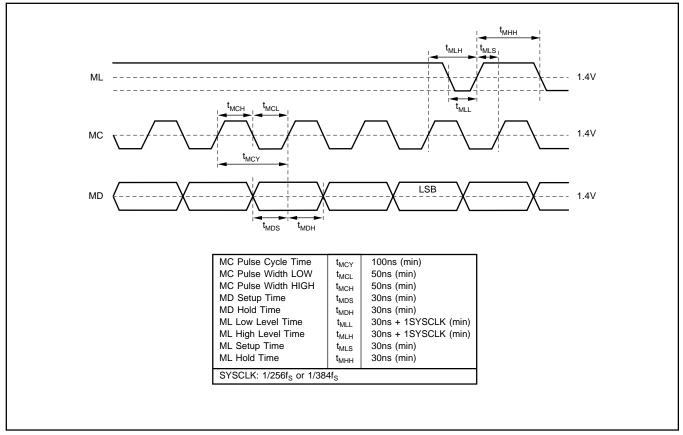

FIGURE 6. I<sup>2</sup>S Data Input Timing.

FIGURE 7. Audio Data Input Timing.

using a crystal oscillator. The PLL will directly track any variations in the master clock frequency, and jitter on the system clock is specified at 250ps maximum. Figure 3 illustrates the timing requirements for the 27MHz master clock. Figure 4 illustrates the system clock connections for an external clock or crystal oscillator.

The PCM1723 internal PLL can be programmed for nine different sampling frequencies (LRCIN), as shown in Table I. The internal sampling clocks generated by the various programmed frequencies are shown in Table II. The system clock output frequency for the PCM1723 is 100% accurate. To provide MCKO clock and SCKO clock for external circuit, external buffer circuit is effective to avoid degrading audio performance.

| Sampling Frequencies-LRCIN (k    |    |       |    |  |  |  |  |  |  |  |  |

|----------------------------------|----|-------|----|--|--|--|--|--|--|--|--|

| Half of Standard Sampling Freq   | 16 | 22.05 | 24 |  |  |  |  |  |  |  |  |

| Standard Sampling Freq           | 32 | 44.1  | 48 |  |  |  |  |  |  |  |  |

| Double of Standard Sampling Freq | 64 | 88.2  | 96 |  |  |  |  |  |  |  |  |

TABLE I. Sampling Frequencies.

| Sampling<br>Frequency<br>(LRCIN) |          | System Clock<br>256f <sub>S</sub> | System Clock<br>384f <sub>S</sub> |  |

|----------------------------------|----------|-----------------------------------|-----------------------------------|--|

| 16kHz                            | Half     | 4.096MHz                          | 6.144MHz                          |  |

| 32kHz                            | Standard | 8.192MHz                          | 12.288MHz                         |  |

| 64kHz                            | Double   | 16.384MHz                         | 24.576MHz                         |  |

| 22.05kHz                         | Half     | 5.6448MHz                         | 8.4672MHz                         |  |

| 44.1kHz                          | Standard | 11.2896MHz                        | 16.9344MHz                        |  |

| 88.2kHz                          | Double   | 22.5792MHz                        | 33.8688MHz                        |  |

| 24kHz                            | Half     | 6.144MHz                          | 9.216MHz                          |  |

| 48kHz                            | Standard | 12.288MHz                         | 18.432MHz                         |  |

| 96kHz                            | Double   | 24.576MHz                         | 36.864MHz                         |  |

TABLE II. Sampling Frequencies vs Internal SystemClock (= Output Frequencies of PLL).

#### SPECIAL FUNCTIONS

The PCM1723 includes several special functions, including digital attenuation, digital de-emphasis, soft mute, data format selection and input word resolution. These functions are controlled using a three-wire interface. MD (pin 8) is used for the program data, MC (pin 7) is used to clock in the program data, and ML (pin 6) is used to latch in the program data. Table III lists the selectable special functions.

| FUNCTION                                                                                                                                                                                                                                                | DEFAULT MODE                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Input Audio Data Format Selection<br>Normal Format<br>I <sup>2</sup> S Format                                                                                                                                                                           | Normal Format                               |

| Input Audio Data Bit Selection<br>16/20/24 Bits                                                                                                                                                                                                         | 16 Bits                                     |

| Input LRCIN Polarity Selection<br>Lch/Rch = High/Low<br>Lch/Rch = Low/High                                                                                                                                                                              | Lch/Rch = High/Low                          |

| De-emphasis Control                                                                                                                                                                                                                                     | OFF                                         |

| Soft Mute Control                                                                                                                                                                                                                                       | OFF                                         |

| Attenuation Control<br>Lch, Rch Individually<br>Lch, Rch Common                                                                                                                                                                                         | 0dB<br>Lch, Rch Individually Fixed          |

| Infinite Zero Detection Circuit Control                                                                                                                                                                                                                 | OFF                                         |

| Operation Enable (OPE)                                                                                                                                                                                                                                  | Enabled                                     |

| Sample Rate Selection<br>Internal System Clock Selection<br>256f <sub>s</sub><br>384f <sub>s</sub><br>Double Sampling Rate Selection<br>Standard Sampling Rate—44.1/48/32kHz<br>Double Sampling Rate—28.2/96/32kHz<br>Half Sampling Rate—22.05/24/16kHz | 384f <sub>S</sub><br>Standard Sampling Rate |

| Sampling Frequency<br>44.1kHz Group<br>48kHz Group<br>32kHz Group                                                                                                                                                                                       | 44.1kHz                                     |

| Analog Output Mode<br>L, R, Mono, Mute                                                                                                                                                                                                                  | Stereo                                      |

TABLE III. Selectable Functions.

|       | B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8  | B7  | B6  | B5   | B4   | B3  | B2  | B1  | B0               |

|-------|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|------|------|-----|-----|-----|------------------|

| MODE0 | res | res | res | res | res | A1  | A0 | LDL | AL7 | AL6 | AL5  | AL4  | AL3 | AL2 | AL1 | AL0              |

|       |     |     |     |     |     |     |    |     |     |     |      |      |     |     |     |                  |

| MODE1 | res | res | res | res | res | A1  | A0 | LDR | AR7 | AR6 | AR5  | AR4  | AR3 | AR2 | AR1 | AR0              |

|       |     |     |     |     |     |     |    |     |     |     |      |      |     |     |     |                  |

| MODE2 | res | res | res | res | res | A1  | A0 | PL3 | PL2 | PL1 | PL0  | IW1  | IW0 | OPE | DEM | MUT              |

|       |     |     |     |     |     |     |    |     |     |     |      |      |     |     |     |                  |

| MODE3 | res | res | res | res | res | A1  | A0 | IZD | SF1 | SF0 | DSR1 | DSR0 | SYS | ATC | LRP | l <sup>2</sup> S |

#### MAPPING OF PROGRAM REGISTERS

#### PROGRAM REGISTER BIT MAPPING

The PCM1723 special functions are controlled using four program registers that are 16 bits long. These registers are all loaded using MD. After the 16 data bits are clocked in, ML is used to latch in the data to the appropriate register. Table IV shows the complete mapping of the four registers and Figure 8 illustrates the serial interface timing.

| REGISTER<br>NAME | BIT<br>NAME                                                                             | DESCRIPTION                                                                                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register 0       | AL (7:0)<br>LDL<br>A (1:0)<br>Res                                                       | DAC Attenuation Data for Lch<br>Attenuation Data Load Control for Lch<br>Register Address<br>Reserved                                                                                                                                       |

| Register 1       | AR (7:0)<br>LDL<br>A (1:0)<br>Res                                                       | DAC Attenuation Data for Rch<br>Attenuation Data Load Control for Rch<br>Register Address<br>Reserved                                                                                                                                       |

| Register 2       | MUT<br>DEM<br>OPE<br>IW (1:0)<br>PL (3:0)<br>A (1:0)<br>res                             | Left and Right DACs Soft Mute Control<br>De-emphasis Control<br>Left and Right DACs Operation Control<br>Input Audio Data Bit Select<br>Output Mode Select<br>Register Address<br>Reserved                                                  |

| Register 3       | I <sup>2</sup> S<br>LRP<br>ATC<br>SYS<br>DSR (1:0)<br>SF (1:0)<br>IZD<br>A (1:0)<br>Res | Audio Data Format Select<br>Polarity of LRCIN (pin 7) Select<br>Attenuator Control<br>System Clock Select<br>Double Sampling Rate Select<br>Sampling Rate Select<br>Infinite Zero Detection Circuit Control<br>Register Address<br>Reserved |

TABLE IV. Internal Register Mapping.

#### REGISTER 0 (A1 = 0, A0 = 0)

B15

B14

B13

B12

B11

B10

B9

B8

B7

B6

B5

B4

B3

B2

B1

B0

res

res

res

res

res

res

A1

A0

LDL

AL7

AL6

AL5

AL4

AL3

AL2

AL1

AL0

Register 0 is used to control left channel attenuation. Bits 0 - 7 (AL0 - AL7) are used to determine the attenuation level. The level of attenuation is given by:

$ATT = [20 log10 (ATT_DATA/255)] dB$

#### ATTENUATION DATA LOAD CONTROL

Bit 8 (LDL) is used to control the loading of attenuation data in B0:B7. When LDL is set to 0, attenuation data will be loaded into AL0:AL7, but it will not affect the attenuation level until LDL is set to 1. LDR in Register 1 has the same function for right channel attenuation.

Attenuation Level (ATT) can be controlled as following Resistor set AL (R) (7:0).

| AL (R) (7:0) | ATT LEVEL   |

|--------------|-------------|

| 00h          | -∞dB (Mute) |

| 01h          | -48.16dB    |

| •            |             |

|              | •           |

| •            | •           |

| FEh          | -0.07dB     |

| FFh          | 0dB         |

#### REGISTER 1 (A1 = 0, A0 = 1)

|     | B14 |     |     |     |    |    |     |     |     |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| res | res | res | res | res | A1 | A0 | LDR | AR7 | AR6 | AR5 | AR4 | AR3 | AR2 | AR1 | AR0 |

Register 1 is used to control right channel attenuation. As in Register 1, bits 0 - 7 (AR0 - AR7) control the level of attenuation.

#### **REGISTER 2 (A1 = 1, A0 = 0)**

| B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8  | B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0   |

|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|------|

| res | res | res | res | res | A1  | A0 | PL3 | PL2 | PL1 | PL0 | IW1 | IW0 | OPE | DEM | MUTE |

Register 2 is used to control soft mute, de-emphasis, operation enable, input resolution, and output format. Bit 0 is used for soft mute: a HIGH level on bit 0 will cause the output to be muted (this is ramped down in the digital domain, so no *click* is audible). Bit 1 is used to control de-emphasis. A LOW level on bit 1 disables de-emphasis, while a HIGH level enables de-emphasis.

Bit 2 (OPE) is used for operational control. Table V illustrates the features controlled by OPE.

|                                                                  | DATA INPUT | DAC OUTPUT                   | SOFTWARE MODE<br>INPUT |  |  |  |  |

|------------------------------------------------------------------|------------|------------------------------|------------------------|--|--|--|--|

| OPE = 1                                                          | Zero       | Forced to BPZ <sup>(1)</sup> | Enabled                |  |  |  |  |

|                                                                  | Other      | Forced to BPZ <sup>(1)</sup> | Enabled                |  |  |  |  |

|                                                                  | Zero       | Controlled by IZD            | Enabled                |  |  |  |  |

| OPE = 0 Other Normal Enabled                                     |            |                              |                        |  |  |  |  |

| NOTE: (1) $\Delta \Sigma$ is disconnected from output amplifier. |            |                              |                        |  |  |  |  |

TABLE V. Operation Enable (OPE) Function.

OPE controls the operation of the DAC: when OPE is LOW, the DAC will convert all non-zero input data. If the input data is continuously zero for 65,536 cycles of BCKIN, the output will be forced to zero only if IZD is HIGH. When OPE is HIGH, the output of the DAC will be forced to bipolar zero, irrespective of any input data.

|                                                                                                                          | DATA INPUT | DAC OUTPUT                   |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|------------|------------------------------|--|--|--|--|--|

| IZD = 1                                                                                                                  | Zero       | Forced to BPZ <sup>(1)</sup> |  |  |  |  |  |

| 120 = 1                                                                                                                  | Other      | Normal                       |  |  |  |  |  |

|                                                                                                                          | Zero       | Zero <sup>(2)</sup>          |  |  |  |  |  |

| IZD = 0                                                                                                                  | Other      | Normal                       |  |  |  |  |  |

| NOTES: (1) $\Delta\Sigma$ is disconnected from output amplifier.<br>(2) $\Delta\Sigma$ is connected to output amplifier. |            |                              |  |  |  |  |  |

TABLE VI. Infinite Zero Detection (IZD) Function.

|                                                                 | DATA INPUT | DAC OUTPUT                      | SOFTWARE<br>MODE<br>INPUT |  |  |  |

|-----------------------------------------------------------------|------------|---------------------------------|---------------------------|--|--|--|

| RSTB = HIGH                                                     | Zero       | Controlled by OPE and IZD       | Enabled                   |  |  |  |

|                                                                 | Other      | Other Controlled by OPE and IZD |                           |  |  |  |

| RSTB = LOW                                                      | Zero       | Forced to BPZ <sup>(1)</sup>    | Disabled                  |  |  |  |

| KOTB = LOW                                                      | Other      | Forced to BPZ <sup>(1)</sup>    | Disabled                  |  |  |  |

| NOTE: (1) $\Delta\Sigma$ is disconnected from output amplifier. |            |                                 |                           |  |  |  |

TABLE VII. Reset (RSTB) Function.

Bits 3 (IW0) and 4 (IW1) are used to determine input word resolution. PCM1723 can be set up for input word resolutions of 16, 20, or 24 bits:

| Bit 4 (IW1) | Bit 3 (IW0) | Input Resolution |

|-------------|-------------|------------------|

| 0           | 0           | 16-bit Data Word |

| 0           | 1           | 20-bit Data Word |

| 1           | 0           | 24-bit Data Word |

| 1           | 1           | Reserved         |

Bits 5, 6, 7, and 8 (PL0:3) are used to control output format. The output of PCM1723 can be programmed for 16 different states, as shown in Table VIII.

| PL0 | PL1 | PL2 | PL3 | Lch OUTPUT Rch OUTPUT |           | NOTE    |

|-----|-----|-----|-----|-----------------------|-----------|---------|

| 0   | 0   | 0   | 0   | MUTE MUTE             |           | MUTE    |

| 0   | 0   | 0   | 1   | MUTE                  | R         |         |

| 0   | 0   | 1   | 0   | MUTE                  | L         |         |

| 0   | 0   | 1   | 1   | MUTE                  | (L + R)/2 |         |

| 0   | 1   | 0   | 0   | R                     | MUTE      |         |

| 0   | 1   | 0   | 1   | R                     | R         |         |

| 0   | 1   | 1   | 0   | R L F                 |           | REVERSE |

| 0   | 1   | 1   | 1   | R (L + R)/2           |           |         |

| 1   | 0   | 0   | 0   | L                     | MUTE      |         |

| 1   | 0   | 0   | 1   | L R S                 |           | STEREO  |

| 1   | 0   | 1   | 0   | L L                   |           |         |

| 1   | 0   | 1   | 1   | L (L + R)/2           |           |         |

| 1   | 1   | 0   | 0   | (L + R)/2 MUTE        |           |         |

| 1   | 1   | 0   | 1   | (L + R)/2             | R         |         |

| 1   | 1   | 1   | 0   | (L + R)/2 L           |           |         |

| 1   | 1   | 1   | 1   | (L + R)/2             | (L + R)/2 | MONO    |

TABLE VIII. Programmable Output Format.

#### **REGISTER 3 (A1 = 1, A0 = 1)**

|     | - · · |     |     |     |    |    |     |     |     | B5   |      |     |     |     |                  |

|-----|-------|-----|-----|-----|----|----|-----|-----|-----|------|------|-----|-----|-----|------------------|

| res | res   | res | res | res | A1 | A0 | IZD | SF1 | SF0 | DSR1 | DSR0 | SYS | ATC | LRP | I <sup>2</sup> S |

Register 3 is used to control input data format and polarity, attenuation channel control, system clock frequency, sampling frequency, and infinite zero detection.

Bits 0 (I<sup>2</sup>S) and 1 (LRP) are used to control the input data format. A LOW on bit 0 sets the format to Normal (MSBfirst, right-justified Japanese format), and a HIGH sets the format to I<sup>2</sup>S (Philips serial data protocol). Bit 1 (LRP) is used to select the polarity of LRCIN (sample rate clock). When bit 1 is LOW, left channel data are assumed when LRCIN is in a HIGH phase and right channel data are assumed when LRCIN is in a LOW phase. When bit 1 is HIGH, the polarity assumption is reversed.

Bit 2 (ATC) is used for controlling the attenuator. When bit 2 is HIGH, the attenuation data loaded in program Register 0 are used for both left and right channels. When bit 2 is LOW, the attenuation data for each register are applied separately to left and right channels.

Bit 3 (SYS) is the system clock selection. When bit 3 is LOW, the system clock frequency is set to  $384f_S$ . When bit 3 is HIGH, the system clock frequency is set to  $256f_S$ .

Bits 4 (DSR0) and 5 (DSR1) are used to control multiples of the sampling rate:

| DSR1 | DSR0 | Multiple |                |  |  |  |  |

|------|------|----------|----------------|--|--|--|--|

| 0    | 0    | Normal   | 32/44.1/48kHz  |  |  |  |  |

| 0    | 1    | Double   | 64/88.2/96kHz  |  |  |  |  |

| 1    | 0    | One-half | 16/22.05/24kHz |  |  |  |  |

| 1    | 1    | Reserved | Not Defined    |  |  |  |  |

Bits 6 (SF0) and 7 (SF1) are used to select the sampling frequency. Frequency selection must be made with an interval time greater than  $20\mu s$ .

| SF1 | SF0 | Sampling Frequency |                    |  |  |  |  |  |

|-----|-----|--------------------|--------------------|--|--|--|--|--|

| 0   | 0   | 44.1kHz group      | 22.05/44.1/88.2kHz |  |  |  |  |  |

| 0   | 1   | 48kHz group        | 24/48/96kHz        |  |  |  |  |  |

| 1   | 0   | 32kHz group        | 16/32/64kHz        |  |  |  |  |  |

| 1   | 1   | Reserved           | Not Defined        |  |  |  |  |  |

Bit 8 is used to control the infinite zero detection function (IZD).

When IZD is LOW, the zero detect circuit is off. Under this condition, no automatic muting will occur if the input is continuously zero. When IZD is HIGH, the zero detect feature is enabled. If the input data are continuously zero for 65,536 cycles of BCKIN, the output will be immediately forced to a bipolar zero state ( $V_{CC}/2$ ). The zero detection feature is used to avoid noise which may occur when the input is DC. When the output is forced to bipolar zero, there may be an audible click. PCM1723 allows the zero detect feature to be disabled so the user can implement an external muting circuit.

| ML (pin 6)<br>MC (pin 7)<br>MD (pin 8)<br>B15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0 |

|-------------------------------------------------------------------------------------------------|

|                                                                                                 |

| MD (pin 8) B15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0                                |

|                                                                                                 |

FIGURE 8. Three-Wire Serial Interface.

FIGURE 9. Program Register Input Timing.

### APPLICATION CONSIDERATIONS DELAY TIME

There is a finite delay time in delta-sigma converters. In analog-to-digital converters (ADCs), this is commonly referred to as latency. For a delta-sigma DAC, delay time is determined by the order number of the FIR filter stage, and the chosen sampling rate. The following equation expresses the delay time of PCM1723:

$t_D = 11.125 \text{ x } 1/f_S$

For  $f_s = 44.1 \text{kHz}$ ,  $t_D = 11.125/44.1 \text{kHz} = 251.4 \mu \text{s}$

Applications using data from a disc or tape source, such as CD audio, CD-Interactive, Video CD, DAT, Minidisc, etc., generally are not affected by delay time. For some profes-

sional applications such as broadcast audio for studios, it is important for total delay time to be less than 2ms.

#### **OUTPUT FILTERING**

For testing purposes all dynamic tests are done on the PCM1723 using a 20kHz low-pass filter. This filter limits the measured bandwidth for THD+N, etc. to 20kHz. Failure to use such a filter will result in higher THD+N and lower SNR and Dynamic Range readings than are found in the specifications. The low-pass filter removes out of band noise. Although it is not audible, it may affect dynamic specification numbers.

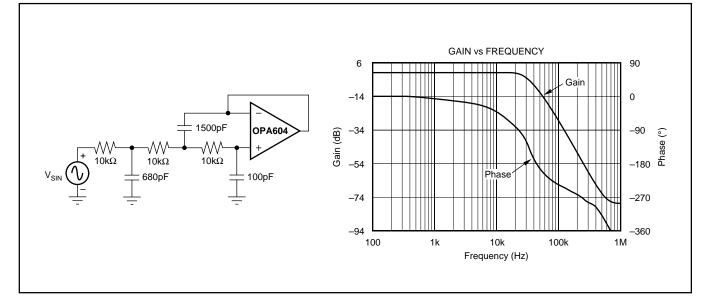

The performance of the internal low-pass filter from DC to 24kHz is shown in Figure 10. The higher frequency rolloff of the filter is shown in Figure 11. If an application has the PCM1723 driving a wideband amplifier, it is recommended to use an external low-pass filter. A simple 3rd-order filter is shown in Figure 12. For some applications, a passive RC filter or 2nd-order filter may be adequate.

#### Reset

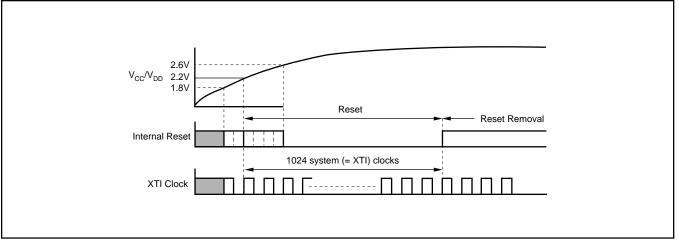

The PCM1723 has both internal power-on reset circuit and the  $\overline{\text{RSTB}}$  pin (pin 9) that accepts an external forced reset by

$\overline{\text{RSTB}}$  = LOW. For internal power on reset, initialize (reset) is done automatically at power on V<sub>DD</sub> >2.2V (typ). During internal reset = LOW, the output of the DAC is invalid and the analog outputs are forced to V<sub>CC</sub>/2. Figure 13 illustrates the timing of internal power on reset.

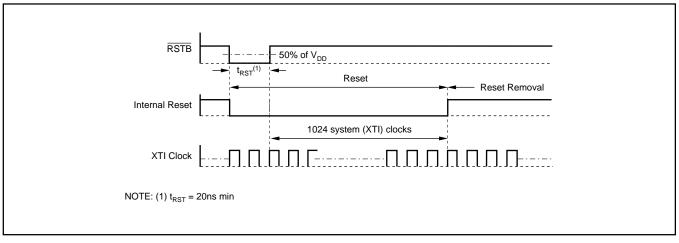

The PCM1723 accepts an external forced reset when  $\overline{\text{RSTB}} = \text{L}$ . During  $\overline{\text{RSTB}} = \text{L}$ , the output of the DAC is invalid and the analog outputs are forced to  $V_{CC}/2$  after internal initialize (1024 system clocks count after  $\overline{\text{RSTB}} = \text{H}$ ). Figure 14 illustrates the timing of  $\overline{\text{RSTB}}$  pin reset.

FIGURE 10. Low-Pass Filter Frequency Response.

FIGURE 11. Low-Pass Filter Wideband Frequency Response.

FIGURE 12. 3rd-Order Low-Pass Filter.

FIGURE 13. Internal Power-On Reset Timing.

FIGURE 14. RSTB-Pin Reset Timing.

## POWER SUPPLY CONNECTIONS

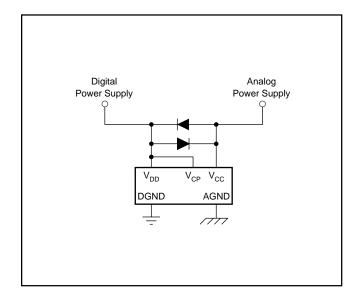

The PCM1723 has three power supply connections: digital  $(V_{DD})$ , analog  $(V_{CC})$ , and PLL  $(V_{CP})$ . Each connection also has a separate ground return pin. It is acceptable to use a common +5V power supply for all three power pins. If separate supplies are used without a common connection, the delta between the supplies during ramp-up time must be less than 0.6V. An application circuit to avoid a power-on latch-up condition is shown in Figure 15.

#### **BYPASSING POWER SUPPLIES**

The power supplies should be bypassed as close as possible to the unit. Refer to Figure 18 for optimal values of bypass capacitors. It is also recommended to include a  $0.1\mu$ F ceramic capacitor in parallel with the  $10\mu$ F tantalum capacitor.

FIGURE 15. Latch-up Prevention Circuit.

# THEORY OF OPERATION

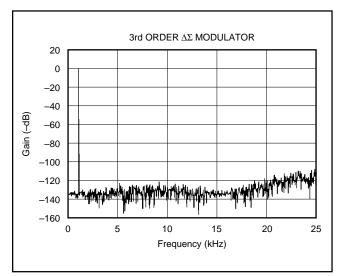

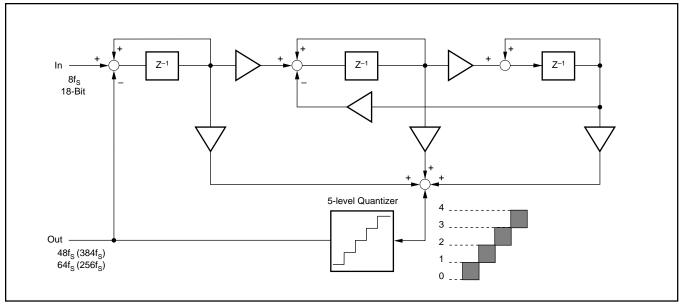

The delta-sigma section of the PCM1723 is based on a 5level amplitude quantizer and a 3rd-order noise shaper. This section converts the oversampled input data to 5-level deltasigma format.

A block diagram of the 5-level delta-sigma modulator is shown in Figure 16. This 5-level delta-sigma modulator has the advantage of stability and clock jitter sensitivity over the typical one-bit (2 level) delta-sigma modulator.

The combined oversampling rate of the delta-sigma modulator and the internal 8X interpolation filter is  $48f_s$  for a  $384f_s$  system clock, and  $64f_s$  for a  $256f_s$  system clock. The theoretical quantization noise performance of the 5-level delta-sigma modulator is shown in Figure 17.

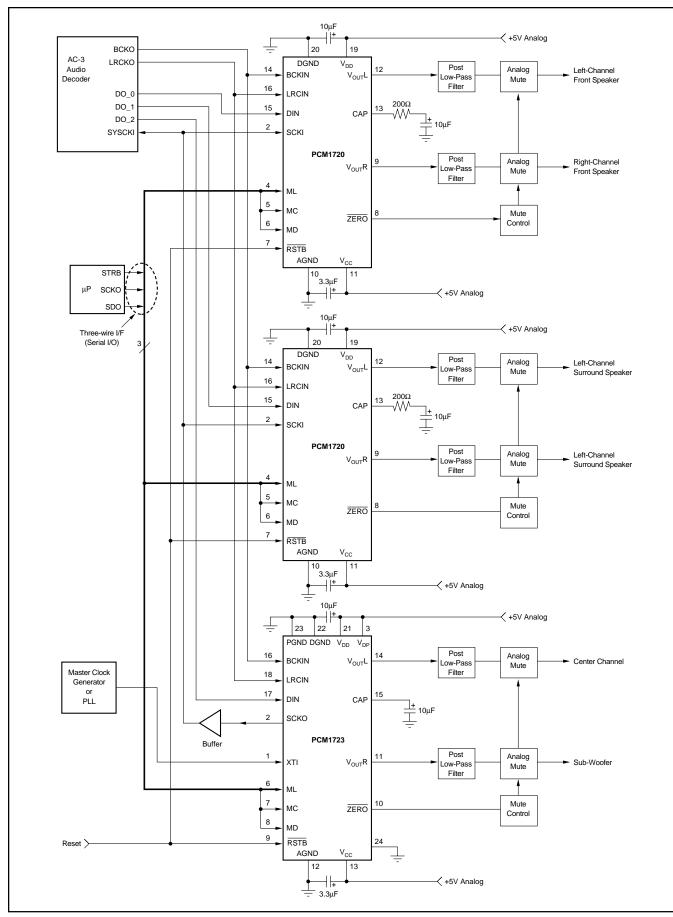

### AC-3 APPLICATION CIRCUIT

A typical application for the PCM1723 is AC-3 5.1 channel audio decoding and playback. This circuit uses the PCM1723 to develop the audio system clock from the 27MHz video clock, with the SCKO pin used to drive the AC-3 decoder and two PCM1720 units, the non-PLL version of the PCM1723.

FIGURE 17. Quantization Noise Spectrum.

FIGURE 16. 5-Level  $\Delta\Sigma$  Modulator Block Diagram.

FIGURE 18. Connection Diagram for a 6-Channel AC-3 Application.

### **Revision History**

| DATE | REVISION | PAGE | SECTION                                                                           | DESCRIPTION                                                             |  |  |  |  |

|------|----------|------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

|      |          | —    | Entire Document                                                                   | Updated format and added missing overbars to RSTB and ZERO pins.        |  |  |  |  |

|      |          | 2    | Electrical Characteristics                                                        | Added "Selectable" to Audio Data Interface Format typical value column. |  |  |  |  |

|      |          |      |                                                                                   | Deleted "Selectable" from Audio Data Format unit column.                |  |  |  |  |

| 5/07 | А        | A 6  | PLL Circuit                                                                       | Changed "XTO should be connected" to "XTO must be connected."           |  |  |  |  |

| 0,01 |          |      |                                                                                   | Added sentence regarding XTI signal amplitude and C1, C2 determination. |  |  |  |  |

|      |          |      | Figure 3                                                                          | Changed 2.0V/0.8V to 1.2V/0.4V.                                         |  |  |  |  |

|      |          | 8    | PLL Circuit                                                                       | Deleted paragraph regarding frequency error.                            |  |  |  |  |

|      |          | 10   | 10 Register 3 Added sentence to Bit 6 regarding interval time must be greater the |                                                                         |  |  |  |  |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| PCM1723E         | ACTIVE                | SSOP            | DB                 | 24   | 58             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| PCM1723E/2K      | ACTIVE                | SSOP            | DB                 | 24   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| PCM1723E/2KG4    | ACTIVE                | SSOP            | DB                 | 24   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| PCM1723EG/2K     | ACTIVE                |                 |                    |      |                | Pb-Free<br>(RoHS)          | CU SNBI          | Level-2-260C-1 YEAR          |

| PCM1723EG4       | ACTIVE                | SSOP            | DB                 | 24   | 58             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. **TBD**: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

19-Sep-2007

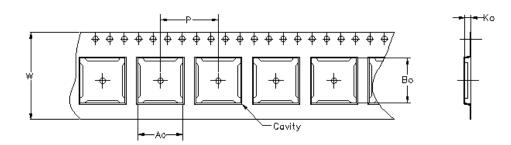

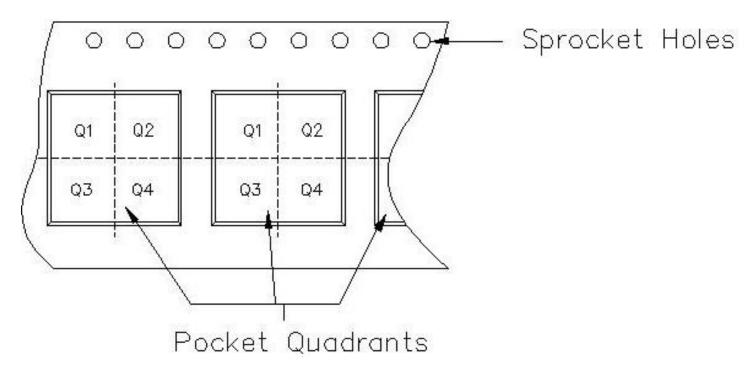

Carrier tape design is defined largely by the component lentgh, width, and thickness.

| Ao = Dimension designed to accommodate the component width.     |  |  |  |  |  |  |  |

|-----------------------------------------------------------------|--|--|--|--|--|--|--|

| Bo = Dimension designed to accommodate the component length.    |  |  |  |  |  |  |  |

| Ko = Dimension designed to accommodate the component thickness. |  |  |  |  |  |  |  |

| W = Overall width of the carrier tape.                          |  |  |  |  |  |  |  |

| P = Pitch between successive cavity centers.                    |  |  |  |  |  |  |  |

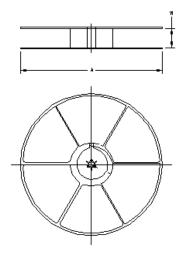

TAPE AND REEL INFORMATION

## PACKAGE MATERIALS INFORMATION

19-Sep-2007

| Device       | Package | Pins | Site    | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>(mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|---------|------|---------|--------------------------|-----------------------|---------|---------|---------|------------|-----------|------------------|

| PCM1723E/2K  | DB      | 24   | SITE 49 | 330                      | 17                    | 8.5     | 8.6     | 2.4     | 12         | 16        | Q1               |

| PCM1723EG/2K |         | 0    | SITE 49 | 330                      | 17                    | 8.5     | 8.6     | 2.4     | 12         | 16        | Q1               |

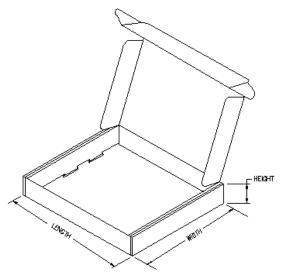

### TAPE AND REEL BOX INFORMATION

| Device       | Package | Pins | Site    | Length (mm) | Width (mm) | Height (mm) |

|--------------|---------|------|---------|-------------|------------|-------------|

| PCM1723E/2K  | DB      | 24   | SITE 49 | 0.0         | 0.0        | 0.0         |

| PCM1723EG/2K |         | 0    | SITE 49 | 0.0         | 0.0        | 0.0         |

## **MECHANICAL DATA**

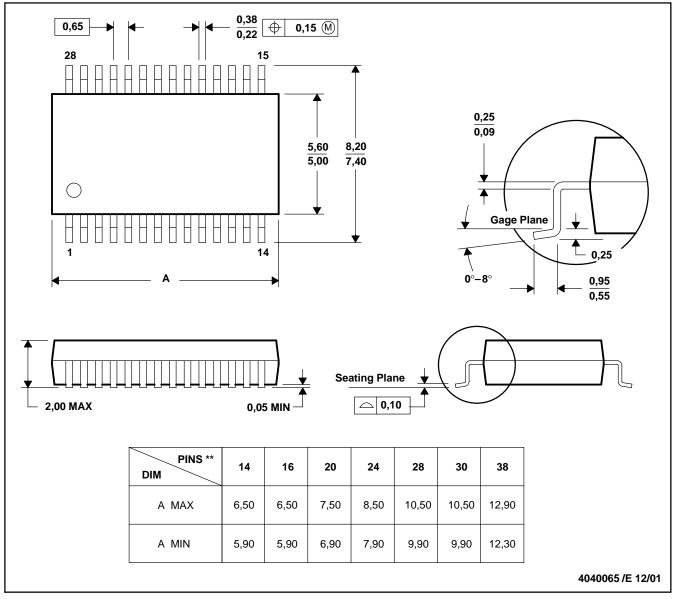

MSSO002E - JANUARY 1995 - REVISED DECEMBER 2001

### DB (R-PDSO-G\*\*)

PLASTIC SMALL-OUTLINE

28 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-150

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products              |                        | Applications       |                           |

|-----------------------|------------------------|--------------------|---------------------------|

| Amplifiers            | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters       | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                   | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface             | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic                 | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt            | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers      | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                  | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| Low Power<br>Wireless | www.ti.com/lpw         | Video & Imaging    | www.ti.com/video          |

|                       |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2007, Texas Instruments Incorporated