# **SIEMENS**

# ICs for Communications

Four Channel Codec Filter with PCM- and  $\mu\text{-Controller}$  Interface  $\text{SICOFI}^{\text{\tiny{B}}}4\text{-}\mu\text{C}$

PEB 2466 Version 1.2

Data Sheet 02.97

#### Edition 02.97

This edition was realized using the software system FrameMaker<sup>®</sup>.

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1997. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

# Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain hu-

| PEB 2466                |                                                                                                               |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------|--|

| Revision Hist           | ory: Current Version: 02.97                                                                                   |  |

| Previous Versi          | Errata Sheet 08.95 (valid) for V1.1) Errata Sheet 05.96 (valid for V1.2) Preliminary Data Sheet 03.96         |  |

| Last Revision           | Data Sheet 06/96                                                                                              |  |

| Page (in last revision) | Subjects (major changes regarding Preliminary Data Sheet 03.96)                                               |  |

| 1                       | Featurelist updated                                                                                           |  |

| 2-4                     | Chapter "Major Applications" added                                                                            |  |

| 5-8                     | Errors in pin configuration fixed Values of filter and coupling capacitors fixed Several minor clarifications |  |

| 12-15                   | PCM interface clarified                                                                                       |  |

| 17                      | Byte by byte transfer with the μC-interface added                                                             |  |

| 18                      | Types of Commands and Databytes clarified                                                                     |  |

| 19-23                   | Several errors in programming examples fixed                                                                  |  |

| 25                      | IM-Filter changed to IM/R1-filter                                                                             |  |

| 32                      | CRAM architecture described                                                                                   |  |

| 38                      | Error in definition of XR4-register fixed                                                                     |  |

| 39                      | Error in definition of XR5-register fixed                                                                     |  |

| 39                      | Definition of "crash" added                                                                                   |  |

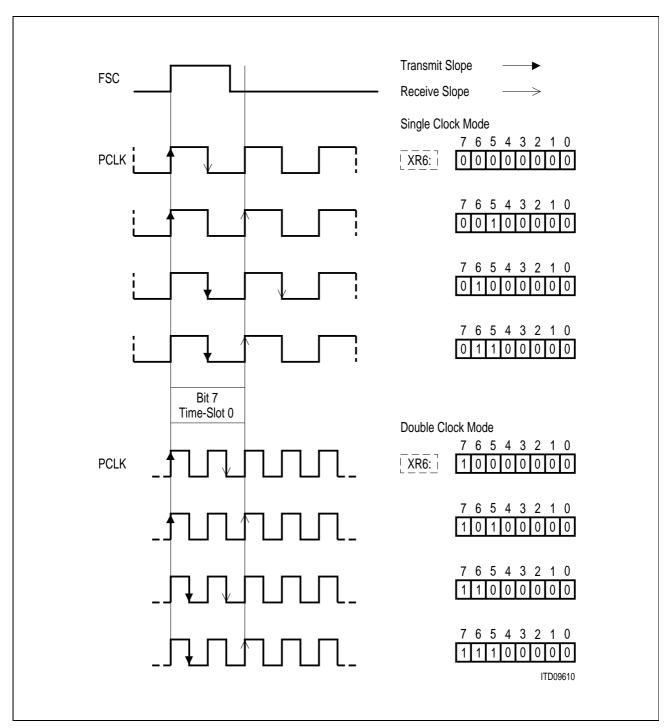

| 41                      | Figure for "setting slopes in XR6" added                                                                      |  |

| 45-46                   | Chapter about programmable filters updated                                                                    |  |

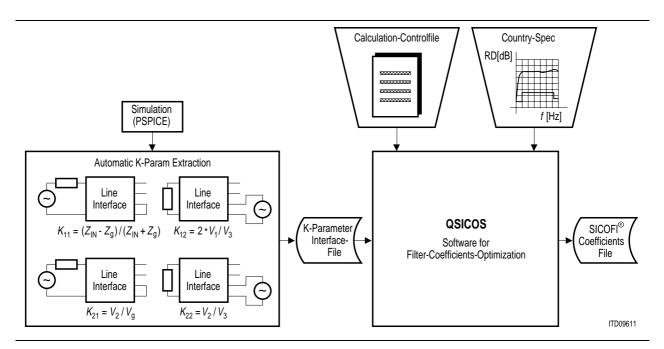

| 46-47                   | Chapter about "QSICOS" added                                                                                  |  |

| 48                      | Clear separation of A-law and μ-law                                                                           |  |

| 49                      | ICN-spec updated                                                                                              |  |

| 58                      | Values for power dissipation and current-consumption updated                                                  |  |

| 59                      | Values for analog input and output resistance updated                                                         |  |

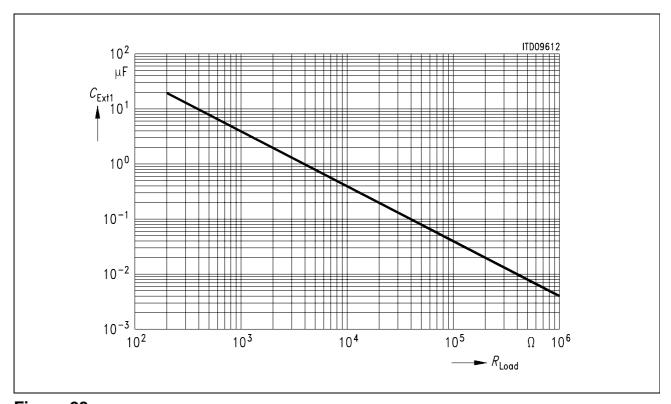

| 60                      | Figure for selection of optimum coupling cap. added                                                           |  |

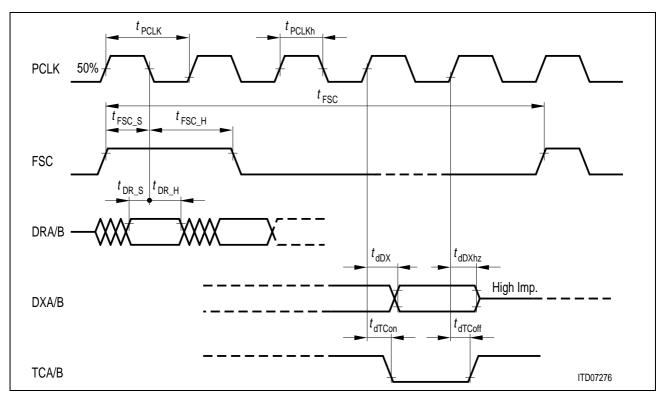

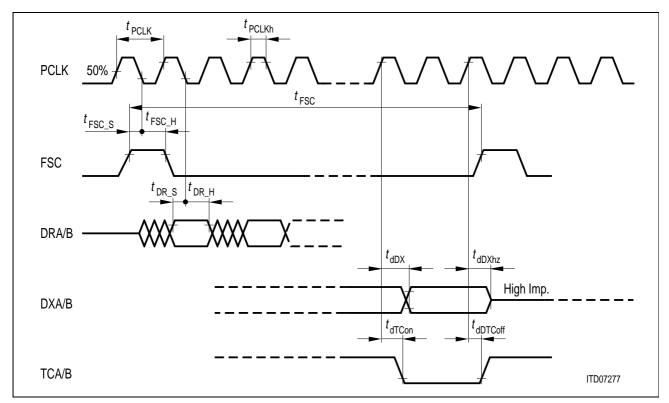

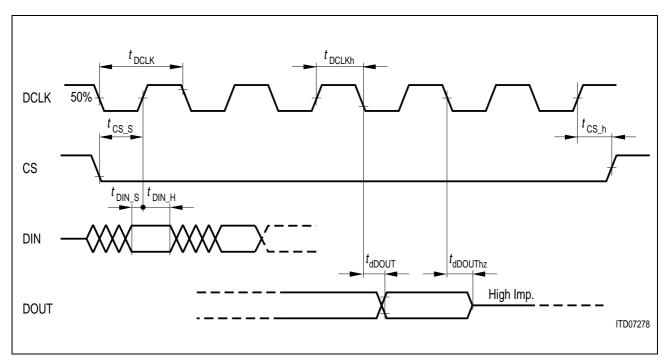

| 61-64                   | Timing spec. figures for digital interfaces added, times updated                                              |  |

| 65                      | Description of Level Metering function added                                                                  |  |

| 68                      | Guidelines for Boarddesign added                                                                              |  |

| PEB 2466<br>Revision H            | listory:                                                                | Current Version: 02.97                                                                                                                             |

|-----------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Previous Versions:  Last Revision |                                                                         | Preliminary Data Sheet 05.95 Errata Sheet 08.95 (valid for V1.1) Errata Sheet 05.96 (valid for V1.2) Preliminary Data Sheet 03.96 Data Sheet 06.96 |

| Page (in current version)         | Subjects (majo                                                          | or changes since last revision)                                                                                                                    |

| 4                                 |                                                                         | d to the pins VDDA12 and VDDA34, reference added to footnote for clarification, INT12, INT34 are active high                                       |

| 26                                | AX1 and AX2 exchanged, in figure "CUT OFFs" and Loops                   |                                                                                                                                                    |

| 27                                | Footnote added regarding attenuation of HPR and HPX                     |                                                                                                                                                    |

| 39                                | Figure "Setting of Slopes in Register XR6" updated                      |                                                                                                                                                    |

| 42                                | Errors in description "Standby- and Operating mode" fixed (PU bit, CR1) |                                                                                                                                                    |

| 44                                | Figure in chapter "QSICOS" clarified                                    |                                                                                                                                                    |

| 45                                | Hint for tool "QSUCCONV.EXE" added                                      |                                                                                                                                                    |

| 46                                | Test conditions completed                                               |                                                                                                                                                    |

| 57                                | "Analog output load"-spec added                                         |                                                                                                                                                    |

| 58                                | Change for clarification, $R_{\rm out} \rightarrow R_{\rm load}$        |                                                                                                                                                    |

| 63                                | Figure updated (AX1 and AX2 exchanged)                                  |                                                                                                                                                    |

| 64                                | Command desc                                                            | cription updated                                                                                                                                   |

| 65                                | Figure "Propos                                                          | ed Test Circuit" updated                                                                                                                           |

| 66                                | Layout-figure u                                                         | pdated                                                                                                                                             |

| 5, 6, 58                          | Coupling capac                                                          | citors in transmit direction updated to 39 nF                                                                                                      |

# **SIEMENS**

| Table                                                                                                                                                                                             | of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| <b>1</b><br>1.1<br>1.2<br>1.3                                                                                                                                                                     | General Description Features Pin Configuration Pin Definition and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8                                            |

| <b>2</b><br>2.1<br>2.2<br>2.3                                                                                                                                                                     | Functional Description $SICOFI^{\text{@}}\text{-}4\text{-}\mu\text{C Principles} \\ The PCM-interface \\ The $\mu$-Controller Interface \\ \\ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15                                           |

| 3<br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.5<br>3.5.6<br>3.5.7<br>3.5.8<br>3.5.9<br>3.6.1<br>3.6.2<br>3.6.3 | Programming the SICOFI®-4-µC Types of Command and Data Bytes Examples for SICOFI®-4 Commands SOP Command CR0 Configuration Register 0 CR1 Configuration Register 1 CR2 Configuration Register 2 CR3 Configuration Register 3 CR4 Configuration Register 4 CR5 Configuration Register 5 COP Command XOP Command XR0 Extended Register 0 XR1 Extended Register 1 XR2 Extended Register 2 XR3 Extended Register 3 XR4 Extended Register 3 XR4 Extended Register 4 XR5 Extended Register 5 XR6 Extended Register 6 XR7 Extended Register 7 Setting of Slopes in Register XR6 The Signaling Interface Operating Modes Programmable Filters QSICOS Software | 24253132333436373840414243444545464748495050 |

|                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                              |

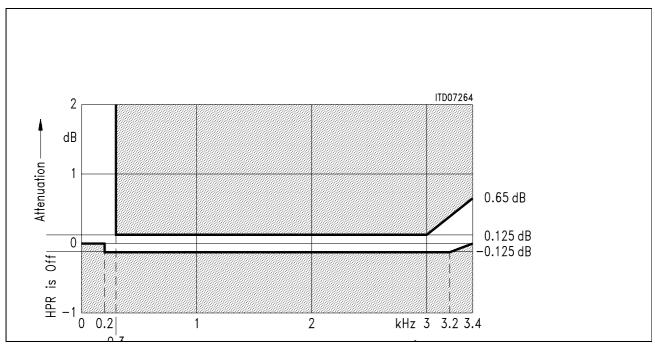

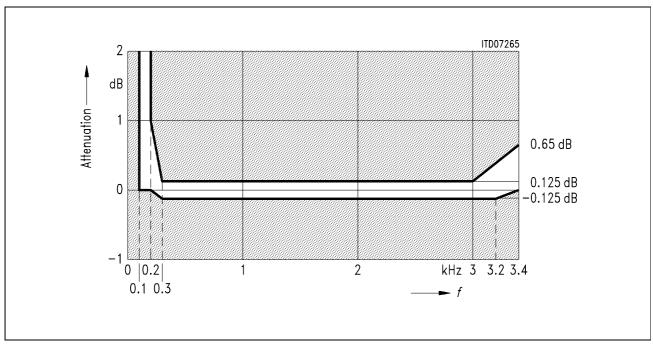

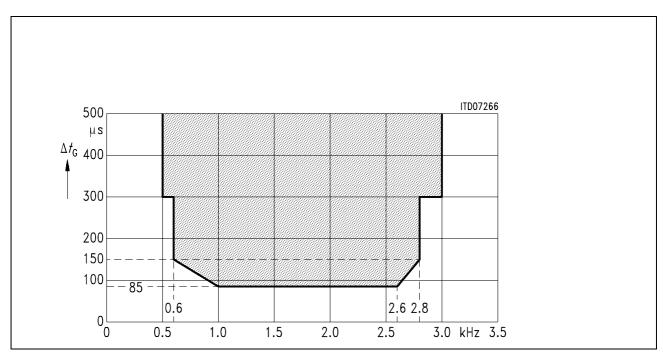

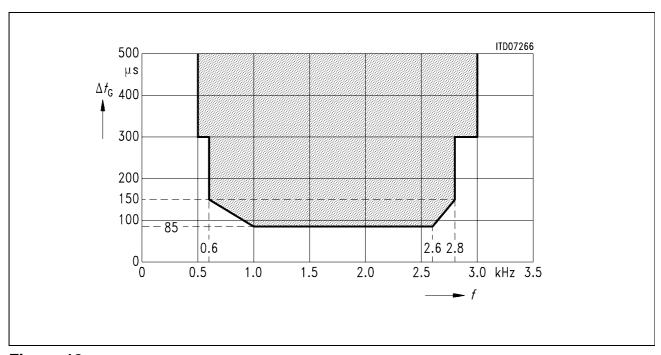

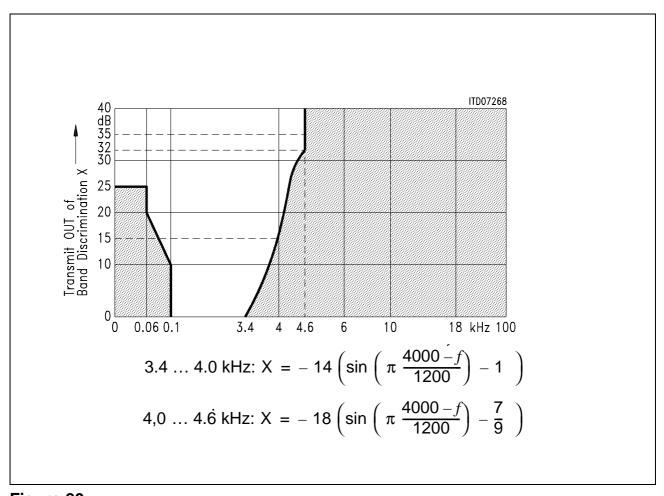

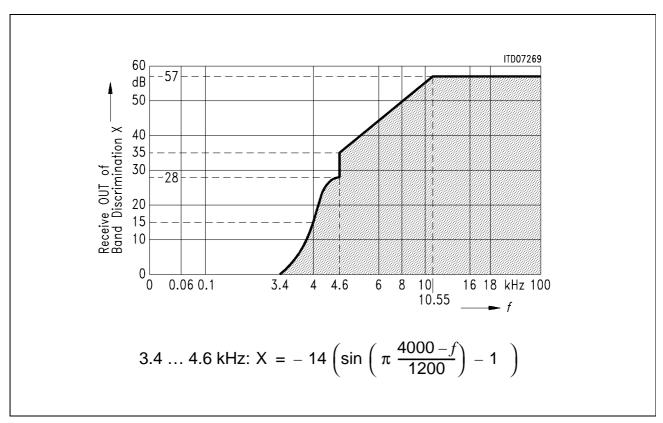

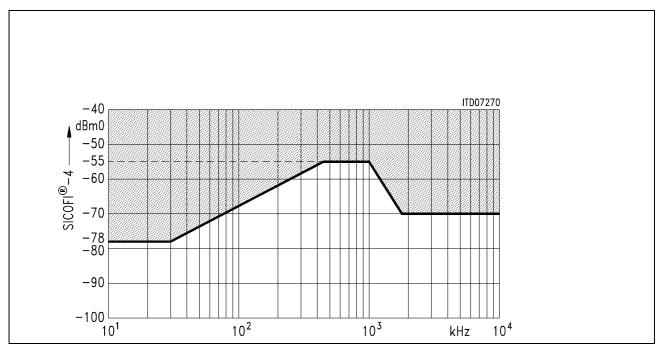

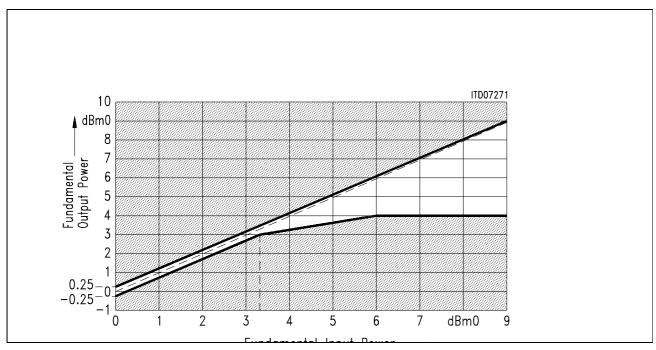

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                                                                                                                            | Transmission Characteristics  Frequency Response  Group Delay  Out-of-Band Signals at Analog Input  Out-of-Band Signals at Analog Output  Out of Band Idle Channel Noise at Analog Output  Overload Compression                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57<br>58<br>60<br>61<br>62                   |

| 4.7                                                                                                                                                                                               | Gain Tracking (receive or transmit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64                                           |

# **SIEMENS**

| Table (                                            | of Contents                                                                                                                                                                                                                                                                                       | Page                 |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 4.8<br>4.8.1<br>4.8.2<br>4.9<br>4.10               | Total Distortion                                                                                                                                                                                                                                                                                  | 65<br>66             |

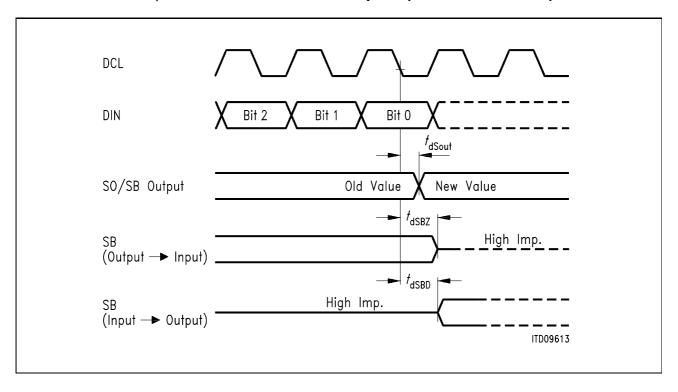

| 5<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | Electrical Characteristics  Coupling Capacitors at the Analog Interface  Reset Timing  PCM-Interface Timing $\mu$ -Controller Interface Timing  Signaling Interface  From the $\mu$ C-interface to the SO/SB-pins (data downstream)  From the SI/SB-pins to the $\mu$ C-interface (data upstream) | 71<br>72<br>74<br>75 |

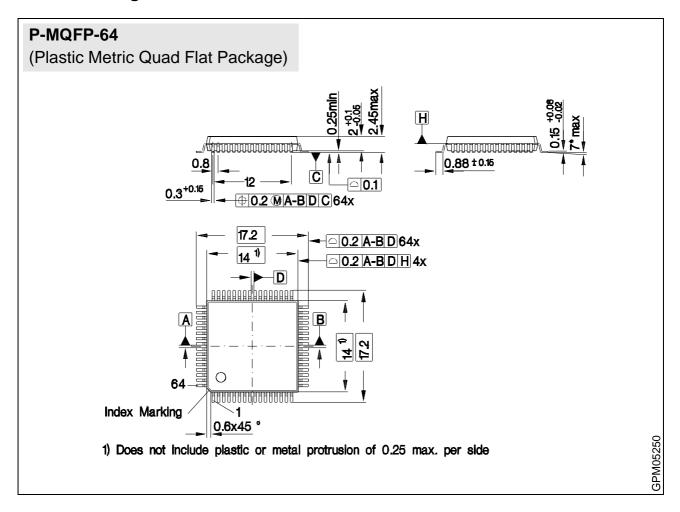

| 6                                                  | Package Outlines                                                                                                                                                                                                                                                                                  | 76                   |

| <b>7</b><br>7.1<br>7.2                             | Appendix                                                                                                                                                                                                                                                                                          | 77                   |

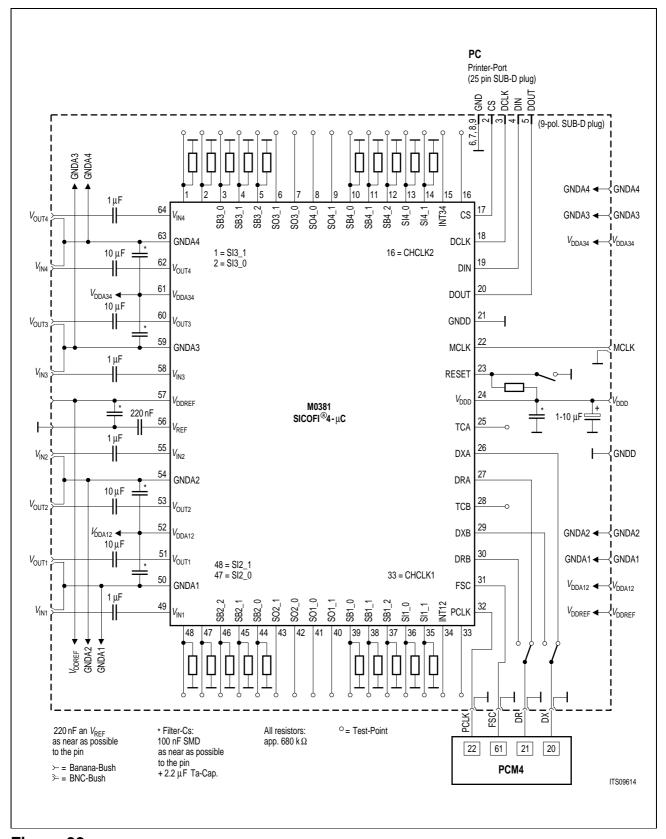

| 8                                                  | Proposed Test Circuit                                                                                                                                                                                                                                                                             | 80                   |

| 9<br>9.1<br>9.2<br>9.3                             | Guidelines for Board-Design  Board Layout Recommendation                                                                                                                                                                                                                                          | 81                   |

IOM®, IOM®-1, IOM®-2, SICOFI®-2, SICOFI®-4 and SICOFI®-4 $\mu$ C, are registered trademarks of Siemens AG.

**General Description**

#### 1 General Description

replaces the IOM-2 interface.

The four channel Signal Processing Codec Filter PEB 2466 SICOFI-4- $\mu$ C is the logical continuation of a well established family of SIEMENS programmable codec-filter-ICs. Its major difference to the PEB 2465 (SICOFI-4) is the PCM and  $\mu$ C interface, which

The SICOFI-4- $\mu$ C is a fully integrated PCM CODEC and FILTER fabricated in low power 1 $\mu$  CMOS technology for applications in digital communication systems. Based on an advanced digital filter concept, the PEB 2466-H provides excellent transmission performance and high flexibility. The new filter concept (second generation) leads to a maximum of independence between the different filter blocks. Each filter block can be seen like a one to one representative of the corresponding network element.

To complete the functionality of the PEB 2466 only two external capacitors per channel are needed. The internal level accuracy is based on a very accurate bandgap reference. The frequency behaviour is mainly determined by digital filters, which do not have any fluctuations. As a result of the new ADC - and DAC - concepts linearity is only limited by second order parasitic effects. Although the device works with only one single 5 V supply there is a very good dynamic range available.

# **SIEMENS**

# Four Channel Codec Filter with PCM- and $\mu$ -Controller Interface SICOFI®4- $\mu$ C

**PEB 2466**

Version 1.2 CMOS

#### 1.1 Features

- Single chip programmable CODEC and FILTER to handle four

- Central Office

- or PABX-channels

- Specification according to relevant CCITT, EIA and LSSGR recommendations

- Digital signal processing technique

- Serial μ-Controller interface

- 2 programmable PCM-interfaces (up to 8 Mbit/s)

- Programmable interface to electronic SLICs and transformer solutions for signaling information

- High analog driving capability (300  $\Omega$ ) for direct driving of transformers

- Programmable digital filters to adapt the transmission behaviour especially for

- AC impedance matching

- transhybrid balancing

- frequency response

- gain

- A/μ-law conversion

- Single 5 V power supply

- Advanced low power 0.9 μm analog CMOS technology

- Low power consumption (< 35 mW per channel)</li>

- High performance A/D conversion

- High performance D/A conversion

- · Advanced test capabilities

- five digital loops

- four analog loops

- two programmable tone generators (DTMF possible)

- built in self-test

- level metering function for system tests

- Standard P-MQFP-64 package

- Comprehensive development platform available

- software for automatic filter coefficient calculation QSICOS

- Hardware development board STSI 2466

| Туре            | Ordering Code | Package   |

|-----------------|---------------|-----------|

| PEB 2466-H V1.2 | on request    | P-MQFP-64 |

8

#### **General Description**

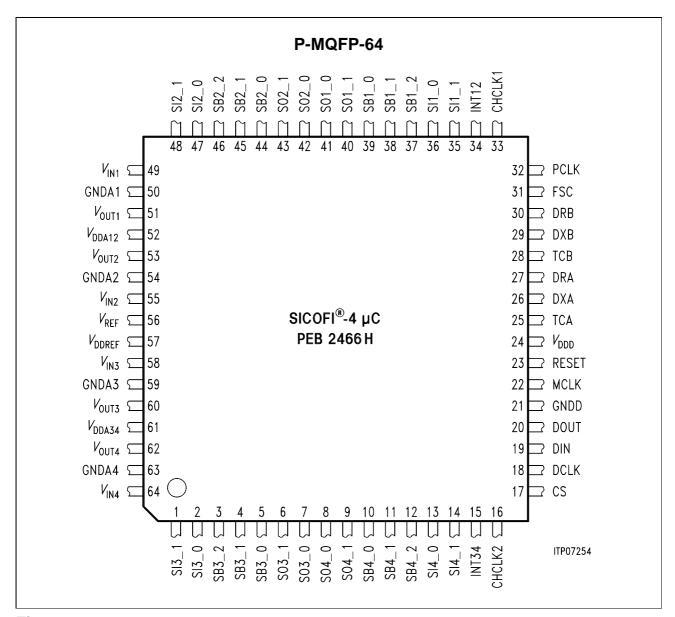

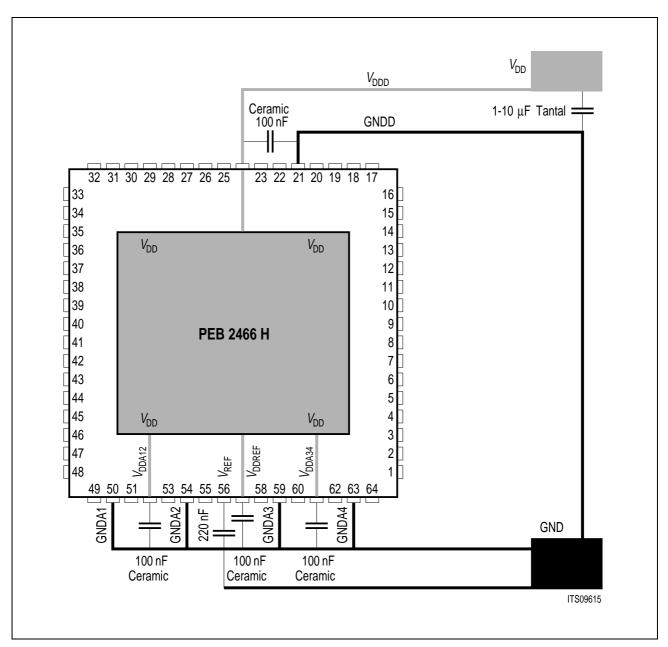

#### 1.2 Pin Configuration

(top view)

Figure 1

# **General Description**

#### 1.3 Pin Definition and Functions

| Output (O) | Pin No. | • | Input (I)<br>Output (O) | Function |

|------------|---------|---|-------------------------|----------|

|------------|---------|---|-------------------------|----------|

#### **Common Pins for all Channels**

| 24 | $V_{DDD}$   | I   | + 5 V supply for the digital circuitry 1)                                                                                                                          |

|----|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 | GNDD        | I   | Ground Digital, not internally connected to GNDA1,2,3,4 All digital signals are referred to this pin                                                               |

| 52 | $V_{DDA12}$ | I   | + 5 V Analog supply voltage for channel 1 and 2 1)                                                                                                                 |

| 61 | $V_{DDA34}$ | ı   | + 5 V Analog supply voltage for channel 3 and 4 1)                                                                                                                 |

| 56 | $V_{REF}$   | I/O | Reference voltage, has to be connected to a 220 nF cap. to ground, can also be used as virtual ground for analog inputs and outputs (high-ohmic buffer needed !!!) |

| 57 | $V_{DDREF}$ | I   | + 5 V Analog supply voltage (100 nF cap. required)                                                                                                                 |

| 31 | FSC         | I   | Frame synchronization clock, 8 kHz, identifies the beginning of the frame, individual time slots are referenced to this pin, FSC must be synchronous to PCLK       |

| 32 | PCLK        | I   | Data clock 128 to 8192 kHz, determines the rate at which PCM data is shifted into or out of the PCM-ports                                                          |

| 30 | DRB         | I   | PCM-interface: Receive PCM data from PCM-highway B, data for each channel is received in 8 bit bursts every 125 μs                                                 |

| 29 | DXB         | 0   | PCM-interface: Transmit PCM data to PCM-highway B, data for each channel is transmitted in 8 bit burst every 125 μs                                                |

| 28 | TCB         | 0   | PCM-interface: Transmit control output B, is active if data is transmitted via DXB, active low, open drain                                                         |

| 27 | DRA         | I   | PCM-interface: Receive PCM data from PCM-highway A, data for each channel is received in 8 bit bursts every 125 μs                                                 |

| 26 | DXA         | 0   | PCM-interface: Transmit PCM data to PCM-highway A, data for each channel is transmitted in 8 bit burst every 125 μs                                                |

# **General Description**

# 1.3 Pin Definition and Functions (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                   |

|---------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25      | TCA    | 0                       | PCM-interface: Transmit control output A, is active if data is transmitted via DXA, active low, open drain                                                 |

| 23      | RESET  | I                       | Reset input - forces the device to default mode, active low                                                                                                |

| 22      | MCLK   | 1                       | Master clock input, 1536, 2048, 4096 or 8192 kHz, synchronous to FSC, must be available if the SICOFI-4-μC is used                                         |

| 17      | CS     | I                       | μ-Controller interface: chip select enable to read or write data, active low                                                                               |

| 18      | DCLK   | I                       | μ-Controller interface: data clock, shifts data from or to device, the maximum clock rate is 8192 kHz                                                      |

| 19      | DIN    | I                       | μ-Controller interface: control data input pin, DCLK determines the data rate                                                                              |

| 20      | DOUT   | 0                       | $\mu$ -Controller interface: control data output pin, DCLK determines the data rate, DOUT is high 'Z' if no data is transmitted from the SICOFI-4- $\mu$ C |

| 33      | CHCLK1 | 0                       | Chopper Clock output, provides a programmable (2 28 ms) output signal (synchronous to MCLK)                                                                |

| 16      | CHCLK2 | 0                       | Chopper Clock output, provides a 256, or 512 or 16384 kHz signal, is synchronous to MCLK                                                                   |

| 34      | INT12  | 0                       | Interrupt output pin for channel 1 and 2, active high                                                                                                      |

| 15      | INT34  | 0                       | Interrupt output pin for channel 3 and 4, active high                                                                                                      |

# **General Description**

02.97

# 1.3 Pin Definition and Functions (cont'd)

| Pin No. | Symbol | Input (I)  | Function |

|---------|--------|------------|----------|

|         |        | Output (O) |          |

# **Specific Pins for Channel 1**

| GNDA1      | I                                                                                  | Ground Analog for channel 1, not internally connected to GNDD or GNDA2,3,4                                   |

|------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| $V_{IN1}$  | I                                                                                  | Analog voice (voltage) input for channel 1, has to be connected to the SLIC by a 39 nF cap.                  |

| $V_{OUT1}$ | 0                                                                                  | Analog voice (voltage) output for channel 1, has to be connected to the SLIC via a cap. <sup>2)</sup>        |

| SI1_0      | I                                                                                  | Signaling input pin 0 for channel 1                                                                          |

| SI1_1      | I                                                                                  | Signaling input pin 1 for channel 1                                                                          |

| SO1_0      | 0                                                                                  | Signaling output pin 0 for channel 1                                                                         |

| SO1_1      | 0                                                                                  | Signaling output pin 1 for channel 1                                                                         |

| SB1_0      | I/O                                                                                | Bi-directional signaling pin 0 for channel 1                                                                 |

| SB1_1      | I/O                                                                                | Bi-directional signaling pin 1 for channel 1                                                                 |

| SB1_2      | I/O                                                                                | Bi-directional signaling pin 2 for channel 1                                                                 |

|            | $V_{\rm IN1}$ $V_{\rm OUT1}$ $SI1\_0$ $SI1\_1$ $SO1\_0$ $SO1\_1$ $SB1\_0$ $SB1\_1$ | $V_{\text{IN1}}$ I $V_{\text{OUT1}}$ O $SI1\_0$ I $SI1\_1$ I $SO1\_0$ O $SO1\_1$ O $SB1\_0$ I/O $SB1\_1$ I/O |

# **Specific Pins for Channel 2**

| 54 | GNDA2      | I   | Ground Analog for channel 2, not internally connected to GNDD or GNDA 1,3,4                 |

|----|------------|-----|---------------------------------------------------------------------------------------------|

| 55 | $V_{IN2}$  | I   | Analog voice (voltage) input for channel 2, has to be connected to the SLIC by a 39 nF cap. |

| 53 | $V_{OUT2}$ | 0   | Analog voice (voltage) output for channel 2, has to be connected to the SLIC via a cap. 2)  |

| 47 | SI2_0      | I   | Signaling input pin 0 for channel 2                                                         |

| 48 | SI2_1      | I   | Signaling input pin 1 for channel 2                                                         |

| 42 | SO2_0      | 0   | Signaling output pin 0 for channel 2                                                        |

| 43 | SO2_1      | 0   | Signaling output pin 1 for channel 2                                                        |

| 44 | SB2_0      | I/O | Bi-directional signaling pin 0 for channel 2                                                |

| 45 | SB2_1      | I/O | Bi-directional signaling pin 1 for channel 2                                                |

| 46 | SB2_2      | I/O | Bi-directional signaling pin 2 for channel 2                                                |

# **General Description**

# 1.3 Pin Definition and Functions (cont'd)

| Pin No. | Symbol | Input (I)  | Function |

|---------|--------|------------|----------|

|         |        | Output (O) |          |

# **Specific Pins for Channel 3**

| 59 | GNDA3      | I   | Ground Analog for channel 3, not internally connected to GNDD or GNDA1,2,4                  |

|----|------------|-----|---------------------------------------------------------------------------------------------|

| 58 | $V_{IN3}$  | I   | Analog voice (voltage) input for channel 3, has to be connected to the SLIC by a 39 nF cap. |

| 60 | $V_{OUT3}$ | 0   | Analog voice (voltage) output for channel 3, has to be connected to the SLIC via a cap. 2)  |

| 2  | SI3_0      | I   | Signaling input pin 0 for channel 3                                                         |

| 1  | SI3_1      | I   | Signaling input pin 1 for channel 3                                                         |

| 7  | SO3_0      | 0   | Signaling output pin 0 for channel 3                                                        |

| 6  | SO3_1      | 0   | Signaling output pin 1 for channel 3                                                        |

| 5  | SB3_0      | I/O | Bi-directional signaling pin 0 for channel 3                                                |

| 4  | SB3_1      | I/O | Bi-directional signaling pin 1 for channel 3                                                |

| 3  | SB3_2      | I/O | Bi-directional signaling pin 2 for channel 3                                                |

#### **General Description**

02.97

# 1.3 Pin Definition and Functions (cont'd)

| Pin No. | Symbol | Input (I)  | Function |

|---------|--------|------------|----------|

|         |        | Output (O) |          |

#### **Specific Pins for Channel 4**

| 63 | GNDA4      | I   | Ground Analog for channel 4, not internally connected to GNDD or GNDA1,2,3                            |

|----|------------|-----|-------------------------------------------------------------------------------------------------------|

| 64 | $V_{IN4}$  | I   | Analog voice (voltage) input for channel 4, has to be connected to the SLIC by a 39 nF cap.           |

| 62 | $V_{OUT4}$ | 0   | Analog voice (voltage) output for channel 4, has to be connected to the SLIC via a cap. <sup>2)</sup> |

| 13 | SI4_0      | I   | Signaling input pin 0 for channel 4                                                                   |

| 14 | SI4_1      | I   | Signaling input pin 1 for channel 4                                                                   |

| 8  | SO4_0      | 0   | Signaling output pin 0 for channel 4                                                                  |

| 9  | SO4_1      | 0   | Signaling output pin 1 for channel 4                                                                  |

| 10 | SB4_0      | I/O | Bi-directional signaling pin 0 for channel 4                                                          |

| 11 | SB4_1      | I/O | Bi-directional signaling pin 1 for channel 4                                                          |

| 12 | SB4_2      | I/O | Bi-directional signaling pin 2 for channel 4                                                          |

<sup>&</sup>lt;sup>1)</sup> A 100 nF cap. should be used for blocking these pins, see also on page 82

<sup>&</sup>lt;sup>2)</sup> The value for the capacitor needed, depends on the input impedance of the 'SLIC'-circuitry. For choosing the appropriate values see figure on page 71.

#### 2 Functional Description

#### 2.1 SICOFI®-4-μC Principles

The change from 2  $\mu m$  to 1  $\mu m$  CMOS process requires new concepts in the realization of the analog functions. High performance (in the terms of gain, speed, stability ...) 1  $\mu m$  CMOS devices cannot withstand more than 5.5 V of supply-voltage. On that account the negative supply voltage VSS of the previous SICOFIs is omitted. This is a benefit for the user but it makes a very high demand on the analog circuitry.

ADC and DAC are changed to Sigma-Delta-concepts to fulfill the stringent requirements on the dynamic parameters.

Using 1  $\mu$ m CMOS does not only lead to problems - it is the only acceptable solution in terms of area and power consumption for the integration of more than two SICOFI channels on a single chip.

It is rather pointless to implement 4 codec-filter-channels on one chip with pure analog circuitry. The use of a DSP-concept (the SICOFI and the SICOFI-2-approach) for this function is a must for an adequate four channel architecture.

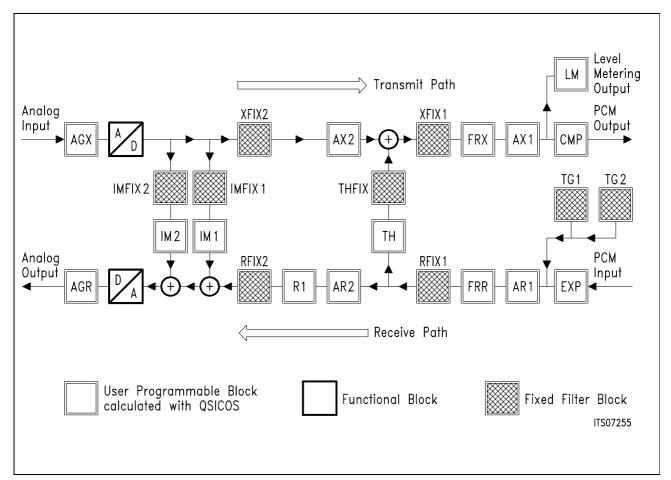

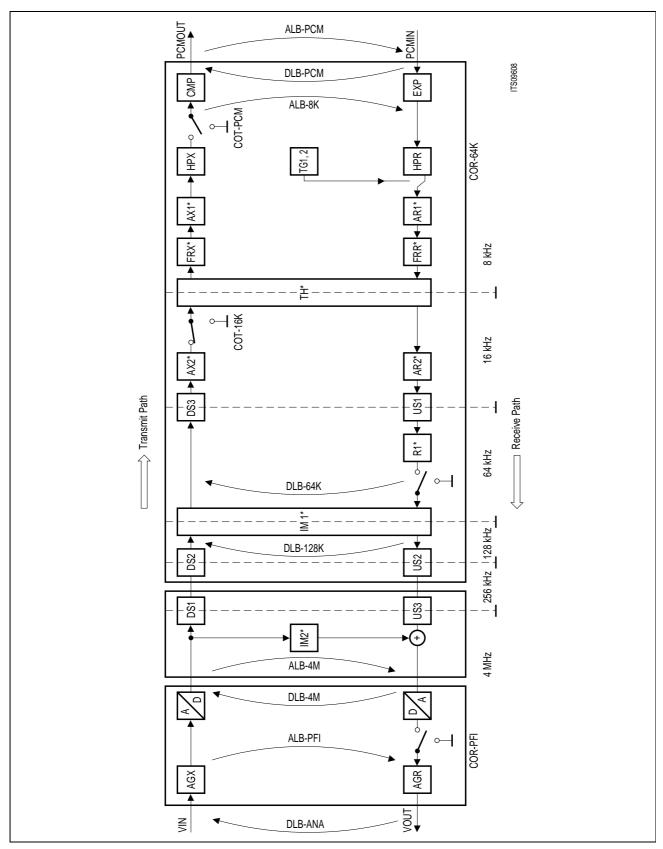

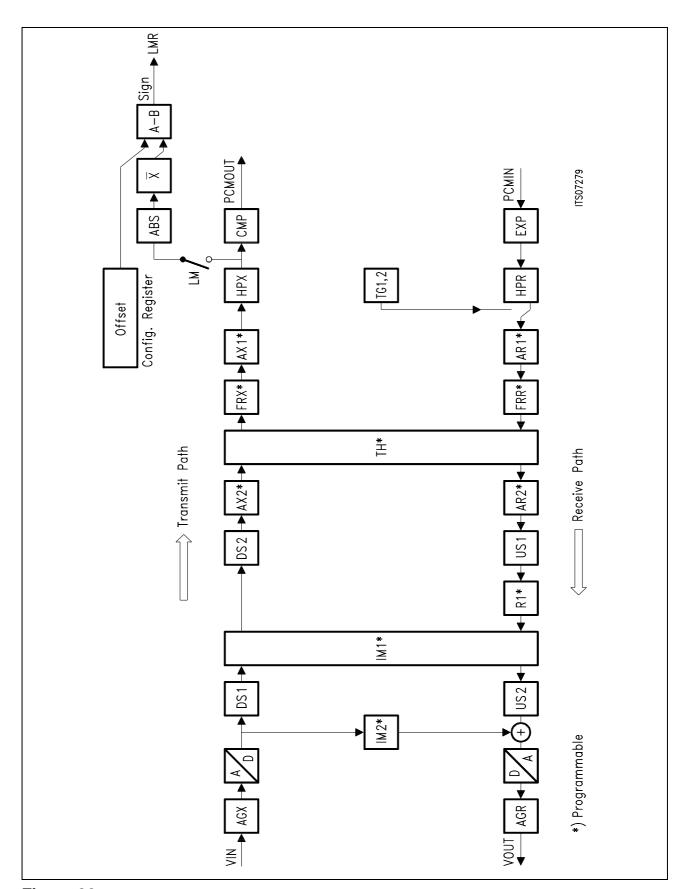

Figure 2 SICOFI®-4 μC Signal Flow Graph (for any channel)

#### **Transmit Path**

The analog input signal has to be DC-free connected by an external capacitor because there is an internal virtual reference ground potential. After passing a simple antialiasing prefilter (PREFI) the voice signal is converted to a 1-bit digital data stream in the Sigma-Delta-converter. The first downsampling steps are done in fast running digital hardware filters. The following steps are implemented in the micro-code which has to be executed by the central Digital Signal Processor. This DSP-machine is able to handle the workload for all four channels. At the end the fully processed signal (flexibly programmed in many parameters) is transferred to the PCM- interface in a PCM-compressed signal representation.

#### **Receive Path**

The digital input signal is received via the PCM interface. Expansion, PCM-Law-pass-filtering, gain correction and frequency response correction are the next steps which are done by the DSP-machine. The upsampling interpolation steps are again processed by fast hardware structures to reduce the DSP-workload. The upsampled 1-bit data stream is then converted to an analog equivalent which is smoothed by a POST-Filter (POFI). As the signal  $V_{\rm OUT}$  is also referenced to an internal virtual ground potential, an external capacitor is required for DC-decoupling.

#### Loops

There are two loops implemented. The first is to generate the AC-input impedance (IM) and the second is to perform a proper hybrid balancing (TH). A simple extra path IM2 (from the transmit to the receive path) supports the impedance matching function.

#### **Test Features**

There are four analog and five digital test loops implemented in the SICOFI-4. For special tests it is possible to Cut Off the receive and the transmit path at two different points.

02.97

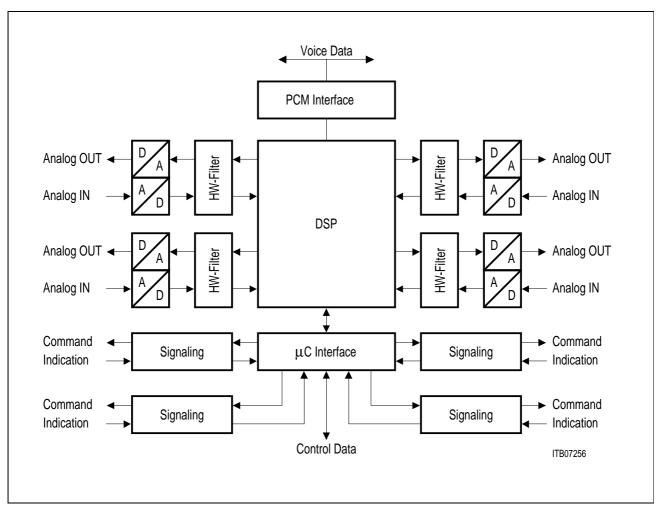

Figure 3 SICOFI<sup>®</sup>-4-μC Block Diagram

The SICOFI-4- $\mu$ C bridges the gap between analog and digital voice signal transmission in modern telecommunication systems. High performance oversampling Analog-to-Digital Converters (ADC) and Digital-to-Analog Converters (DAC) provide the conversion accuracy required. Analog antialiasing prefilters (PREFI) and smoothing postfilters (POFI) are included. The connection between the ADC and the DAC (with high sampling rate) and the DSP, is done by specific Hardware Filters, for filtering like interpolation and decimation. The dedicated Digital Signal Processor (DSP) handles all the algorithms necessary e.g. for PCM bandpass filtering, sample rate conversion and PCM companding. The PCM-interface handles digital voice transmission, a serial  $\mu$ C-interface handles SICOFI-4- $\mu$ C feature control and transparent access to the SICOFI-4- $\mu$ C command and indication pins. To program the filters, precalculated sets of coefficients are downloaded from the system to the on-chip Coefficient-RAM (CRAM).

#### **Functional Description**

02.97

#### 2.2 The PCM-interface

Two serial PCM-interfaces are used for the transfer of A- or  $\mu$ -law compressed voice data. The PCM-interface consist of 8 pins:

PCLK: PCM-Clock, 128 kHz to 8192 kHz

FSC: Frame Synchronization Clock, 8 kHz

DRA: Receive Data input for PCM-highway A

DRB: Receive Data input for PCM-highway B

DXA: Transmit Data output for PCM-highway A

DXB: Transmit Data output for PCM-highway B

TCA: Transmit Control Output for PCM-highway A, active low during transmission

TCB: Transmit Control Output for PCM-highway B, active low during transmission

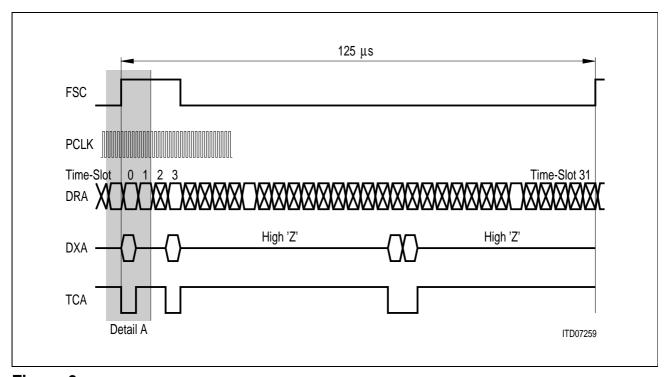

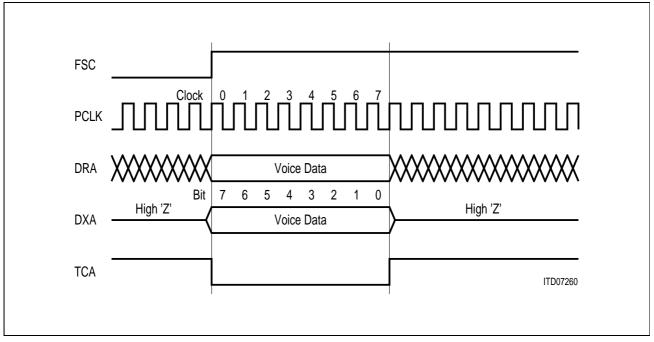

The Frame Sync FSC pulse identifies the beginning of a receive and transmit frame for all of the four channels. The PCLK clock is the signal to synchronize the data transfer on both lines DXA (DXB) and DRA (DRB). Bytes in all channels are serialized to 8 bit width and MSB first. As a default setting, the rising edge indicates the start of the bit, while the falling edge is used to latch the contents of the received data on DRA (DRB). If the double clock rate is chosen (twice the transmission rate) the first rising edge indicates the start of a bit, while the second falling edge is used for latching the contents of the data line DRA (DRB) by default.

The data rate of the interface can vary from  $2 \times 128$  kbit/s to  $2 \times 8192$  kbit/s (2 highways) A frame may consist of up to 128 time slots of 8 bits each. In the Time Slot Configuration Registers CR5 and CR6 the user can select an individual time slot, and an individual PCM-highway, for any of the four voice channels. Receive and transmit time slots can also be programmed individually. An extra delay of up to 7 clocks, valid for all channels, as well as the sampling slope may be programmed (see XR6).

When the SICOFI-4- $\mu$ C is transmitting data on DXA (DXB), pin TCA (TCB) is activated to control an extra external driving device.

The following table shows possible examples for the PCM-interface, other frequencies like 768 kHz or 1536 kHz are also possible.

Table 1

|         | Frequency<br>[kHz] | Single/Double [1/2] | Time Slots<br>[per highway] | Datarate<br>[kbit/s per highway] |

|---------|--------------------|---------------------|-----------------------------|----------------------------------|

|         | 128                | 1                   | 2                           | 128                              |

|         | 256                | 2                   | 2                           | 128                              |

|         | 256                | 1                   | 4                           | 256                              |

|         | 512                | 2                   | 4                           | 256                              |

|         | 512                | 1                   | 8                           | 512                              |

|         | 1024               | 2                   | 8                           | 512                              |

|         | 1024               | 1                   | 16                          | 1024                             |

|         | 2048               | 2                   | 16                          | 1024                             |

|         | 2048               | 1                   | 32                          | 2048                             |

|         | 4096               | 2                   | 32                          | 2048                             |

|         | 4096               | 1                   | 64                          | 4096                             |

|         | 8192               | 2                   | 64                          | 4096                             |

|         | 8192               | 1                   | 128                         | 8192                             |

| Formula | f                  | 1                   | f/64                        | f                                |

| Formula | f                  | 2                   | f/128                       | f/2                              |

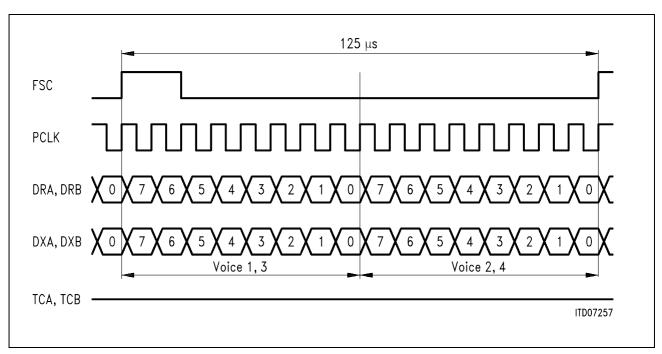

Figure 4

Example for Single Clock Rate, 128 kbit/s

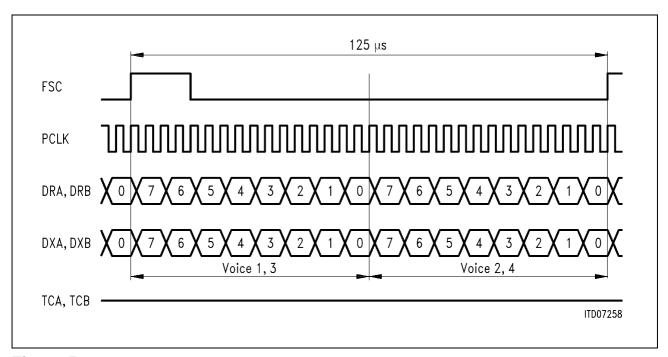

Figure 5

Example for Double Clock Rate, 128 kbit/s

Figure 6

Example for 2048 kbit/s, Single Clock Operation, only Highway A used

Figure 7

Detail A

For special purposes the DRA/B and DXA/B pins may be strapped together, and form bi-directional data-'pin' (like SIP with the SLD-bus).

#### 2.3 The $\mu$ -Controller Interface

The internal configuration registers, the signaling interface, and the Coefficient-RAM (CRAM) of the SICOFI-4- $\mu$ C are programmable via a serial  $\mu$ -Controller interface.

The μ-Controller interface consists of four lines: CS, DCLK, DIN and DOUT:

CS is used to start a serial access to the SICOFI-4- $\mu$ C registers and Coefficient-RAM. Following a falling edge of CS, the first eight bits received on DIN specify the command. Subsequent data bytes (number depends on command) are stored in the selected configuration registers or the selected part of the Coefficient-RAM.

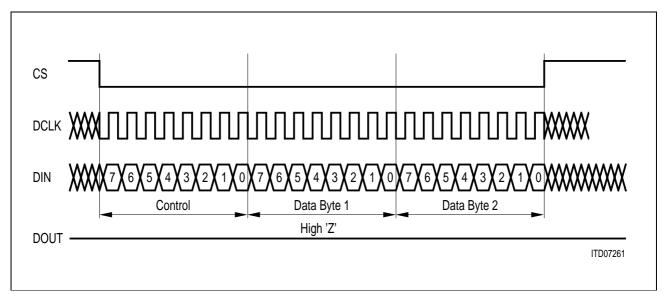

Figure 8

Example for a Write Access, with Two Data Bytes Transferred

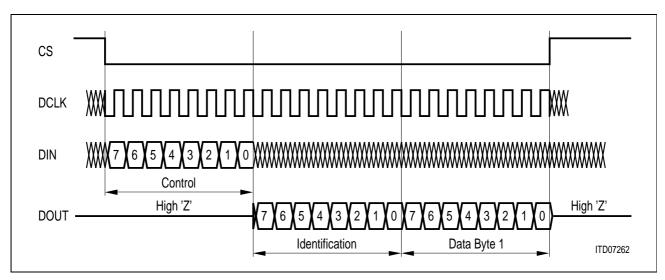

If the first eight bits received via DIN specify a read-command, the SICOFI-4 will start a response via DOUT with its specific address byte (81<sub>H</sub>). After transmitting this identification, the specified n data bytes (contents of configuration registers, or contents of the CRAM) will follow on DOUT.

Figure 9

Example for a Read Access, with One Data Byte Transferred via DOUT

The data transfer is synchronized by the DCLK input. The contents of DIN is latched at the rising edge of DCLK, while DOUT changes with the falling edge of DCLK. During execution of commands that are followed by output data (read commands), the device will not accept any new command via DIN. The data transfer sequence can be broken by setting CS to high.

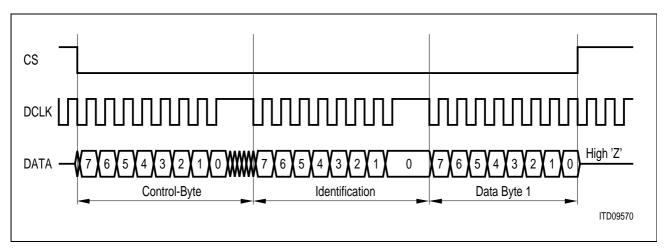

To reduce the number of connections to the  $\mu P$  DIN and DOUT may be strapped together, and form a bi-directional data-'pin'.

For special applications a byte by byte transfer is needed. This can be done by prolonging the high time of DCLK for a user defined 'waiting time' after transferring any byte.

Figure 10

Example for a Write/Read Access, with a Byte by Byte Transfer, and DIN and DOUT Strapped Together

The Identification Byte is "81<sub>H</sub>" for the PEB 2466.

#### 3 Programming the SICOFI®-4-μC

With the appropriate commands, the SICOFI-4- $\mu$ C can be programmed and verified very flexibly via the  $\mu$ -Controller interface.

With the first byte received via DIN, one of 3 different types of commands (SOP, XOP and COP) is selected. Each of those can be used as a write or read command. Due to the extended SICOFI-4- $\mu$ C feature control facilities, SOP, COP and XOP commands contain additional information (e.g. number of subsequent bytes) for programming (write) and verifying (read) the SICOFI-4- $\mu$ C status.

A write command is followed by up to 8 bytes of data. The SICOFI-4- $\mu$ C responds to a read command with its specific identification and the requested information, that is up to 8 bytes of data.

#### 3.1 Types of Command and Data Bytes

The 8-bit bytes have to be interpreted as either commands or status information stored in Configuration Registers or the Coefficient-RAM. There are three different types of SICOFI-4-μC commands which are selected by bit 3 and 4 as shown below.

| SOP | STA | TUS OPE  | RATION: | 5               | SICOFI-4-μC status setting/monitoring |              |            |         |  |  |  |  |

|-----|-----|----------|---------|-----------------|---------------------------------------|--------------|------------|---------|--|--|--|--|

| Bit | 7   |          |         |                 |                                       |              |            | 0       |  |  |  |  |

|     | AD2 | AD1      |         | 1               | 0                                     |              |            |         |  |  |  |  |

| ХОР | EXT | ENDED O  | PERATIO | N: (            | C/I <sup>1)</sup> chanr               | nel configu  | ration/eva | luation |  |  |  |  |

| Bit | 7   |          |         |                 |                                       |              |            | 0       |  |  |  |  |

|     |     | 0        |         | 1               | 1                                     |              |            |         |  |  |  |  |

| СОР | COE | FFICIENT | OPERAT  | Γ <b>ΙΟΝ:</b> f | Iter coeffic                          | eient settin | g/monitori | ng      |  |  |  |  |

| Bit | 7   |          |         |                 |                                       |              |            | 0       |  |  |  |  |

|     | AD2 | AD1      |         | 0               |                                       |              |            |         |  |  |  |  |

Note: 1) Command/Indication (signaling) channel.

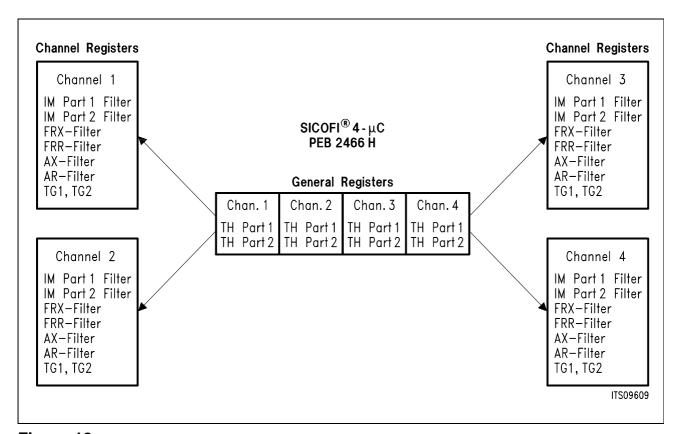

#### **Storage of Programming Information**

6 configuration registers per channel: CR0, CR1, CR2, CR3, CR4 and CR5

accessed by SOP commands

8 common configuration registers: XR0 .. XR7 accessed by XOP commands,

valid for all 4 channels

1 Coefficient-RAM per channel: CRAM accessed by COP commands

#### 3.2 Examples for SICOFI®-4 Commands

#### **SOP - Write Commands**

| DIN               | 7        | c | E | 1  | 2   | 2 | 4 | ^    | D:+ | 7 | c | E | 1  | 2  | 2 | 4 | 0 | DOLIT |

|-------------------|----------|---|---|----|-----|---|---|------|-----|---|---|---|----|----|---|---|---|-------|

| DIN               | <i>'</i> | 6 | 5 | 4  | 3   | 2 | 1 | 0    | Bit | 7 | 6 | 5 | 4  | 3  |   | 1 | 0 | DOUT  |

| SOP-Write 1 Byte  |          |   | 0 | 1  | 0   | 0 | 0 | 0    |     |   |   |   | ld | le |   |   |   |       |

| CR0               |          |   |   | Da | ata |   |   |      |     |   |   |   | ld | le |   |   |   |       |

| DIN               | 7        | 6 | 5 | 4  | 3   | 2 | 1 | 0    | Bit | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | DOUT  |

| SOP-Write 2 Bytes |          |   | 0 | 1  | 0   | 0 | 0 | 1    |     |   |   |   | ld | le |   |   |   |       |

| CR1               |          | • | • | Da | ata |   |   |      |     |   |   |   | ld | le |   |   |   |       |

| CR0               |          |   |   | Da | ata |   |   |      |     |   |   |   | ld | le |   |   |   |       |

| DIN               | 7        | 6 | 5 | 4  | 3   | 2 | 1 | 0    | Bit | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | DOUT  |

| SOP-Write 3 Bytes |          |   | 0 | 1  | 0   | 0 | 1 | 0    |     |   |   |   | ld | le |   |   |   |       |

| CR2               |          | • | • | Da | ata |   |   |      |     |   |   |   | ld | le |   |   |   |       |

| CR1               |          |   |   | Da | ata |   |   |      |     |   |   |   | ld | le |   |   |   |       |

| CR0               |          |   |   | Da | ata |   |   |      |     |   |   |   | ld | le |   |   |   |       |

| DIN               | 7        | 6 | 5 | 4  | 3   | 2 | 1 | 0    | Bit | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | DOUT  |

| SOP-Write 4 Bytes |          |   | 0 | 1  | 0   | 0 | 1 | 1    |     |   |   |   | ld | le |   |   |   |       |

| CR3               |          | I |   | Da | ata | ı |   | ı    |     |   |   |   | ld | le |   |   |   |       |

| CR2               |          |   |   | Da | ata |   |   |      |     |   |   |   | ld | le |   |   |   |       |

| CR1               | Data     |   |   |    |     |   |   | Idle |     |   |   |   |    |    |   |   |   |       |

| CR0               |          |   |   | Da | ata |   |   |      |     |   |   |   | Id | le |   |   |   |       |

#### **XOP - Write Commands**

| DIN               | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | DOUT |

|-------------------|---|---|---|----|-----|---|---|---|-----|---|---|---|----|----|---|---|---|------|

| XOP-Write 2 Bytes |   |   | 0 | 1  | 1   | 0 | 0 | 1 |     |   |   |   | ld | le |   |   |   |      |

| XR1               |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| XR0               |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| DIN               | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | DOUT |

| XOP-Write 3 Bytes |   |   | 0 | 1  | 1   | 0 | 1 | 0 |     |   |   |   | ld | le |   |   |   |      |

| XR2               |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| XR1               |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

Data

#### **COP - Write Commands**

XR0

| DIN               | 7 | 6    | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7 | 6    | 5 | 4  | 3   | 2 | 1 | 0 | DOUT |

|-------------------|---|------|---|----|-----|---|---|---|-----|---|------|---|----|-----|---|---|---|------|

| COP-Write 4 Bytes |   |      | 0 | 0  |     |   |   |   |     |   |      |   | ld | lle |   |   |   |      |

| Coeff. 3          |   |      |   | Da | ata |   |   |   |     |   |      |   | ld | lle |   |   |   |      |

| Coeff. 2          |   | Data |   |    |     |   |   |   |     |   | Idle |   |    |     |   |   |   |      |

| Coeff. 1          |   |      |   | Da | ata |   |   |   |     |   |      |   | ld | lle |   |   |   |      |

| Coeff. 0          |   |      |   | Da | ata |   |   |   |     |   |      |   | ld | lle |   |   |   |      |

| DIN               | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | DOUT |

|-------------------|---|---|---|----|-----|---|---|---|-----|---|---|---|----|----|---|---|---|------|

| COP-Write 8 Bytes |   |   | 0 | 0  |     |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| Coeff. 7          |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| Coeff. 6          |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| Coeff. 5          |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| Coeff. 4          |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| Coeff. 3          |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| Coeff. 2          |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| Coeff. 1          |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | le |   |   |   |      |

| Coeff. 0          |   | • | • | Da | ata | • | • | • |     |   |   |   | ld | le |   | • |   |      |

| Idle |  |

|------|--|

| ldle |  |

| Idle |  |

| Idle |  |

Idle

#### **SOP - Read Commands**

| DIN              | 7 6 5 4 3 2 1 0 | Bit | 7 6 5 4 3 2 1 0 | DOUT           |

|------------------|-----------------|-----|-----------------|----------------|

| SOP-Read 1 Byte  | 1 1 0 0 0 0     |     | Idle            |                |

|                  | Idle            |     | 1 0 0 0 0 0 0 1 | Identification |

|                  | Idle            |     | Data            | CR0            |

| DIN              | 7 6 5 4 3 2 1 0 | Bit | 7 6 5 4 3 2 1 0 | DOUT           |

| SOP-Read 2 Bytes | 1 1 1 0 0 0 1   |     | Idle            |                |

|                  | Idle            |     | 1 0 0 0 0 0 0 1 | Identification |

|                  | Idle            |     | Data            | CR1            |

|                  | Idle            |     | Data            | CR0            |

| DIN              | 7 6 5 4 3 2 1 0 | Bit | 7 6 5 4 3 2 1 0 | DOUT           |

| SOP-Read 3 Bytes | 1 1 0 0 1 0     |     | Idle            |                |

|                  | Idle            |     | 1 0 0 0 0 0 0 1 | Identification |

|                  | Idle            |     | Data            | CR2            |

|                  | Idle            |     | Data            | CR1            |

|                  | Idle            |     | Data            | CR0            |

| DIN              | 7 6 5 4 3 2 1 0 | Bit | 7 6 5 4 3 2 1 0 | DOUT           |

| SOP-Read 4 Bytes | 1 1 0 0 1 1     |     | Idle            |                |

|                  | Idle            |     | 1 0 0 0 0 0 0 1 | Identification |

|                  | Idle            |     | Data            | CR3            |

|                  | ldle            |     | Data            | CR2            |

|                  | Idle            |     | Data            | CR1            |

|                  | Idle            |     | Data            | CR0            |

#### **XOP-Read Commands**

| DIN              | 7    | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7 | 6               | Į   | 5 4 | 1 :  | 3            | 2 | 1              | 0   | DOUT           |

|------------------|------|---|---|----|-----|---|---|---|-----|---|-----------------|-----|-----|------|--------------|---|----------------|-----|----------------|

| XOP-Read 1 Byte  |      |   | 1 | 1  | 1   | 0 | 0 | 0 |     |   |                 |     |     | ldle | <del>)</del> |   |                |     |                |

|                  |      | • |   | lo | lle | • |   |   |     | 1 | 1 0 0 0 0 0 0 1 |     |     |      |              | 1 | Identification |     |                |

|                  |      |   |   | Id | lle |   |   |   |     |   |                 |     |     | Dat  | a            |   |                |     | XR0            |

| DIN              | 7    | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7 | 6               | į   | 5 4 | 4 :  | 3            | 2 | 1              | 0   | DOUT           |

| XOP-Read 2 Bytes |      |   | 1 | 1  | 1   | 0 | 0 | 1 |     |   |                 |     |     | ldle | <del>)</del> |   |                |     |                |

|                  |      |   |   | lo | lle |   |   |   |     | 1 | 0               | (   | ) ( | ) (  | )            | 0 | 0              | 1   | Identification |

|                  | Idle |   |   |    |     |   |   |   |     |   |                 |     | Dat | а    |              |   |                | XR1 |                |

|                  |      |   |   | lc | lle |   |   |   |     |   |                 |     |     | Dat  | а            |   |                |     | XR0            |

| DIN              | 7    | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7 | 6               | į   | 5 4 | 4 :  | 3            | 2 | 1              | 0   | DOUT           |

| XOP-Read 3 Bytes |      |   | 1 | 1  | 1   | 0 | 1 | 0 |     |   |                 |     |     | ldle | )            |   |                |     |                |

|                  |      |   |   | lo | lle |   |   |   |     | 1 | 0               | (   | ) ( | ) (  | )            | 0 | 0              | 1   | Identification |

|                  |      |   |   | lc | lle |   |   |   |     |   |                 |     |     | Dat  | а            |   |                |     | XR2            |

|                  | Idle |   |   |    |     |   |   |   |     |   |                 | Dat | a   |      |              |   | XR1            |     |                |

|                  | Idle |   |   |    |     |   |   |   |     |   |                 |     |     | Dat  | a            |   |                |     | XR0            |

#### **COP-Read Commands**

| DIN | 765   | 4 3 2 1 | ∩ Rit 7 | 65432     | 1 0 DOUT |

|-----|-------|---------|---------|-----------|----------|

|     | 1 0 0 | T U Z I |         | 0 0 7 0 2 | 1 0 0001 |

|                  | <br>0 | <u> </u> |    | <u> </u> |  | U |

|------------------|-------|----------|----|----------|--|---|

| COP-Read 4 Bytes |       | 1        | 0  | 1        |  |   |

|                  |       |          | ld | lle      |  |   |

|                  |       |          | ld | lle      |  |   |

|                  |       |          | ld | lle      |  |   |

|                  |       |          | ld | lle      |  |   |

|                  |       |          | ld | lle      |  |   |

|   |                 |  | ld       | le       |  |  |                |  |

|---|-----------------|--|----------|----------|--|--|----------------|--|

| 1 | 1 0 0 0 0 0 0 1 |  |          |          |  |  | Identification |  |

|   |                 |  | Da       | Coeff. 3 |  |  |                |  |

|   |                 |  | Da       | Coeff. 2 |  |  |                |  |

|   |                 |  | Da       | Coeff. 1 |  |  |                |  |

|   |                 |  | Coeff. 0 |          |  |  |                |  |

DIN 7 6 5 4 3 2 1 0 Bit 7 6 5 4 3 2 1 0 DOUT

| COP-Read 8 Byte |

|-----------------|

|-----------------|

| • |      | ı | U  | O   |  |  |

|---|------|---|----|-----|--|--|

|   |      |   | ld | lle |  |  |

|   |      |   | ld | lle |  |  |

|   |      |   | ld | lle |  |  |

|   |      |   | ld | lle |  |  |

|   |      |   | ld | lle |  |  |

|   |      |   | ld | lle |  |  |

|   |      |   | ld | lle |  |  |

|   |      |   | ld | lle |  |  |

|   |      |   | ld | lle |  |  |

|   | <br> |   |    |     |  |  |

|   |   |   | ld       | le       |   |   |   |                |

|---|---|---|----------|----------|---|---|---|----------------|

| 1 | 0 | 0 | 0        | 0        | 0 | 0 | 1 | Identification |

|   |   |   | Coeff. 8 |          |   |   |   |                |

|   |   |   | Coeff. 7 |          |   |   |   |                |

|   |   |   | Da       | Coeff. 6 |   |   |   |                |

|   |   |   | Coeff. 5 |          |   |   |   |                |

|   |   |   | Da       | ata      |   |   |   | Coeff. 4       |

|   |   |   | Da       | ata      |   |   |   | Coeff. 3       |

|   |   |   | Da       | ata      |   |   |   | Coeff. 2       |

|   |   |   | Da       | ata      |   |   |   | Coeff. 1       |

# **Example of a Mixed Command**

| DIN | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | Ω | DOUT  |

|-----|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|-------|

|     | , | U | J |   | J | _ |   | U | וטו | • | U | J | _ | J | _ |   | U | וטטטו |

| SOP-Write 4 Bytes |      |  | 0 | 1  | 0   | 0 | 1 | 1 |  |  |  |  |  |

|-------------------|------|--|---|----|-----|---|---|---|--|--|--|--|--|

| CR3               |      |  |   | Da | ata |   |   |   |  |  |  |  |  |

| CR2               |      |  |   | Da | ata |   |   |   |  |  |  |  |  |

| CR1               | Data |  |   |    |     |   |   |   |  |  |  |  |  |

| CR0               |      |  |   | Da | ata |   |   |   |  |  |  |  |  |

| XOP-Write 2 Bytes |      |  | 0 | 1  | 1   | 0 | 0 | 1 |  |  |  |  |  |

| XR1               |      |  |   | Da | ata |   |   |   |  |  |  |  |  |

| XR0               |      |  |   | Da | ata |   |   |   |  |  |  |  |  |

| COP-Write 4 Bytes |      |  | 0 | 0  | 1   |   |   |   |  |  |  |  |  |

| Coeff. 3          |      |  |   | Da | ata |   |   |   |  |  |  |  |  |

| Coeff. 2          |      |  |   | Da | ata |   |   |   |  |  |  |  |  |

| Coeff. 1          |      |  |   | Da | ata |   |   |   |  |  |  |  |  |

| Coeff. 0          | Data |  |   |    |     |   |   |   |  |  |  |  |  |

| SOP-Read 3 Bytes  |      |  | 1 | 1  | 0   | 0 | 1 | 0 |  |  |  |  |  |

|                   |      |  |   | lo | lle |   |   |   |  |  |  |  |  |

|                   | Idle |  |   |    |     |   |   |   |  |  |  |  |  |

|                   | Idle |  |   |    |     |   |   |   |  |  |  |  |  |

|                   |      |  |   | lo | lle |   |   |   |  |  |  |  |  |

| COP-Read 4 Bytes  |      |  | 1 | 0  | 1   |   |   |   |  |  |  |  |  |

|                   |      |  |   | lo | lle |   |   |   |  |  |  |  |  |

|                   |      |  |   | lo | lle |   |   |   |  |  |  |  |  |

|                   |      |  |   | lo | lle |   |   |   |  |  |  |  |  |

|                   |      |  |   | lo | lle |   |   |   |  |  |  |  |  |

|                   |      |  |   | lo | lle |   |   |   |  |  |  |  |  |

| XOP-Read 1 Byte   |      |  | 1 | 1  | 1   | 0 | 0 | 0 |  |  |  |  |  |

|                   |      |  |   | lo | lle |   |   |   |  |  |  |  |  |

|                   |      |  |   | lo | lle |   |   |   |  |  |  |  |  |

| ļ                 |      |  |   |    |     |   |   |   |  |  |  |  |  |

| 7 0 0 4 0 2 1   | 0 0001           |

|-----------------|------------------|

| Idle            |                  |

| 1 0 0 0 0 0 0   | 1 Identification |

| Data            | CR2              |

| Data            | CR1              |

| Data            | CR0              |

| Idle            |                  |

| 1 0 0 0 0 0 0 0 | 1 Identification |

| Data            | Coeff. 3         |

| Data            | Coeff. 2         |

| Data            | Coeff. 1         |

| Data            | Coeff. 0         |

| Idle            |                  |

| 1 0 0 0 0 0 0 0 | 1 Identification |

| Data            | XR0              |

|                 |                  |

#### 3.3 SOP Command

To modify or evaluate the SICOFI-4- $\mu$ C status, the contents of up to 6 configuration registers CR0 .. CR7 may be transferred to or from the SICOFI-4- $\mu$ C. This is started by a SOP-Command (status operation command).

| Bit 7 | ( |

|-------|---|

| 3it 7 |   |

| AD2 | AD1 | RW | 1 | 0 | LSEL2 | LSEL1 | LSEL0 |

|-----|-----|----|---|---|-------|-------|-------|

|-----|-----|----|---|---|-------|-------|-------|

#### **AD** Address Information

| AD = 00 | SICOFI-4- $\mu$ C - channel 1 is addressed with this command |

|---------|--------------------------------------------------------------|

| AD = 01 | SICOFI-4- $\mu$ C - channel 2 is addressed with this command |

| AD = 10 | SICOFI-4- $\mu$ C - channel 3 is addressed with this command |

| AD = 11 | SICOFI-4- $\mu$ C - channel 4 is addressed with this command |

RW Read/Write Information: Enables reading from the SICOFI-4- $\mu$ C or writing information to the SICOFI-4- $\mu$ C

```

RW = 0 Write to SICOFI-4 \muC RW = 1 Read from SICOFI-4 \muC

```

LSEL Length select information (see also programming procedure)

This field identifies the number of subsequent data bytes

```

LSEL = 000 1 byte of data is following (CR0)

LSEL = 001 2 bytes of data are following (CR1, CR2)

LSEL = 010 3 bytes of data are following (CR2, CR1, CR0)

LSEL = 011 4 bytes of data are following (CR3, CR2, CR1, CR0)

LSEL = 100 5 bytes of data are following (CR4, CR3, CR2, CR1, CR0)

LSEL = 101 6 bytes of data are following (CR5, CR4, CR3, CR2, CR1, CR0)

```

All other codes are reserved for future use!

Note: If only one configuration register requires modification, for example CR5, this can be accomplished by setting LSEL = 101 and releasing pin CS after CR5 is written.

#### Programming the SICOFI®-4-μC

#### 3.3.1 CR0 Configuration Register 0

Configuration register CR0 defines the basic SICOFI-4- $\mu$ C settings, which are: enabling/disabling the programmable digital filters.

Bit

7

0

TH

IM/R1

FRX

FRR

AX

AR

TH-SEL

**TH** Enable TH- (Trans Hybrid Balancing) Filter

TH = 0: TH-filter disabled

TH = 1: TH-filter enabled

**IM/R1** Enable IM-(Impedance Matching) Filter and R1-Filter

IM/R1 = 0: IM-filter and R1-filter disabled IM/R1 = 1: IM-filter and R1-filter enabled

**FRX** Enable FRX (Frequency Response Transmit)-Filter

FRX = 0: FRX-filter disabled FRX = 1: FRX-filter enabled

FRR Enable FRR (Frequency Response Receive)-Filter

FRR = 0: FRR-filter disabled FRR = 1: FRR-filter enabled

**AX** Enable AX-(Amplification/Attenuation Transmit) Filter

AX = 0: AX-filter disabled AX = 1: AX-filter enabled

AR Enable AR-(Amplification/Attenuation Receive) Filter

AR = 0: AX-filter disabled AR = 1: AX-filter enabled

**TH-SEL** 2 bit field to select one of four programmed TH-filter coefficient sets

TH-Sel = 0 0: TH-filter coefficient set 1 is selected TH-Sel = 0 1: TH-filter coefficient set 2 is selected TH-Sel = 1 0: TH-filter coefficient set 3 is selected TH-Sel = 1 1: TH-filter coefficient set 4 is selected

#### Programming the SICOFI®-4-μC

#### 3.3.2 CR1 Configuration Register 1

Configuration register CR1 selects tone generator modes and other operation modes.

ETG2 Enable programmable tone generator 2 1)

ETG2 = 0: Programmable tone generator 2 is disabled

ETG2 = 1: Programmable tone generator 2 is enabled

**ETG1** Enable programmable tone generator 1

ETG1 = 0: Programmable tone generator 1 is disabled

ETG1 = 1: Programmable tone generator 1 is enabled

PTG2 User programmed frequency or fixed frequency is selected

PTG2 = 0: Fixed frequency for tone generator 2 is selected (1 kHz)

PTG2 = 1: Programmed frequency for tone generator 2 is selected

PTG1 User programmed frequency or fixed frequency is selected

PTG1 = 0: Fixed frequency for tone generator 1 is selected (1 kHz)

PTG1 = 1: Programmed frequency for tone generator 1 is selected

**LAW** PCM - law selection

LAW = 0: A-Law is selected

LAW = 1:  $\mu$ -Law ( $\mu$ 255 PCM) is selected

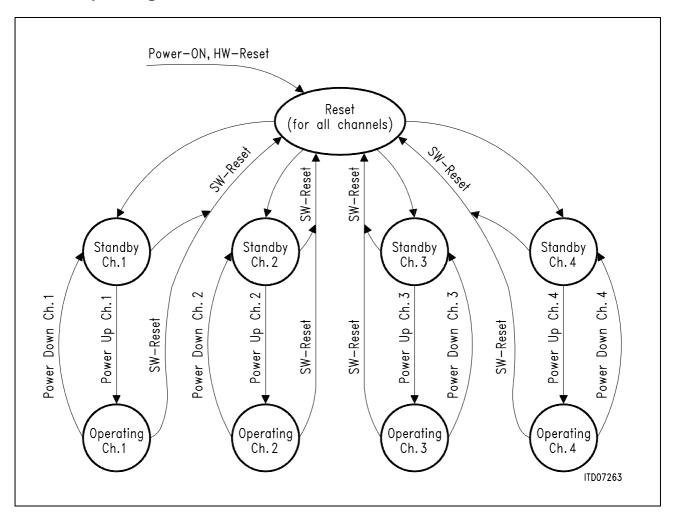

PU Power UP, sets the addressed channel to Power Up / Down

PU = 0: The addressed channel is set to Power Down (standby)

PU = 1: The addressed channel is set to Power Up (operating)

<sup>&</sup>lt;sup>1)</sup> Tone generator 2 is not available if Level Metering Function is enabled!

#### Programming the SICOFI®-4-μC

#### 3.3.3 CR2 Configuration Register 2

| Bit 7 |       |   |     |    | 0   |     |

|-------|-------|---|-----|----|-----|-----|

|       | COT/R | 0 | IDR | LM | LMR | V+T |

#### **COT/R** Selection of Cut off Transmit/Receive Paths

0 0 0: Normal Operation

0 0 1: COT16 Cut Off Transmit Path at 16 kHz (input of TH-Filter)

0 1 0: COT8 Cut Off Transmit Path at 8 kHz (input of

compression, output is zero for  $\mu$ -law, 1 LSB for

A-law)

1 0 1: COR4M Cut Off Receive Path at 4 MHz (POFI-output)

1 1 0: COR64 Cut Off Receive Path at 64 kHz (IM-filter input)

#### **IDR** Initialize Data RAM

IDR = 0: Normal operation is selected

IDR = 1: Contents of Data RAM is set to 0

(used for production test purposes)

#### **LM** Level Metering function 1)

LM = 0: Level metering function is disabled

LM = 1: Level metering function is enabled

#### **LMR** Result of Level Metering function (this bit can not be written)

LMR = 0: Level detected was lower than the reference

LMR = 1: Level detected was higher than the reference

#### **V+T** Add Voice signal and Tone Generator signal

V+T=0: Voice or Tone Generator is fed to the DAC

V+T = 1: Voice and Tone Generator Signals are added, and fed to the Digital to Analog Converter

A signal fed to  $A/\mu$ -Law compression via AX- and HPX-filters (from a digital loop, or externally via VIN), is rectified, and the power is measured. If the power exceeds a certain value, loaded to XR7, bit LMR is set to '1'. The power of the incoming signal can be adjusted by AX-filters.

<sup>1)</sup> Explanation of the level metering function:

Figure 11 'CUT OFF's' and Loops

#### Programming the SICOFI®-4-μC

#### 3.3.4 CR3 Configuration Register 3

| Bit 7 |            |     | 0   |       |       |

|-------|------------|-----|-----|-------|-------|

|       | Test-Loops | AGX | AGR | D-HPX | D-HPR |

Test-Loops 4 bit field for selection of Analog and Digital Loop Backs

| 0 0 0 0: |          | No loop back is selected (normal operation)                                          |

|----------|----------|--------------------------------------------------------------------------------------|

| 0 0 0 1: | ALB-PFI  | Analog loop back via PREFI-POFI is selected                                          |

| 0 0 1 1: | ALB-4M   | Analog loop back via 4 MHz is selected                                               |

| 0 1 0 0: | ALB-PCM  | Analog loop back via 8 kHz (PCM) is selected (attention: special settings necessary) |

| 0 1 0 1: | ALB-8K   | Analog loop back via 8 kHz (linear) is selected                                      |

| 1 0 0 0: | DLB-ANA  | Digital loop back via analog port is selected                                        |

| 1 0 0 1: | DLB-4M   | Digital loop back via 4 MHz is selected                                              |

| 1 1 0 0: | DLB-128K | Digital loop back via 128 kHz is selected                                            |

| 1 1 0 1: | DLB-64K  | Digital loop back via 64 kHz is selected                                             |

| 1 1 1 1: | DLB-PCM  | Digital loop back via PCM-registers is selected                                      |

#### **AGX** Analog gain in transmit direction

AGX = 0: Analog gain is disabled

AGX = 1: Analog gain is enabled (6.02 dB amplification)

#### **AGR** Analog gain in receive direction

AGR = 0: Analog gain is disabled

AGR = 1: Analog gain is enabled (6.02 dB attenuation)

#### **D-HPX** Disable highpass in transmit direction

D-HPX = 0: Transmit high pass is enabled D-HPX = 1: Transmit high pass is disabled<sup>1)</sup>

#### **D-HPR** Disable highpass in receive direction

D-HPR = 0: Receive high pass is enabled D-HPR = 1: Receive high pass is disabled<sup>2)</sup>

<sup>1)</sup> In this case the transmit-path signal is attenuated 0.06 dB

<sup>2)</sup> In this case the receive-path signal is attenuated 0.12 dB

### 3.3.5 CR4 Configuration Register 4

Configuration register CR4, sets the receiving time slot and the receiving PCM-highway.

Bit 7 0 R-WAY RS6 RS5 RS4 RS3 RS2 RS1 RS0

**R-WAY** Selects the PCM-Highway for the receiving of PCM-data

R-WAY = 0: PCM-Highway A is selected R-WAY = 1: PCM-Highway B is selected

**RS[6:0]** Selects the time slot (0 to 127) used for receiving the PCM-data

The time slot-number is binary coded.

0 0 0 0 0 0 0: Time slot 0 is selected 0 0 0 0 0 0 1: Time slot 1 is selected

....

1 1 1 1 1 0: Time slot 126 is selected

1 1 1 1 1 1 1: Time slot 127 is selected

### 3.3.6 CR5 Configuration Register 5

Configuration register CR5, sets the transmit time slot and the transmit PCM-highway.

X-WAY Selects the PCM-Highway for transmitting PCM-data

X-WAY = 0: PCM-Highway A is selected X-WAY = 1: PCM-Highway B is selected

**XS[6:0]** Selects the time slot (0 to 127) used for transmitting the PCM-data

The time slot-number is binary coded.

0 0 0 0 0 0 0: Time slot 0 is selected 0 0 0 0 0 0 1: Time slot 1 is selected

• • • •

1 1 1 1 1 1 0: Time slot 126 is selected 1 1 1 1 1 1 1: Time slot 127 is selected

## Programming the SICOFI®-4-μC

#### 3.4 COP Command

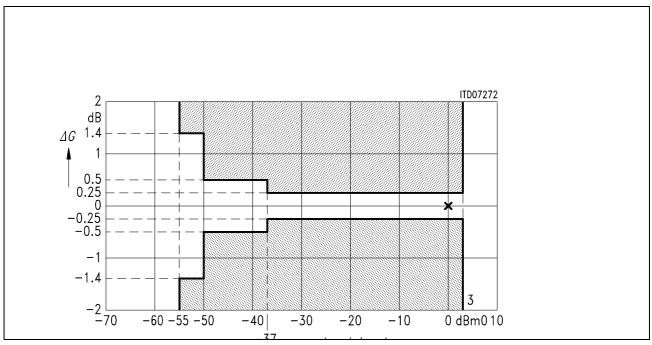

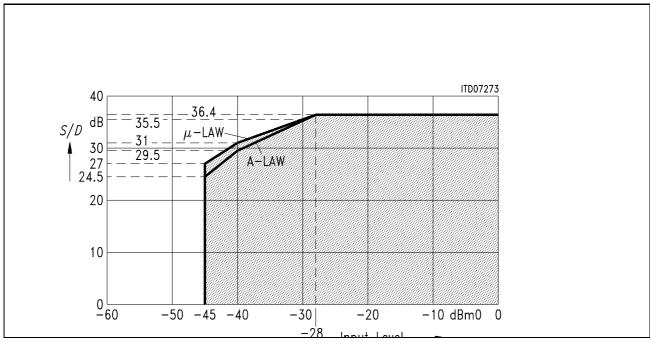

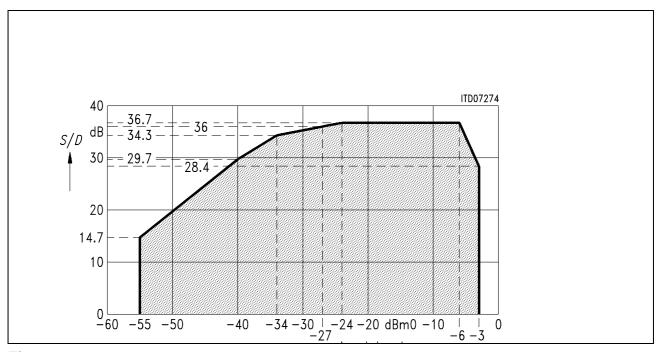

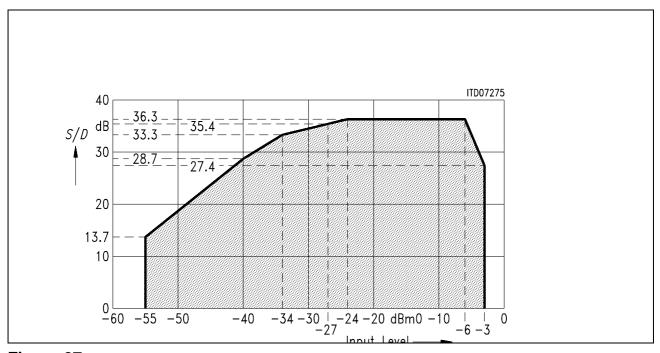

With a COP command coefficients for the programmable filters can be written to the SICOFI-4- $\mu$ C coefficient-RAM or read from the Coefficient-RAM via the  $\mu$ -Controller interface for verification