# 25供应商 C - SIERR

# 专业PCB打样工厂,24小时加急出货

# PM4325 **OCTLIU ST**

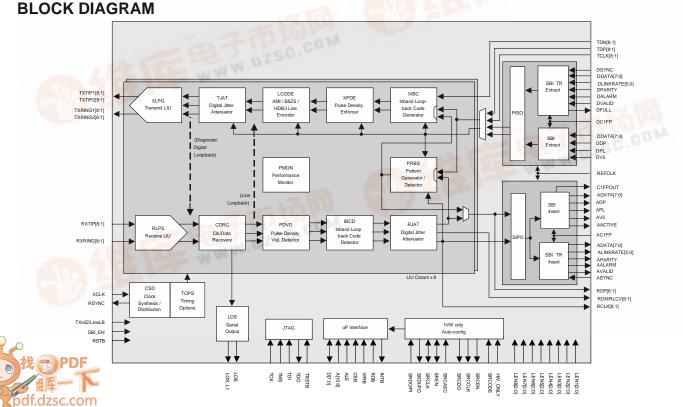

## Octal Short Haul T1/E1/J1 Low Latency Transport Line Interface

### FEATURES

- Monolithic device integrating eight T1/J1 or E1 short haul line interface units

- Software switchable between T1/J1 and E1 operation on a per-device basis

- Meets or exceeds T1/J1 and E1 short haul network access specifications including ANSI T1.102, T1.403, T1.408, AT&T TR 62411, ITU-T G.703, G.704 as well as ETSI 300-011, TBR 4, TBR 12, and TBR 13. In conjunction with the TEMAP 84 (PM5366), allows Add Drop Multiplexers and Terminal Multiplexers to meet GR253, GR496, and G.783.

- Optional encoding/decoding of B8ZS, HDB3, and AMI line codes.

- Provides receive equalization, clock recovery, and line performance monitoring.

- Provides transmit and receive jitter attenuation.

- Provides digitally programmable pulse templates.

- · Provides a selectable, per channel independent de-jittered T1 or E1 recovered clock for system timing and redundancy.

- Provides PRBS generators and detectors on each tributary for error testing at DS1 and E1 rates as recommended in ITU-T 0.151.

- Uses line rate system clock.

### SYSTEM INTERFACE

Supports transfer of transmitted single rail PCM and signaling data from 1.544 Mbit/s and 2.048 Mbit/s backplane buses or a SBI/SBI TR interface for low pin count interconnection of up to 11 OCTLIU STs to the high-density PM5366 TEMAP 84 T1/E1 framer.

### **RECEIVE SECTION**

- Supports T1/E1 signal reception for distances with up to 12dB of cable attenuation at nominal conditions using PIC 22 gauge cable emulation.

- Supports G.772 compliant non-intrusive protected monitoring points.

- Recovers clock and data using a digital phase locked loop for high jitter tolerance.

- Tolerates more than 0.4 UI peak-topeak high frequency jitter as required by AT&T TR 62411 and Bellcore TR-TSY-000170.

- · Outputs dual rail recovered line pulses, a single rail DS-1/E1 signal, or parallel data in SBI/SBI TR bus format.

- Performs B8ZS or AMI decoding when processing a bipolar DS-1 signal and HDB3 or AMI decoding when processing a bipolar E1 signal.

- Detects line code violations (LCVs), B8ZS/HDB3 line code signatures, and four (E1), eight (T1+B8ZS), or sixteen (T1 AMI) successive zeros.

- Provides a programmable depth FIFO buffer for jitter attenuation, rate conversion, and latency optimization in the receive path.

### TRANSMIT SECTION

Generates DSX-1 short haul pulses with programmable pulse shape compatible with AT&T, ANSI, and ITU requirements.

# PM4325 OCTLIU ST

## Octal Short Haul T1/E1/J1 Low Latency Transport Line Interface

- Generates E1 pulses compliant to G.703 recommendations.

- Provides line outputs that are current limited and may be tristated for protection or use in redundant applications.

- Provides a digital phase locked loop for generation of a low jitter transmit clock complying with all jitter attenuation, jitter transfer, and residual jitter specifications of AT&T TR 62411 and ETSI TBR 12 and TBR 13.

- Accepts either dual rail or single rail DS-1/E1 signals or parallel data from the SBI/SBI TR interface.

- Performs B8ZS or AMI encoding when processing a single rail or SBI/SBI TRsourced DS-1 signal and HDB3 or AMI encoding when processing a single rail or SBI/SBI TR-sourced E1 signal.

- Provides a programmable depth FIFO buffer for jitter attenuation, rate conversion, and latency optimization in the transmit path.

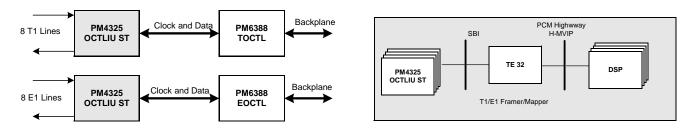

### TYPICAL APPLICATIONS T1/E1 FRAMER/TRANCEIVER

### GENERAL

- Provides an 8-bit microprocessor bus interface for configuration, control, and status monitoring.

- Provides a hardware-only (no microprocessor) mode in which configuration data is read from an SPI-compatible serial PROM. The PROM interface can be cascaded such that multiple OCTLIU ST devices can be configured simultaneously from a single PROM.

- Supports line and system side diagnostic loopbacks.

- Provides an IEEE 1149.1 (JTAG) compliant Test Access Port (TAP) and controller for boundary scan test.

- Implemented in low power 3.3 V tolerant 1.8/3.3 V CMOS technology.

- Available in a high-density 288-pin Tape-SBGA package with a -40 °C to +85 °C Industrial temperature operating range.

### APPLICATIONS

- Metro Optical Access Equipment.

- Edge Router Line Cards.

- Multi-service ATM Switch Line Cards.

- 3G Base Wireless Equipment.

- Digital Private Branch Exchanges (PBX).

- Digital Access Cross-Connect Systems (DACS) and Electronic DSX Cross-Connect Systems (EDSX).

### VOICE GATEWAY

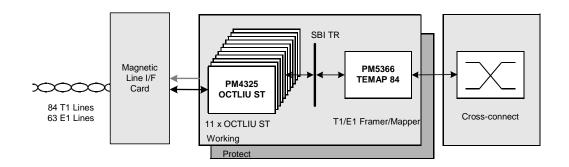

### SINGLE MAGNETIC LINE PROTECTON

Head Office: PMC-Sierra, Inc. 8555 Baxter Place Burnaby, B.C. V5A 4V7 Canada Tel: +1.604.415.6000 Fax: +1.604.415.6200 To order documentation, send email to: document@pmc-sierra.com or contact the head office, Attn: Document Coordinator

All product documentation is available on our web site at: http://www.pmc-sierra.com For corporate information, send email to: info@pmc-sierra.com PMC-2030527 (R2) © Copyright PMC-Sierra, Inc. 2003. All rights reserved. March 2003. For a complete list of PMC-Sierra's trademarks and registered trademarks, visit: http://www.pmc-sierra.com/legal/