PM5343 STXC

DATA SHEET

PMC-930303

ISSUE 6

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

# PM5343

# STXC

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER TELECOM STANDARD PRODUCT

# DATA SHEET

**ISSUE 6: SEPTEMBER 1998**

ISSUE 6

ISSUE 6

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

### **REVISION HISTORY**

| Issue No. | Issue Date         | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Issue 6   | September,<br>1998 | <ol> <li>Name of PECL input parameter changed from VPIA to VPSWG. Spec. revised to 550 mV to reflect characterization results</li> <li>Clarified usage of MBEB and CSB signals in test feature description section.</li> <li>Clarified conditions required for test mode 0 access to RIN and SCPI/SCPO signals</li> <li>Improved description of register 1AH.</li> <li>Pin descriptions for GRICLK/RICLK and GTICLK/TICLK in bit-serial mode was improved.</li> <li>Bit error rate tables added to meet ITU specs.</li> <li>IDDOP2 spec improved</li> <li>TIFP pin description corrected.</li> <li>Changed lead temperature max rating to 230 deg</li> <li>Changed all references from PQFP to more technically correct MQFP.</li> <li>Changed PECL pin types from Input and Output to PECL Input and PECL output.</li> </ol> |

| Issue 5   | September,<br>1997 | Re-formatted to fit new template.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

# **CONTENTS**

| 1  | FEAT  | URES                                | 1  |

|----|-------|-------------------------------------|----|

| 2  | APPL  | ICATIONS                            | 3  |

| 3  | REFE  | RENCES                              | 4  |

| 4  | APPL  | ICATION EXAMPLE                     | 5  |

| 5  | BLOC  | CK DIAGRAM                          | 6  |

| 6  | DESC  | CRIPTION                            | 7  |

| 7  | PIN D | DIAGRAM                             | 9  |

| 8  | PIN D | DESCRIPTION                         | 10 |

| 9  | FUNC  | CTIONAL DESCRIPTION                 | 36 |

|    | 9.1   | SERIAL TO PARALLEL CONVERTER        | 36 |

|    | 9.2   | RECEIVE SECTION OVERHEAD PROCESSOR  | 36 |

|    | 9.3   | RECEIVE LINE OVERHEAD PROCESSOR     | 37 |

|    | 9.4   | RECEIVE TRANSPORT OVERHEAD ACCESS   | 39 |

|    | 9.5   | RING CONTROL PORT                   | 39 |

|    | 9.6   | TRANSMIT TRANSPORT OVERHEAD ACCESS  | 40 |

|    | 9.7   | TRANSMIT LINE OVERHEAD PROCESSOR    | 40 |

|    | 9.8   | TRANSMIT SECTION OVERHEAD PROCESSOR | 41 |

|    | 9.9   | PARALLEL TO SERIAL CONVERTER        | 42 |

|    | 9.10  | RECEIVE SECTION TRACE BUFFER        | 42 |

|    | 9.11  | TRANSMIT SECTION TRACE BUFFER       | 43 |

|    | 9.12  | MICROPROCESSOR INTERFACE            | 43 |

| 10 | REGI  | STER DESCRIPTION                    | 44 |

|    |       |                                     |    |

ISSUE 6

| 11 | TEST FEATURES DESCRIPTION                          |

|----|----------------------------------------------------|

| 12 | FUNCTIONAL TIMING                                  |

| 13 | OPERATION152                                       |

|    | 13.1 BIT ERROR RATE MONITOR                        |

| 14 | ABSOLUTE MAXIMUM RATINGS155                        |

| 15 | D.C. CHARACTERISTICS                               |

| 16 | MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS161 |

| 17 | STXC TIMING CHARACTERISTICS                        |

|    | 17.1 INPUT TIMING                                  |

|    | 17.2 OUTPUT TIMING                                 |

| 18 | ORDERING AND THERMAL INFORMATION 181               |

| 19 | MECHANICAL INFORMATION182                          |

#### SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

## **LIST OF REGISTERS**

| ADDRESS 00H: MASTER CONFIGURATION             | 47 |

|-----------------------------------------------|----|

| ADDRESS 01H: MASTER CONTROL/ENABLE            | 50 |

| ADDRESS 02H: MASTER INTERRUPT STATUS          | 53 |

| ADDRESS 03H: MASTER RESET AND IDENTITY        | 55 |

| ADDRESS 04H: TLOP CONTROL                     | 56 |

| ADDRESS 05H: TLOP DIAGNOSTIC                  | 59 |

| ADDRESS 06H: TRANSMIT K1                      | 60 |

| ADDRESS 07H: TRANSMIT K2                      | 61 |

| ADDRESS 08H: RLOP CONTROL/STATUS              | 62 |

| ADDRESS 09H: RLOP INTERRUPT ENABLE AND STATUS | 64 |

| ADDRESS 0AH: B2 ERROR COUNT #1                | 66 |

| ADDRESS 0BH: B2 ERROR COUNT #2                | 66 |

| ADDRESS 0CH: B2 ERROR COUNT #3                | 66 |

| ADDRESS 0DH: REI ERROR COUNT #1               | 68 |

| ADDRESS 0EH: REI ERROR COUNT #2               | 68 |

| ADDRESS 0FH: REI ERROR COUNT #3               | 68 |

| ADDRESS 10H: RSOP CONTROL                     | 70 |

| ADDRESS 11H: RSOP INTERRUPT STATUS            | 72 |

| ADDRESS 12H: B1 ERROR COUNT #1                | 74 |

| ADDRESS 13H: B1 ERROR COUNT #2                | 74 |

| ADDRESS 14H: OUTPUT PORT                      | 75 |

| ADDRESS 15H: INPUT PORT INTERRUPT ENABLE      | 76 |

ISSUE 6

| ADDRESS 16H: MODE SELECT77                                     |

|----------------------------------------------------------------|

| ADDRESS 17H: RING CONTROL79                                    |

| REGISTER 18H: TSOP CONTROL82                                   |

| REGISTER 19H: TSOP DIAGNOSTIC85                                |

| REGISTER 1AH: TRANSMIT Z186                                    |

| REGISTER 1BH: RECEIVE Z1 (ENH=0)                               |

| REGISTER 1BH: TRANSMIT Z0 (ENH=1)                              |

| ADDRESS 1DH: RECEIVE K1 (ENH=0)89                              |

| ADDRESS 1DH: AIS CONTROL (ENH=1)90                             |

| ADDRESS 1EH: RECEIVE K2 (ENH=0)                                |

| ADDRESS 1EH: RDI CONTROL (ENH=1)93                             |

| ADDRESS 1FH: CONFIGURATION INPUT PORT STATUS/VALUE95           |

| REGISTER 20H: SECTION TRACE CONTROL (ENH=0)97                  |

| REGISTER 20H: RASE INTERRUPT ENABLE (ENH=1)                    |

| REGISTER 21H: SECTION TRACE STATUS (ENH=0):101                 |

| REGISTER 21H: RASE INTERRUPT STATUS (ENH=1)103                 |

| REGISTER 22H: SECTION TRACE INDIRECT ADDRESS REGISTER (ENH=0): |

| REGISTER 22H: RASE CONFIGURATION/CONTROL REGISTER (ENH=1):     |

| REGISTER 23H: SECTION TRACE INDIRECT DATA REGISTER (ENH=0)     |

| REGISTER 23H: RASE SF ACCUMULATION PERIOD (LSB, ENH=1) 109     |

| REGISTER 24H: RASE SF ACCUMULATION PERIOD (ENH=1)109           |

| REGISTER 25H: RASE SF ACCUMULATION PERIOD (MSB, ENH=1) 109     |

ISSUE 6

| REGISTER 26H: RASE SF SATURATION THRESHOLD (LSB, ENH=1)  | 11 |

|----------------------------------------------------------|----|

| REGISTER 27H: RASE SF SATURATION THRESHOLD (MSB, ENH=1)1 | 11 |

| REGISTER 28H: SECTION TRACE AIS INSERTION (ENH=0)1       | 12 |

| REGISTER 28H: RASE SF DECLARING THRESHOLD (LSB, ENH=1) 1 | 13 |

| REGISTER 29H: RASE SF DECLARING THRESHOLD (MSB, ENH=1)1  | 13 |

| REGISTER 2AH: RASE SF CLEARING THRESHOLD (LSB, ENH=1) 1  | 14 |

| REGISTER 2BH: RASE SF CLEARING THRESHOLD (MSB, ENH=1) 1  | 14 |

| REGISTER 2CH: RASE SD ACCUMULATION PERIOD (LSB, ENH=1)1  | 15 |

| REGISTER 2DH: RASE SD ACCUMULATION PERIOD (ENH=1)1       | 15 |

| REGISTER 2EH: RASE SD ACCUMULATION PERIOD (MSB, ENH=1)1  | 15 |

| REGISTER 2FH: RASE SD SATURATION THRESHOLD (LSB, ENH=1)1 | 17 |

| REGISTER 30H: RASE SD SATURATION THRESHOLD (MSB, ENH=1)  | 17 |

| REGISTER 31H: RASE SD DECLARING THRESHOLD (LSB, ENH=1)1  | 18 |

| REGISTER 32H: RASE SD DECLARING THRESHOLD (MSB, ENH=1)1  | 18 |

| REGISTER 33H: RASE SD CLEARING THRESHOLD (LSB, ENH=1) 1  | 19 |

| REGISTER 34H: RASE SD CLEARING THRESHOLD (MSB, ENH=1) 1  | 19 |

| ADDRESS 35H: RECEIVE K1 (ENH=1)1                         | 20 |

| ADDRESS 36H: RECEIVE K2 (ENH=1)1                         | 21 |

| REGISTER 37H: RECEIVE Z1 (ENH=1)1                        | 22 |

ISSUE 6

| REGISTER 38H: SECTION TRACE CONTROL (ENH=1):                     | 123 |

|------------------------------------------------------------------|-----|

| REGISTER 39H: SECTION TRACE STATUS (ENH=1):                      | 125 |

| REGISTER 3AH: SECTION TRACE INDIRECT ADDRESS<br>REGISTER (ENH=1) | 127 |

| REGISTER 3BH: SECTION TRACE INDIRECT DATA REGISTER (ENH=1)       | 128 |

| ADDRESS 43H: MASTER TEST                                         | 131 |

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

# **LIST OF FIGURES**

| FIGURE 1 - STS-3/STM-1 LINE INTERFACE                                   | 5 |

|-------------------------------------------------------------------------|---|

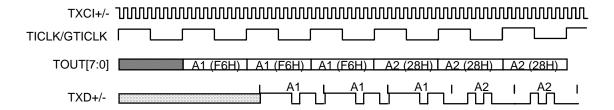

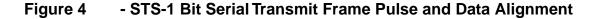

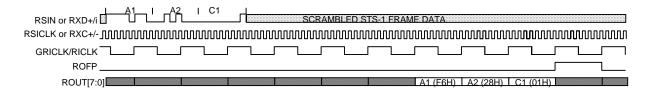

| FIGURE 2 - STS-3 BIT SERIAL TRANSMIT FRAME PATTERN AND DATA ALIGNMENT13 | 5 |

| FIGURE 3 - STS-3 BYTE SERIAL TRANSMIT FRAME PULSE AND DATA ALIGNMENT    | 5 |

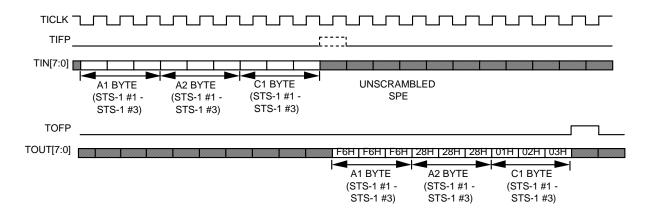

| FIGURE 4 - STS-1 BIT SERIAL TRANSMIT FRAME PULSE AND DATA ALIGNMENT     | 6 |

| FIGURE 5 - STS-1 BYTE SERIAL TRANSMIT FRAME PULSE AND DATA ALIGNMENT    | 6 |

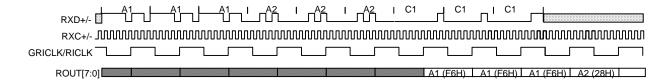

| FIGURE 6 - STS-3 BIT SERIAL RECEIVE FRAME PATTERN AND DATA ALIGNMENT    | 7 |

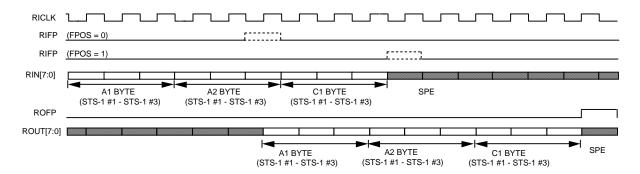

| FIGURE 7 - STS-3 BYTE SERIAL RECEIVE FRAME PULSE AND DATA ALIGNMENT     | 7 |

| FIGURE 8 - STS-1 BIT SERIAL RECEIVE FRAME PULSE AND DATA ALIGNMENT      | 8 |

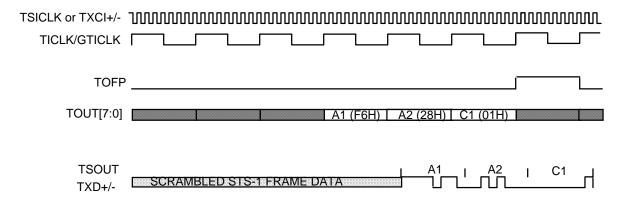

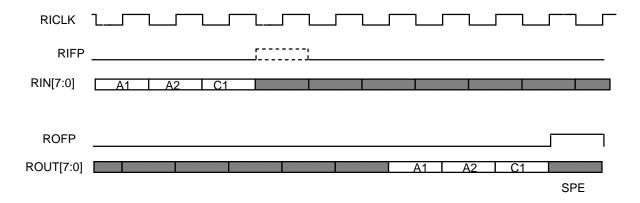

| FIGURE 9 - STS-1 BYTE SERIAL RECEIVE FRAME PULSE AND DATA ALIGNMENT     | 8 |

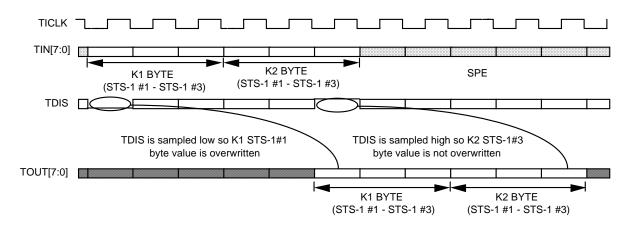

| FIGURE 10-TRANSPORT OVERHEAD OVERWRITE ENABLE AND DISABLE 139           |   |

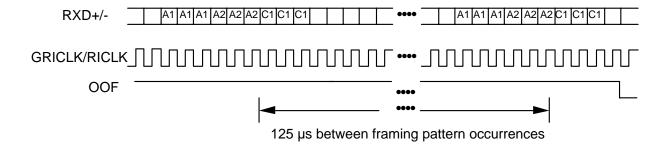

| FIGURE 11- IN FRAME DECLARATION (BIT SERIAL INTERFACE, RSER=1) 139      |   |

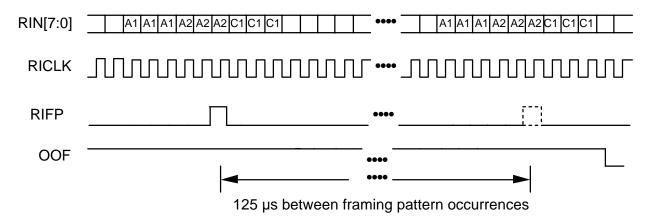

| FIGURE 12- IN FRAME DECLARATION (BYTE SERIAL INTERFACE, RSER=0) 140     |   |

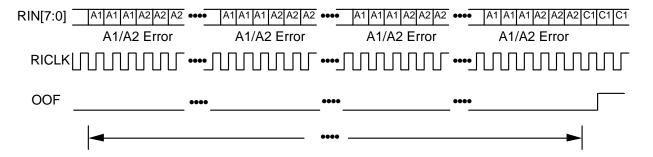

| FIGURE 13- OUT OF FRAME DECLARATION14                                   | 1 |

| FIGURE 14- LOSS OF SIGNAL DECLARATION/REMOVAL14                         | 1 |

| FIGURE 15- LOSS OF FRAME DECLARATION/REMOVAL 14:                        | 2 |

| FIGURE 16- LINE AIS AND LINE RDI DECLARATION/REMOVAL 14:                | 2 |

ISSUE 6

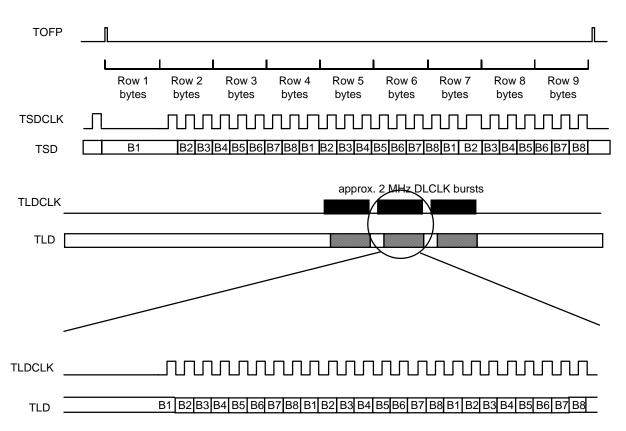

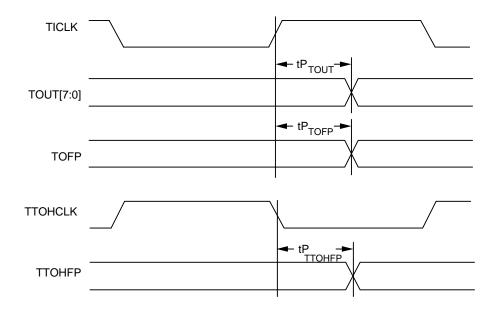

| FIGURE 17- TRANSMIT OVERHEAD CLOCK AND DATA ALIGNMENT                   | 143   |

|-------------------------------------------------------------------------|-------|

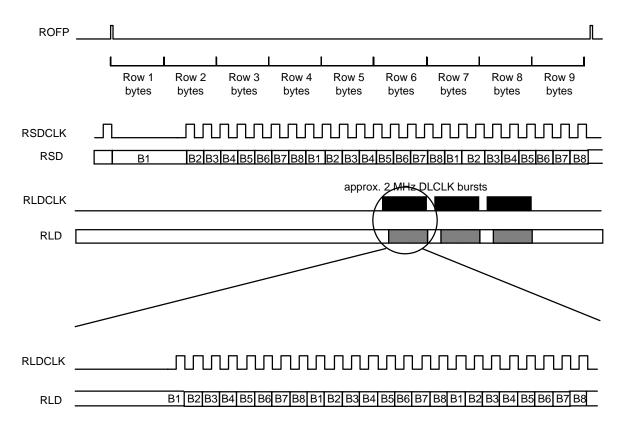

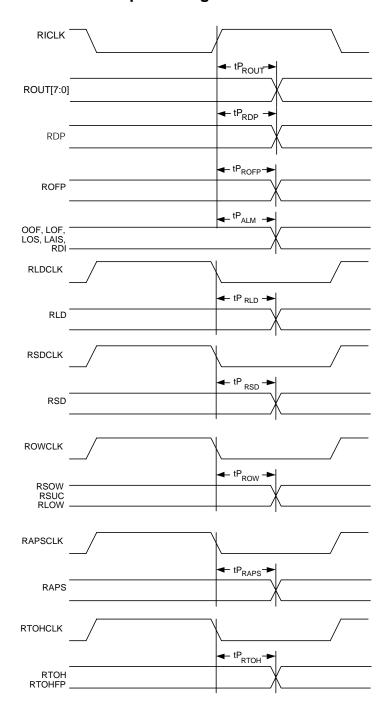

| FIGURE 18- RECEIVE OVERHEAD CLOCK AND DATA ALIGNMENT                    | 144   |

| FIGURE 19- TRANSMIT DATA LINK CLOCK AND DATA ALIGNMENT                  | 145   |

| FIGURE 20- RECEIVE DATA LINK CLOCK AND DATA ALIGNMENT                   | 146   |

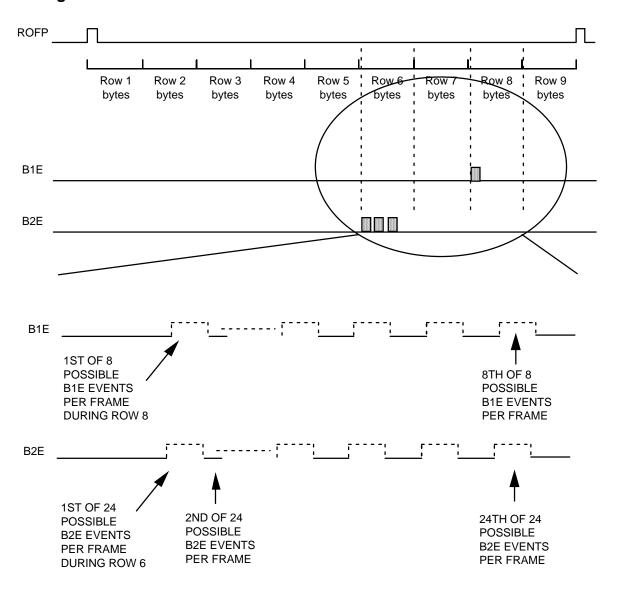

| FIGURE 21- B1 AND B2 ERROR EVENT OCCURRENCE                             | 147   |

| FIGURE 22- TRANSPORT OVERHEAD EXTRACTION                                | 148   |

| FIGURE 23- TRANSPORT OVERHEAD INSERTION                                 | 149   |

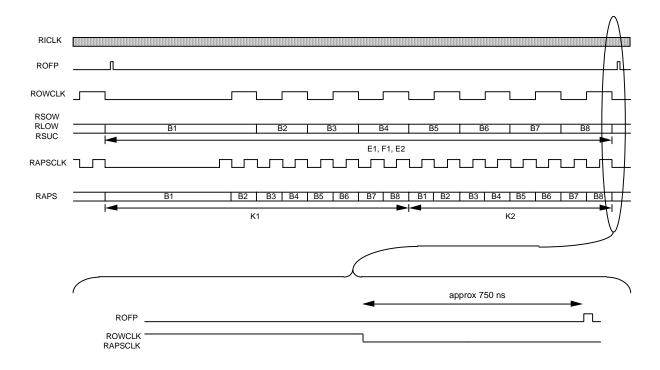

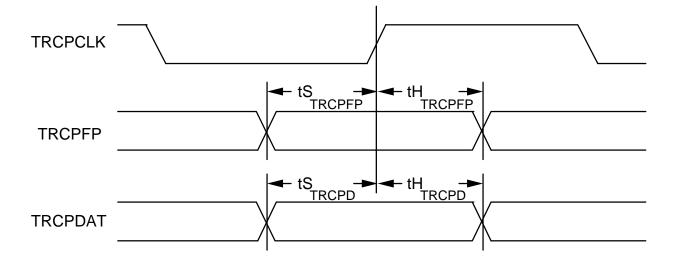

| FIGURE 24- TRANSMIT RING CONTROL PORT                                   | 150   |

| FIGURE 25- RECEIVE RING CONTROL PORT                                    | 151   |

| FIGURE 26- PECL OUTPUT LOW VOLTAGE                                      | 159   |

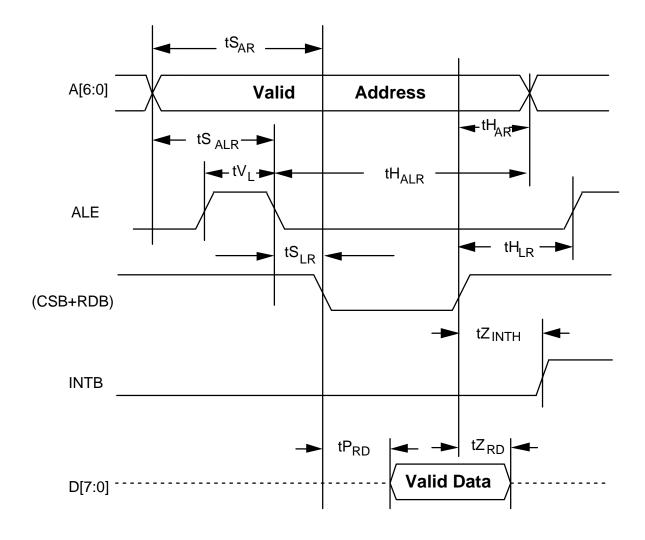

| FIGURE 27- MICROPROCESSOR INTERFACE READ ACCESS TIMING (INTEL MODE)     | 162   |

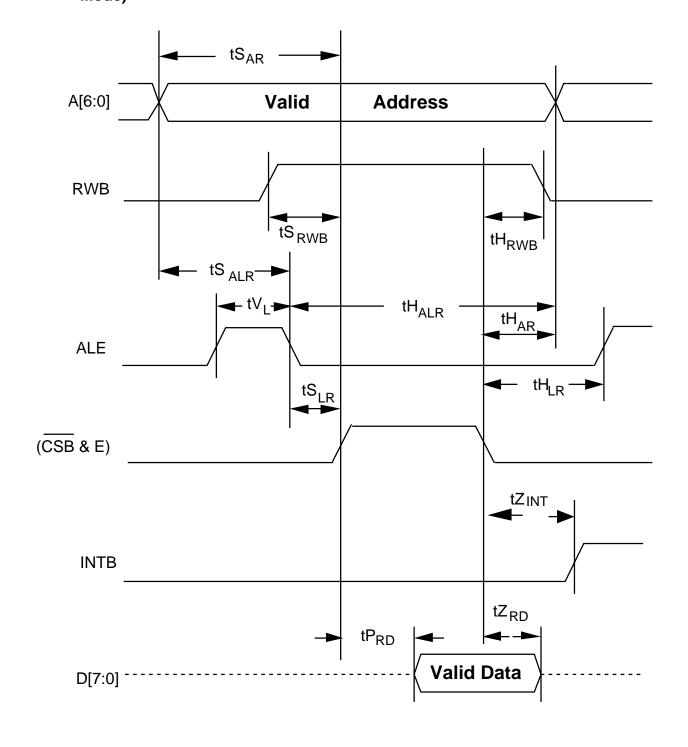

| FIGURE 28- MICROPROCESSOR INTERFACE READ ACCESS TIMING (MOTOROLA MODE)  | . 163 |

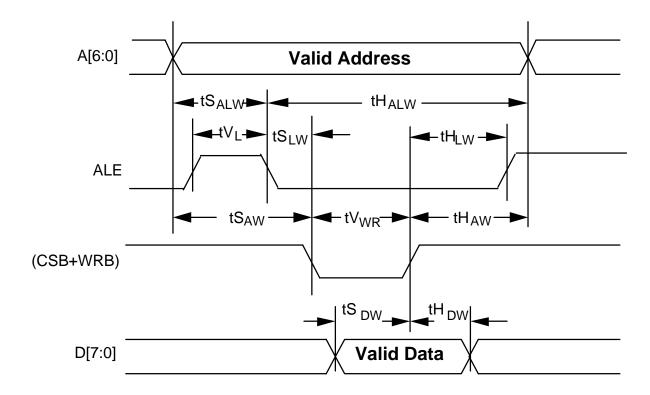

| FIGURE 29- MICROPROCESSOR INTERFACE WRITE ACCESS TIMING (INTEL MODE)    | . 166 |

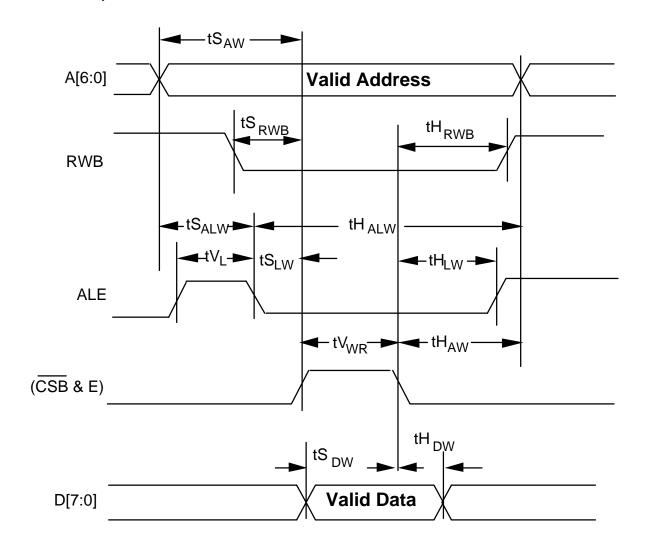

| FIGURE 30- MICROPROCESSOR INTERFACE WRITE ACCESS TIMING (MOTOROLA MODE) | . 167 |

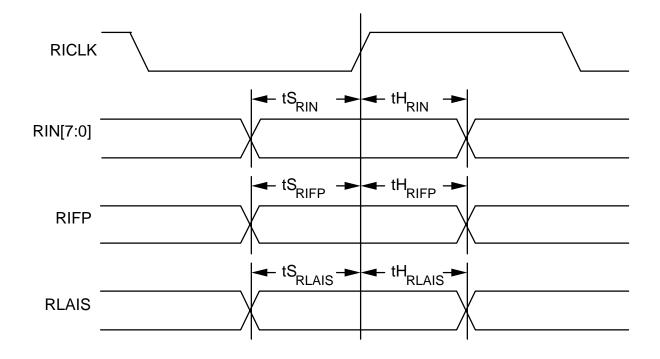

| FIGURE 31- RECEIVE INPUT TIMING                                         | . 170 |

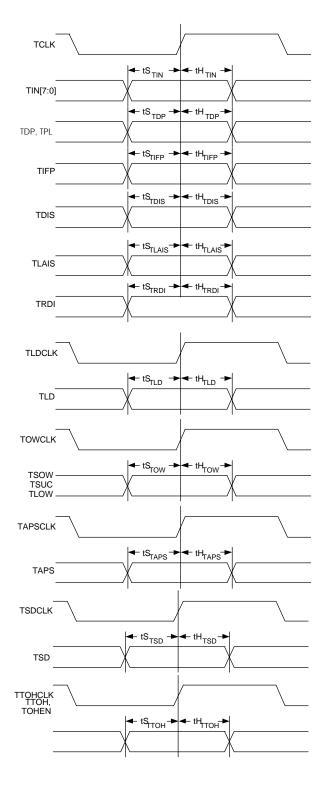

| FIGURE 32- TRANSMIT INPUT                                               | .172  |

| FIGURE 33- STS-3 BIT SERIAL INPUT                                       | 173   |

| FIGURE 34- STS-1 INPUT                                                  | 174   |

| FIGURE 35- TRANSMIT RING CONTROL PORT INPUT                             | 175   |

| FIGURE 36- RECEIVE OUTPUT TIMING                                        | . 177 |

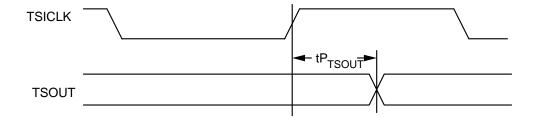

| FIGURE 37- TRANSMIT OUTPUT TIMING                                       | 178   |

ISSUE 6

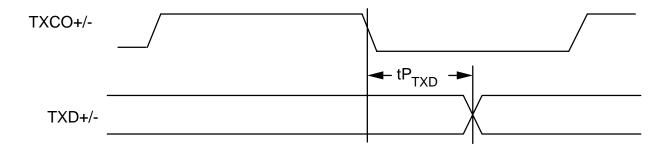

| FIGURE 38- STS-3 BIT SERIAL OUTPUT TIMING                              | . 179 |

|------------------------------------------------------------------------|-------|

| FIGURE 39- STS-1 OUTPUT TIMING                                         | . 179 |

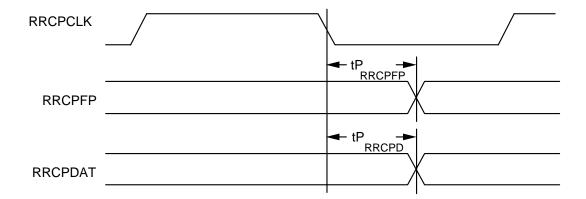

| FIGURE 40- RING CONTROL PORT OUTPUT                                    | . 180 |

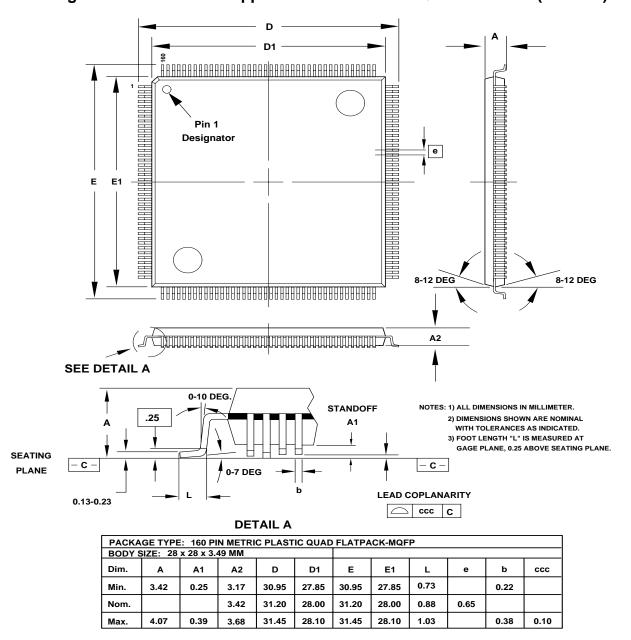

| FIGURE 41 - 160 PIN COPPER LEADFRAME METRIC QUAD FLAT PACK (R SUFFIX): | . 182 |

#### SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

# **LIST OF TABLES**

| TABLE 1             | - NORMAL MODE REGISTER MEMORY MAP4                          | 14         |

|---------------------|-------------------------------------------------------------|------------|

| TABLE 2             | - TEST MODE REGISTER MEMORY MAP12                           | 29         |

| TABLE 3             | - TEST MODE 0 INPUT OBSERVATION                             | 32         |

| TABLE 4             | - TEST MODE 0 OUTPUT CONTROL                                | 33         |

| TABLE 5             | - RASE-BERM CONFIGURATION FOR SDH STM-015                   | 53         |

| TABLE 6             | - RASE-BERM CONFIGURATION FOR SDH STM-115                   | 53         |

| TABLE 7             | - RASE-BERM CONFIGURATION FOR SONET STS-115                 | 54         |

| TABLE 8             | - RASE-BERM CONFIGURATION FOR SONET STS-315                 | 54         |

| TABLE 9             | - STXC ABSOLUTE MAXIMUM RATINGS15                           | 55         |

| TABLE 10            | - STXC D.C. CHARACTERISTICS                                 | 56         |

|                     | - MICROPROCESSOR INTERFACE READ ACCESS<br>27, FIGURE 28)16  | 31         |

|                     | - MICROPROCESSOR INTERFACE WRITE ACCESS<br>29, FIGURE 30)16 | 35         |

| TABLE 13            | - RECEIVE INPUT (FIGURE 31)                                 | 39         |

| TABLE 14            | - TRANSMIT INPUT (FIGURE 32)17                              | 70         |

| TABLE 15            | - STS-3 BIT SERIAL INPUT (FIGURE 33)                        | 73         |

| TABLE 16            | - STS-1 INPUT (FIGURE 34)17                                 | 74         |

| TABLE 17<br>35) 175 | - TRANSMIT RING CONTROL PORT INPUT (FIGURE                  |            |

| TABLE 18            | - RECEIVE OUTPUT TIMING (FIGURE 36)17                       | 76         |

| TABLE 19            | - TRANSMIT OUTPUT TIMING (FIGURE 37)                        | <b>7</b> 8 |

| TABLE 20            | - STS-3 BIT SERIAL OUTPUT (FIGURE 38)                       | 79         |

ISSUE 6

| TABLE 21            | - STS-1 OUTPUT (FIGURE 39)                 | 179 |

|---------------------|--------------------------------------------|-----|

| TABLE 22<br>40) 180 | - RECEIVE RING CONTROL PORT OUTPUT (FIGURE |     |

| TABLE 23            | - STXC ORDERING INFORMATION                | 181 |

| TABLE 24            | - STXC THERMAL INFORMATION                 | 181 |

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

### 1 FEATURES

- Monolithic SONET/SDH Transport Overhead Terminating Transceiver for use in STS-1, STS-3 or STM-1 interface applications, operating at serial interface speeds of up to 155.52 Mbit/s.

- Provides termination for SONET Section and Line, and SDH Regenerator Section and Multiplexer Section transport overhead.

- Companion to the PM5344 SPTX SONET/SDH Path Terminating Transceiver.

- Operates in STS-1 and STS-3 bit-serial (PECL/TTL I/O) and byte-serial (TTL I/O) modes. Provides independent control of the transmit and receive operating modes for asymmetrical bandwidth applications.

- Frames to the STS-1 or STS-3 (STM-1) receive stream and inserts the framing bytes (A1, A2) and the STS identification bytes (J0) into the transmit stream; Descrambles the receive stream and scrambles the transmit stream.

- Calculates and compares the bit interleaved parity error detection codes (B1, B2) for the receive stream and calculates and inserts B1 and B2 in the transmit stream.

- Accumulates near end errors (B1, B2) and far end errors (M1) and inserts line remote error indications (REI) into the Z2 growth byte based on received B2 errors.

- Detects signal degrade (SD) and signal fail (SF) threshold crossing alarms based on received B2 errors.

- Optionally inserts the line BIP-8 error detection code into each of the constituent STS-1s (B2 bytes) of the transmit STS-1/3 stream.

- Extracts and serializes the order wire channels (E1, E2), the data communication channels (D1-D3, D4-D12) and the section user channel (F1) from the receive stream, and inserts the corresponding signals into the transmit stream.

- Extracts and serializes the automatic protection switch (APS) channel (K1, K2) bytes, filtering and extracting them into internal registers. Inserts the APS channel into the transmit stream.

ISSUE 6

- Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line remote defect indication (RDI), line alarm indication signal (AIS), and protection switching byte failure alarms.

- Inserts and extracts a 64 byte or 16 byte section trace (J0) message using an internal register bank. Detects an unstable section trace message or mismatch with an expected message, and inserts Line AIS upon either of these conditions.

- Inserts RDI and AIS in the transmit stream.

- Provides loss of signal insertion, framing pattern error insertion, and coding violation insertion (B1 and B2) for diagnostic purposes. B1 and B2 errors can also be generated "on-the-fly" using an error insertion mask.

- Provides a transmit and receive ring control port, allowing alarm and maintenance signal control and status to be passed between mate STXCs for ring-based add drop multiplexer applications.

- Low power +5 Volt 0.8 micron CMOS. Device has PECL and TTL compatible inputs and outputs.

- 160 pin copper leadframe MQFP package. Supports Industrial Temperature Range (-40°C to 85°C) operation.

ISSUE 6

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

## **2** APPLICATIONS

- OC-N Regenerators

- OC-N to OC-M multiplexers

- SONET/SDH add drop multiplexers

- SONET/SDH terminal multiplexers

- Broadband ISDN user network interfaces

- SONET/SDH test equipment

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

### 3 REFERENCES

- 1. American National Standard for Telecommunications Digital Hierarchy Optical Interface Rates and Formats Specification, ANSI T1.105-1991.

- 2. Committee T1 Contribution, "Draft of T1.105 SONET Rates and Formats", T1X1.5/94-033R2-1994.

- 3. ITU, Recommendation G.707 "Network Node Interface For The Synchronous Digital Hierarchy", 1996.

- American National Standard for Telecommunications Digital Hierarchy -Optical Interface Rates and Formats Specification - Supplement, ANSI T1.105a-1991.

- 5. Bell Communications Research SONET Transport Systems: Common Generic Criteria, GR-253-CORE Issue 2, December, 1995.

- 10. ETSI DE/TM1015, "Generic Functional Requirement for SDH Transmission Equipment", Version 0.4, February 1993.

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

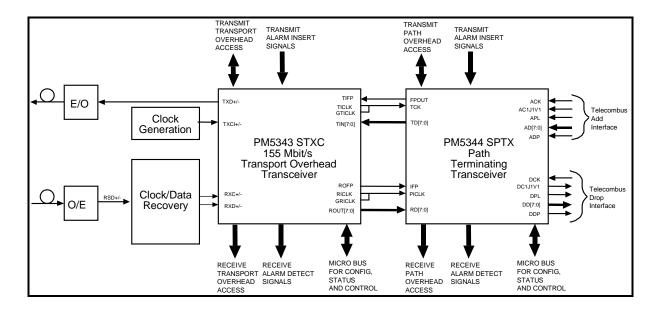

### 4 APPLICATION EXAMPLE

The STXC is typically used to implement a portion of an STS-3/STM-1 line Interface. The STXC may find application in many different types of SONET/SDH network elements including switches, terminal multiplexers, and add-drop multiplexers. In such applications, the STXC typically interfaces on its line side with a clock and data recovery device (for the receiver) and a physical media device such as a laser (for the transmitter). The system side interfaces directly to the PM5344 SONET/SDH Path Terminating Transceiver (SPTX) where pointer processing and path overhead termination are performed for an STS-3/STM-1 stream. The initial configuration and ongoing control and monitoring of the STXC are normally provided via a generic microprocessor interface.

Figure 1 - STS-3/STM-1 Line Interface

ISSUE 6

ISSUE 6

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

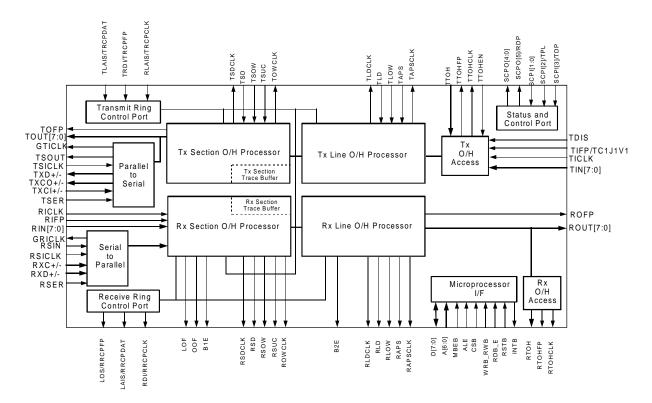

### 5 BLOCK DIAGRAM

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

### 6 DESCRIPTION

The PM5343 SONET/SDH 155 Mbit/s Transport Overhead Terminating Transceiver (STXC) processes the transport overhead (section overhead) of STS-1, and STS-3 (STM-1) streams at 51.84 Mbit/s and 155.52 Mbit/s. The STXC implements significant functions for a SONET/SDH compliant line interface.

The STXC receives SONET/SDH frames via a bit serial or byte serial interface and processes section (regenerator section) and line (multiplexer section) overhead. It performs framing (A1, A2), descrambling, detects alarm conditions, and monitors section and line path bit interleaved parity (B1, B2), accumulating error counts at each level for performance monitoring purposes. B2 errors are also monitored to detect signal fail and signal degrade threshold crossing alarms. Line remote error indications (M1) are also accumulated. A 16 or 64 byte section trace (J0) message may be buffered and compared against an expected message.

The STXC also provides convenient access to all transport overhead bytes, which are extracted and serialized on lower rate interfaces, allowing additional external processing of overhead.

The STXC transmits SONET/SDH frames, via a bit serial or a byte serial interface, and formats section and line overhead appropriately. It performs framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates section and line bit interleaved parity (B1, B2) as required to allow performance monitoring at the far end. Line remote error indications (M1) are optionally inserted. A 16 or 64 byte section trace (J0) message may be inserted.

The STXC also provides convenient access to all transport overhead bytes, which are optionally inserted from lower rate serial interfaces, allowing external sourcing of overhead. The STXC also supports the insertion of a large variety of errors into the transmit stream, such as framing pattern errors and bit interleaved parity errors, which are useful for system diagnostics and tester applications.

Ring control ports provide the ability to pass control and status information between mate transceivers.

The transmitter and receiver are independently configurable to allow for asymmetric interfaces. The STXC is configured, controlled and monitored via a generic 8-bit microprocessor bus interface.

ISSUE 6

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

The STXC is implemented in low power, +5 Volt, CMOS technology. It has TTL and pseudo ECL (PECL) compatible inputs and outputs and is packaged in a 160 pin MQFP package.

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

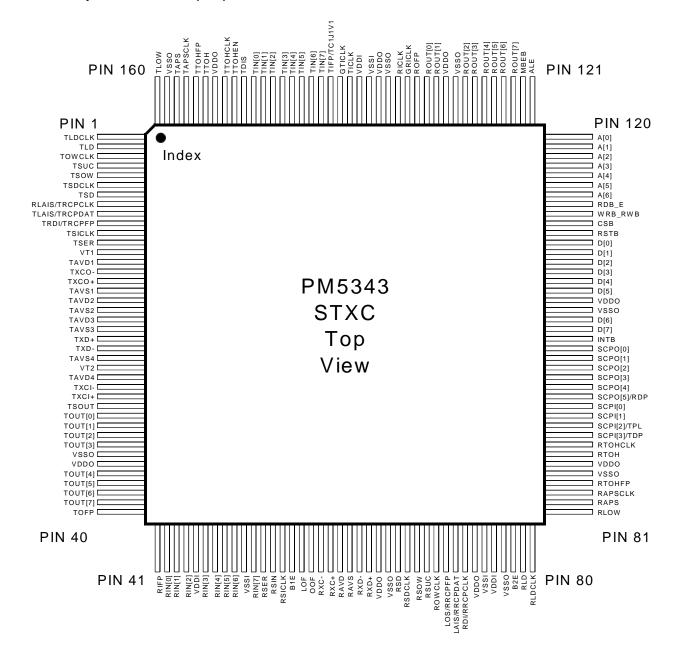

### 7 PIN DIAGRAM

The STXC is available in a 160 pin MQFP package having a body size of 28 mm by 28 mm and a pin pitch of 0.65 mm.

ISSUE 6

SONET/SDH TRANSPORT OVERHEAD TRANSCEIVER

# **8 PIN DESCRIPTION**

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSER     | Input    | 52         | The receive serial input (RSER) selects the receive line interface. RSER is tied high to select the bit serial interface on PECL pins RXC+, RXC-, RXD+, and RXD A TTL interface is also supported in STS-1 mode on pins RSIN and RSICLK. RSER is tied low to select the byte serial interface (on pins RICLK, RIN[7:0], and RIFP).                                                                         |

| RICLK/   | Input    | 135        | The receive incoming clock (RICLK) provides timing for processing the byte serial receive stream, RIN[7:0]. RICLK is nominally a 6.48 MHz (STS-1), or 19.44 MHz (STS-3/STM-1) 50% duty cycle clock, depending on the selected operating mode. RIN[7:0], and RIFP are sampled on the rising edge of RICLK. RICLK must be externally shorted directly to GRICLK when processing a bit serial receive stream. |

| RVCLK    |          |            | The receive vector clock (RVCLK) is used during STXC production test to verify internal functionality.                                                                                                                                                                                                                                                                                                     |

| RIN[7]   | Input    | 51         | The receive incoming stream (RIN[7:0]) carries                                                                                                                                                                                                                                                                                                                                                             |

| RIN[6]   | Input    | 49         | the scrambled STS-1 or STS-3/STM-1 stream in byte serial format. RIN[7] is the most                                                                                                                                                                                                                                                                                                                        |

| RIN[5]   | Input    | 48         | significant bit (corresponding to bit 1 of each                                                                                                                                                                                                                                                                                                                                                            |

| RIN[4]   | Input    | 47         | serial PCM word, the first bit transmitted).                                                                                                                                                                                                                                                                                                                                                               |

| RIN[3]   | Input    | 46         | RIN[0] is the least significant bit (corresponding to bit 8 of each serial PCM word, the last bit                                                                                                                                                                                                                                                                                                          |

| RIN[2]   | Input    | 44         | transmitted). RIN[7:0] is sampled on the rising                                                                                                                                                                                                                                                                                                                                                            |

| RIN[1]   | Input    | 43         | edge of RICLK.                                                                                                                                                                                                                                                                                                                                                                                             |

| RIN[0]   | Input    | 42         |                                                                                                                                                                                                                                                                                                                                                                                                            |

ISSUE 6

| Pin Name     | Pin Type      | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RIFP         | Input         | 41         | The active high receive incoming framing position (RIFP) signal indicates when the first byte of the synchronous payload envelope is available on the RIN[7:0] inputs. RIFP is sampled on the rising edge of RICLK.                                                                                                                                                                                                  |

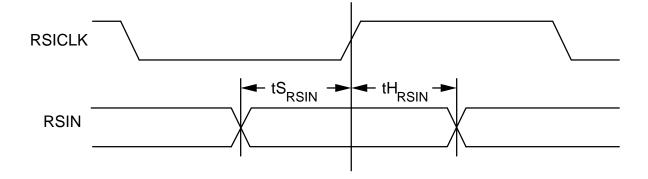

| RSIN         | Input         | 53         | The receive incoming serial stream (RSIN) contains the TTL compatible 51.84 Mbit/s receive STS-1 stream. RSIN is sampled on the rising edge of RSICLK. The RSIN input has an integral pull down resistor. The RXD+/- inputs may also carry the receive STS-1 stream.                                                                                                                                                 |

| RSICLK       | Input         | 54         | The receive serial incoming clock (RSICLK) provides timing for processing the bit serial receive stream, RSIN when the TTL bit serial STS-1 mode is selected. RSICLK is nominally a 51.84 MHz, 50% duty cycle clock. RSIN is sampled on the rising edge of RSICLK. RSICLK is divided by eight to produce GRICLK when the TTL bit serial STS-1 mode is selected. The RSICLK input has an integral pull down resistor. |

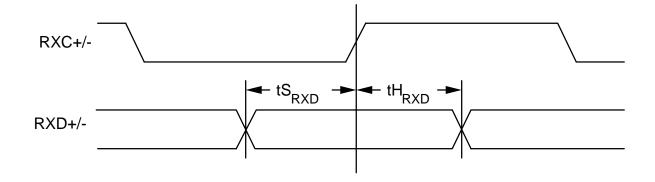

| RXD+<br>RXD- | PECL<br>Input | 63<br>62   | The receive differential data inputs (RXD+, RXD-) contain the 155.52 Mbit/s receive STS-3/STM-1 or 51.84 Mbit/s receive STS-1 stream. RXD+/- is sampled on the rising edge of RXC+/- (the falling edge may be used by reversing RXC+/-).                                                                                                                                                                             |

| RXC+<br>RXC- | PECL<br>Input | 59<br>58   | The receive differential clock inputs (RXC+, RXC-) provides timing for processing the bit serial receive stream, RXD+/- when the PECL bit serial mode is selected. RXC+/- is nominally a 155.52 MHz or 51.84 MHz, 50% duty cycle clock. RXD+/- is sampled on the rising edge of RXC+/ RXC+/- is divided by eight to produce GRICLK when the PECL bit serial mode is selected.                                        |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLAIS/   | Input    | 8          | The receive line AIS insertion (RLAIS) signal controls the insertion of line AIS in the receive outgoing stream, ROUT[7:0], when the ring control port is disabled. When RLAIS is high, line AIS is inserted in the outgoing stream. Line AIS is also optionally inserted automatically upon detection of loss of signal, loss of frame, section trace alarms or line AIS in the incoming stream. RLAIS is sampled on the rising edge of RICLK.                                                 |

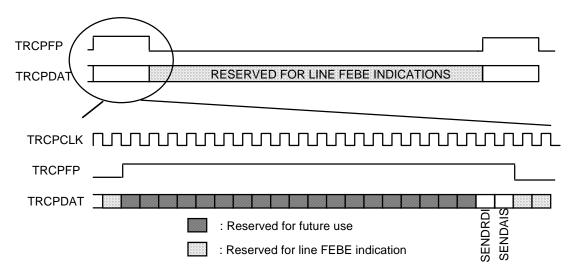

| TRCPCLK  |          |            | The transmit ring control port clock (TRCPCLK) signal provides timing for the transmit ring control port when the ring control port is enabled (the enabling and disabling of the ring control port is controlled by a bit in the Master Control Register). TRCPCLK is nominally a 3.24 MHz, 50% duty cycle clock and is normally connected to the RRCPCLK output of a mate STXC in ring-based add-drop multiplexer applications. TRCPFP and TRCPDAT are sampled on the rising edge of TRCPCLK. |

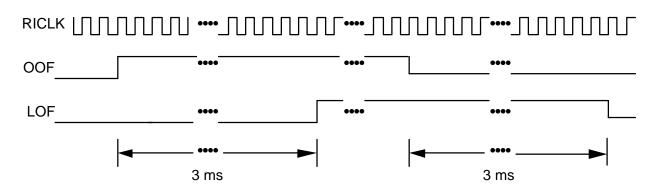

| OOF      | Output   | 57         | The out of frame (OOF) signal is set high while the STXC is unable to find a valid framing pattern (A1, A2) in the incoming stream. OOF is set low when a valid framing pattern is detected. OOF is updated on the rising edge of RICLK.                                                                                                                                                                                                                                                        |

| LOF      | Output   | 56         | The loss of frame (LOF) signal is set high when an out of frame state persists for 3 ms. LOF is set low when an in frame state persists for 3 ms. LOF is updated on the rising edge of RICLK.                                                                                                                                                                                                                                                                                                   |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

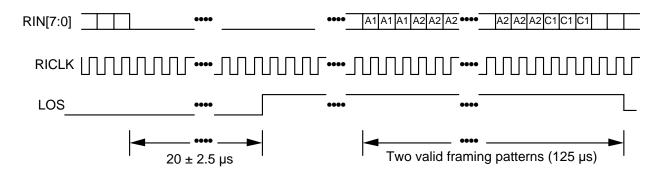

| LOS/     | Output   | 71         | Loss of signal (LOS) is active when the ring control port is disabled. Loss of signal (LOS) is set high when a violating period ( $20 \pm 2.5 \mu s$ ) of consecutive all zeros patterns is detected in the incoming stream. LOS is set low when two valid framing words (A1, A2) are detected, and during the intervening time ( $125 \mu s$ ), no violating period of all zeros patterns is observed. LOS is updated on the rising edge of RICLK.                                                                                                                                                                                                                            |

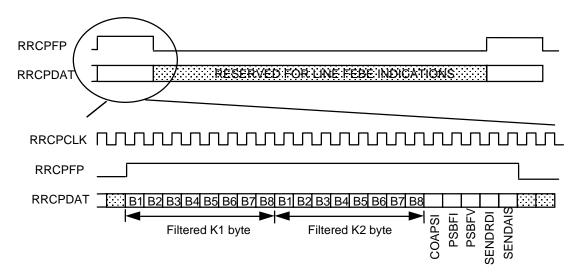

| RRCPFP   |          |            | The receive ring control port frame position (RRCPFP) signal identifies bit positions in the receive ring control port data (RRCPDAT) when the ring control port is enabled (the enabling and disabling of the ring control port is controlled by a bit in the Master Control Register). RRCPFP is high during the filtered K1, K2 bit positions, the change of APS value bit position, the protection switch byte failure bit position, and the send AIS and send RDI bit positions in the RRCPDAT stream. RRCPFP is normally connected to the TRCPFP input of a mate STXC in ring-based add-drop multiplexer applications. RRCPFP is updated on the falling edge of RRCPCLK. |

| B1E      | Output   | 55         | The B1 error clock (B1E) is a return to zero signal that pulses high for 154 ns with a minimum low time of 154 ns for every section bit interleaved parity error (B1) detected in the incoming stream. Up to eight pulses may occur on B1E per frame.                                                                                                                                                                                                                                                                                                                                                                                                                          |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

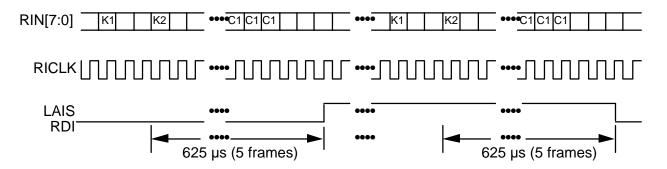

| RDI/     | Output   | 73         | The far end receive failure (RDI) signal is active when the ring control port is disabled. RDI is set high when line RDI is detected in the incoming stream. RDI is declared when a 110 binary pattern is detected in bits 6, 7, and 8 of the K2 byte for three or five consecutive frames. RDI is removed when any pattern other than 110 is detected in bits 6, 7, and 8 of the K2 byte for three or five consecutive frames. This alarm indication is also available through register access. RDI is updated on the rising edge of RICLK. |

| RRCPCLK  |          |            | The receive ring control port clock (RRCPCLK) signal provides timing for the receive ring control port when the ring control port is enabled (the enabling and disabling of the ring control port is controlled by a bit in the Master Control Register). RRCPCLK is nominally a 3.24 MHz, 50% duty cycle clock and is normally connected to the TRCPCLK input of a mate STXC in ring-based add-drop multiplexer applications. RRCPFP and RRCPDAT are updated on the falling edge of RRCPCLK.                                                |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAIS/    | Output   | 72         | The line alarm indication (LAIS) signal is active when the ring control port is disabled. LAIS is set high when line AIS is detected in the incoming stream. LAIS is declared when a 111 binary pattern is detected in bits 6, 7, and 8 of the K2 byte for three or five consecutive frames. LAIS is removed when any pattern other than 111 is detected in bits 6, 7, and 8 of the K2 byte for three or five consecutive frames. This alarm indication is also available through register access. LAIS is updated on the rising edge of RICLK.                                                                                                                                        |

| RRCPDAT  |          |            | The receive ring control port data (RRCPDAT) signal contains the receive ring control port data stream when the ring control port is enabled (the enabling and disabling of the ring control port is controlled by a bit in the Master Control Register). The receive ring control port data consists of the filtered K1, K2 byte values, the change of APS value bit position, the protection switch byte failure status bit position, the send AIS and send RDI bit positions, and the line REI bit positions. RRCPDAT is normally connected to the TRCPDAT input of a mate STXC in ring-based add-drop multiplexer applications. RRCPDAT is updated on the falling edge of RRCPCLK. |

| B2E      | Output   | 78         | The B2 error clock (B2E) is a return to zero signal that pulses 154 ns with a minimum low time of 154 ns for every line bit interleaved parity error (B2) detected in the incoming stream. Up to 8 (STS-1), or 24 (STS-3/STM-1) pulses may occur on B2E, per frame.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RSDCLK   | Output   | 67         | The receive section DCC clock (RSDCLK) is a 192 kHz clock used to update the RSD output. RSDCLK is generated by gapping a 216 kHz clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                             |

|----------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSD      | Output   | 66         | The receive section DCC (RSD) signal contains the section data communications channel (D1, D2, D3) extracted from the incoming stream. RSD is updated on the falling edge of RSDCLK. |

| ROWCLK   | Output   | 70         | The receive order wire clock (ROWCLK) is a 64 kHz clock used to update the RSOW, RSUC, and RLOW outputs. ROWCLK is generated by gapping a 72 kHz clock.                              |

| RSOW     | Output   | 68         | The receive section order wire (RSOW) signal contains the section order wire channel (E1) extracted from the incoming stream. RSOW is updated on the falling edge of ROWCLK.         |

| RSUC     | Output   | 69         | The receive section user channel (RSUC) signal contains the section user channel (F1) extracted from the incoming stream. RSUC is updated on the falling edge of ROWCLK.             |

| RLOW     | Output   | 81         | The receive line order wire (RLOW) signal contains the line order wire channel (E2) extracted from the incoming stream. RLOW is updated on the falling edge of ROWCLK.               |

| RLDCLK   | Output   | 80         | The receive line DCC clock (RLDCLK) is a 576 kHz clock used to update the RLD output. RLDCLK is generated by gapping a 2.16 MHz clock.                                               |

| RLD      | Output   | 79         | The receive line DCC (RLD) signal contains the line data communications channel (D4 - D12) extracted from the incoming stream. RLD is updated on the falling edge of RLDCLK.         |

| RAPSCLK  | Output   | 83         | The receive automatic protection switch channel clock (RAPSCLK) is a 128 kHz clock used to update the RAPS output. RAPSCLK is generated by gapping a 144 kHz clock.                  |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                   |

|----------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAPS     | Output   | 82         | The receive automatic protection switch channel (RAPS) signal carries the automatic protection switch channel (K1, K2) extracted from the incoming stream. RAPS is updated on the falling edge of RAPSCLK.                                                                                                                                                                 |

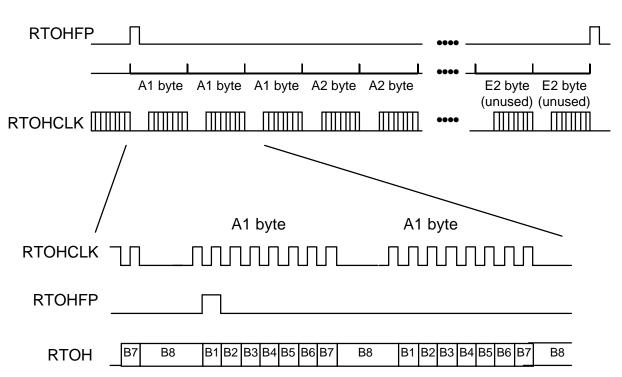

| RTOH     | Output   | 87         | The receive transport overhead (RTOH) signal contains the receive transport overhead bytes (A1, A2, J0, Z0, B1, E1, F1, D1-D3, H1-H3, B2, K1, K2, D4-D12, Z1, Z2, and E2) extracted from the incoming stream. RTOH is updated on the falling edge of RTOHCLK.                                                                                                              |

| RTOHCLK  | Output   | 88         | The receive transport overhead clock (RTOHCLK) is nominally a 5.184 MHz or 1.728 MHz clock that provides timing to process the extracted receive transport overhead, RTOH. RTOHCLK is a gapped 6.48 MHz clock when accessing the transport overhead of an STS-3/STM-1 stream. RTOHCLK is a gapped 2.16 MHz clock when accessing the transport overhead of an STS-1 stream. |

| RTOHFP   | Output   | 84         | The receive transport overhead frame position (RTOHFP) signal is used to locate the individual receive transport overhead bits in the receive transport overhead, RTOH. RTOHFP is set high while bit 1 (the most significant bit) of the first framing byte (A1) is present in the RTOH stream. RTOHFP is updated on the falling edge of RTOHCLK.                          |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GRICLK   | Output   | 134        | When either of the bit serial receive interfaces are enabled, GRICLK is the generated byte serial clock. When the bit serial STS-1 mode is enabled, GRICLK is a 6.48 MHz clock that is generated by dividing the receive serial incoming clock (RSICLK) by eight. When the bit serial STS-3 mode is enabled, GRICLK is a 19.44 MHz clock that is generated by dividing the receive serial incoming clock (RSC+/-) by eight. GRICLK must be externally shorted directly to the receive incoming clock (RICLK) when processing a bit serial stream. |

| ROUT[7]  | Output   | 123        | ROUT[7:0] contains the descrambled outgoing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ROUT[6]  | Output   | 124        | stream in byte serial format. ROUT[7] is the most significant bit (corresponding to bit 1 of                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ROUT[5]  | Output   | 125        | each serial PCM word, the first bit received).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ROUT[4]  | Output   | 126        | ROUT[0] is the least significant bit (corresponding to bit 8 of each serial PCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROUT[3]  | Output   | 127        | word). ROUT[7:0] is updated on the rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ROUT[2]  | Output   | 128        | edge of RICLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ROUT[1]  | Output   | 131        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROUT[0]  | Output   | 132        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROFP     | Output   | 133        | The active high receive outgoing frame position (ROFP) signal is set high once per frame in the byte position immediately following the Z0 bytes in the ROUT[7:0] stream. ROFP is also used to mark the alignment of the RSOW, RSUC, RLOW and RAPS bit streams.                                                                                                                                                                                                                                                                                   |

|          |          |            | ROFP is updated on the rising edge of RICLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TSER     | Input    | 12         | The transmit serial input (TSER) selects the transmit line interface. TSER is tied high to select the bit serial interface on PECL pins TXCI+, TXCI-, TXCO+, TXCO-, TXD+, and TXD A TTL interface is also supported in STS-1 mode on pins TSICLK and TSOUT. TSER is tied low to select the byte serial interface on pins TICLK, TOFP, and TOUT[7:0].                                                                                                                                                                                              |

ISSUE 6

| Pin Name       | Pin Type      | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TICLK/         | Input         | 140        | The transmit incoming clock (TICLK) provides timing for processing the transmit stream, TIN[7:0]. TICLK is nominally a 6.48 MHz (STS-1), or 19.44 MHz (STS-3/STM-1) 50% duty cycle clock, depending on the selected operating mode. TIN[7:0], and TIFP are sampled on the rising edge of TICLK. TICLK must be externally shorted directly to GTICLK when processing bit serial transmit streams.                                                                                        |

| TVCLK          |               |            | The transmit vector clock (TVCLK) is used during STXC production test to verify internal functionality.                                                                                                                                                                                                                                                                                                                                                                                 |

| GTICLK         | Output        | 141        | When either of the bit serial transmit interfaces are enabled, GTICLK is the generated byte serial clock. GTICLK is a 6.48 MHz or 19.44 MHz clock that is generated by dividing the transmit serial incoming clock (TSICLK or TXCI+/-) by eight. GTICLK must be externally shorted directly to the transmit incoming clock (TICLK) when processing a bit serial stream. In line loopback mode operation (LLE bit set high), GTICLK is generated by dividing the RXC+/- inputs by eight. |

| TSICLK         | Input         | 11         | The transmit serial incoming clock (TSICLK) provides timing for updating the bit serial outgoing stream when STS-1 mode is selected. TSICLK is nominally a 51.84 MHz, 50% duty cycle clock. TSOUT is updated on the rising edge of TSICLK. The TSICLK input has an integral pull down resistor. The device may be configured to use the TXCI+/- inputs as the serial clock.                                                                                                             |

| TXCI+<br>TXCI- | PECL<br>Input | 28<br>27   | The transmit differential clock inputs (TXCI+, TXCI-) provide timing for updating the bit serial outgoing stream. TXCI+/- is nominally a 155.52 MHz or 51.84 MHz, 50% duty cycle clock. The TSICLK is the default clock for the 51.84 Mbit/s data rate.                                                                                                                                                                                                                                 |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                    |

|----------|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIN[7]   | Input    | 143        | The transmit incoming bus, (TIN[7:0]), carries                                                                                                                                                                                                                                                              |

| TIN[6]   |          | 144        | an STS-1 or STS-3/STM-1 stream in byte serial format. TIN[7] is the most significant bit                                                                                                                                                                                                                    |

| TIN[5]   |          | 145        | (corresponding to bit 1 of each serial PCM                                                                                                                                                                                                                                                                  |

| TIN[4]   |          | 146        | word, the first bit transmitted). TIN[0] is the                                                                                                                                                                                                                                                             |

| TIN[3]   |          | 147        | least significant bit (corresponding to bit 8 of each serial PCM word). TIN[7:0] is sampled on                                                                                                                                                                                                              |

| TIN[2]   |          | 148        | the rising edge of TICLK.                                                                                                                                                                                                                                                                                   |

| TIN[1]   |          | 149        |                                                                                                                                                                                                                                                                                                             |

| TIN[0]   |          | 150        |                                                                                                                                                                                                                                                                                                             |

| TIFP/    | Input    | 142        | The active high transmit incoming framing position (TIFP/TC1J1V1) signal indicates the frame alignment for incoming streams. When Register Mode Select bit C1EN is logic 0, a high level on TIFP marks the byte immediately following the Z0 bytes in the transmit STS-1 or STS-3 (STM-1) stream, TIN[7:0]. |

| TC1J1V1  |          |            | When Register Mode Select bit C1EN is logic 1, a high level on TIFP marks the first J0 byte in the transmit STS-1 or STS-3 (STM-1) stream, TIN[7:0]. TIFP/TC1J1V1 is sampled on the rising edge of TICLK.                                                                                                   |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDIS     | Input    | 151        | The active high transmit disable (TDIS) signal selectively disables overwriting the STS-1 or STS-3 (STM-1) byte serial stream with the corresponding overhead byte. TDIS is sampled on the rising edge of TICLK. TDIS takes precedence over the TTOHEN and TTOH inputs.                                                                                                                                                                             |

|          |          |            | In general, the value on TIN[7:0] passes through transparently if TDIS is high. Three exceptions exist:                                                                                                                                                                                                                                                                                                                                             |

|          |          |            | 1.) Bits 6 to 8 of the K2 byte may be overwritten by a active RDI indication ("110") regardless of the state of TDIS.                                                                                                                                                                                                                                                                                                                               |

|          |          |            | 2.) If TDIS is high during the section BIP byte (B1), the TIN[7:0] value becomes an error mask for the generated section BIP.                                                                                                                                                                                                                                                                                                                       |

|          |          |            | 3.) If TDIS is high during the line BIP bytes (B2), and the DB2 bit in the TLOP Control register is logic 0, the TIN[7:0] value becomes an error mask for the generated line BIP.                                                                                                                                                                                                                                                                   |

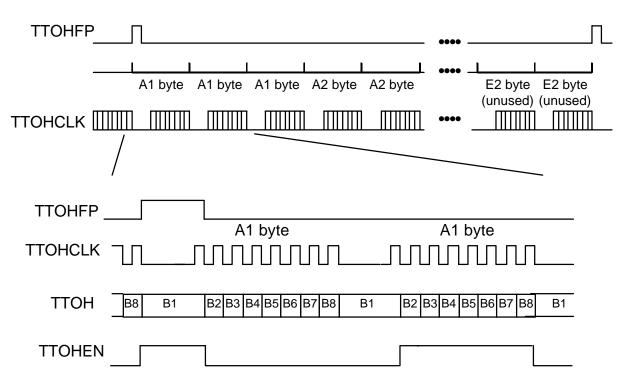

| TTOH     | Input    | 155        | The transmit transport overhead bus (TTOH) contains the transport overhead bytes (A1, A2, J0, Z0, E1, F1, D1-D3, H3, K1, K2, D4-D12, Z1, Z2, and E2) and error masks (H1, H2, B1, and B2) which may be inserted, or used to insert bit interleaved parity errors or payload pointer bit errors into the overhead byte positions in the outgoing stream. Insertion is controlled by the TTOHEN input. TTOH is sampled on the rising edge of TTOHCLK. |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

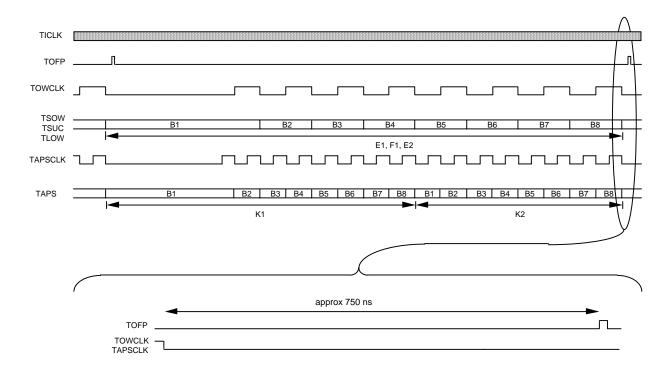

| TTOHFP   | Output   | 156        | The transmit transport overhead frame position (TTOHFP) signal is used to locate the individual transport overhead bits in the transport overhead bus, TTOH. TTOHFP is set high while bit 1 (the most significant bit) of the first framing byte (A1) is expected in the incoming stream. TTOHFP is updated on the falling edge of TTOHCLK.                                               |

| TTOHCLK  | Output   | 153        | The transmit transport overhead clock (TTOHCLK) is nominally a 5.184 MHz (1.728 MHz for STS-1) clock that provides timing for upstream circuitry that sources the transport overhead, TTOH. TTOHCLK is a gapped 6.48 MHz clock when accessing the transport overhead of STS-3/STM-1 streams. TTOHCLK is a gapped 2.16 MHz clock when accessing the transport overhead of an STS-1 stream. |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TTOHEN   | Input    | 152        | The transmit transport overhead insert enable (TTOHEN) signal controls the source of the transport overhead data which is inserted in the transmit stream. While TTOHEN is high during the most significant bit of a TTOH byte (and TDIS is low), values sampled on the TTOH input are inserted into the corresponding transport overhead bit positions (for the A1, A2, J0, Z0, E1, F1, D1-D3, H3, K1, K2, D4-D12, Z1, Z2, and E2 bytes). While TTOHEN is low during the most significant bit of a TTOH byte, the default values are inserted into these transport overhead byte positions. A high level on TTOHEN during most significant bit of TTOH for the H1, H2, B1, or B2 bytes enables an error mask. While the error mask is enabled, a high level on TTOH causes the corresponding H1, H2, B1 or B2 bit positions to be inverted. When the section trace enable (STEN) bit is a logic 1, the J0 byte contents are sourced from the section trace buffer, regardless of the state of TTOHEN. A low level on TTOH allows the corresponding bit positions to pass through the STXC uncorrupted. TTOHEN is sampled on the rising edge of TTOHCLK. |

ISSUE 6

| Pin Name | Pin Type | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|