STANDARD PRODUCT

PM6344 EQUAD

PMC-951013

ISSUE 5

**QUADRUPLE E1 FRAMER**

# PM6344

# **EQUAD**

# QUADRUPLE E1 FRAMER

**ISSUE 5: JUNE 1998**

# **CONTENTS**

| 1 | FEAT  | FEATURES                                      |    |  |  |

|---|-------|-----------------------------------------------|----|--|--|

| 2 | APPL  | ICATIONS                                      | 4  |  |  |

| 3 | REFE  | REFERENCES                                    |    |  |  |

| 4 | APPL  | ICATION EXAMPLES                              | 7  |  |  |

| 5 | BLOC  | CK DIAGRAM                                    | 8  |  |  |

| 6 | PIN D | DIAGRAM                                       | 11 |  |  |

| 7 | PIN D | DESCRIPTION                                   | 12 |  |  |

| 8 | FUNC  | CTIONAL DESCRIPTION                           | 29 |  |  |

|   | 8.1   | DIGITAL RECEIVE INTERFACE (DRIF)              | 29 |  |  |

|   | 8.2   | CLOCK AND DATA RECOVERY (CDRC)                | 29 |  |  |

|   | 8.3   | FRAMER (FRMR)                                 | 31 |  |  |

|   | 8.4   | PERFORMANCE MONITOR COUNTERS (PMON)           | 38 |  |  |

|   | 8.5   | HDLC RECEIVER (RFDL)                          | 38 |  |  |

|   | 8.6   | ELASTIC STORE (ELST)                          | 39 |  |  |

|   | 8.7   | SIGNALING EXTRACTOR (SIGX)                    | 39 |  |  |

|   | 8.8   | BACKPLANE RECEIVE INTERFACE (BRIF)            | 40 |  |  |

|   | 8.9   | TRANSMITTER (TRAN)                            | 40 |  |  |

|   | 8.10  | TRANSMIT PER-CHANNEL SERIAL CONTROLLER (PCSC) | 41 |  |  |

|   | 8.11  | HDLC TRANSMITTER (XFDL)                       | 41 |  |  |

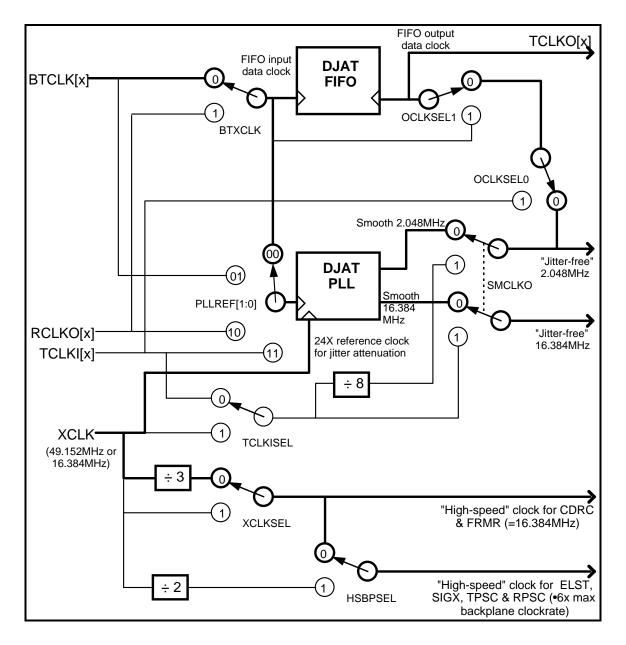

|   | 8.12  | DIGITAL JITTER ATTENUATOR (DJAT)              | 42 |  |  |

|   | 8.13  | TIMING OPTIONS (TOPS)                         | 46 |  |  |

|   | 8.14  | DIGITAL E1 TRANSMIT INTERFACE (DTIF)          | 46 |  |  |

|   | 8.15  | BACKPLANE TRANSMIT INTERFACE (BTIF)           | 47 |  |  |

**QUADRUPLE E1 FRAMER** PMC-951013 ISSUE 5 MICROPROCESSOR INTERFACE (MPIF) .......47 8.16 9 REGISTER DESCRIPTION ......48 NORMAL MODE REGISTER DESCRIPTION.......52 10 SIGX INDIRECT REGISTERS 96 (60H) - 127 (7FH) - SEGMENT 4: TYPICAL 10.1 REGISTERS 049-04FH, 0C9H-0CFH, 149H-14FH, 1C9H-1CFH; LATCHING 10.2 11 11.1 FUNCTIONAL TIMING......180 12 12.1 13 13.1 USING THE INTERNAL FDL TRANSMITTER ......192 USING THE INTERNAL FDL RECEIVER......194 13.2 13.3 USING THE LOOPBACK MODES......201 USING THE PER-CHANNEL SERIAL CONTROLLERS......204 13.4 13.4.3 INDIRECT ACCESS MODE .......205 USING THE DIGITAL JITTER ATTENUATOR ......206 13.5

#### STANDARD PRODUCT

| PMC-951013 | ISSUE 5 | QUADRUPLE E1 FRAMER |

|------------|---------|---------------------|

|------------|---------|---------------------|

|    | 13.5.3 ELASTIC STORE APPLICATION207                  |

|----|------------------------------------------------------|

|    | 13.5.4 ALTERNATE TCLKO REFERENCE APPLICATION207      |

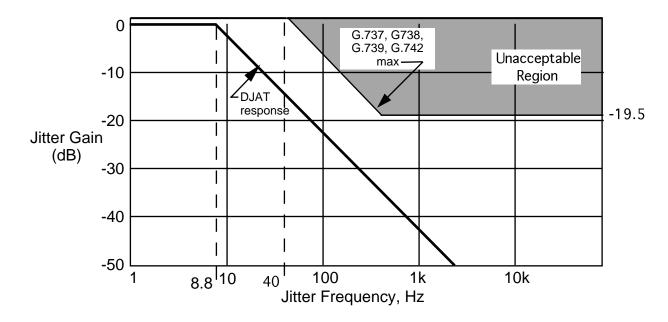

|    | 13.5.5 CHANGING THE JITTER TRANSFER FUNCTION208      |

|    | 13.5.6 RECEIVER JITTER ATTENUATION                   |

|    | 13.6 USING THE PERFORMANCE MONITOR COUNTER VALUES210 |

|    | 13.7 RESET PROCEDURE                                 |

| 14 | ABSOLUTE MAXIMUM RATINGS216                          |

| 15 | CAPACITANCE217                                       |

| 16 | D.C. CHARACTERISTICS218                              |

| 17 | MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS220   |

| 18 | EQUAD I/O TIMING CHARACTERISTICS                     |

| 19 | ORDERING AND THERMAL INFORMATION                     |

| 20 | MECHANICAL INFORMATION                               |

# **LIST OF REGISTERS**

| REGISTER 000H, 080H, 100H, 180H: RECEIVE OPTIONS                      | 53 |

|-----------------------------------------------------------------------|----|

| REGISTER 001H, 081H, 101H, 181H: RECEIVE BACKPLANE OPTIONS            | 56 |

| REGISTER 002H, 082H, 102H, 182H: DATALINK OPTIONS                     | 60 |

| REGISTER 003H, 083H, 103H, 183H: RECEIVE INTERFACE CONFIGURATION      | 63 |

| REGISTER 004H, 084H, 104H, 184H: TRANSMIT INTERFACE CONFIGURATION     | 65 |

| REGISTER 005H, 085H, 105H, 185H: TRANSMIT BACKPLANE OPTIONS           | 68 |

| REGISTER 006H, 086H, 106H, 186H: TRANSMIT FRAMING OPTIONS             | 70 |

| REGISTER 007H, 087H, 107H, 187H: TRANSMIT TIMING OPTIONS              | 72 |

| REGISTER 008H, 088H, 108H, 188H: INTERRUPT SOURCE                     | 77 |

| REGISTER 009H, 089H, 109H, 189H: RECEIVE TS0 DATA LINK ENABLES        | 78 |

| REGISTER 00AH, 08AH, 10AH, 18AH: MASTER DIAGNOSTICS                   | 80 |

| REGISTER 00BH, 20BH: EQUAD MASTER TEST                                | 82 |

| REGISTER 00CH: EQUAD REVISION/CHIP ID/GLOBAL PMON UPDATE              | 84 |

| REGISTER 00DH, 08DH, 10DH, 18DH: FRAMER RESET                         | 85 |

| REGISTER 00EH, 08EH, 10EH, 18EH: PHASE STATUS WORD (LSB)              | 86 |

| REGISTER 00FH, 08FH, 10FH, 18FH: PHASE STATUS WORD (MSB)              | 88 |

| REGISTER 010H, 090H, 110H, 190H: CDRC CONFIGURATION                   | 89 |

| REGISTER 011H, 091H, 111H, 191H: CDRC INTERRUPT ENABLE                | 91 |

| REGISTER 012H, 092H, 112H, 192H: CDRC INTERRUPT STATUS                | 92 |

| REGISTER 013H, 093H, 113H, 193H: CDRC ALTERNATE LOSS OF SIGNAL STATUS | 94 |

| REGISTERS 014H, 094H, 114H AND 194H: CHANNEL SELECT (0 TO 7)          | 95 |

| REGISTERS 015H, 095H, 115H AND 195H: CHANNEL SELECT (8 TO 15)         | 96 |

| REGISTERS 016H, 096H, 116H AND 196H: CHANNEL SELECT (16 TO 23)        | 97 |

| REGISTERS 017H, 097H, 117H AND 197H: CHANNEL SELECT (24 TO 31)98                    |

|-------------------------------------------------------------------------------------|

| REGISTER 018H, 098H, 118H, 198H: DJAT INTERRUPT STATUS99                            |

| REGISTER 019H, 099H, 119H, 199H: DJAT REFERENCE CLOCK DIVISOR (N1) CONTROL100       |

| REGISTER 01AH, 09AH, 11AH, 19AH: DJAT OUTPUT CLOCK DIVISOR (N2) CONTROL101          |

| REGISTER 01BH, 09BH, 11BH, 19BH: DJAT CONFIGURATION102                              |

| REGISTER 01CH, 09CH, 11CH, 19CH: ELST CONFIGURATION104                              |

| REGISTER 01DH, 09DH, 11DH, 19DH: ELST INTERRUPT STATUS                              |

| REGISTER 01EH, 09EH, 11EH, 19EH: ELST IDLE CODE                                     |

| REGISTER 020H, 0A0H, 120H, 1A0H: FRMR FRAME ALIGNMENT OPTIONS107                    |

| REGISTER 021H, 0A1H, 121H, 1A1H: FRMR MAINTENANCE MODE OPTIONS109                   |

| REGISTER 022H, 0A2H, 122H, 1A2H: FRMR FRAMING STATUS INTERRUPT ENABLE111            |

| REGISTER 023H, 0A3H, 123H, 1A3H: FRMR MAINTENANCE/ALARM STATUS INTERRUPT ENABLE     |

| REGISTER 024H, 0A4H, 124H, 1A4H: FRMR FRAMING STATUS INTERRUPT INDICATION.113       |

| REGISTER 025H, 0A5H, 125H, 1A5H: FRMR MAINTENANCE/ALARM STATUS INTERRUPT INDICATION |

| REGISTER 026H, 0A6H, 126H, 1A6H: FRMR FRAMING STATUS115                             |

| REGISTER 027H, 0A7H, 127H, 1A7H: FRMR MAINTENANCE/ALARM STATUS117                   |

| REGISTER 028H, 0A8H, 128H, 1A8H: FRMR INTERNATIONAL/NATIONAL BITS119                |

| REGISTER 029H, 0A9H, 129H, 1A9H: FRMR EXTRA BITS                                    |

| REGISTER 02AH, 0AAH, 12AH, 1AAH: FRMR CRC ERROR COUNTER - LSB121                    |

| REGISTER 02BH, 0ABH, 12BH, 1ABH: FRMR CRC ERROR COUNTER - MSB122                    |

| REGISTER 02CH, 0ACH, 12CH, 1ACH: TS16 AIS ALARM STATUS123                           |

| REGISTER 030H, 0B0H, 130H, 1B0H: TPSC BLOCK CONFIGURATION                           |

| REGISTER 031H, 0B1H, 131H, 1B1H: TPSC BLOCK µP ACCESS STATUS125                     |

| REGISTER 032H, 0B2H, 132H, 1B2H: TPSC BLOCK TIMESLOT INDIRECT  ADDRESS/CONTROL                                    | 126   |

|-------------------------------------------------------------------------------------------------------------------|-------|

| REGISTER 033H, 0B3H, 133H, 1B3H: TPSC BLOCK TIMESLOT INDIRECT DATA BUFFER                                         | 127   |

| TPSC INTERNAL REGISTERS 20-3FH: DATA CONTROL BYTE                                                                 | 129   |

| TPSC INTERNAL REGISTERS 40-5FH: IDLE CODE BYTE                                                                    | 131   |

| REGISTER 034H, 0B4H, 134H, 1B4H: XFDL BLOCK CONFIGURATION                                                         | 132   |

| REGISTER 035H, 0B5H, 135H, 1B5H: XFDL INTERRUPT STATUS                                                            | 134   |

| REGISTER 036H, 0B6H, 136H, 1B6H: XFDL TRANSMIT DATA                                                               | 135   |

| REGISTER 038H, 0B8H, 138H, 1B8H: RFDL CONFIGURATION                                                               | 136   |

| REGISTER 039H, 0B9H, 139H, 1B9H: RFDL INTERRUPT CONTROL/STATUS                                                    | 137   |

| REGISTER 03AH, 0BAH, 13AH, 1BAH: RFDL STATUS                                                                      | 139   |

| REGISTER 03BH, 0BBH, 13BH, 1BBH: RFDL RECEIVE DATA                                                                | 142   |

| REGISTERS 03CH, 0BCH, 13CH AND 1BCH: INTERRUPT ID/CLOCK MONITOR                                                   | 143   |

| REGISTERS 03DH, 0BDH, 13DH AND 1BDH: BACKPLANE PARITY CONFIGURATION AN STATUS                                     |       |

| REGISTER 040H, 0C0H, 140H, 1C0H: SIGX BLOCK CONFIGURATION                                                         | 147   |

| REGISTER 041H, 0C1H, 141H, 1C1H: SIGX BLOCK µP ACCESS STATUS                                                      | 149   |

| REGISTER 042H, 0C2H, 142H, 1C2H: SIGX BLOCK TIME SLOT INDIRECT ADDRESS/CONTROL                                    | 150   |

| REGISTER 043H, 0C3H, 143H, 1C3H: SIGX BLOCK TIME SLOT INDIRECT DATA BUFFER                                        | ₹.151 |

| SIGX INDIRECT REGISTERS 33 (21H)- 47 (2FH) - SEGMENT 2: TYPICAL TIMESLOT SIGNALING DATA REGISTER (TSS 1-15)       | 153   |

| SIGX INDIRECT REGISTERS 49 (31H)- 63 (3FH) - SEGMENT 2: TYPICAL TIMESLOT SIGNALING DATA REGISTER (TSS 17-31)      | 154   |

| SIGX INDIRECT REGISTERS 64 (40H) - 95 (5FH) - SEGMENT 3: TYPICAL PER-TIMESLO PCM TRUNK CONDITIONING DATA REGISTER |       |

| CONDITIONING DATA REGISTER                                                                                        | 156   |

| REGISTE | R 044H, 0C | 4H, 144H, 1 | 1C4H: TRAN ( | CONFIGURA  | ATION      |              | 158     |

|---------|------------|-------------|--------------|------------|------------|--------------|---------|

| REGISTE | R 045H, 0C | 5H, 145H, 1 | 1C5H: TRAN T | RANSMIT A  | ALARM/DIAC | SNOSTIC CONT | ROL.162 |

| REGISTE | R 046H, 0C | 6H, 146H, 1 | 1C6H: TRAN I | NTERNATIO  | ONAL/NATIO | NAL CONTROL  | 164     |

| REGISTE | R 047H, 0C | 7H, 147H, 1 | 1C7H: TRAN E | EXTRA BITS | CONTROL    |              | 166     |

| REGISTE | R 048H, 0C | 8H, 148H, 1 | 1C8H: PMON   | CONTROL/   | STATUS     |              | 167     |

| REGISTE | R 049H, 0C | 9H, 149H, 1 | 1C9H: FRAMII | NG BIT ERF | ROR COUNT  | -            | 169     |

| REGISTE | R 04AH, 0C | AH, 14AH,   | 1CAH: FAR E  | ND BLOCK   | ERROR CO   | UNT LSB      | 170     |

| REGISTE | R 04BH, 0C | BH, 14BH,   | 1CBH: FAR E  | ND BLOCK   | ERROR CO   | UNT MSB      | 171     |

| REGISTE | R 04CH, 0C | CH, 14CH,   | 1CCH: CRC I  | ERROR CO   | UNT LSB    |              | 172     |

| REGISTE | R 04DH, 0C | DH, 14DH,   | 1CDH: CRC I  | ERROR CO   | UNT MSB    |              | 173     |

| REGISTE | R 04EH, 0C | EH, 14EH,   | 1CEH: LINE ( | CODE VIOL  | ATION COUI | NT LSB       | 174     |

| REGISTE | R 04FH. 0C | FH. 14FH.   | 1CFH: LINE C | ODE VIOLA  | ATION COUN | IT MSB       | 175     |

# **LIST OF FIGURES**

| FIGURE 1  | - EXAMPLE 1. DS-3 TERMINAL MULTIPLEXER/CHANNEL BANK             | 7   |

|-----------|-----------------------------------------------------------------|-----|

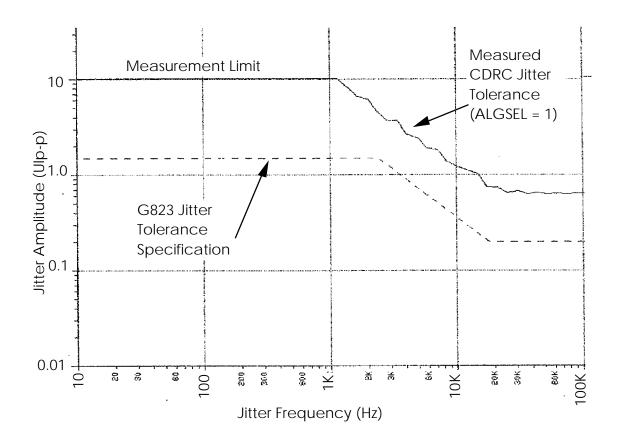

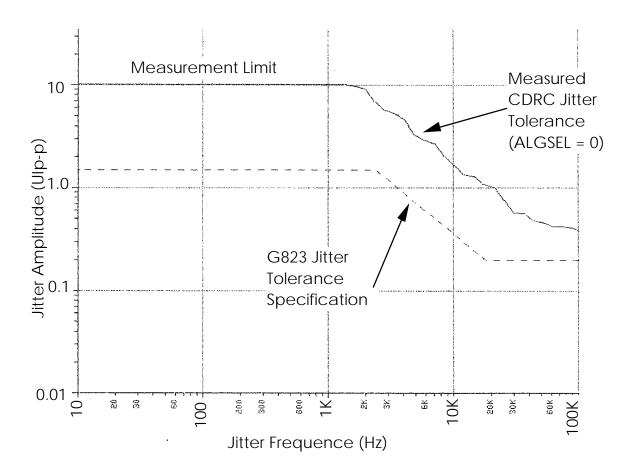

| FIGURE 2  | - CDRC JITTER TOLERANCE WITH ALGSEL = 1                         | 30  |

| FIGURE 3  | - CDRC JITTER TOLERANCE WITH ALGSEL = 0                         | 31  |

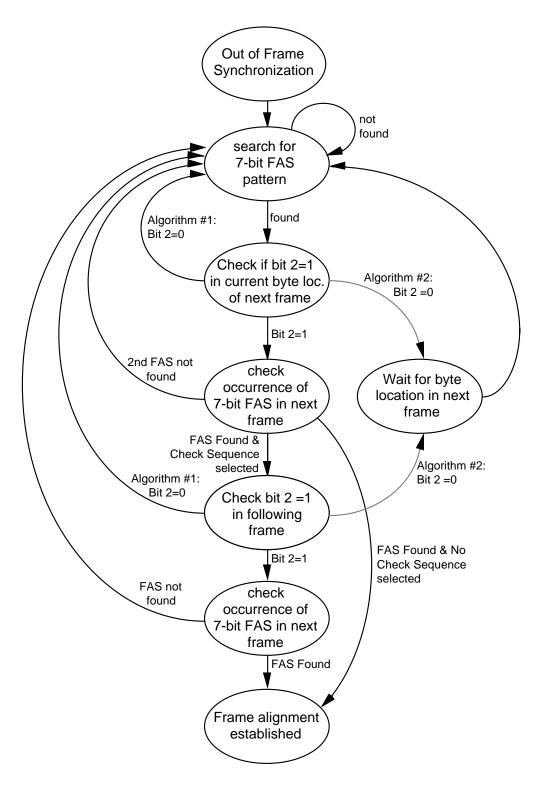

| FIGURE 4  | - BASIC FRAMING ALGORITHM FLOWCHART                             | 34  |

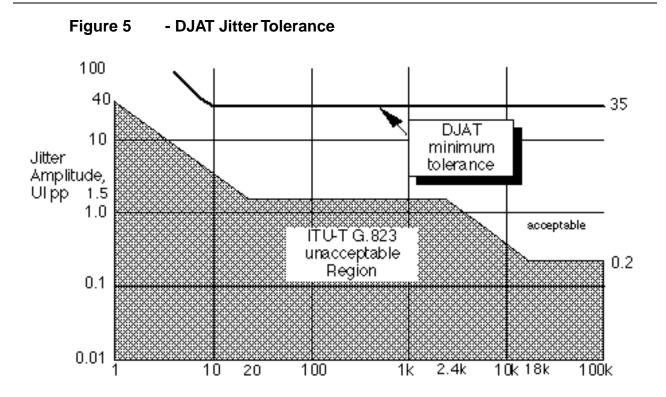

| FIGURE 5  | - DJAT JITTER TOLERANCE                                         | 44  |

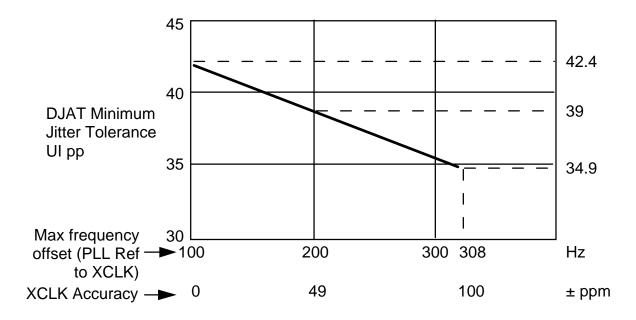

| FIGURE 6  | - DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY               | 45  |

| FIGURE 7  | - DJAT JITTER TRANSFER                                          | 46  |

| FIGURE 8  | - TRANSMIT TIMING OPTIONS                                       | 76  |

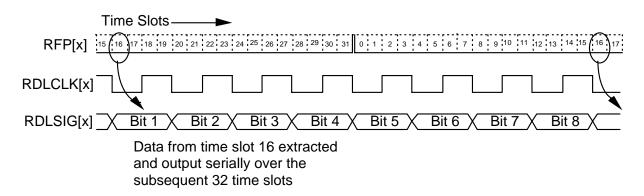

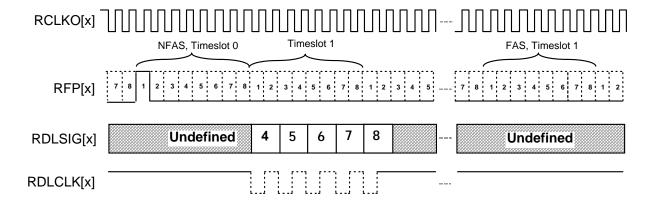

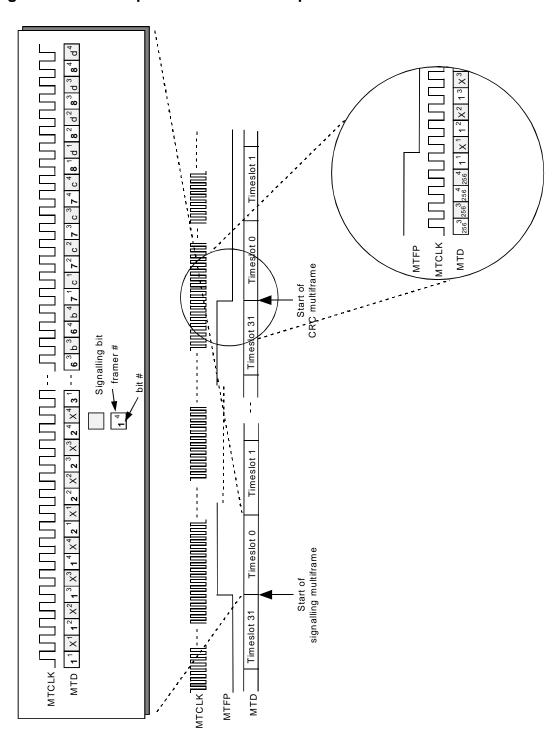

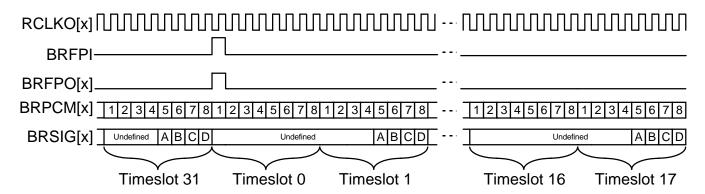

| FIGURE 9  | - TS16 RECEIVE DATALINK INTERFACE                               | 180 |

| FIGURE 10 | - TS0 RECEIVE DATALINK INTERFACE                                | 180 |

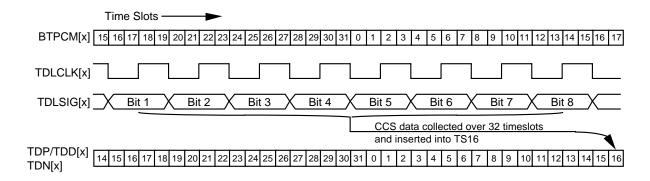

| FIGURE 11 | - TS16 TRANSMIT DATALINK INTERFACE                              | 181 |

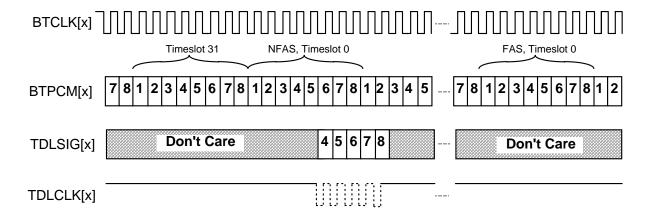

| FIGURE 12 | - TS0 TRANSMIT DATALINK INTERFACE                               | 181 |

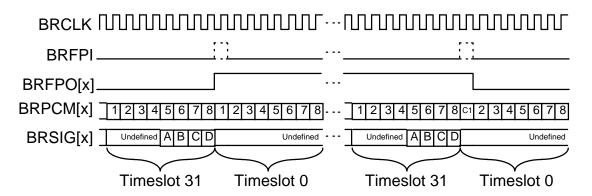

| FIGURE 13 | - ROHM=0, BRX2RAIL=0, BRXSMFP=0 AND BRXCMFP=0                   | 182 |

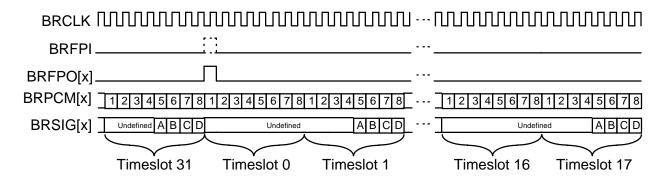

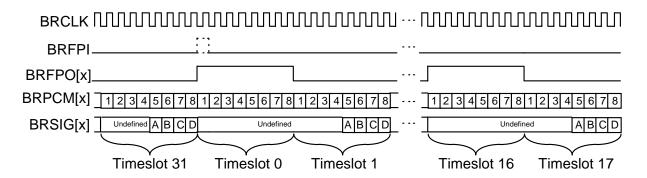

| FIGURE 14 | - RECEIVE COMPOSITE MULTIFRAME OUTPUT (BRXSMFP=1 AND BRXCMFP=1) | 183 |

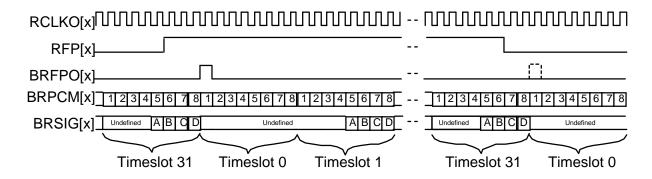

| FIGURE 15 | - RECEIVE OVERHEAD OUTPUT (ROHM=1)                              | 183 |

| FIGURE 16 | - ELSTBYP=1, SRSMFP=1, SRCMFP=1, BRXSMFP=1, BRXCMFP=0           | 184 |

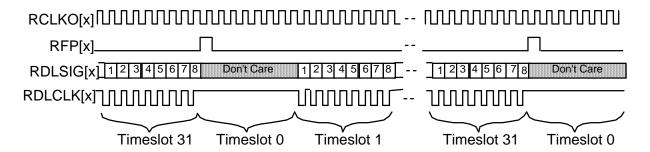

| FIGURE 17 | - RECEIVE CHANNEL INTERFACE                                     | 184 |

| FIGURE 18 | - TRANSMIT BACKPLANE INTERFACE                                  | 185 |

| FIGURE 19 | - TRANSMIT CHANNEL INTERFACE                                    | 185 |

| FIGURE 20 | - MULTIPLEXED RECEIVE BACKPLANE INTERFACE                       | 186 |

| FIGURE 21 | - MULTIPLEXED TRANSMIT BACKPLANE INTERFACE                      | 188 |

| FIGURE 22 | - MULTIPLEXED TRANSMIT BACKPLANE INTERFACE WITH BTXMFP=1        | 190 |

| PMC-951013 | ISSUE 5                                           | QUADRUPLE E1 FRAM |

|------------|---------------------------------------------------|-------------------|

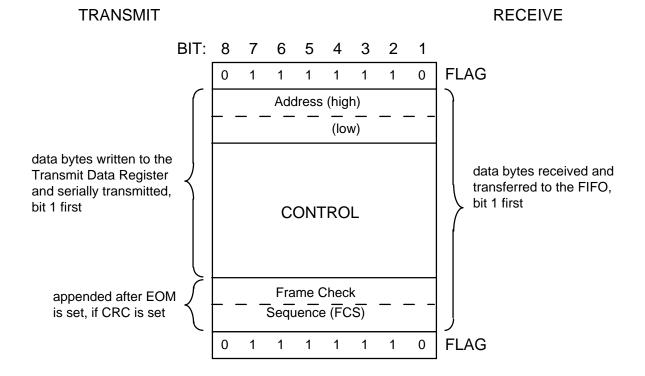

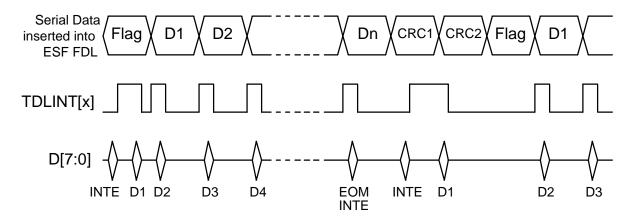

| FIGURE 23  | - TYPICAL DATA FRAME                              | 197               |

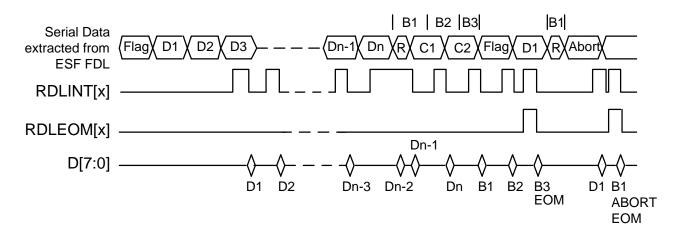

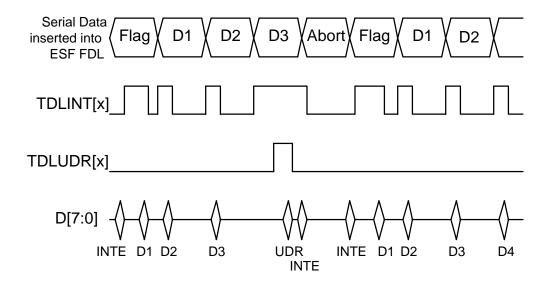

| FIGURE 24  | - RFDL NORMAL DATA AND ABORT SEQUENCE             | 198               |

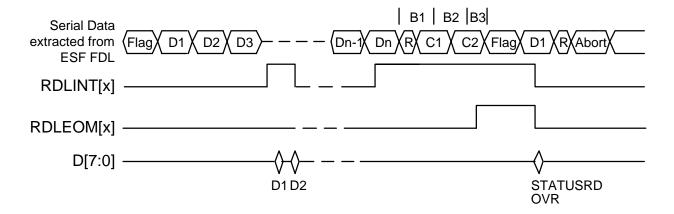

| FIGURE 25  | - RFDL FIFO OVERRUN                               | 199               |

| FIGURE 26  | - XFDL NORMAL DATA SEQUENCE                       | 200               |

| FIGURE 27  | - XFDL UNDERRUN SEQUENCE                          | 201               |

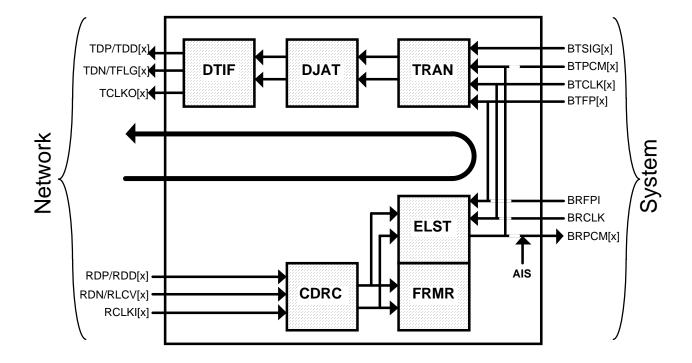

| FIGURE 28  | - PAYLOAD LOOPBACK                                | 202               |

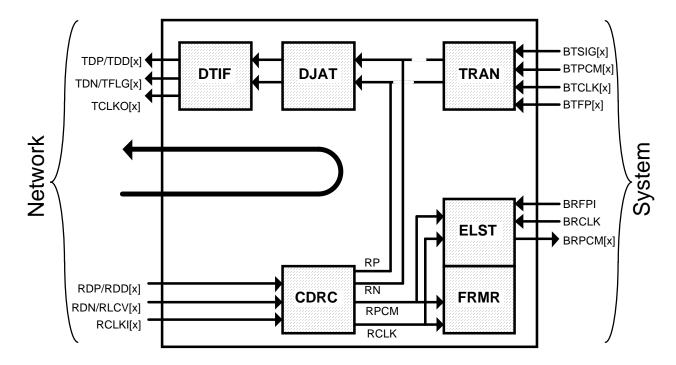

| FIGURE 29  | - LINE LOOPBACK                                   | 203               |

| FIGURE 30  | - DIAGNOSTIC DIGITAL LOOPBACK                     | 204               |

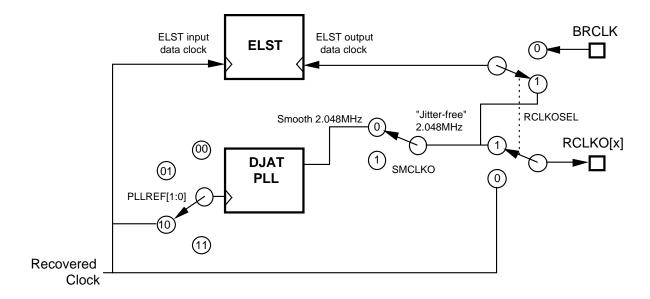

| FIGURE 31  | - RECEIVE BACKPLANE INTERFACE WITH RCLKOSEL = 1   | 209               |

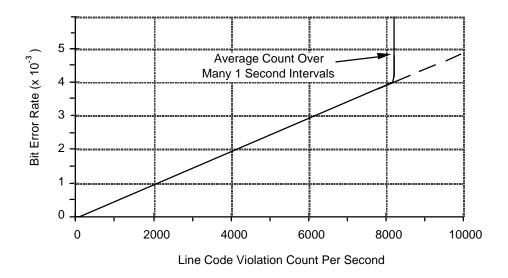

| FIGURE 32  | - LCV COUNT VS. BER                               | 211               |

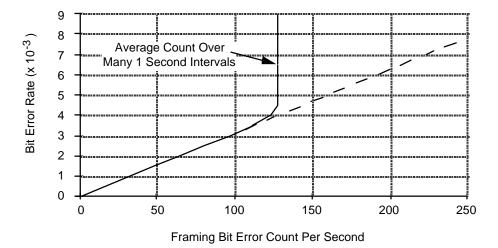

| FIGURE 33  | - FER COUNT VS. BER                               | 211               |

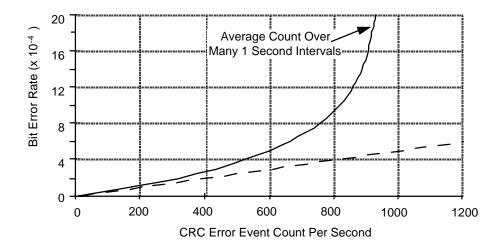

| FIGURE 34  | - CRCE COUNT VS. BER                              | 212               |

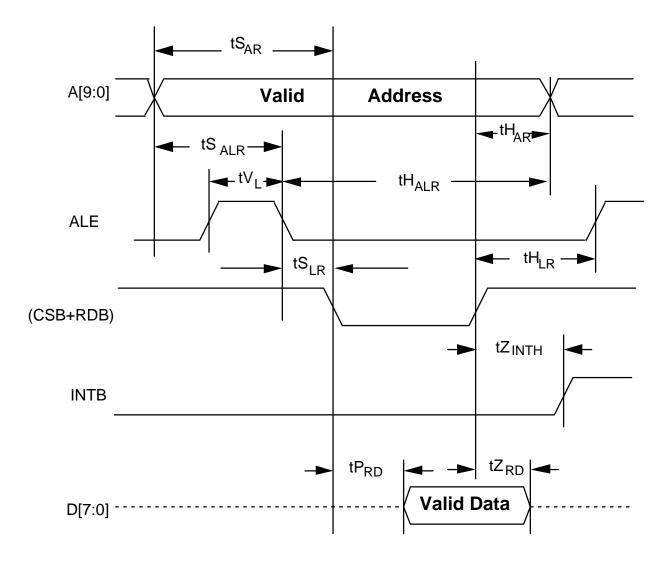

| FIGURE 35  | - MICROPROCESSOR READ ACCESS TIMING               | 221               |

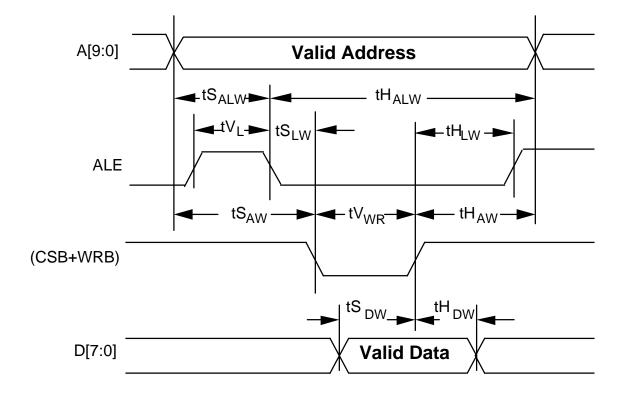

| FIGURE 36  | - MICROPROCESSOR WRITE ACCESS TIMING              | 223               |

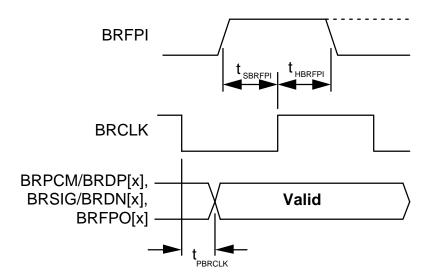

| FIGURE 37  | - BACKPLANE TRANSMIT INPUT TIMING DIAGRAM         | 225               |

| FIGURE 38  | - BACKPLANE TRANSMIT INPUT TIMING DIAGRAM         | 226               |

| FIGURE 39  | - XCLK=37.056 MHZ INPUT TIMING                    | 227               |

| FIGURE 40  | - TCLKI INPUT TIMING                              | 228               |

| FIGURE 41  | - DIGITAL RECEIVE INTERFACE INPUT TIMING DIAGRAM  | 229               |

| FIGURE 42  | - TRANSMIT DATA LINK INPUT TIMING DIAGRAM         | 230               |

| FIGURE 43  | - BACKPLANE RECEIVE TIMING DIAGRAM                | 231               |

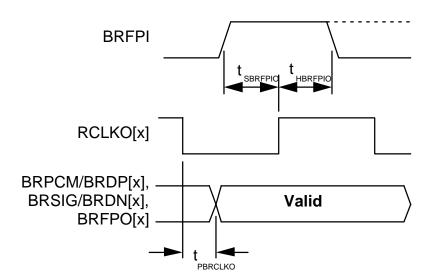

| FIGURE 44  | - BACKPLANE RECEIVE TIMING (RCLKOSEL = 1) DIAGRAM | 232               |

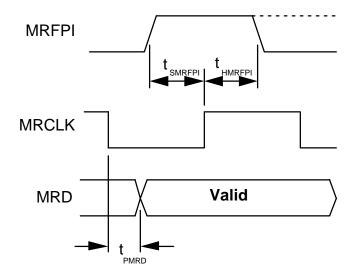

| FIGURE 45  | - MULTIPLEXED BACKPLANE RECEIVE TIMING DIAGRAM    | 233               |

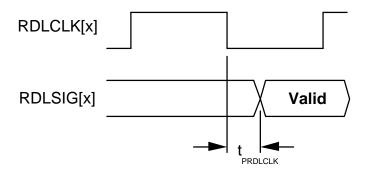

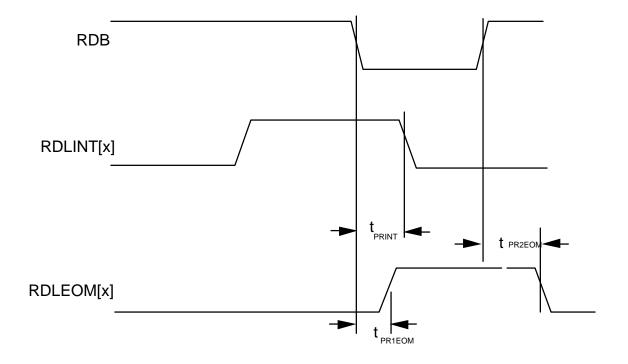

FIGURE 46 - RECEIVE DATA LINK OUTPUT TIMING DIAGRAM......234

PM6344 EQUAD

**QUADRUPLE E1 FRAMER**

#### STANDARD PRODUCT

PMC-951013

ISSUE 5

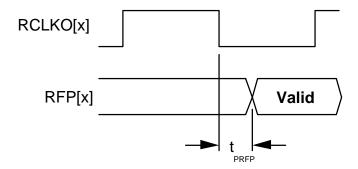

| FIGURE 47 | - RECOVERED FRAME OUTPUT TIMING DIAGRAM                      | 234 |

|-----------|--------------------------------------------------------------|-----|

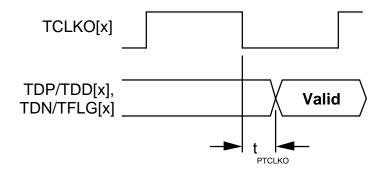

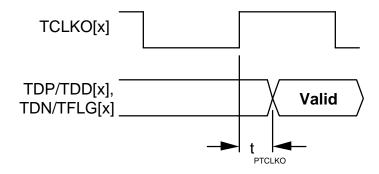

| FIGURE 48 | - TRANSMIT INTERFACE OUTPUT TIMING DIAGRAM                   | 235 |

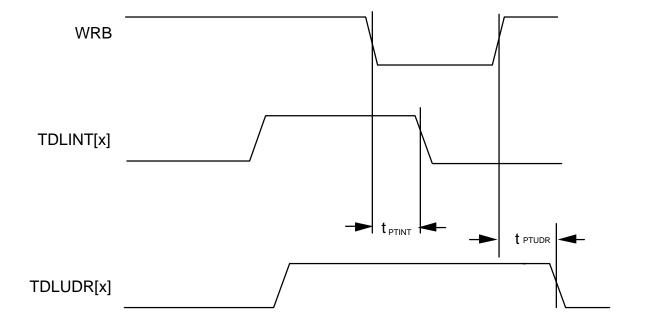

| FIGURE 49 | - TRANSMIT DATA LINK DMA INTERFACE OUTPUT TIMING DIAGRAM     | 236 |

| FIGURE 50 | - RECEIVE DATA LINK DMA INTERFACE OUTPUT TIMING DIAGRAM      | 237 |

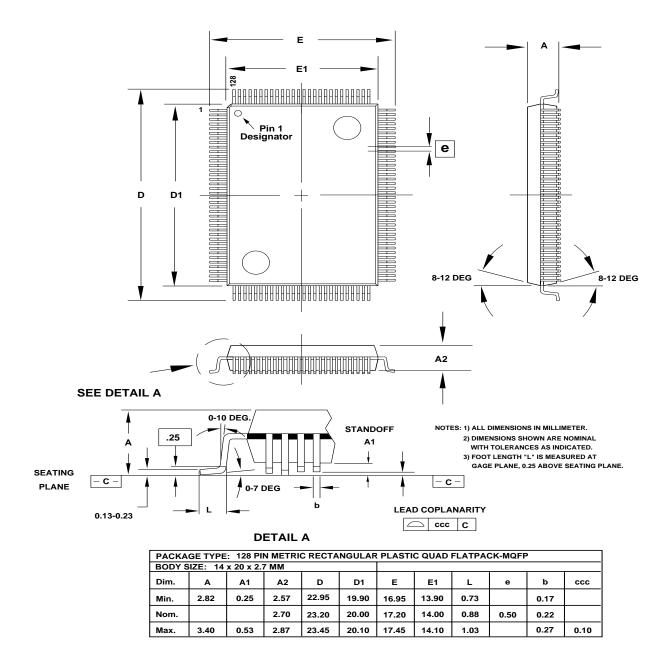

| FIGURE 51 | - 128 PIN COPPER LEADFRAME PLASTIC QUAD FLAT PACK (R SUFFIX) | 240 |

# **LIST OF TABLES**

| TABLE 1  | - NORMAL MODE REGISTER MEMORY MAP                                   | 48   |

|----------|---------------------------------------------------------------------|------|

| TABLE 2  |                                                                     | 74   |

| TABLE 3  |                                                                     | 87   |

| TABLE 4  |                                                                     | 177  |

| TABLE 5  |                                                                     | 177  |

| TABLE 6  | - CONFIGURING THE EQUAD FROM RESET                                  | 191  |

| TABLE 7  |                                                                     | 210  |

| TABLE 8  | - EQUAD CAPACITANCE                                                 | 217  |

| TABLE 9  | - EQUAD D.C. CHARACTERISTICS                                        | 218  |

| TABLE 10 | - MICROPROCESSOR READ ACCESS (FIGURE 35)                            | 220  |

| TABLE 11 | - MICROPROCESSOR WRITE ACCESS (FIGURE 36)                           | 222  |

| TABLE 12 | - BACKPLANE TRANSMIT INPUT TIMING, MENB INPUT HIGH (FIGURE 37)      | .225 |

| TABLE 13 | - BACKPLANE TRANSMIT INPUT TIMING, MENB INPUT LOW (FIGURE 37)       | 226  |

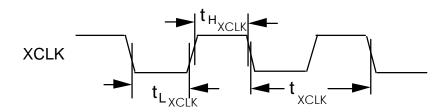

| TABLE 14 | - XCLK=49.152 MHZ INPUT (FIGURE 39)                                 | 227  |

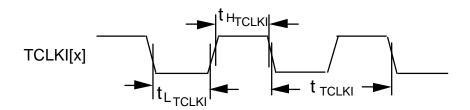

| TABLE 15 | - TCLKI INPUT (FIGURE 40                                            | 227  |

| TABLE 16 | - DIGITAL RECEIVE INTERFACE INPUT TIMING (FIGURE 41)                | 228  |

| TABLE 17 | - TRANSMIT DATA LINK INPUT TIMING (FIGURE 42)                       | 230  |

| TABLE 18 | - BACKPLANE RECEIVE TIMING, MENB INPUT HIGH (FIGURE 43)             | 231  |

| TABLE 19 | - BACKPLANE RECEIVE TIMING, MENB INPUT HIGH, RCLKOSEL = 1 (FIG. 44) |      |

| TABLE 20 | - MULTIPLEXED BACKPLANE RECEIVE TIMING, MENB INPUT LOW (FIGUR       |      |

| TABLE 21 | - RECEIVE DATA LINK OUTPUT TIMING (FIGURE 46)                       | 234  |

| TABLE 22 | - RECOVERED FRAME PULSE OUTPUT TIMING (FIGURE 47)                   | 234  |

#### PM6344 EQUAD

#### STANDARD PRODUCT

| PMC-951013 | ISSUE 5                                   | QUADRUPLE E1 FRAMER     |  |

|------------|-------------------------------------------|-------------------------|--|

| TABLE 23   | - TRANSMIT INTERFACE OUTPUT TIMING (FIGUR | RE 48)235               |  |

| TABLE 24   | - TRANSMIT DATA LINK DMA INTERFACE OUTPU  | T TIMING (FIGURE 49)236 |  |

| TABLE 25   | - RECEIVE DATA LINK DMA INTERFACE OUTPUT  | TIMING (FIGURE 50)237   |  |

| TABLE 26   | - EQUAD ORDERING INFORMATION              | 239                     |  |

| TABLE 27   | - FOUAD THERMAL INFORMATION               | 239                     |  |

#### 1 FEATURES

- Integrates four full-featured E1 framers and transmitters in a single device for terminating duplex E1 signals.

- Software and functionally compatible with the PM6341 E1XC Single E1 Transceiver.

- Pin compatible with the PM4344 Quad T1 Framer device.

- Provides an 8-bit microprocessor bus interface for configuration, control, and status monitoring.

- Low power CMOS technology

- Available in a 128 pin PQFP package.

#### Each one of four receiver sections:

- Recovers clock and data using a digital phase locked loop for high jitter tolerance. A direct clock input is provided to allow clock recovery to be bypassed.

- Accepts dual rail or single rail digital PCM inputs.

- Supports HDB3 or AMI line code.

- Accepts gapped data streams to support higher rate demultiplexing.

- Frames to a G.704 2048 kbit/s signal within 1 ms.

- Frames to the signaling multiframe alignment when enabled.

- Frames to the CRC multiframe alignment when enabled.

- Provides loss of signal detection, and indicates loss of frame alignment (OOF), loss of signaling multiframe alignment and loss of CRC multiframe alignment.

- Supports line and path performance monitoring according to ITU-T recommendations. Accumulators are provided for counting:

- CRC-4 errors to 1000 per second;

Far end block errors to 1000 per second;

Frame sync errors to 127 per second; and

Line code violations to 8191 per second.

- Indicates the reception of remote alarm and remote multiframe alarm.

- Indicates the reception of alarm indication signal (AIS) and time slot 16 AIS.

- Declares RED and AIS alarms using Q.516 recommended integration periods.

- Provides an HDLC/LAPD interface for terminating a data link. Supports polled, interrupt-driven, or DMA servicing of the HDLC interface.

- Optionally extracts the data link from timeslot 16 (64 kbit/s), which may be used to receive common channel signaling, or from any combination of the national bits in timeslot 0 of non-frame alignment signal frames (4 kbit/s - 20 kbit/s).

- Supports fractional E1 channel extraction.

- Provides a two-frame elastic store buffer for jitter and wander attenuation that performs controlled slips and indicates slip occurrence and direction.

- Provides channel associated signaling extraction, with optional data inversion, programmable idle code substitution, and up to 3 multiframes of signaling debounce on a per-timeslot basis.

- Provides trunk conditioning which forces programmable trouble code substitution and signaling conditioning on all timeslots or on selected timeslots.

- Optionally provides dual rail digital PCM output signals to allow BPV transparency. Also supports unframed mode.

- Supports transfer of PCM and signaling data to 2.048 Mbit/s or 16.384Mbit/s backplane buses.

- Can be configured to attenuate jitter on the receive side by placing the digital jitter attenuator in the receive path.

#### Each one of four transmitter sections:

- Formats data to create a G.704 2048 kbit/s signal. Optionally inserts signaling multiframe alignment signal. Optionally inserts CRC multiframe structure including optional transmission of far end block errors.

- Optionally accepts dual rail digital PCM inputs to allow BPV transparency.

Also supports unframed mode and framing bit, CRC, or data link by-pass.

- Supports transfer of PCM and signaling data from 2.048 Mbit/s or 16.384Mbit/s backplane buses.

- Provides channel associated signaling insertion, programmable idle code substitution, digital milliwatt code substitution, and data inversion on a per timeslot basis.

- Provides trunk conditioning which forces programmable trouble code substitution and signaling conditioning on all timeslots or on selected timeslots.

- Supports transmission of the alarm indication signal (AIS), timeslot 16 AIS, remote alarm signal or remote multiframe alarm signal.

- Provides an HDLC/LAPD interface for generating a data link. Supports polled, interrupt-driven, or DMA servicing of the HDLC interface.

- Optionally inserts the data link into timeslot 16 (64 kbit/s), which may be used to transmit common channel signaling, or into any combination of the national bits in timeslot 0 of non-frame alignment signal frames (4 kbit/s - 20 kbit/s).

- Supports fractional E1 channel insertion.

- Provides a digital phase locked loop for generation of a low jitter transmit clock.

- Provides a FIFO buffer for jitter attenuation and rate conversion in the transmitter. FIFO full or empty indication allows for bit-stuffing in higher rate multiplexing applications.

- Supports HDB3 or AMI line code.

- Provides dual rail or single rail digital PCM output signals.

## **2 APPLICATIONS**

- E1 Channel Service Units (CSU) and Data Service Units (DSU)

- E1 Channel Banks and Multiplexers

- Digital Private Branch Exchanges (PBX)

- Digital Access and Cross-Connect Systems (DACS) and Electronic DSX Cross-Connect Systems (EDSX)

- E1 Frame Relay Interfaces

- E1 ATM Interfaces

- ISDN Primary Rate Interfaces (PRI)

- SDH Byte Synchronous TU12 Mappers

- Test Equipment

#### 3 REFERENCES

- 1. ITU-T Recommendation G.704, "Synchronous Frame Structures Used at Primary and Secondary Hierarchical Levels", Vol. III, Fascicle III.4, 1988.

- ITU-T Recommendation G.706, "Frame Alignment and Cyclic Redundancy Check (CRC) Procedures Relating to Basic Frame Structures Defined in Recommendation G.704", Vol. III, Fascicle III.4, 1988.

- ITU-T Recommendation G.706, "Frame Alignment and Cyclic Redundancy Check (CRC) Procedures Relating to Basic Frame Structures Defined in Recommendation G.704", 1991

- 4. ITU-T Recommendation G.711, "Pulse Code Modulation (PCM) of Voice Frequencies", Volume III, Fascicle III.3, 1988.

- 5. ITU-T Recommendation G.732, "Characteristics of Primary PCM Multiplex Equipment Operating at 2048 kbit/s", Vol. III, Fascicle III.4, 1988.

- 6. ITU-T Recommendation G.735, "Characteristics of Primary PCM Multiplex Equipment Operating at 2048 kbit/s and Offering Synchronous Digital Access at 384 kbit/s and/or 64 kbit/s", Vol. III, Fascicle III.4, 1988.

- 7. ITU-T Recommendation G.821, "Error Performance of an International Digital Connection Forming Part of an Integrated Services Digital Network", Vol. III, Fascicle III.5, 1988.

- 8. ITU-T Recommendation G.823, "The Control of Jitter and Wander Within Digital Networks Which are Based on the 2048 kbit/s Hierarchy", Vol. III, Fascicle III.5, 1988.

- 9. ITU-T Recommendation O.151, "Error Performance Measuring Equipment For Digital Systems at the Primary Bit Rate and Above", Vol. IV, Fascicle IV.4, 1988.

- 10. ITU-T Blue Book, Recommendation O.162, "Equipment to Perform in Service Monitoring on 2048 kbit/s Signals", Vol. IV, Fascicle IV.4, 1988.

- 11. ITU-T Recommendation Q.506, "Operations and maintenance functions", Vol. VI, Fascicle VI.5, 1984.

- 12.ITU-T Recommendation Q.516, "Operations and maintenance functions", Vol. VI, Fascicle VI.5, 1984.

PM6344 EQUAD

STANDARD PRODUCT

PMC-951013 ISSUE 5 QUADRUPLE E1 FRAMER

13. Transmission and Multiplexing (TM); Generic Functional Requirements for SDH Transmission Equipment, Part 1: Generic Processes and Performance", ETSI DE/TM-1015, November, 1993, Version 1.0.

#### 4 APPLICATION EXAMPLES

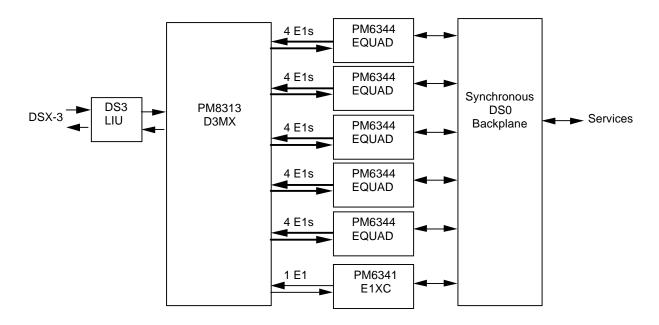

Figure 1 - Example 1. DS-3 Terminal Multiplexer/Channel Bank

Example 1 shows a DS-3 Terminal Multiplexer/Channel Bank using 5 EQUAD devices, PMC-Sierra's PM8313 D3MX M13 Multiplexer, the PM6341 E1XC E1 Transceiver, and Silicon System's SSI 78P236 DS-3 Line Interface Unit.

21 E1 signals can be multiplexed into a DSX-3 formatted signal. Five EQUAD devices and a single E1XC device are used to terminate these 21 signals. The DS-0 backplane data is transmitted and received using a 2.048 MHz system clock.

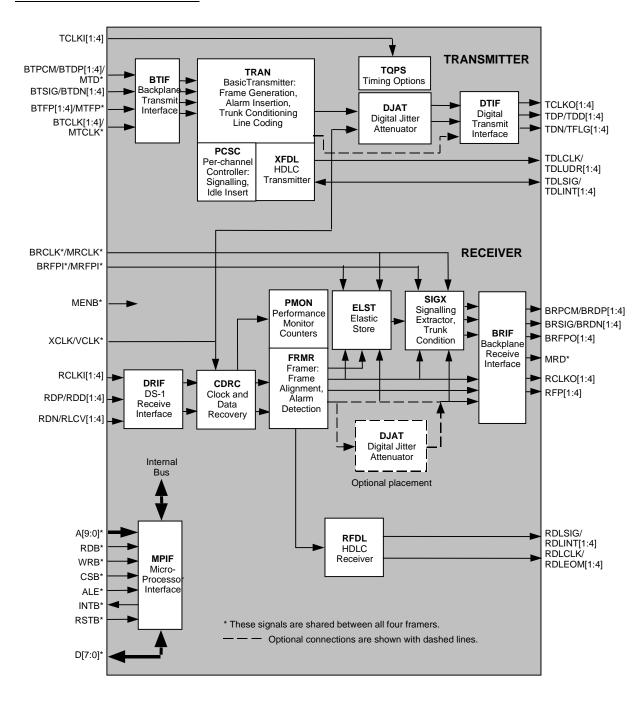

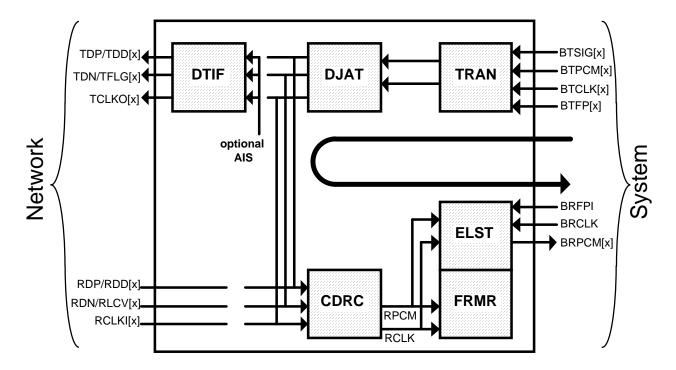

### 5 BLOCK DIAGRAM

#### **Description**

The PM6344 Quadruple E1 Framer (EQUAD) is a feature-rich device suitable for use in many E1 systems with a minimum of external circuitry. Each of the framers and transmitters is independently software configurable, allowing feature selection without changes to external wiring.

On the receive side, the EQUAD recovers clock and data and can be configured to frame to a basic G.704 2048 kbit/s signal or also frame to the signaling multiframe alignment signal and the CRC multiframe alignment signal.

The EQUAD also supports detection of various alarm conditions such as loss of signal, loss of frame, loss of signaling multiframe, loss of CRC multiframe, and reception of remote alarm signal, remote multiframe alarm signal, alarm indication signal, and timeslot 16 alarm indication signal. The EQUAD detects and indicates the presence of remote alarm and AIS patterns and also integrates red and AIS alarms as per industry specifications.

Performance monitoring with accumulation of CRC-4 errors, far end block errors, framing bit errors, and line code violation is provided. The EQUAD also detects and terminates HDLC messages on a data link. The data link may be extracted from timeslot 16 and used for common channel signaling or may be extracted from the national bits.

An elastic store for slip buffering and adaptation to backplane timing is provided, as is a signaling extractor that supports signaling debounce, signaling freezing, idle code substitution, digital milliwatt tone substitution, data inversion, and signaling bit fixing on a per-channel basis. Receive side data and signaling trunk conditioning is also provided.

On the transmit side, the EQUAD generates framing for a basic G.704 2048 kbit/s signal, or framing can be optionally disabled. The signaling multiframe alignment structure may be optionally inserted and the CRC multiframe structure may be optionally inserted.

Channel associated signaling insertion, idle code substitution, digital milliwatt tone substitution, and data inversion on a per-timeslot basis is also supported. Transmit side data and signaling trunk conditioning is provided.

HDLC messages on a data link can be transmitted. The data link may be inserted into timeslot 16 and used for common channel signaling or may be inserted into the national bits. The EQUAD can generate a low jitter transmit clock and provides a FIFO for transmit jitter attenuation. When not used for jitter

PM6344 EQUAD

STANDARD PRODUCT

PMC-951013 ISSUE 5 QUADRUPLE E1 FRAMER

attenuation, the full or empty status of this FIFO is made available to facilitate higher order multiplexing applications by controlling bit-stuffing logic.

The EQUAD provides a parallel microprocessor interface for controlling the operation of the EQUAD device. Serial PCM interfaces allow 2.048 Mbit/s backplanes to be directly supported. Tolerance of gapped clocks allows other backplane rates to be supported with a minimum of external logic. Optional bit interleaved multiplexing of the individual serial streams supports 16.384 Mbit/s backplanes.

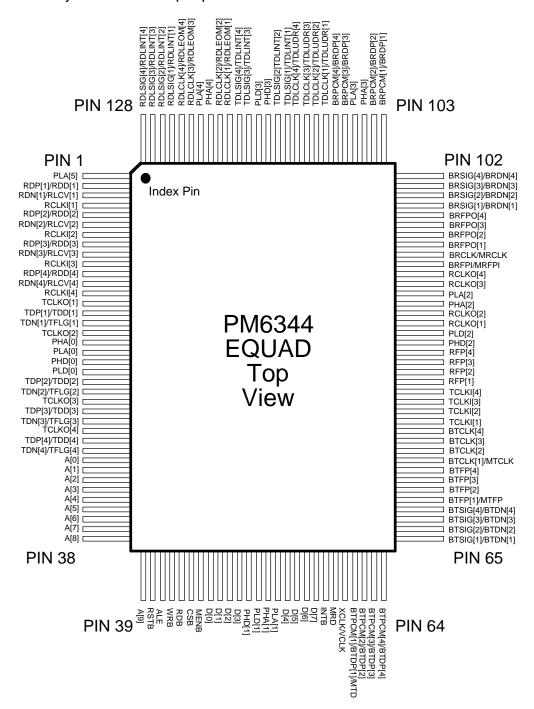

#### 6 PIN DIAGRAM

The EQUAD is packaged in a 128-pin plastic QFP package having a body size of 14 mm by 20 mm and a pin pitch of 0.5 mm.

# **7 PIN DESCRIPTION**

| Pin Name                               | Туре  | Pin No.           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MENB                                   | Input | 45                | Multiplex Enable (MENB). When this input is asserted low, the four sets of PCM and signaling streams are combined into a single bit interleaved 16.384 Mbit/s serial stream. In the transmit direction, all data is expected on MTD with alignment indicated by MTFP. MTD and MTFP are sampled on the rising edge of MTCLK. In the receive direction, data is presented on MRD aligned with MRFPI. MRFPI is sampled on the rising edge of MRCLK and MRD is updated on the falling edge of MRCLK. |

|                                        |       |                   | When this input is deasserted high, each PCM and signaling stream has its own dedicated pin.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                        |       |                   | MENB has an integral pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RDP[1]<br>RDP[2]<br>RDP[3]<br>RDP[4] / | Input | 2<br>5<br>8<br>11 | Receive Positive Line Pulse (RDP[4:1]). These inputs are available when the EQUAD is configured to receive dual-rail formatted data. The RDP[4:1] inputs may be enabled for either RZ or NRZ waveforms. When enabled for NRZ, this input may be enabled to be sampled on the rising or falling edge of the corresponding RCLKI[4:1]. When enabled for RZ, the clocks are recovered from the corresponding RDP[4:1] and RDN[4:1] inputs.                                                          |

| RDD[1]<br>RDD[2]<br>RDD[3]<br>RDD[4]   |       |                   | Receive Digital E1 Signal (RDD[4:1]). When the EQUAD is configured to receive single-rail data, these inputs may be enabled to be sampled on the rising or falling edge of the corresponding RCLKI[4:1].                                                                                                                                                                                                                                                                                         |

| Pin Name                                     | Туре   | Pin No.              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------|--------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDN[1]<br>RDN[2]<br>RDN[3]<br>RDN[4] /       | Input  | 3<br>6<br>9<br>12    | Receive Digital Negative Line Pulse (RDN[4:1]). These inputs are available when the EQUAD is configured to receive dual-rail formatted data. The RDN[4:1] inputs may be enabled for either RZ or NRZ waveforms. When enabled for NRZ, these inputs may be enabled to be sampled on the rising or falling edge of the corresponding RCLKI[4:1]. When enabled for RZ, the clocks are recovered from the corresponding RDP[4:1] and RDN[4:1] inputs. |

| RLCV[1]<br>RLCV[2]<br>RLCV[3]<br>RLCV[4]     |        |                      | Receive Line Code Violation Indication (RLCV[4:1]). When the EQUAD is configured to receive single-rail data, this input may be enabled to be sampled on the rising or falling edge of the corresponding RCLKI[4:1].                                                                                                                                                                                                                              |

| RCLKI[1]<br>RCLKI[2]<br>RCLKI[3]<br>RCLKI[4] | Input  | 4<br>7<br>10<br>13   | Receive Line Clock Inputs (RCLKI[4:1]). Each input is an externally recovered 2.048 MHz line clock that may be enabled to sample the RDP[x] and RDN[x] inputs on its rising or falling edge when the input format is enabled for dual-rail NRZ; or to sample the RDD[x] and RLCV[x] inputs on its rising or falling edge when the input format is enabled for single-rail.                                                                        |

| RCLKO[1]<br>RCLKO[2]<br>RCLKO[3]<br>RCLKO[4] | Output | 87<br>88<br>91<br>92 | Recovered PCM Clock Output (RCLKO[4:1]). Each output signal is the recovered 2.048 MHz clock, synchronized to the XCLK signal. Each RCLKO[x] signal is recovered from the RDP[x] and RDN[x] inputs (if the input format is dual-rail RZ) or from the RCLKI[x] input (if the input format is NRZ).                                                                                                                                                 |

|                                              |        |                      | When the ELST is by-passed or the RCLKOSEL register bit is set, BRPCM[x] and BRSIG[x] are updated on the falling edge of the associated RCLKO[x].                                                                                                                                                                                                                                                                                                 |

|                                              |        |                      | As an option, the digital attenuator's smooth 2.048 MHz clock may be presented on RCLKO[x]. See the Operations Section for details on this application.                                                                                                                                                                                                                                                                                           |

| Pin Name         | Туре   | Pin No.         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFP[1]<br>RFP[2] | Output | Output 81<br>82 | Receive Frame Pulse (RFP[4:1]). The RFP[x] outputs are intended as a timing references.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RFP[3]<br>RFP[4] |        | 83<br>84        | When the EQUAD is configured for receive frame pulse output, RFP[x] pulses high for 1 RCLKO cycle during bit 1 of each 256-bit frame, indicating the frame alignment of the receive stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                  |        |                 | When configured for receive signaling multiframe output, RFP[x] pulses high for 1 RCLKO[x] cycle during bit 1 of frame 1 of the 16 frame signaling multiframe, indicating the signaling multiframe alignment of the receive stream. (Even when signaling multiframing is disabled, the RFP[x] output continues to indicate the position of bit 1 of every 16 <sup>th</sup> frame.)                                                                                                                                                                                                                                                                                                   |

|                  |        |                 | When configured for receive CRC multiframe output, RFP[x] pulses high for 1 RCLKO[x] cycle during bit 1 of frame 1 of every 16 frame CRC multiframe, indicating the CRC multiframe alignment of the receive stream. (Even when CRC multiframing is disabled, the RFP[x] output continues to indicate the position of bit 1 of the FAS frame every 16 <sup>th</sup> frame.)                                                                                                                                                                                                                                                                                                           |

|                  |        |                 | When configured for composite multiframe output, RFP[x] goes high on the falling RCLKO[x] edge marking the beginning of bit 1 of frame 1 of every 16 frame signaling multiframe, indicating the signaling multiframe alignment of the receive stream, and returns low on the falling RCLKO[x] edge marking the ending of bit 1 of frame 1 of every 16 frame CRC multiframe, indicating the CRC multiframe alignment of the receive stream. This mode allows both multiframe alignments to be decoded externally from the single RFP[x] signal. Note that if the signaling and CRC multiframe alignments are coincident, RFP[x] will pulse high for 1 RCLKO[x] cycle every 16 frames. |

|                  |        |                 | Each RFP[x] is updated on the falling edge of the associated RCLKO[x]. RFP[x] should not be used when register bit RCLKOSEL is set to a logic 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin Name                                          | Туре   | Pin No.                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------|--------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

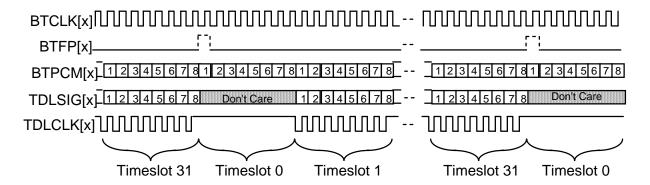

| RDLSIG[1]<br>RDLSIG[2]<br>RDLSIG[3]<br>RDLSIG[4]/ | Output | 125<br>126<br>127<br>128 | Receive Data Link Signal (RDLSIG[4:1]). The RDLSIG[4:1] signals are available on these outputs when the associated internal HDLC receiver (RFDL) is disabled from use, or, optionally, when fractional E1 is extracted. RDLSIG contains the data link stream extracted from the selected data link bits. The EQUAD may be configured to utilize timeslot 16 as a data link or utilize any combination of the national bits as a data link. Each RDLSIG[x] is updated on the falling edge of the associated RDLCLK[x]. |

| RDLINT[1]<br>RDLINT[2]<br>RDLINT[3]<br>RDLINT[4]  |        |                          | Receive Data Link Interrupt (RDLINT[4:1]). The RDLINT[4:1] signals are available on these outputs when the associated RFDL is enabled. Each RDLINT[x] goes high when an event occurs which changes the status of the associated HDLC receiver.                                                                                                                                                                                                                                                                        |

| RDLCLK[1]<br>RDLCLK[2]<br>RDLCLK[3]<br>RDLCLK[4]/ | Output | 119<br>120<br>123<br>124 | Receive Data Link Clock (RDLCLK[4:1]). The RDLCLK[4:1] signals are available on these outputs when the associated internal HDLC receiver (RFDL) is disabled from use, or, optionally, when fractional E1 is extracted. The rising edge of RDLCLK[x] can be used to sample the data-link data or the fractional E1 data on the associated RDLSIG[x] when the internal HDLC receiver is disabled or when fractional E1 is enabled respectively.                                                                         |

| RDLEOM[1]<br>RDLEOM[2]<br>RDLEOM[3]<br>RDLEOM[4]  |        |                          | Receive Data Link End of Message (RDLEOM[4:1]). The RDLEOM[4:1] signals are available on these outputs when the associated RFDL is enabled. Each RDLEOM[x] goes high when the last byte of a received sequence is read from the associated RFDL FIFO buffer, or when the FIFO buffer is overrun.                                                                                                                                                                                                                      |

| Pin Name                                      | Туре   | Pin No.                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------|--------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRPCM[1]<br>BRPCM[2]<br>BRPCM[3]<br>BRPCM[4]/ | Output | 103<br>104<br>107<br>108 | Backplane Receive PCM (BRPCM[4:1]). The BRPCM[4:1] signals are available on these outputs when the backplane is configured for single-rail output. Each BRPCM[x] signal contains the recovered data stream passed through the ELST block, and the SIGX block. When the ELST is not by-passed or the RCLKOSEL register bit is not set, the BRPCM[x] stream is aligned to the backplane timing and is updated on the falling edge of the associated BRCLK. When the ELST is by-passed or the RCLKOSEL register bit is set, BRPCM[x] is aligned to the receive line timing and is updated on the falling edge of the associated RCLKO[x]. |

| BRDP[1]<br>BRDP[2]<br>BRDP[3]<br>BRDP[4]      |        |                          | Backplane Receive Positive Line Pulse (BRDP[4:1]). The BRDP[4:1] signals are available on these outputs when the backplane is configured for dual-rail output. Each BRDP[x] NRZ output represents the RZ receive digital positive pulse signal extracted from the input bipolar signal. BRDP[x] is updated on the falling edge of the associated RCLKO[x].                                                                                                                                                                                                                                                                             |

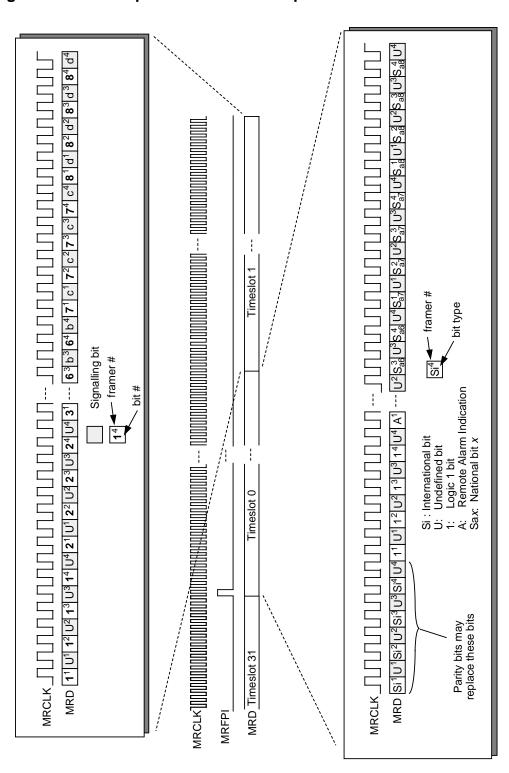

| MRD                                           | Output | 59                       | Multiplexed Receive Data (MRD). When the multiplex enable (MENB) input is asserted low, the four sets of PCM and signaling streams are bit interleaved into a single 16.384 Mbit/s serial stream presented on MRD aligned with MRFPI. MRFPI is sampled on the rising edge of MRCLK and MRD is updated on the falling edge of MRCLK.                                                                                                                                                                                                                                                                                                    |

|                                               |        |                          | When MENB input is deasserted high, each PCM and signaling stream has its own dedicated pin and MRD is unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pin Name                                     | Туре   | Pin No.                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRSIG[1]<br>BRSIG[2]<br>BRSIG[3]<br>BRSIG[4] | Output | 99<br>100<br>101<br>102 | Backplane Receive Signaling (BRSIG[4:1]). The BRSIG[4:1] signals are available on these outputs when the backplane is configured for single-rail output. Each BRSIG[x] contains the extracted signaling bits for each channel in the frame, repeated for the entire superframe. Each channel's signaling bits are valid in bit locations 5,6,7,8 of the channel and are channel-aligned with the BRPCM[x] data stream. When the ELST is not by-passed or the RCLKOSEL register bit is not set, the BRSIG[x] stream is aligned to the backplane timing and is updated on the falling edge of BRCLK. When the ELST is by-passed or the RCLKOSEL register bit is set, BRSIG[x] is aligned to the receive line timing and is updated on the falling edge of the associated RCLKO[x]. |

| BRDN[1]<br>BRDN[2]<br>BRDN[3]<br>BRDN[4]     |        |                         | Backplane Receive Negative Line Pulse (BRDN[4:1]). The BRDN[4:1] signals are available on these outputs when the backplane is configured for dual-rail output. Each BRDN[x] NRZ output represents the RZ receive digital negative pulse signal extracted from the input bipolar signal. BRDN[x] is updated on the falling edge of the associated RCLKO[x].                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pin Name                                     | Туре   | Pin No.              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|--------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRFPO[1]<br>BRFPO[2]<br>BRFPO[3]<br>BRFPO[4] | Output | 95<br>96<br>97<br>98 | Backplane Frame Pulse Output (BRFPO[4:1]). When the EQUAD is configured for backplane receive frame pulse output, each BRFPO[x] pulses high for 1 BRCLK cycle (or 1 RCLKO[x] cycle if ELST is by-passed or the RCLKOSEL register bit is set) during bit 1 of each 256-bit frame, indicating the frame alignment of the BRPCM[x] data stream.                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                              |        |                      | When configured for backplane receive signaling multiframe output, BRFPO[x] pulses high for 1 BRCLK cycle (or 1 RCLKO[x] cycle if ELST is by-passed) during bit 1 of frame 1 of the 16 frame signaling multiframe, indicating the signaling multiframe alignment of the BRPCM[x] data stream. (Even when signaling multiframing is disabled, the BRFPO[x] output continues to indicate every 16 <sup>th</sup> frame.)                                                                                                                                                                                                                                                                                                                                           |

|                                              |        |                      | When configured for backplane receive CRC multiframe output, BRFPO[x] pulses high for 1 BRCLK cycle (or 1 RCLKO[x] cycle if ELST is by-passed) during bit 1 of frame 1 of every 16 frame CRC multiframe, indicating the CRC multiframe alignment of the BRPCM[x] data stream. (Even when CRC multiframing is disabled, the BRFPO[x] output continues to indicate the position of bit 1 of the FAS frame every 16 <sup>th</sup> frame.)                                                                                                                                                                                                                                                                                                                          |

|                                              |        |                      | When configured for backplane receive composite multiframe output, BRFPO[x] goes high on the falling BRCLK edge (or RCLKO[x] edge if ELST is by-passed) marking the beginning of bit 1 of frame 1 of every 16 frame signaling multiframe, indicating the signaling multiframe alignment of the BRPCM[x] data stream, and returns low on the falling BRCLK edge (or RCLKO[x] edge if ELST is by-passed) marking the end of bit 1 of frame 1 of every 16 frame CRC multiframe, indicating the CRC multiframe alignment of the BRPCM[x] data stream. In this mode both multiframe alignments can be decoded externally from the single BRFPO[x] signal. If the signaling and CRC multiframe alignments are coincident, BRFPO[x] will pulse high for 1 clock cycle. |

|                                              |        |                      | When configured for backplane receive overhead output, BRFPO[x] is high for timeslot 0 and timeslot 16 of each 256-bit frame, indicating the overhead bit positions of the BRPCM[x] data stream.  BRFPO[x] is updated on the falling edge of the BRCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                              |        |                      | or RCLKO[x].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin Name | Туре  | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRCLK    | Input | 94      | Backplane Receive Clock (BRCLK). When the multiplex enable (MENB) input is deasserted high, BRCLK is a 2.048MHz clock with optional gapping for adaptation to non-uniform backplane data streams. BRCLK is common to all four framers. The EQUAD may be configured to ignore the BRCLK input and use the RCLKO[x] signal in its place when the ELST is bypassed or the RCLKOSEL register bit is set. |

| MRCLK    |       |         | Multiplex Receive Clock (MRCLK). When the multiplex enable (MENB) input is asserted low, MRCLK is a 16.384 MHz clock. MRFPI is sampled on the rising edge of MRCLK and MRD is updated on the rising edge of MRCLK. The multiplexed bus can not be used if the ELST is bypassed or the RCLKOSEL register bit is set.                                                                                  |

| BRFPI    | Input | 93      | Backplane Frame Pulse Input (BRFPI). When the multiplex enable (MENB) input is deasserted high, this input is used to frame align the received data to the system backplane. BRFPI is common to all four framers. If frame alignment only is required, a pulse at least 1 BRCLK cycle wide must be provided on each BRFPI every 256 bit periods.                                                     |

| MRFPI    |       |         | Multiplexed Frame Pulse Input (MRFPI). When the multiplex enable (MENB) input is asserted low, this input aligns all four sets of PCM and signaling streams to allow bit interleaved multiplexing. If frame alignment only is required, a pulse no more than 1 MRCLK cycle wide must be provided on each MRFPI every 2048 bit periods.                                                               |

| Pin Name                                      | Туре  | Pin No.              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------|-------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

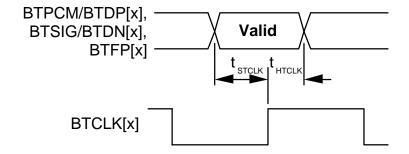

| BTPCM[1]<br>BTPCM[2]<br>BTPCM[3]<br>BTPCM[4]/ | Input | 61<br>62<br>63<br>64 | Backplane Transmit PCM (BTPCM[4:1]). The non-return to zero, digital data streams to be transmitted are input on these pins when the backplane is configured for non-multiplexed single-rail input. The BTPCM[x] signal is sampled on the rising edge of the associated BTCLK[x].                                                                                                                                                                                                                        |

| BTDP[1]<br>BTDP[2]<br>BTDP[3]<br>BTDP[4]      |       |                      | Backplane Transmit Positive Line Pulse (BTDP[4:1]). The positive pulse of the dual-rail signals to be transmitted is input on these pins when the backplane is configured for non-multiplexed dual-rail input. In dual-rail input mode, the BTDP[x] input by-passes the transmitter and is fed directly into the DJAT. BTDP[x] is sampled on the rising edge of the associated BTCLK[x].                                                                                                                 |

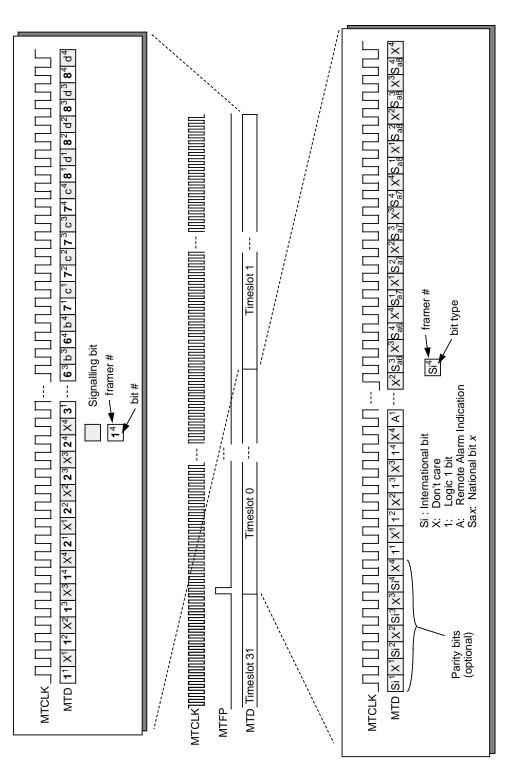

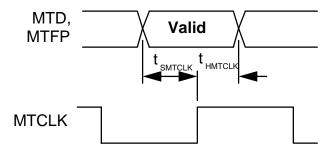

| MTD                                           |       |                      | Multiplexed Transmit Data (MTD). MTD shares a pin with BTPCM[1]. BTPCM[4:2] are unused when the multiplex enable (MENB) input is asserted low. When the multiplex enable (MENB) input is asserted low, the four sets of PCM and signaling streams are expected in a single bit interleaved 16.384 Mbit/s serial stream. Frame alignment is indicated by MTFP. MTD is sampled on the rising edge of MTCLK.                                                                                                |

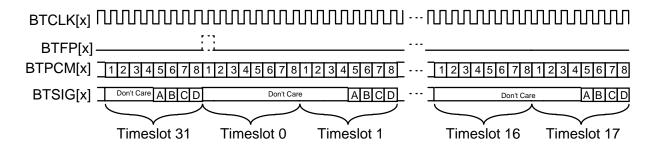

| BTSIG[1]<br>BTSIG[2]<br>BTSIG[3]<br>BTSIG[4]  | Input | 65<br>66<br>67<br>68 | Backplane Transmit Signaling (BTSIG[4:1]). The BTSIG[4:1] input signals contain the signaling bits for each channel in the transmit data frame, repeated for the entire superframe. Each signal is input on the BTSIG[x] pin when the backplane is configured for non-multiplexed single-rail input. Each channel's signaling bits are in bit locations 5,6,7,8 of the channel and are channel-aligned with the BTPCM[x] data stream. BTSIG[x] is sampled on the rising edge of the associated BTCLK[x]. |

|                                               |       |                      | If frame alignment is not required, BTFP[x] may be tied to power or ground.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BTDN[1]<br>BTDN[2]<br>BTDN[3]<br>BTDN[4]      |       |                      | Backplane Transmit Negative Line Pulse (BTDN[4:1]). The negative pulse of the dual-rail signal to be transmitted is input on these pins when the backplane is configured for non-multiplexed dual-rail input. In dual-rail input mode, the BTDN[x] input by-passes the transmitter and is fed directly into the DJAT. BTDN[x] is sampled on the rising edge of the associated BTCLK[x].                                                                                                                  |

|                                               |       |                      | These inputs are unused when the multiplex enable (MENB) input is asserted low.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin Name                                 | Туре  | Pin No.              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------|-------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BTFP[1]<br>BTFP[2]<br>BTFP[3]<br>BTFP[4] | Input | 69<br>70<br>71<br>72 | Backplane Transmit Frame Pulse (BTFP[4:1]). These inputs are used to frame align the transmitters to the system backplane. If basic frame alignment only is required, a pulse at least 1 BTCLK[x] cycle wide must be provided on BTFP[x] at multiples of 256 bit periods. If multiframe alignment is required, transmit multiframe alignment must be enabled, and BTFP[x] must be brought high to mark bit 1 of frame 1 of every 16 frame signaling multiframe and brought low following bit 1 of frame 1 of every 16 frame CRC multiframe. This mode allows both multiframe alignments to be independently controlled using the single BTFP[x] signal. Note that if the signaling and CRC multiframe alignments are coincident, BTFP[x] must pulse high for 1 BTCLK[x] cycle every 16 frames. If register bit BTFPREF is set to logic 1, BTFP[x] becomes the reference frame pulse for the associated interface.                                                                                                                                                                                                                                                                                                 |

|                                          |       |                      | If frame alignment is not required, BTFP[x] may be tied to logic high or low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MTFP                                     |       |                      | Multiplexed Transmit Frame Pulse (MTFP). MTFP shares a pin with BTFP[1]. BTFP[4:2] are unused when the multiplex enable (MENB) input is asserted low. When the multiplex enable (MENB) input is asserted low, MTFP indicates the frame alignment of the bit interleaved PCM and signaling streams in the same way as BTFP[x]. If basic frame alignment only is required, a pulse 1 MTCLK cycle wide must be provided on MTFP at multiples of 2048 clock periods. If multiframe alignment is required, transmit multiframe alignment must be enabled, and MTFP must be brought high to mark bit 1 of frame 1 of the first multiplexed PCM stream (destined for transmitter number one) of every 16 frame signaling multiframe and brought low following bit 1 of frame 1 of the first multiplexed PCM stream of every 16 frame CRC multiframe. This mode allows both multiframe alignments to be independently controlled using the single MTFP signal. All four interfaces will have the same frame alignment. Note that if the signaling and CRC multiframe alignments are coincident, MTFP must pulse high for 1 MTCLK cycle every 16 frames (32768 clock cycles). MTFP is sampled on the rising edge of MTCLK. |

| Pin Name                                          | Туре  | Pin No.                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------|-------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BTCLK[1]<br>BTCLK[2]<br>BTCLK[3]<br>BTCLK[4]      | Input | 73<br>74<br>75<br>76     | Backplane Transmit Clock (BTCLK[4:1]). BTCLK[4:1] are the 2.048MHz transmit clocks with optional gapping for adaptation from non-uniform backplane data streams. The EQUAD may be configured to ignore the BTCLK[x] input and use the associated RCLKO[x] signal in its place.                                                                                                                                                              |

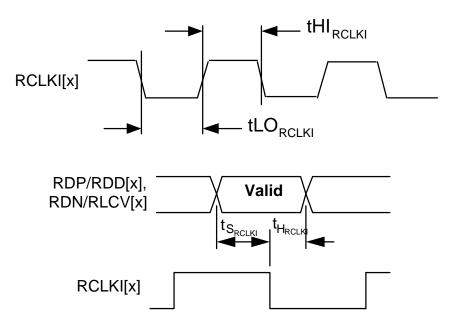

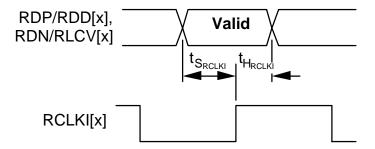

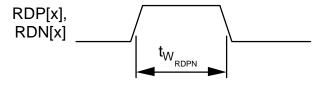

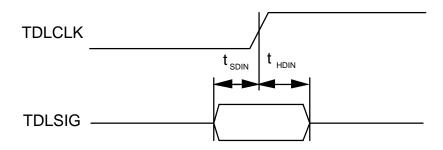

| MTCLK                                             |       |                          | Multiplexed Transmit Clock (MTCLK). MTCLK shares a pin with BTCLK[1]. BTCLK[4:2] are unused when the multiplex enable (MENB) input is asserted low. When the multiplex enable (MENB) input is asserted low, this clock is 16.384 MHz. MTFP and MTD are sampled on the rising edge of MTCLK.                                                                                                                                                 |