查询PM7350供应商

#### 捷多邦,专业PCB打样工厂,24小时加急出货

RELEASED

DATA SHEET PMC-1980581

PM7350 S/UNI-DUPLEX

ISSUE 5

**DUAL SERIAL LINK PHY MULTIPLEXER**

**PM7350**

# S/UNI-DUPLEX

DUAL SERIAL LINK, PHY MULTIPLEXER

**DATA SHEET**

**RELEASED**

**ISSUE 5: APRIL 2000**

DATA SHEET PMC-1980581

DUAL SERIAL LINK PHY MULTIPLEXER

## **REVISION HISTORY**

| Issue No. | Issue Date       | Originator       | Details of Change                                                                                               |

|-----------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------|

| Issue 5   | April 2000       | Phil Walston     | Updated analog parameters, IDDOP, thermal info and corrected register description typos. Release to production. |

| Issue 4   | February<br>2000 | Phil Walston     | Updated to incorporate Revision B changes outinled in previous Errata. Change bars highlight specific changes.  |

| Issue 3   | June 1999        | James<br>Lamothe | Changed confidentiality notices for document's public release.                                                  |

| Issue 2   | May, 1999        | Jeff Brown       | Extensive updates throughout                                                                                    |

| Issue 1   | May, 1998        | Jeff Brown       | First release                                                                                                   |

DATA SHEET

PMC-1980581 ISSUE 5

DUAL SERIAL LINK PHY MULTIPLEXER

## **CONTENTS**

| 1  | FEAT  | TURES                                   | 1   |

|----|-------|-----------------------------------------|-----|

| 2  | APPI  | LICATIONS                               | 3   |

| 3  | REF   | ERENCES                                 | 4   |

| 4  | APPI  | LICATION EXAMPLES                       | 5   |

| 5  | BLO   | CK DIAGRAM                              | 11  |

| 6  | DES   | CRIPTION                                | 12  |

| 7  | PIN [ | DIAGRAM                                 | 14  |

| 8  | PIN [ | DESCRIPTION                             | 15  |

| 9  | FUN   | CTIONAL DESCRIPTION                     | 45  |

|    | 9.1   | PARALLEL BUS INTERFACE                  | 45  |

|    | 9.2   | CLOCKED SERIAL DATA INTERFACE           | 57  |

|    | 9.3   | HIGH-SPEED SERIAL INTERFACE             | 61  |

|    | 9.4   | CELL BUFFERING AND FLOW CONTROL         | 71  |

|    | 9.5   | TIMING REFERENCE INSERTION AND RECOVERY | 75  |

|    | 9.6   | JTAG TEST ACCESS PORT                   | 76  |

|    | 9.7   | MICROPROCESSOR INTERFACE                | 76  |

|    | 9.8   | INTERNAL REGISTERS                      | 80  |

|    | 9.9   | REGISTER MEMORY MAP                     | 80  |

| 10 | NOR   | MAL MODE REGISTER DESCRIPTION           | 84  |

| 11 | TEST  | FEATURES DESCRIPTION                    | 170 |

|    | 11.1  | RAM BUILT-IN-SELF-TEST                  | 173 |

|    | 11.2  | JTAG TEST PORT                          | 177 |

| DATA SHEET  |

|-------------|

| PMC-1980581 |

ISSUE 5 DUAL SERIAL LINK PHY MULTIPLEXER

| 12 | OPERATION                                            |

|----|------------------------------------------------------|

|    | 12.1 MICROPROCESSOR INBAND COMMUNICATION 182         |

|    | 12.2 INTERACTION BETWEEN BUS AND LVDS CONFIGURATIONS |

|    | 12.3 MAXIMUM CELL BIT RATE                           |

|    | 12.4 MINIMUM PROGRAMMING                             |

|    | 12.5 JTAG SUPPORT                                    |

| 13 | FUNCTIONAL TIMING                                    |

|    | 13.1 SCI-PHY/ANY-PHY INTERFACE                       |

|    | 13.2 CLOCKED SERIAL DATA INTERFACE                   |

| 14 | ABSOLUTE MAXIMUM RATINGS                             |

| 15 | D.C. CHARACTERISTICS                                 |

| 16 | MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS 215  |

| 17 | A.C. TIMING CHARACTERISTICS                          |

| 18 | ORDERING AND THERMAL INFORMATION                     |

| 19 | MECHANICAL INFORMATION227                            |

DUAL SERIAL LINK PHY MULTIPLEXER

## **LIST OF REGISTERS**

|                | MASTER RESET AND IDENTITY / LOAD PERFORMANC |     |

|----------------|---------------------------------------------|-----|

| REGISTER 0X01: | MASTER CONFIGURATION                        | 86  |

| REGISTER 0X02: | MASTER INTERRUPT STATUS                     | 88  |

| REGISTER 0X03: | MISCELLANEOUS INTERRUPT STATUS              | 90  |

| REGISTER 0X04: | CLOCK MONITOR                               | 92  |

| REGISTER 0X05: | SERIAL LINKS MAINTENANCE                    | 94  |

| REGISTER 0X06: | EXTENDED ADDRESS MATCH (LSB)                | 96  |

| REGISTER 0X07: | EXTENDED ADDRESS MATCH (MSB)                | 97  |

| REGISTER 0X08: | EXTENDED ADDRESS MASK (LSB)                 | 98  |

| REGISTER 0X09: | EXTENDED ADDRESS MASK (MSB)                 | 99  |

| REGISTER 0X0A: | OUTPUT ADDRESS MATCH1                       | 100 |

| REGISTER 0X0B: | CONFIGURATION PINS STATUS1                  | 101 |

| REGISTER 0X0C: | SCI-PHY/ANY-PHY INPUT CONFIGURATION 1 1     | 103 |

| REGISTER 0X0D: | SCI-PHY/ANY-PHY INPUT CONFIGURATION 2 1     | 105 |

| REGISTER 0X0E: | SCI-PHY/ANY-PHY INPUT INTERRUPT ENABLES 1   | 107 |

| REGISTER 0X0F: | SCI-PHY/ANY-PHY INPUT INTERRUPT STATUS 1    | 108 |

| REGISTER 0X10: | INPUT CELL AVAILABLE ENABLE (LSB)           | 109 |

| REGISTER 0X11: | INPUT CELL AVAILABLE ENABLE (2ND) 1         | 109 |

| REGISTER 0X12: | INPUT CELL AVAILABLE ENABLE (3RD)           | 110 |

| REGISTER 0X13: | INPUT CELL AVAILABLE ENABLE (MSB)           | 110 |

| REGISTER 0X14: | SCI-PHY/ANY-PHY OUTPUT CONFIGURATION        | 112 |

| REGISTER 0X15: | SCI-PHY/ANY-PHY OUTPUT POLLING RANGE        | 115 |

PMC-1980581

ISSUE 5

| REGISTERS 0X18, 0X1A: RXD1, RXD2 BIT ORIENTED CODE RECEIVER ENABLE |     |

|--------------------------------------------------------------------|-----|

| REGISTER 0X19, 0X1B: RXD1, RXD2 RECEIVE BIT ORIENTED CODE STATUS   | 117 |

| REGISTERS 0X1D, 0X1F: TXD1, TXD2 TRANSMIT BIT ORIENTED CODE.       | 118 |

| REGISTER 0X20: MICROPROCESSOR CELL BUFFER INTERRUPT                | 119 |

| REGISTER 0X21: MICROPROCESSOR INSERT FIFO CONTROL                  | 121 |

| REGISTER 0X22: MICROPROCESSOR EXTRACT FIFO CONTROL                 | 122 |

| REGISTER 0X23: MICROPROCESSOR INSERT FIFO READY                    | 124 |

| REGISTER 0X24: MICROPROCESSOR EXTRACT FIFO READY                   | 125 |

| REGISTER 0X25: INSERT CRC-32 ACCUMULATOR (LSB)                     | 126 |

| REGISTER 0X26: INSERT CRC-32 ACCUMULATOR (2ND)                     | 126 |

| REGISTER 0X27: INSERT CRC-32 ACCUMULATOR (3RD)                     | 126 |

| REGISTER 0X28: INSERT CRC-32 ACCUMULATOR (MSB)                     | 127 |

| REGISTER 0X29: EXTRACT CRC-32 ACCUMULATOR (LSB)                    | 128 |

| REGISTER 0X2A: EXTRACT CRC-32 ACCUMULATOR (2ND)                    | 128 |

| REGISTER 0X2B: EXTRACT CRC-32 ACCUMULATOR (3RD)                    | 128 |

| REGISTER 0X2C: EXTRACT CRC-32 ACCUMULATOR (MSB)                    | 129 |

| REGISTER 0X2D: MICROPROCESSOR CELL DATA                            | 130 |

| REGISTER 0X30: RXD1 EXTRACT FIFO CONTROL                           | 131 |

| REGISTER 0X31: RXD1 EXTRACT FIFO INTERRUPT STATUS                  | 132 |

| REGISTER 0X34: RXD2 EXTRACT FIFO CONTROL                           | 133 |

| REGISTER 0X35: RXD2 EXTRACT FIFO INTERRUPT STATUS                  | 134 |

| REGISTER 0X3C: RECEIVE LOGICAL CHANNEL FIFO CONTROL                | 135 |

| REGISTER 0X3D:RECEIVE LOGICAL CHANNEL FIFO INTERRUPT STATUS13                          | 7     |

|----------------------------------------------------------------------------------------|-------|

| REGISTERS 0X40, 0X50: RXD1, RXD2 HIGH-SPEED SERIAL CONFIGURATION                       | 8     |

| REGISTERS 0X41, 0X51: RXD1, RXD2 HIGH-SPEED SERIAL CELL FILTERING CONFIGURATION/STATUS | 0     |

| REGISTERS 0X42, 0X52: RXD1, RXD2 HIGH-SPEED SERIAL INTERRUPT ENABLES                   | 2     |

| REGISTERS 0X43,0X53: RXD1, RXD2 HIGH-SPEED SERIAL INTERRUPT STATUS                     | 4     |

| REGISTERS 0X44, 0X54: RXD1, RXD2 HIGH-SPEED SERIAL HCS ERROR COUNT                     | 6     |

| REGISTERS 0X45, 0X55: RXD1, RXD2 HIGH-SPEED SERIAL CELL COUNTER (LSB)                  | 7     |

| REGISTERS 0X46, 0X56: RXD1, RXD2 HIGH-SPEED SERIAL CELL COUNTER                        | 7     |

| REGISTERS 0X47, 0X57: RXD1, RXD2 HIGH-SPEED SERIAL CELL COUNTER (MSB)                  | 8     |

| REGISTER 0X5C: TRANSMIT LOGICAL CHANNEL FIFO CONTROL 14                                | 9     |

| REGISTER 0X5D: TRANSMIT LOGICAL CHANNEL FIFO INTERRUPT STATU                           | IS150 |

| REGISTER 0X5E: TRANSMIT LOGICAL CHANNEL FIFO DEPTH 15                                  | 1     |

| REGISTER 0X60: TRANSMIT HIGH-SPEED SERIAL CONFIGURATION 15                             | 2     |

| REGISTER 0X61: TRANSMIT HIGH-SPEED SERIAL CELL COUNT STATUS                            | 4     |

| REGISTER 0X62: TRANSMIT HIGH-SPEED SERIAL CELL COUNTER (LSB)                           | 5     |

| REGISTER 0X63: TRANSMIT HIGH-SPEED SERIAL CELL COUNTER 15                              | 5     |

| REGISTER 0X64: TRANSMIT HIGH-SPEED SERIAL CELL COUNTER (MSB)                           | 6     |

|                                                                                        |       |

ISSUE 5 DUAL SERIAL LINK PHY MULTIPLEXER

| REGISTER 0X68: RECEIVE SERIAL INDIRECT CHANNEL SELECT              | 157 |

|--------------------------------------------------------------------|-----|

| REGISTER 0X69: RECEIVE SERIAL INDIRECT CHANNEL CONFIGURATIO        |     |

| REGISTER 0X6A: RECEIVE SERIAL INDIRECT CHANNEL INTERRUPT ENABLES   | 161 |

| REGISTER 0X6B: RECEIVE SERIAL INDIRECT CHANNEL INTERRUPT AN STATUS |     |

| REGISTER 0X6C: RECEIVE SERIAL INDIRECT CHANNEL HCS ERROR COUNT     | 164 |

| REGISTER 0X6D: RECEIVE SERIAL LCD COUNT THRESHOLD                  | 165 |

| REGISTER 0X70: TRANSMIT SERIAL INDIRECT CHANNEL SELECT             | 166 |

| REGISTER 0X71:TRANSMIT SERIAL INDIRECT CHANNEL DATA                | 167 |

| REGISTER 0X74:TRANSMIT SERIAL ALIGNMENT CONTROL                    | 169 |

| REGISTER 0X80: MASTER TEST                                         | 171 |

| REGISTER 0X83: MISCELLANEOUS TEST                                  | 172 |

DUAL SERIAL LINK PHY MULTIPLEXER

## **LIST OF FIGURES**

| FIG. 1 TYPICAL TARGET APPLIC         | ATION                            | 5   |

|--------------------------------------|----------------------------------|-----|

| FIG. 2 THREE STAGE MULTIPLE          | X ARCHITECTURE                   | 7   |

| FIG. 3 CLOCK AND DATA PHY IN         | TERFACE                          | 8   |

| FIG. 4 S/UNI-DUPLEX TO S/UNI-I       | DUPLEX APPLICATIONS              | 10  |

| FIG. 5 S/UNI-DUPLEX TO S/UNI-I       | DUPLEX PROTECTION SWITCHING      | 10  |

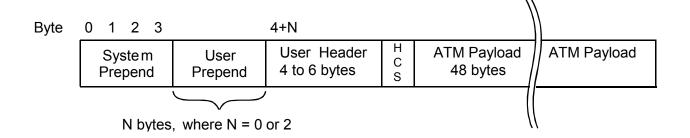

| FIG. 6 EIGHT BIT SCI-PHY/UTOP        | IA/ANY-PHY CELL FORMAT           | 56  |

| FIG. 7 SIXTEEN BIT SCI-PHY/UT        | OPIA/UTOPIA CELL FORMAT          | 57  |

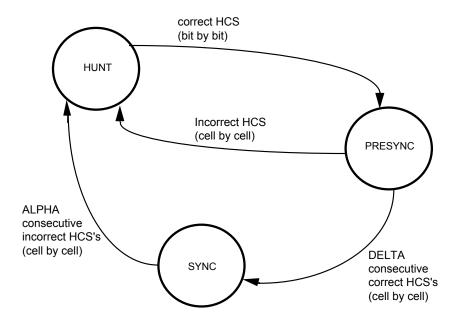

| FIG. 8 CELL DELINEATION STAT         | E DIAGRAM                        | 59  |

| FIG. 9 HIGH-SPEED SERIAL LIN         | K DATA STRUCTURE                 | 62  |

| FIG. 10 DATAPATH LOOPBACK            |                                  | 66  |

| FIG. 11 MICROPROCESSOR CEL           | L FORMAT                         | 79  |

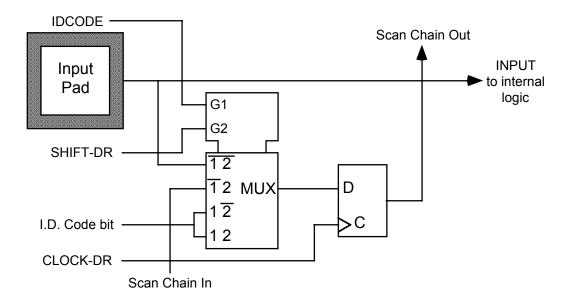

| FIG. 12 INPUT OBSERVATION C          | ELL (IN_CELL)                    | 179 |

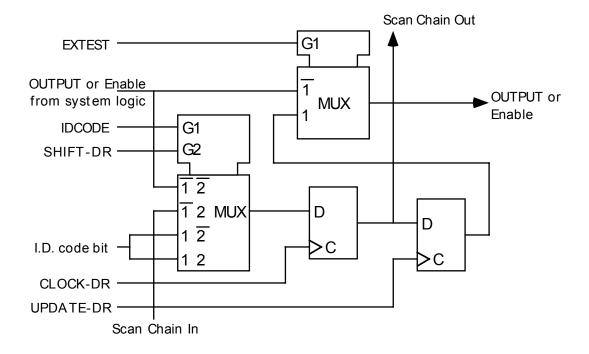

| FIG. 13 OUTPUT CELL (OUT_CE          | LL)                              | 180 |

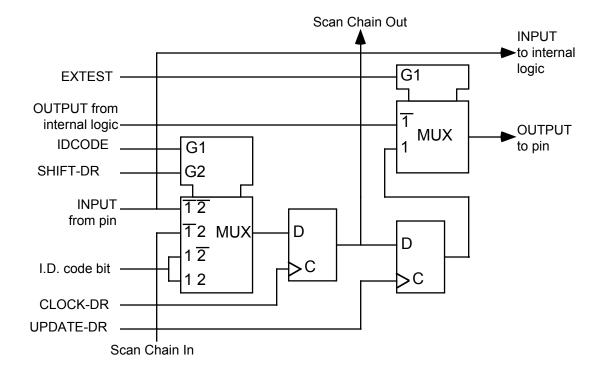

| FIG. 14 BIDIRECTIONAL CELL (IC       | D_CELL)                          | 180 |

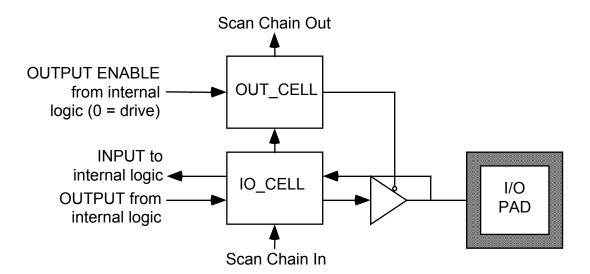

| FIG. 15 LAYOUT OF OUTPUT EN          | ABLE AND BIDIRECTIONAL CELLS     | 181 |

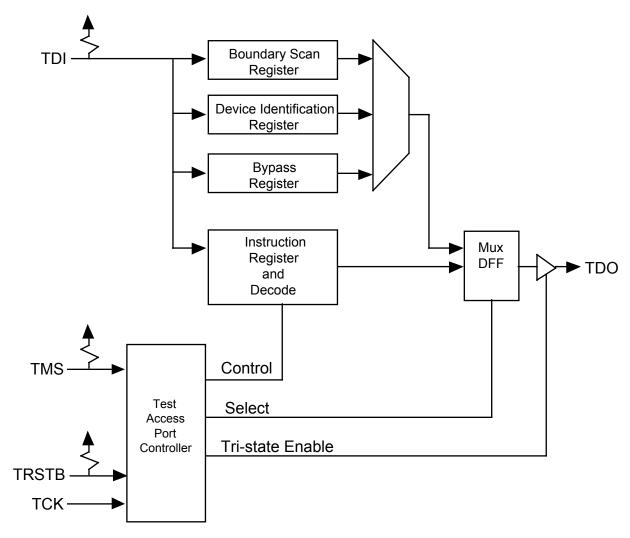

| FIG. 16 BOUNDARY SCAN ARCH           | IITECTURE                        | 197 |

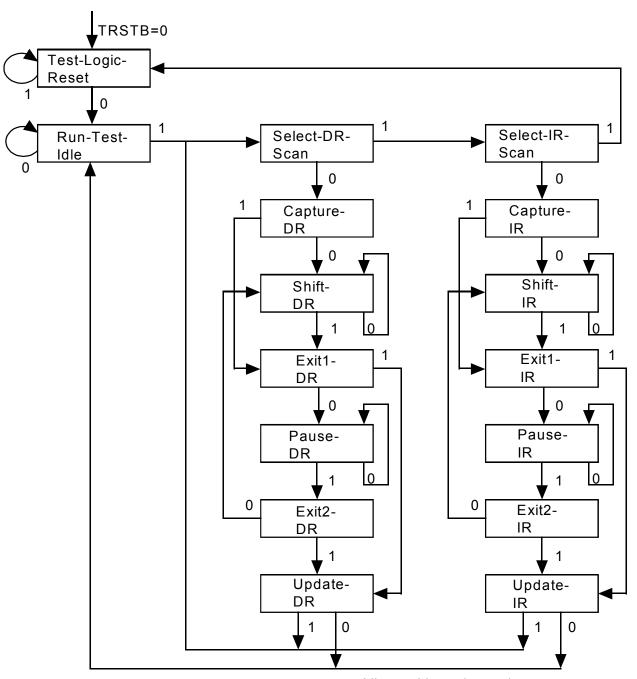

| FIG. 17 TAP CONTROLLER FINIT         | E STATE MACHINE                  | 199 |

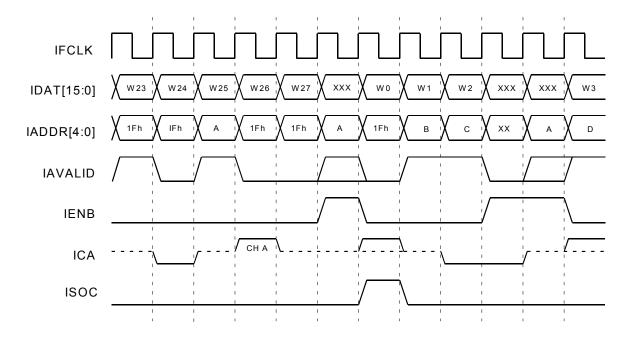

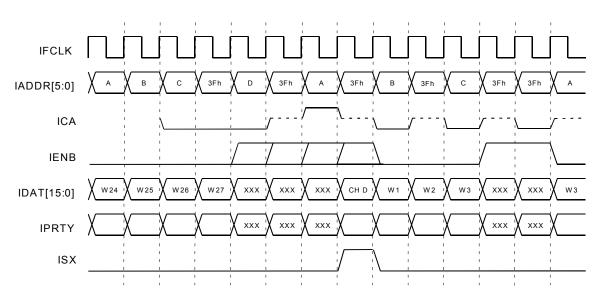

| FIG. 18 SCI-PHY INTERFACE, IN        | PUT BUS SLAVE TRANSFER TIMING    | 203 |

| FIG. 19 SCI-PHY INTERFACE, IN        | PUT BUS MASTER TRANSFER TIMING.  | 204 |

| FIG. 20 ANY-PHY INTERFACE, IN        | IPUT BUS SLAVE TRANSFER TIMING   | 205 |

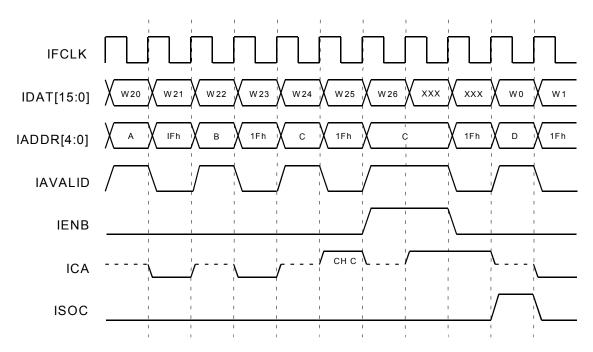

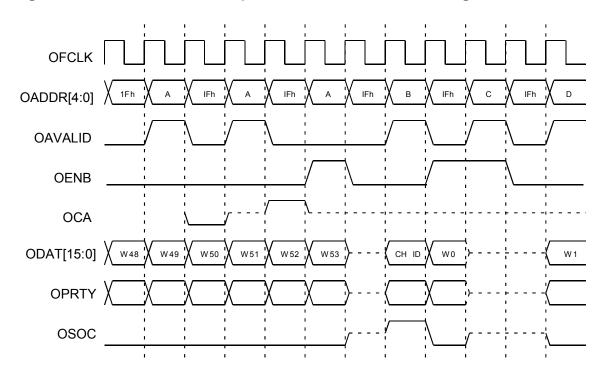

| FIG. 21 SCI-PHY INTERFACE, OL        | JTPUT BUS SLAVE TRANSFER TIMING. | 206 |

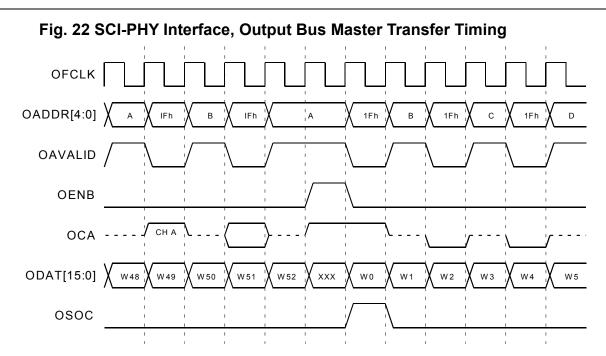

| FIG. 22 SCI-PHY INTERFACE, OU<br>207 | JTPUT BUS MASTER TRANSFER TIMING | G   |

RELEASED

DATA SHEET PMC-1980581

DUAL SERIAL LINK PHY MULTIPLEXER

PM7350 S/UNI-DUPLEX

ISSUE 5

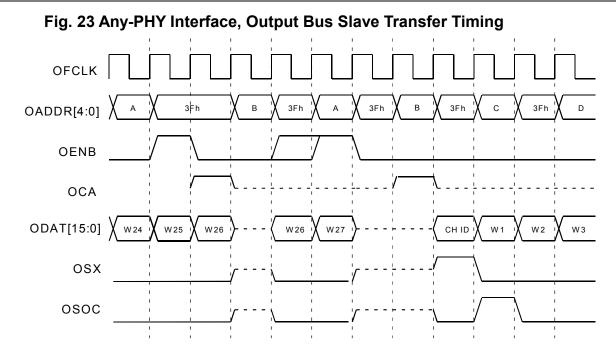

| FIG. 23 ANY-PHY INTERFACE, OUTPUT BUS SLAVE TRANSFER TIMING | 208   |

|-------------------------------------------------------------|-------|

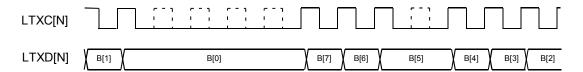

| FIG. 24 CLOCKED SERIAL DATA TRANSMIT INTERFACE              | . 208 |

| FIG. 25 CLOCKED SERIAL DATA TRANSMIT INTERFACE, 1 BIT GAP   | 209   |

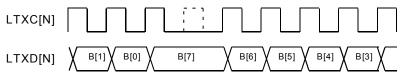

| FIG. 26 CLOCKED SERIAL DATA TRANSMIT INTERFACE, 8 BIT GAP   | 209   |

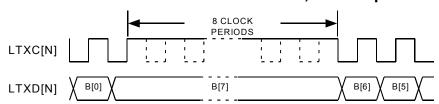

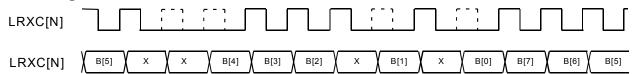

| FIG. 27 CLOCKED SERIAL DATA RECEIVE INTERFACE               | 209   |

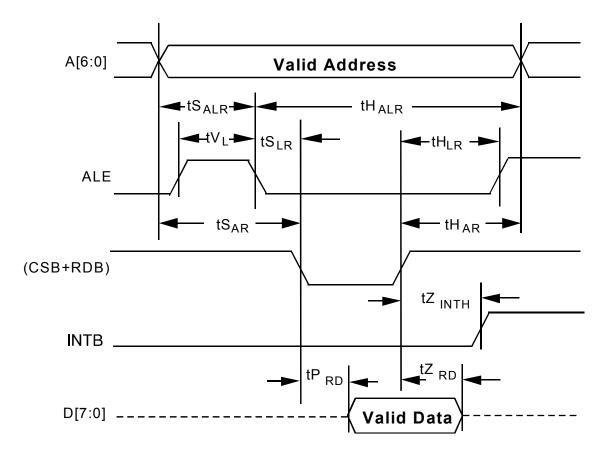

| FIG. 28: MICROPROCESSOR INTERFACE READ TIMING               | 216   |

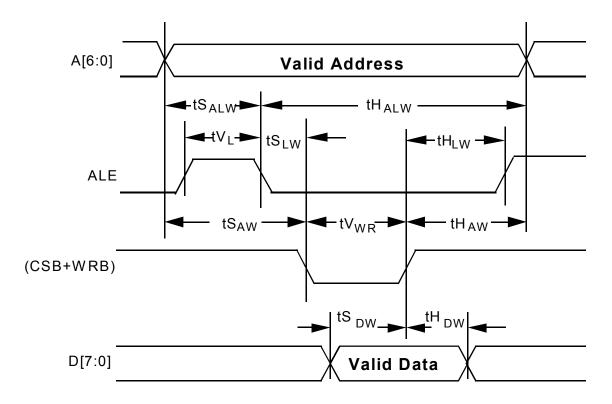

| FIG. 29: MICROPROCESSOR INTERFACE WRITE TIMING              | 218   |

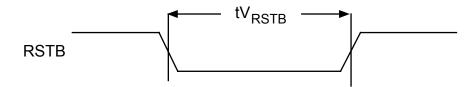

| FIG. 30: RSTB TIMING                                        | . 219 |

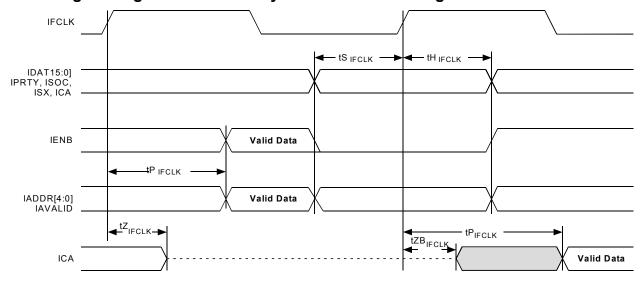

| FIG. 31: INGRESS SCI-PHY/ANY-PHY INTERFACE TIMING           | . 220 |

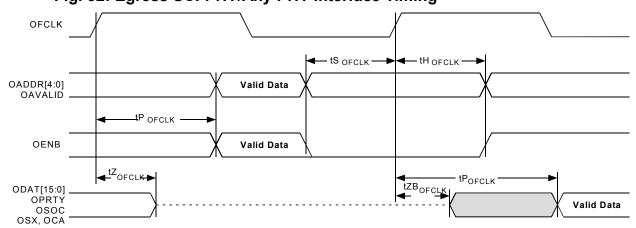

| FIG. 32: EGRESS SCI-PHY/ANY-PHY INTERFACE TIMING            | . 221 |

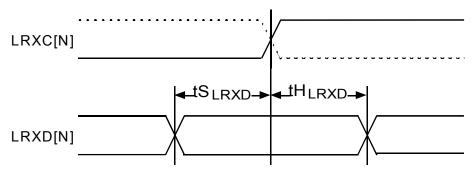

| FIG. 33: CLOCKED SERIAL DATA INTERFACE                      | . 222 |

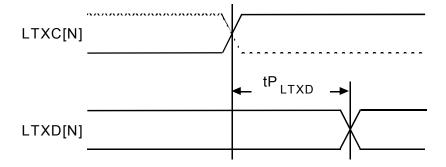

| FIG. 34: JTAG PORT INTERFACE TIMING                         | . 224 |

DUAL SERIAL LINK PHY MULTIPLEXER

## **LIST OF TABLES**

| TABLE 1 SIGNAL NAME CROSS-REFERENCE                                   | . 46 |

|-----------------------------------------------------------------------|------|

| TABLE 2 EIGHT BIT SCI-PHY/UTOPIA BUS MASTER, INPUT<br>CONFIGURATION   | . 48 |

| TABLE 3 SIXTEEN BIT SCI-PHY/UTOPIA BUS MASTER, INPUT<br>CONFIGURATION | . 48 |

| TABLE 4 EIGHT BIT SCI-PHY/UTOPIA BUS MASTER, OUTPUT<br>CONFIGURATION  | . 49 |

| TABLE 5 SIXTEEN BIT SCI-PHY/UTOPIA BUS MASTER, OUTPUT CONFIGURATION   | . 49 |

| TABLE 6 EIGHT BIT SCI-PHY/UTOPIA BUS SLAVE, INPUT CONFIGURATI<br>50   | ON   |

| TABLE 7 SIXTEEN BIT SCI-PHY/UTOPIA BUS SLAVE, INPUT CONFIGURATION     | . 50 |

| TABLE 8 EIGHT BIT SCI-PHY/UTOPIA BUS SLAVE, OUTPUT CONFIGURATION      | . 51 |

| TABLE 9 SIXTEEN BIT SCI-PHY/UTOPIA BUS SLAVE, OUTPUT CONFIGURATION    | . 52 |

| TABLE 10 SCI-PHY/UTOPIA AND ANY-PHY COMPARISON, INGRESS DIRECTION     | . 53 |

| TABLE 11 EIGHT BIT ANY-PHY BUS SLAVE, INPUT CONFIGURATION             | . 53 |

| TABLE 12 SIXTEEN BIT ANY-PHY BUS SLAVE, INPUT CONFIGURATION .         | . 54 |

| TABLE 13 SCI-PHY/UTOPIA AND ANY-PHY COMPARISON, EGRESS<br>DIRECTION   | . 54 |

| TABLE 14 EIGHT BIT ANY-PHY BUS SLAVE, OUTPUT CONFIGURATION            | . 55 |

| TABLE 15 SIXTEEN BIT SCI-PHY/UTOPIA BUS SLAVE, OUTPUT CONFIGURATION   | . 55 |

| TABLE 16 PREPENDED FIELDS                                             | . 62 |

RELEASED

PMC-Sierra, Inc.

PM7350 S/UNI-DUPLEX

DATA SHEET PMC-1980581

| ISSUE 5 | DUAL SERIAL LINK PHY MULTIPLEXER |

|---------|----------------------------------|

|         |                                  |

| TABLE 17 ASSIGNED BIT ORIENTED CODES                    | 69    |

|---------------------------------------------------------|-------|

| TABLE 18: BOUNDARY SCAN REGISTER                        | . 177 |

| TABLE 19 LVDS LINK 59 BYTE CELL CONFIGURATIONS          | . 188 |

| TABLE 20 LVDS LINK 58 BYTE CELL CONFIGURATIONS          | . 188 |

| TABLE 21 LVDS LINK 57 BYTE CELL CONFIGURATIONS          | . 190 |

| TABLE 22 LVDS LINK 61 BYTE CELL CONFIGURATIONS          | . 192 |

| TABLE 23 LVDS LINK 59 BYTE CELL CONFIGURATIONS WITH CRC | . 192 |

PMC-1980581

PM7350 S/UNI-DUPLEX

ISSUE 5

**DUAL SERIAL LINK PHY MULTIPLEXER**

#### **1 FEATURES**

- Integrated analog/digital device that interfaces a high-speed parallel bus to a high speed Low Voltage Differential Signal (LVDS) serial link with optional 1:1 protection.

- For framers or modems without Utopia bus interfaces the S/UNI-DUPLEX provides cell delineation (I.432) across 16 clock and data (bit serial) interfaces.

- Fault detection, redundancy, protection switching, and inserting/removing cards while the system is running (hot swap).

- Interface to other S/UNI-DUPLEX or S/UNI-VORTEX, to satisfy a full set of system level requirements for backplane interconnect:

- Transports user data by providing the inter-card data-path.

- Inter-processor communication by providing an integrated inter-card control channel.

- Exchanges flow control information (back-pressure) to prevent data loss.

- Provides embedded command and control signals across the backplane: system reset, error indications, protection switching commands, etc.

- Clock/timing distribution (system clocks as well as reference clocks such as 8 kHz timing references).

- When used as a parallel bus slave device, can be configured to share the bus with other S/UNI-DUPLEX bus slave devices.

- Can interface to another S/UNI-DUPLEX device (via a single LVDS link) to create a simple point-to-point "Utopia bus extension" capability.

- Can interface to two S/UNI-DUPLEX devices to create a 1:1 protected bus extension.

- Interworks with PM7351 S/UNI-VORTEX devices to implement a point-tomultipoint serial backplane architecture, with optional 1:1 protection of the common card.

- In the LVDS receive direction: selects traffic from the LVDS link marked active and demultiplexes the individual cell streams to the appropriate PHY device.

PM7350 S/UNI-DUPLEX

DUAL SERIAL LINK PHY MULTIPLEXER

- Cell read/write to both LVDS links available through the processor port. Provides optional hardware assisted CRC32 calculation across cells to support an embedded inter-processor communication channel across the LVDS links.

- Requires no external memories.

- Standard 5 pin P1149.1 JTAG test port.

ISSUE 5

- Low-power, 3.3V CMOS technology.

- 160-pin high-performance plastic ball grid array (PBGA) package.

PMC-1980581

ISSUE 5

**DUAL SERIAL LINK PHY MULTIPLEXER**

### **2 APPLICATIONS**

- Single shelf or multi-shelf Digital Subscriber Loop Access Multiplexer (DSLAM).

- ATM, frame relay, IP switch.

- Multiservice access multiplexer.

- Universal Mobile Telecommunication System (UMTS) wireless base stations.

- 16 channel cell delineation (I.432 transmission convergence processing).

**ISSUE 5**

**DUAL SERIAL LINK PHY MULTIPLEXER**

#### 3 REFERENCES

- PMC-Sierra; "Saturn Compatible Interface For ATM PHY Layer And ATM Layer Devices, Level 2"; PMC-940212; Dec. 8, 1995

- ATM Forum, "Universal Test & Operations PHY Interface for ATM (UTOPIA), Level 2", Version 1.0, af-phy-0039.000, June 1995

- PMC-Sierra; "Saturn Interface Specification And Interoperability Framework For Packet And Cell Transfer Between Physical Layer And Link Layer Devices", PMC-980902, Draft

- Draft American National Standard for Telecommunications T1.413 Issue 2, "Network and Customer Installation Interfaces - Asymmetric Digital Subscriber Line (ADSL) Metallic Interface", ANSI T1.413-1998, November 1998

- ITU-T Recommendation I.432.1, "B-ISDN user-network interface Physical layer specification: General characteristics", 08/96

**DUAL SERIAL LINK PHY MULTIPLEXER**

#### 4 APPLICATION EXAMPLES

When designing communication equipment such as access switches, multiplexers, wireless base stations, and base station controllers the equipment architect is faced with a common problem: how to efficiently connect a large number of lower speed ports to a small number of high speed ports? Typically, a number of line-side ports (analog modems, xDSL modems ATM PHYs, or RF modems) are terminated on each line card. Numerous line cards are then slotted into one or more shelves and backplane traces or inter-shelf cables are used to connect the line cards to a centralized (often 1:1 protected) common card, hereafter referred to as the core card. The core card normally includes one or more high speed WAN up-link ports that transport traffic to and from a high speed broadband network.

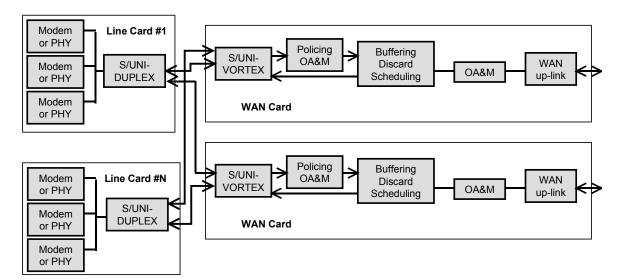

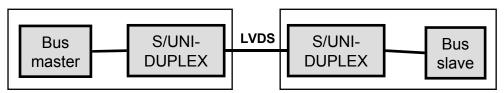

A block diagram of a 1:1 redundant system is shown in Fig. 1.

Fig. 1 Typical Target Application

In this type of equipment the majority (perhaps all) user traffic goes from WAN port to line port, or from line port to WAN port. Although the individual ports on the line cards are often relatively low speed interfaces such as T1, E1, or xDSL, there may be many ports per line card and many line cards per system, resulting in hundreds or even thousands of lines terminating on a single WAN up-link. In the upstream direction (from line card to WAN up-link), the equipment must have capacity to buffer and intelligently manage bursts of upstream traffic simultaneously from numerous line cards.

RELEASED

DATA SHEET

PMC-1980581

PM7350 S/UNI-DUPLEX

**ISSUE 5**

DUAL SERIAL LINK PHY MULTIPLEXER

In the downstream direction the equipment must handle a similar issue, the "big pipe feeding little pipe" problem. When a large burst of traffic destined for a single line port is received at the high speed WAN port it must be buffered and managed as it queues up waiting for the much lower speed line port to clear.

The line cards are always the most numerous cards in this type of equipment. An individual line card, even if it terminates a few dozen low speed ports, does not generate or receive enough traffic to justify putting complex buffering and traffic management devices on it. The ideal architecture has low cost "dumb" line cards and a feature rich, "smart" core card. In order to enhance fault tolerance, the architecture should also inherently support 1:1 protection using a redundant core card and WAN up-link without significantly increasing line card complexity.

A system architecture that keeps buffering and traffic management off the line card with typically exhibit the following features:

- Connection setup is simpler both in terms of programming and during execution because there is minimal or no requirement for line intervention during the connection setup process.

- 2. In-service feature upgrades are simpler because feature complexity is limited to the common equipment.

- 3. Component costs are reduced, while system reliability increases due to reduced component count.

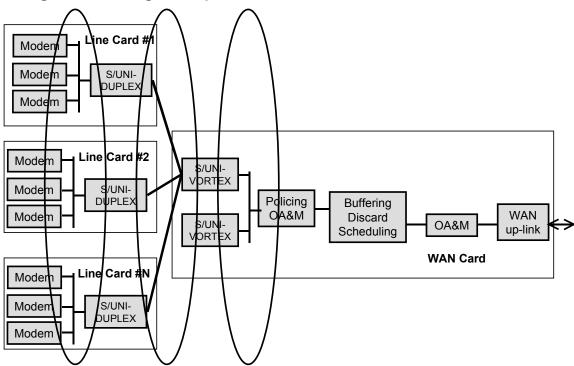

In this type of architecture there are often three stages of signal concentration or multiplexing, as shown in Fig 2.

ISSUE 5 DUAL SERIAL LINK PHY MULTIPLEXER

The first stage resides on the line card and spans only those ports physically terminated by that card. Since it is confined to a single card, this first stage of multiplexing readily lends itself to the simple parallel bus based multiplex topology implemented by the S/UNI-DUPLEX. The second stage of concentration occurs between the core card(s) and the line cards, including line cards that are on a separate shelf. This second stage is best served by a redundant serial point-to-point technology. The third stage of multiplexing is optional and resides on the core card. This third stage is used in systems with a large number of line cards that require several devices to terminate the second stage of aggregation. Since the third stage of aggregation is confined to the core card, it lends itself readily to a parallel bus implementation. This three stage approach is implemented directly by the S/UNI-DUPLEX and its sister device, the S/UNI-VORTEX.

The S/UNI-DUPLEX acts as the line card's bus master. It implements the first stage of multiplexing by routing traffic from the PHYs and transmitting the traffic simultaneously over two high speed (200 Mbps) serial 4-wire LVDS links. One serial link attaches to the active core card, the other to the standby core card. In the downstream direction the S/UNI-DUPLEX demultiplexes traffic from the active core card's LVDS serial link and routes this traffic to the appropriate PHYs. If the active core card (or its LVDS link) should fail, protection switching commands embedded in the spare LVDS link will direct the S/UNI-DUPLEX to start receiving its traffic from this spare link.

DUAL SERIAL LINK PHY MULTIPLEXER

The S/UNI-VORTEX resides on the core card and terminates up to 8 LVDS links connected to 8 S/UNI-DUPLEX devices. The S/UNI-VORTEX implements the second stage of multiplexing. More than one S/UNI-VORTEX will be required if more than 8 links are required – as will be the case for a system with more than 8 line cards. The S/UNI-VORTEX device(s) share a high speed parallel bus with the core card's traffic management and OA&M layers, as implemented by devices such as PMC-Sierra's S/UNI-APEX and the S/UNI-ATLAS.

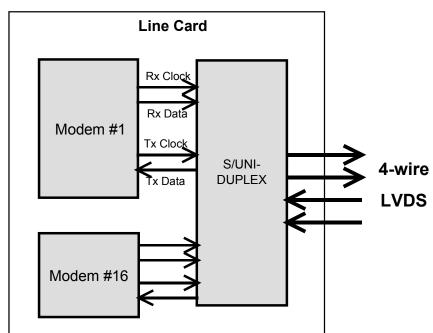

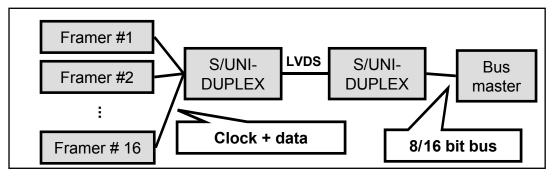

Some applications use framer or modem devices without integrated I.432 processing¹ normally support a clock and data interface, and rely on external circuitry to detect and generate ATM cell framing and overhead. To support these applications, the S/UNI-DUPLEX provides a clock and data mode². In this mode, the input/output pins that normally interface to the Utopia bus are configured to support up to 16 clock and data serial interfaces. This type of line card is shown in Fig. 3. The I.432 processing is transparent to the far end device, which implies that a single S/UNI-VORTEX can simultaneously interface to line cards that implement the Utopia bus and to line cards that use clock and data interfaces.

Fig. 3 Clock and Data PHY Interface

Some PHY devices provide a 3-line interface consisting of clock, data, and overhead indication. For these PHYs external circuitry can be used to adapt to the S/UNI-DUPLEX's 2-line interface.

<sup>&</sup>lt;sup>1</sup> Cell delineation, payload scrambling-descrambling, idle cell generation/discard, etc..

<sup>&</sup>lt;sup>2</sup> Either Utopia mode or clock and data mode can be selected, but not both at once.

RELEASED

DATA SHEET

PMC-1980581

PMC-Sierra, Inc.

PM7350 S/UNI-DUPLEX

**ISSUE 5**

DUAL SERIAL LINK PHY MULTIPLEXER

In the clock and data receive direction the S/UNI-DUPLEX performs bit level ATM cell delineation function. In the transmit direction the S/UNI-DUPLEX can operate in either bit or frame aligned mode. In frame mode (also called byte aligned mode) the two wire transmit interface continuously monitors for gaps in the transmit clock to determine where the frame or byte alignment should occur. The circuitry assumes that when a gap in the transmit clock is detected this is either the framing bit position (e.g. the DS-1 framing bit) or an overhead byte (e.g. ADSL modem). In either case the next clock period after the gap is assumed to represent the byte alignment position.

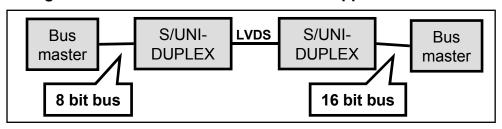

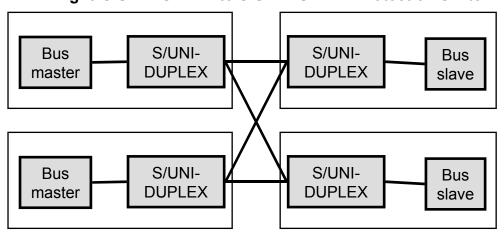

In the multiplexer application discussed previously the S/UNI-DUPLEX's LVDS interfaces are connected to one or two S/UNI-VORTEX devices. It is also possible to interface S/UNI-DUPLEX to S/UNI-DUPLEX via the LVDS link. Since the S/UNI-DUPLEX bus interface can be configured in several ways (clock and data, 8/16 bits bus master, 8/16 bit bus slave) there are various applications where two S/UNI-DUPLEX devices can be used "back-to-back" in order to perform one or more of the following functions:

- 1. Interfacing a bus master device to another bus master.

- 2. Interfacing a bus slave device to another bus slave.

- 3. Converting between 8 bit and 16 bit buses.

- 4. Off card or off shelf bus extension.

- 5. Cell delineation (I.432 processing).

- 6. Protection switching.

Examples of these types of configurations are shown in Fig. 4 and Fig. 5.

**DUAL SERIAL LINK PHY MULTIPLEXER**

Fig. 4 S/UNI-DUPLEX to S/UNI-DUPLEX Applications

**ISSUE 5**

Example of on-card bus conversion: 8 bit bus master to 16 bit bus master

**Example of basic bus extension between cards**

Example of on-card I.432 processing

Fig. 5 S/UNI-DUPLEX to S/UNI-DUPLEX Protection Switching

**Example of protection switching between cards**

**DUAL SERIAL LINK PHY MULTIPLEXER**

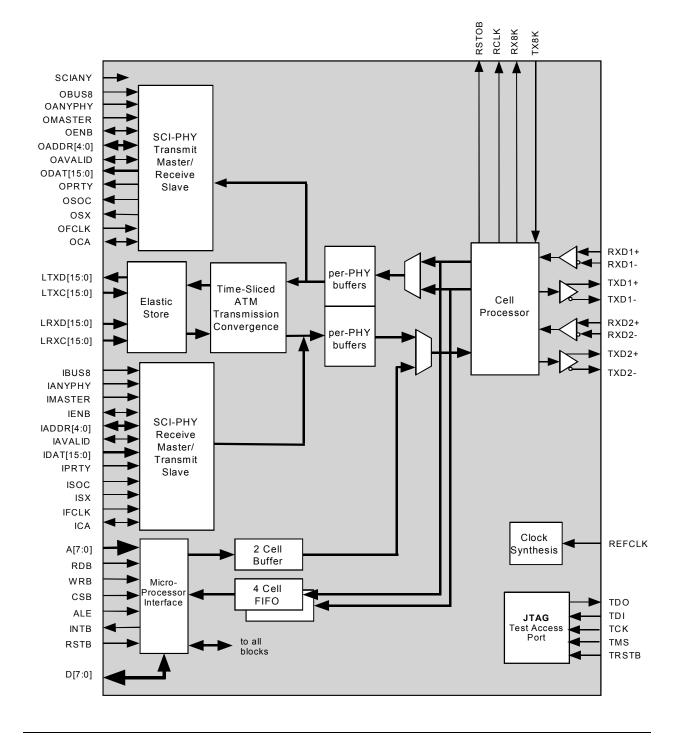

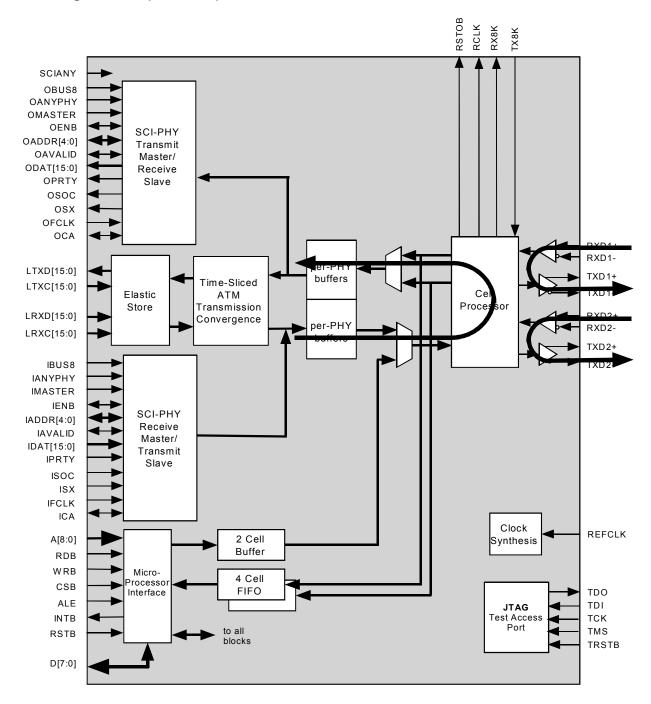

#### 5 BLOCK DIAGRAM

Although separated to improve clarity, many signals in the following diagram share physical package pins. The use of the SCI-PHY/Any-PHY interfaces and the clocked serial data interfaces is mutually exclusive.

PM7350 S/UNI-DUPLEX

DUAL SERIAL LINK PHY MULTIPLEXER

#### 6 DESCRIPTION

The PM7350 S/UNI-DUPLEX is a monolithic integrated circuit typically used with its sister device, the S/UNI-VORTEX, to implement a point-to-point serial backplane interconnect architecture. The primary role of the S/UNI-DUPLEX is to interface to up to 32 devices (typically framers or PHYs) and transfer 52-56 byte data cells in serial format to/from a backplane. Devices interface to the S/UNI-DUPLEX via an 8 or 16-bit SCI-PHY/Utopia/Any-PHY bus, or optionally via a 16 port clock and data interface.

Each S/UNI-DUPLEX can connect to two 100 to 200 Mb/s Low Voltage Differential Signal (LVDS) serial links. A microprocessor port provides access to internal configuration and monitoring registers. The microprocessor port may also be used to insert and extract cells in support of an embedded microprocessor communication channel.

#### **BUS INTERFACE:**

One of four modes can be selected:

- 8 or 16 bit, Utopia L2 bus master operating at up to 33 MHz bus clock frequency. Also supports PMC-Sierra's SCI-PHY bus standard which is compatible with Utopia L2 but allows extended length cells and supports an additional bus address signal in order to support 32 PHY devices rather than Utopia's 31. See Table 1 for a comparison of these bus standards.

- 16 port, 4 pin clocked serial data interface (Tx, TxClk, Rx, RxClk), with integrated I.432 ATM cell delineation operating at up to 52 MHz serial clock frequency.

- 8 or 16 bit, SCI-PHY/Utopia bus slave operating at up to 52 MHz bus clock frequency. The slave input port presents itself as 32 addressable logical channels. The slave output port appears as a single addressable channel carrying the multiplexed traffic from up to 32 logical channels where each cell's channel number can optionally be embedded in the H5 header field (Utopia bus mode) or indicated in a cell prepend (SCI-PHY bus mode).

- 8 or 16 bit, Any-PHY bus slave (bus protocol compatible with the PM7351 S/UNI-VORTEX) operating at up to 52 MHz bus clock frequency. The slave input port presents itself as 32 addressable logical channels. The slave output port appears as a single addressable channel carrying the multiplexed traffic from up to 32 logical channels. In both directions each cell's logical channel number is indicated in a cell prepend.

PM7350 S/UNI-DUPLEX

**DUAL SERIAL LINK PHY MULTIPLEXER**

#### LVDS INTERFACES (both directions):

**ISSUE 5**

- Dual 4-wire LVDS serial transceivers each operating at 100 to 200 Mbps across PCB or backplane traces, or across up to 10 meters of 4-wire twisted pair cabling for inter-shelf communications.

- Full integrated LVDS clock synthesis and recovery. No external analog components are required.

- Usable bandwidth (excludes system overhead) of 186 Mbps.

#### LVDS TRANSMIT DIRECTION

- Simple round robin multiplex of up to 32 PHYs (or 16 clock and data interfaces) plus the microprocessor port's cell transfer buffer.

- Multiplexed cell stream broadcast to both LVDS simultaneously.

- 6 bit port ID prepended to each cell for use by ATM layer to identify cell source (1 of 32 PHYs or processor).

- Back-pressure provided by far end (active link only) to prevent overflow of far end receiver.

#### LVDS RECEIVE DIRECTION

- Cells received from the active LVDS link are forwarded to the appropriate PHY, bit serial interface, or the microprocessor port as specified by a 6 bit port ID added to each cell at the far end device.

- The LVDS link marked as "spare" is monitored for errors, PHY cells are discarded, microprocessor port cells are accepted.

- Individual PHY and microprocessor FIFO back-pressure indications are sent to the far end to prevent FIFO overflows. Per stream back-pressure prevents head-of-line blocking.

#### MICROPROCESSOR INTERFACE

- 8 bit data bus, 8 bit address bus.

- Provides read/write access to all configuration and status registers.

- Provides CRC32 calculation and cell transfer registers to support an embedded microprocessor to microprocessor communication channel over the LVDS link.

PMC-1980581

ISSUE 5

**DUAL SERIAL LINK PHY MULTIPLEXER**

### 7 PIN DIAGRAM

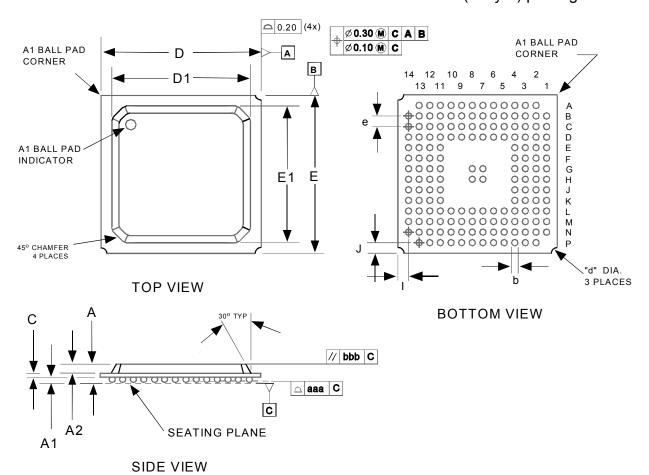

The S/UNI-DUPLEX is packaged in a 160-pin plastic ball grid array (PBGA) package having a body size of 15 mm by 15 mm and a ball pitch of 1.00 mm.

|   | 14    | 13    | 12                | 11                  | 10                  | 9                   | 8           | 7                  | 6                    | 5                    | 4                    | 3                    | 2                    | 1                    |

|---|-------|-------|-------------------|---------------------|---------------------|---------------------|-------------|--------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Α |       | TRSTB | TDI               | A[2]                | RSTB                | A[6]                | RDB         | BIAS               | IMASTER<br>LTXD[15]  | IADDR[3]<br>LRXC[15] | IADDR[1]<br>LRXD[14] | ICA<br>LRXC[13]      | RSTOB                |                      |

| В | TX8K  | тск   | TMS               | A[0]                | A[4]                | A[5]                | ALE         | INTB               | IAVALID<br>LTXC[15]  | vss                  | IENB<br>LRXD[13]     | VDD                  | IPRTY<br>LTXD[13]    | IDAT[15]<br>LTXC[13] |

| С | D[7]  | VDD   | VSS               | A[1]                | VSS                 | A[7]                | VSS         | SCIANY             | IBUS8<br>LTXD[14]    | VDD                  | IADDR[0]<br>LRXC[14] | VSS                  | IDAT[14]<br>LTXD[12] | IDAT[13]<br>LTXC[12] |

| D | D[4]  | D[6]  | D[5]              | A[3]                | VDD                 | WRB                 | CSB         | VSS                | IADDR[4]<br>LRXD[15] | IADDR[2]<br>LTXC[14] | VSS                  | IDAT[11]<br>LRXC[12] | IDAT[12]<br>LRXD[12] | IDAT[10]<br>LTXD[11] |

| E | VDD   | RX8K  | VSS               | RCLK                |                     |                     |             |                    |                      |                      | IDAT[7]<br>LRXC[11]  | IDAT[8]<br>LRXD[11]  | VDD                  | IDAT[9]<br>LTXC[11]  |

| F | D[0]  | D[2]  | D[1]              | D[3]                |                     |                     |             |                    |                      |                      | IFCLK<br>LTXC[9]     | VDD                  | IDAT[6]<br>LTXD[10]  | IDAT[5]<br>LTXC[10]  |

| G | RXD1+ | RXD1- | RES               | TAVD                |                     |                     | GND         | GND                |                      |                      | IDAT[3]<br>LTXD[8]   | IDAT[1]<br>LTXD[7]   | VSS                  | IDAT[4]<br>LTXD[9]   |

| н | TXD1+ | TXD1- | TAVS              | RESK                |                     |                     | GND         | GND                |                      |                      | ISX LTXC[6]          | IDAT[2]<br>LTXC[8]   | ISOC<br>LTXD[6]      | IDAT[0]<br>LTXC[7]   |

| J | RXD2+ | RXD2- | RAVS              | RAVD                |                     |                     |             |                    |                      |                      | ODAT[15]<br>LRXC[10] | VSS                  | OPRTY<br>LRXD[10]    | IANYPHY<br>LTXD[5]   |

| к | TXD2+ | TXD2- | TAVS              | TAVD                |                     |                     |             |                    |                      |                      | VSS                  | ODAT[14]<br>LRXD[9]  | ODAT[13]<br>LRXC[9]  | VDD                  |

| L | ATP0  | ATP1  | CAVS              | CAVD                | OADDR[1]<br>LRXD[0] | VDD                 | VSS         | OSOC<br>LRXD[3]    | ODAT[2]<br>LRXD[4]   | ODAT[4]<br>LRXC[6]   | VDD                  | ODAT[12]<br>LTXC[5]  | ODAT[11]<br>LRXD[8]  | VDD                  |

| М | QAVS  | QAVD  | VDD               | OMASTER<br>LTXD[1]  | OADDR[3]<br>LTXC[1] | OAVALID<br>LRXD[1]  | VSS         | VDD                | VSS                  | OANYPHY<br>LTXD[2]   | ODAT[5]<br>LRXD[6]   | ODAT[9]<br>LTXC[4]   | VSS                  | ODAT[10]<br>LRXC[8]  |

| N | vss   | VDD   | Unused<br>LTXD[0] | vss                 | OADDR[2]<br>LTXC[0] | OADDR[4]<br>LRXC[1] | OCA LRXC[2] | ODAT[1]<br>LRXC[4] | ODAT[3]<br>LRXD[5]   | OFCLK<br>LRXC[5]     | ODAT[6]<br>LRXC[7]   | VDD                  | ODAT[8]<br>LTXC[3]   | Unused<br>LTXD[3]    |

| Р |       | TDO   | REFCLK            | OADDR[0]<br>LRXC[0] | VSS                 | OENB<br>LRXD[2]     | OSX LRXC[3] | ODAT[0]<br>LTXC[2] | VDD                  | VSS                  | OBUS8<br>LTXD[4]     | VSS                  | ODAT[7]<br>LRXD[7]   |                      |

**BOTTOM VIEW**

PMC-1980581

PM7350 S/UNI-DUPLEX

ISSUE 5

DUAL SERIAL LINK PHY MULTIPLEXER

## 8 PIN DESCRIPTION

| Ball<br>Name                     | Туре                    | Ball<br>No.              | Function                                                                                                                                                                                                                                                                                                                               |

|----------------------------------|-------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                         | ŀ                        | High Speed LVDS Links                                                                                                                                                                                                                                                                                                                  |

| RXD1+<br>RXD1-<br>RXD2+<br>RXD2- | Diff.<br>LVDS<br>Input  | G14<br>G13<br>J14<br>J13 | The high-speed receive data (RXD1+/-, RXD2+/-) inputs present NRZ data from a serial backplane. Two pairs are provided for redundancy. The active link may be chosen by the local microprocessor or determined by a simple handshake.                                                                                                  |

|                                  |                         |                          | RXD1+/- and RXD2+/- are truly differential inputs offering superior common-mode noise rejection. They have sufficient sensitivity and common-mode range to support LVDS signals.                                                                                                                                                       |

| TXD1+<br>TXD1-<br>TXD2+<br>TXD2- | Diff.<br>LVDS<br>Output | H14<br>H13<br>K14<br>K13 | The transmit differential data (TXD1+/-, TXD2+/-) outputs present NRZ encoded data to a serial backplane. These outputs are open drain current sinks which interface directly with twisted-pair cabling or board interconnect. Edge rates are controlled to minimize radiated emissions.                                               |

|                                  |                         |                          | Both differential links carry identical traffic except the exact phase relationship is not guaranteed.                                                                                                                                                                                                                                 |

| REFCLK                           | Input                   | P12                      | The reference clock input (REFCLK) must provide a jitter-free reference clock. It is used as the reference clock by both clock recovery and clock synthesis circuits. Any jitter below 1 MHz is transferred directly to the TXD1+/- and TXD2+/- outputs. The high-speed serial interface bit rate is eight times the REFCLK frequency. |

| RES<br>RESK                      | Analog                  | G12<br>H11               | A 4.75k $\Omega$ ±1% resistor must be connected between these two pins to achieve the correct LVDS output signal levels.                                                                                                                                                                                                               |

| ATP0<br>ATP1                     | Analog                  | L14<br>L13               | The Analog Test Points (ATP) are provided for production test purposes. In mission mode they are high impedance and should be connected to ground.                                                                                                                                                                                     |

PM7350 S/UNI-DUPLEX

DATA SHEET PMC-1980581 PMC-Sierra, Inc.

ISSUE 5

| Input  | B14 | end of the high-speed serial links via TXD1+/- and TXD2+/ A rising edge on TX8K is encoded in the next cell transmitted.  Although TX8K is targeted at a typical need of transporting an 8 kHz signal, its frequency is not                                                                         |

|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input  | B14 | allows a traceable signal to be transmitted to the far end of the high-speed serial links via TXD1+/- and TXD2+/ A rising edge on TX8K is encoded in the next cell transmitted.  Although TX8K is targeted at a typical need of transporting an 8 kHz signal, its frequency is not                  |

|        |     | transporting an 8 kHz signal, its frequency is not                                                                                                                                                                                                                                                  |

|        |     | constrained to 8 kHz. Any frequency less than the cell rate is permissible.                                                                                                                                                                                                                         |

| Output | E13 | The receive 8 kHz timing reference (RX8K) output presents the timing extracted from one of the receive high-speed serial links, RXD1+/- or RXD2+/                                                                                                                                                   |

|        |     | The rising edge of RX8K is accurate to the nearest byte boundary of the high-speed serial link; therefore, a small amount of jitter is present. At a link rate of 155.52 Mb/s, the jitter is 63ns peak-to-peak.                                                                                     |

|        |     | Pulses on RX8K are always 16 high-speed serial link bit periods wide (two REFCLK periods).                                                                                                                                                                                                          |

| Output | E11 | The Recovered Clock (RCLK) output presents the byte clock for the active receive high-speed serial link. The RCLK frequency shall be 0.125 of the RXD1+/- or RXD2+/- bit rate.                                                                                                                      |

|        |     | Due to the digital clock recovery technique employed, jitter is introduced as 12.8 ns phase steps. If the active link is changed, RCLK can not be guaranteed to be glitch free. Because of these two factors, RCLK must be cleaned up by a PLL before it is suitable for use as a timing reference. |

|        |     |                                                                                                                                                                                                                                                                                                     |

ISSUE 5

| Ball                                                             |                         | Ball                              |                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------|-------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                             | Type                    | No.                               | Function                                                                                                                                                                                                                                                                                                                                      |

|                                                                  |                         | ŀ                                 | High Speed LVDS Links                                                                                                                                                                                                                                                                                                                         |

| SCIANY                                                           | Input                   | C7                                | The SCI-PHY/Any-PHY Interface (SCIANY) input selects the type of PHY device interface. If SCIANY is a logic high, the S/UNI-DUPLEX will be configured to communicate to the PHY devices via a shared SCI-PHY Level 2, Utopia L2, or Any-PHY cell bus. If SCIANY is a logic low, each PHY device has a dedicated clocked bit serial interface. |

|                                                                  |                         |                                   | The two types of interfaces share common package pins. Failure to present the correct logic level on this signal for the application may result in damage to the S/UNI-DUPLEX or the PHY devices.                                                                                                                                             |

|                                                                  |                         |                                   | When SCIANY is logic high, LTXD[3] and LTXD[0] become inputs and need to be tied to VDD or VSS through a pull up or a pull down.                                                                                                                                                                                                              |

| LRXD[15]<br>LRXD[14]<br>LRXD[13]<br>LRXD[12]                     | Input<br>(SCIANY=<br>0) | D6<br>A4<br>B4<br>D2              | The low-speed receive data (LRXD[15:0]) inputs provide data from individual modem channels. The data streams must carry contiguous ATM cells with valid HCS (Header Check Sequence) bytes.                                                                                                                                                    |

| LRXD[11]<br>LRXD[10]<br>LRXD[9]<br>LRXD[8]<br>LRXD[7]<br>LRXD[6] |                         | E3<br>J2<br>K3<br>L2<br>P2<br>M4  | LRXD[n] can be clocked either by the rising or falling edge of the corresponding LRXC[n] input, depending on the value of the LRXCINV bit of the Master Configuration register. By default, the rising edge is used.                                                                                                                          |

| LRXD[5]<br>LRXD[4]<br>LRXD[3]<br>LRXD[2]<br>LRXD[1]<br>LRXD[0]   |                         | N6<br>L6<br>L7<br>P9<br>M9<br>L10 | These inputs are only active if the SCIANY input is a logic low.                                                                                                                                                                                                                                                                              |

PMC-Sierra, Inc.

DATA SHEET PMC-1980581

ISSUE 5

| Ball                                                                                                                                  |                                        | Ball                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |                                                                   |                      |                      |                      |                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                                                                                                  | Type                                   | No.                                                                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                        |                                                                   |                      |                      |                      |                                                                                                                                                                                                                                        |

| High Speed LVDS Links                                                                                                                 |                                        |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |                                                                   |                      |                      |                      |                                                                                                                                                                                                                                        |

| LRXC[15] LRXC[14] LRXC[13] LRXC[12] LRXC[11] LRXC[10] LRXC[9] LRXC[8] LRXC[7] LRXC[6] LRXC[6] LRXC[6] LRXC[5] LRXC[4] LRXC[3] LRXC[2] | Input<br>(SCIANY<br>= 0)               | A5<br>C4<br>A3<br>D3<br>E4<br>J4<br>K2<br>M1<br>N4<br>L5<br>N7<br>P8<br>N8 | The low-speed receive clock (LRXC[15:0]) inputs provide timing for the receive links. Each LRXC signal is independent of the others.  Each signal in LRXD[15:0] is sampled either on the rising or the falling edge of the corresponding LRXC[15:0] clock, depending the value of the LRXCINV bit of the Master Configuration register. By default, the rising edge is used.  The active edge on each LRXC must only occur during those bit periods containing ATM cell data. It must be suppressed during bit periods containing transmission overhead. These inputs are only active if the SCIANY input is a logic low. |                                                                        |                                                                   |                      |                      |                      |                                                                                                                                                                                                                                        |

| LRXC[1]<br>LRXC[0]                                                                                                                    |                                        | N9<br>P11                                                                  | Maximum clock rate is 50 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                        |                                                                   |                      |                      |                      |                                                                                                                                                                                                                                        |

| LTXD[15]<br>LTXD[14]<br>LTXD[13]<br>LTXD[12]<br>LTXD[11]                                                                              | Output                                 | A6<br>C6<br>B2<br>C2<br>D1                                                 | The low-speed transmit data signals (LTXD[15:0]) carry the outgoing link data in bit serial format. Each LTXD signal is independent of the other signals. The most significant bit of each data byte is transmitted first.                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |                                                                   |                      |                      |                      |                                                                                                                                                                                                                                        |

| LTXD[10]<br>LTXD[9]<br>LTXD[8]<br>LTXD[7]<br>LTXD[6]<br>LTXD[5]                                                                       | G1<br>G4<br>G3<br>H2<br>J1<br>P4<br>N1 | G1<br>G4<br>G3<br>H2<br>J1<br>P4<br>N1                                     | the rising or falling edge of the correct LTXC[15:0] clock, depending the value LTXCINV bit of the Master Configure By default, the rising edge is used.  These outputs are only active if the N1 a logic low.                                                                                                                                                                                                                                                                                                                                                                                                            | 9] G1 the rising or G3 LTXC[15:0] of G3 LTXCINV bit H2 By default, the | G4<br>G3<br>H2                                                    | G1<br>G4<br>G3<br>H2 | G1<br>G4<br>G3<br>H2 | G1<br>G4<br>G3<br>H2 | Each signal in LTXD[15:0] can be updated either on the rising or falling edge of the corresponding LTXC[15:0] clock, depending the value of the LTXCINV bit of the Master Configuration register. By default, the rising edge is used. |

| LTXD[4]<br>LTXD[3]                                                                                                                    |                                        |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P4<br>N1                                                               | These outputs are only active if the SCIANY input is a logic low. |                      |                      |                      |                                                                                                                                                                                                                                        |

| LTXD[2]<br>LTXD[1]<br>LTXD[0]                                                                                                         |                                        | M5<br>M11<br>N12                                                           | When SCIANY is logic high, LTXD[3] and LTXD[0] become inputs and need to be tied to VDD or VSS through a pull up or a pull down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                        |                                                                   |                      |                      |                      |                                                                                                                                                                                                                                        |

ISSUE 5

| Ball                                                              |                          | Ball                       |                                                                                                                                                                                                                                                              |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

|-------------------------------------------------------------------|--------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|-------------------------------------------------------------------|

| Name                                                              | Type                     | No.                        | Function                                                                                                                                                                                                                                                     |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

|                                                                   |                          | ŀ                          | High Speed LVDS Links                                                                                                                                                                                                                                        |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

| LTXC[15]<br>LTXC[14]<br>LTXC[13]                                  | Input<br>(SCIANY<br>= 0) | B6<br>D5<br>B1             | The low-speed transmit clock (LTXC[15:0]) inputs provide timing for the transmit links. Each LTXC signal is independent of the others.                                                                                                                       |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

| LTXC[12]<br>LTXC[11]<br>LTXC[10]<br>LTXC[9]<br>LTXC[8]<br>LTXC[7] | 0)                       | C1<br>E1<br>F1<br>F4<br>H3 | E1<br>F1<br>F4<br>H3                                                                                                                                                                                                                                         | E1<br>F1<br>F4<br>H3 | E1<br>F1<br>F4<br>H3 | E1<br>F1<br>F4<br>H3 | 7   C1<br>  E1<br>  F1<br>  F4<br>  H3 | 7   C1   E<br>E1   F1   E<br>F4   E<br>H3   F3 | Each signal in LTXD[15:0] is updated eintrising or the falling edge of the correspondent of the Master Configuration | Each signal in LTXD[15:0] is updated either on the rising or the falling edge of the corresponding LTXC[15:0] clock, depending on the value of the LTXCINV bit of the Master Configuration register. By default, the rising edge is used. |    |    |    |    |    |    |    |                                                                   |

| LTXC[6]<br>LTXC[5]                                                |                          | H4<br>L3                   | As an option, clock gaps can be recognized to force byte alignment to the transmission overhead.                                                                                                                                                             |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

| LTXC[4]                                                           |                          | M3<br>N2                   | N2                                                                                                                                                                                                                                                           | N2                   | N2                   | N2                   | N2                                     | N2                                             | N2                                                                                                                   |                                                                                                                                                                                                                                           | N2 | These outputs are only active if the SCIANY input is a logic low. |

| LTXC[2]<br>LTXC[1]<br>LTXC[0]                                     |                          | M10<br>N10                 | Maximum clock rate is 50 MHz.                                                                                                                                                                                                                                |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

|                                                                   | Inp                      | ut Para                    | allel Bus – (SCIANY is logic high)                                                                                                                                                                                                                           |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

| IANYPHY                                                           | Input                    | J1                         | The Input Port Any-PHY configuration (IANYPHY) input determines the protocol of the SCI-PHY/Any-PHY input port interface. IANYPHY is only active if the SCIANY input is a logic high.                                                                        |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

|                                                                   |                          |                            | If IANYPHY is logic low, the interface complies to the SCI-PHY/Utopia specification.                                                                                                                                                                         |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

|                                                                   |                          |                            | If IANYPHY is logic high, the interface complies to<br>the Any-PHY specification. The Any-PHY protocol<br>is supported only when the input port cell interface<br>is configured as a bus slave (IMASTER input must<br>be set to logic 0 if IANYPHY is high). |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

|                                                                   |                          |                            | IANYPHY is an asynchronous input and is expected to be held static.                                                                                                                                                                                          |                      |                      |                      |                                        |                                                |                                                                                                                      |                                                                                                                                                                                                                                           |    |    |    |    |    |    |    |                                                                   |

PMC-Sierra, Inc.

DATA SHEET PMC-1980581

ISSUE 5

| Ball    |       | Ball |                                                                                                                                                                                                                                                                                     |

|---------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | Type  | No.  | Function                                                                                                                                                                                                                                                                            |