PM7384 FREEDM-84P672

DATA SHEET PMC-1990445

ISSUE 5

FRAME ENGINE AND DATA LINK MANAGER 84P672

## PM7384

# FREEDM™-84P672

# FRAME ENGINE AND DATALINK MANAGER 84P672

# **DATA SHEET**

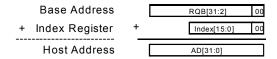

PROPRIETARY AND CONFIDENTIAL

**ISSUE 5: AUGUST 2001**

ISSUE 5

FRAME ENGINE AND DATA LINK MANAGER 84P672

#### **REVISION HISTORY**

| Issue No. | Issue<br>Date     | Details of Change                                                                    |

|-----------|-------------------|--------------------------------------------------------------------------------------|

| Issue 1   | April 10,<br>1999 | Document created.                                                                    |

| Issue 2   | July 7,<br>1999   | Document reissue.                                                                    |

| Issue 3   | January,<br>2000  | Document reissue.                                                                    |

| Issue 4   | July, 2000        | Document reissue. Minor corrections and changes to some DC and AC timing parameters. |

| Issue 5   | August,<br>2001   | Patent information added. Change bars reflect issue 4.                               |

FRAME ENGINE AND DATA LINK MANAGER 84P672

### **CONTENTS**

| 1 | FEAT  | URES     |                                            | 1  |

|---|-------|----------|--------------------------------------------|----|

| 2 | APPL  | ICATION  | S                                          | 3  |

| 3 | REFE  | RENCES   | S                                          | 4  |

| 4 | APPL  | ICATION  | EXAMPLES                                   | 5  |

| 5 | BLOC  | CK DIAGF | RAM                                        | 6  |

| 6 | DESC  | CRIPTION | ١                                          | 7  |

| 7 | PIN D | IAGRAM   | l                                          | 9  |

| 8 | PIN D | ESCRIP   | TION                                       | 10 |

| 9 | FUNC  | CTIONAL  | DESCRIPTION                                | 33 |

|   | 9.1   |          | ABLE BANDWIDTH INTERCONNECT (SBI) INTERFAC |    |

|   | 9.2   | HIGH-L   | EVEL DATA LINK CONTROL (HDLC) PROTOCOL     | 34 |

|   | 9.3   | SBI EXT  | FRACTER AND PISO                           | 35 |

|   | 9.4   | RECEIV   | /E CHANNEL ASSIGNER                        | 35 |

|   |       | 9.4.1    | LINE INTERFACE                             | 37 |

|   |       | 9.4.2    | PRIORITY ENCODER                           | 38 |

|   |       | 9.4.3    | CHANNEL ASSIGNER                           | 38 |

|   |       | 9.4.4    | LOOPBACK CONTROLLER                        | 38 |

|   | 9.5   | RECEIV   | /E HDLC PROCESSOR / PARTIAL PACKET BUFFER. | 38 |

|   |       | 9.5.1    | HDLC PROCESSOR                             | 39 |

|   |       | 9.5.2    | PARTIAL PACKET BUFFER PROCESSOR            | 39 |

|   | 9.6   | RECEIV   | /E DMA CONTROLLER                          | 41 |

|   |       | 9.6.1    | DATA STRUCTURES                            | 42 |

| E 5 | FRAME ENGINE AND DATA LINK MANAGER 84P672 |

|-----|-------------------------------------------|

|      | 9.6.2  | DMA TRANSACTION CONTROLLER                  | .52            |

|------|--------|---------------------------------------------|----------------|

|      | 9.6.3  | WRITE DATA PIPELINE/MUX                     | .52            |

|      | 9.6.4  | DESCRIPTOR INFORMATION CACHE                | .52            |

|      | 9.6.5  | FREE QUEUE CACHE                            | .53            |

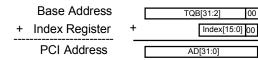

| 9.7  | PCI CO | NTROLLER                                    | .53            |

|      | 9.7.1  | MASTER MACHINE                              | .54            |

|      | 9.7.2  | MASTER LOCAL BUS INTERFACE                  | .56            |

|      | 9.7.3  | TARGET MACHINE                              | .57            |

|      | 9.7.4  | CBI BUS INTERFACE                           | .59            |

|      | 9.7.5  | ERROR / BUS CONTROL                         | .59            |

| 9.8  | TRANS  | MIT DMA CONTROLLER                          | .59            |

|      | 9.8.1  | DATA STRUCTURES                             | .60            |

|      | 9.8.2  | TASK PRIORITIES                             | .72            |

|      | 9.8.3  | DMA TRANSACTION CONTROLLER                  | .72            |

|      | 9.8.4  | READ DATA PIPELINE                          | .72            |

|      | 9.8.5  | DESCRIPTOR INFORMATION CACHE                | .72            |

|      | 9.8.6  | FREE QUEUE CACHE                            | .73            |

| 9.9  | TRANS  | MIT HDLC CONTROLLER / PARTIAL PACKET BUFFER | <b>R73</b>     |

|      | 9.9.1  | TRANSMIT HDLC PROCESSOR                     | .73            |

|      | 9.9.2  | TRANSMIT PARTIAL PACKET BUFFER PROCESSOR    | <del>274</del> |

| 9.10 | TRANS  | MIT CHANNEL ASSIGNER                        | .76            |

|      | 9.10.1 | LINE INTERFACE                              | .78            |

|      | 9.10.2 | PRIORITY ENCODER                            | .79            |

|      | 9.10.3 | CHANNEL ASSIGNER                            | .79            |

|      |        |                                             |                |

|    | 9.11   | SBI INS | ERTER AND SI   | PO          |       | <br>79  |

|----|--------|---------|----------------|-------------|-------|---------|

|    | 9.12   | PERFO   | RMANCE MON     | ITOR        |       | <br>80  |

|    | 9.13   | JTAG TE | EST ACCESS P   | ORT INTERFA | ACE   | <br>80  |

|    | 9.14   | PCI HOS | ST INTERFACE   |             |       | <br>80  |

| 10 | NORN   | MAL MOD | E REGISTER I   | DESCRIPTION | 1     | <br>87  |

|    | 10.1   | PCI HOS | ST ACCESSIBL   | E REGISTER  | S     | <br>87  |

| 11 | PCI C  | ONFIGU  | RATION REGIS   | TER DESCRI  | PTION | <br>284 |

|    | 11.1   | PCI COI | NFIGURATION    | REGISTERS   |       | <br>284 |

| 12 | TEST   | FEATUR  | RES DESCRIPT   | ION         |       | <br>295 |

|    | 12.1   | TEST M  | ODE REGISTE    | RS          |       | <br>295 |

|    | 12.2   | JTAG TE | EST PORT       |             |       | <br>297 |

|    |        | 12.2.1  | IDENTIFICATI   | ON REGISTE  | ₹     | <br>297 |

|    |        | 12.2.2  | BOUNDARY S     | CAN REGIST  | ER    | <br>298 |

| 13 | OPER   | RATIONS |                |             |       | <br>314 |

|    | 13.1   | JTAG SI | UPPORT         |             |       | <br>314 |

| 14 | FUNC   | TIONAL  | TIMING         |             |       | <br>321 |

|    | 14.1   | SBI DRO | OP BUS INTER   | FACE TIMING |       | <br>321 |

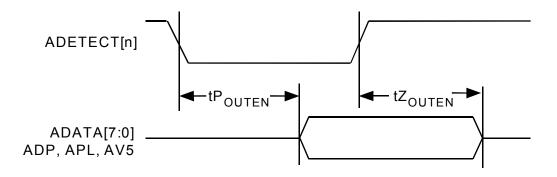

|    | 14.2   | SBI ADE | BUS INTERFA    | ACE TIMING  |       | <br>322 |

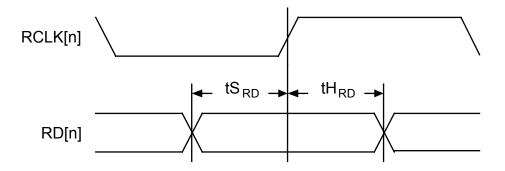

|    | 14.3   | RECEIV  | E LINK TIMING  | )           |       | <br>322 |

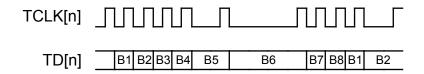

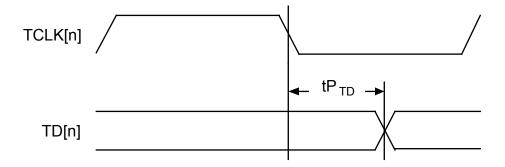

|    | 14.4   | TRANSI  | MIT LINK TIMIN | G           |       | <br>323 |

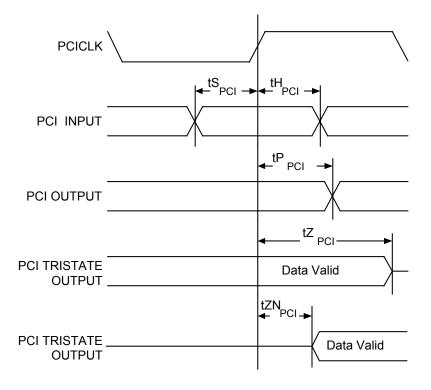

|    | 14.5   | PCI INT | ERFACE         |             |       | <br>323 |

| 15 | ABSC   | LUTE M  | AXIMUM RATIN   | IGS         |       | <br>333 |

| 16 | D.C. C | CHARAC  | TERISTICS      |             |       | <br>334 |

| 17 | FREE   | DM-84P6 | 672 TIMING CH  | ARACTERIST  | ICS   | <br>336 |

|    |        |         |                |             |       |         |

| DATA SHEET  |       |   |  |  |

|-------------|-------|---|--|--|

| PMC-1990445 | ISSUE | 5 |  |  |

| DAME    | <b>ENGINE</b> | AND   | DATA | IINK | MANA | CEP : | RAD672 |

|---------|---------------|-------|------|------|------|-------|--------|

| -KAIVIE | ENGINE        | ANU L | JAIA | LINN | WANA | GER ( | 04P0/Z |

| 18 | ORDERING AND THERMAL INFORMATION | 344 |

|----|----------------------------------|-----|

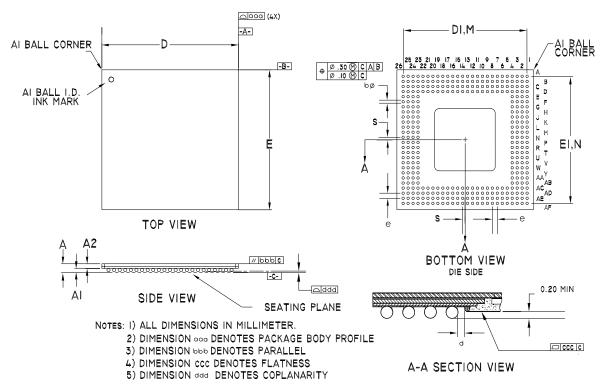

| 10 | MECHANICAL INFORMATION           | 345 |

FRAME ENGINE AND DATA LINK MANAGER 84P672

#### **LIST OF FIGURES**

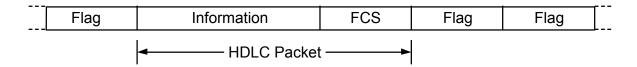

| FIGURE 1 – HDLC FRAME                                      | 34  |

|------------------------------------------------------------|-----|

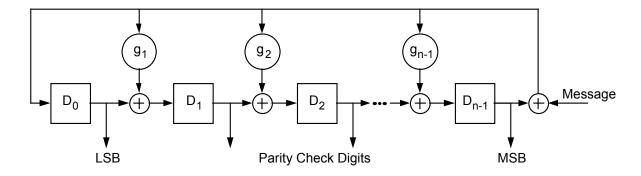

| FIGURE 2 – CRC GENERATOR                                   | 35  |

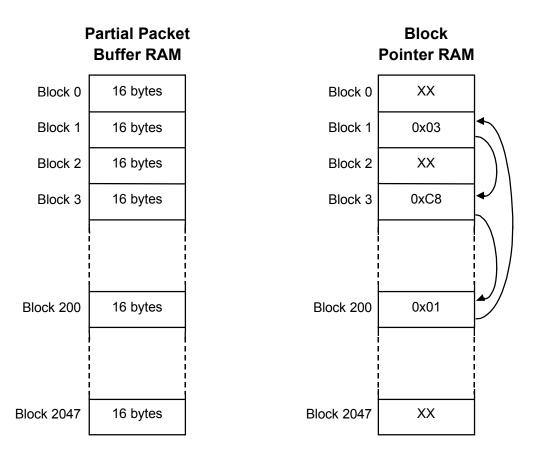

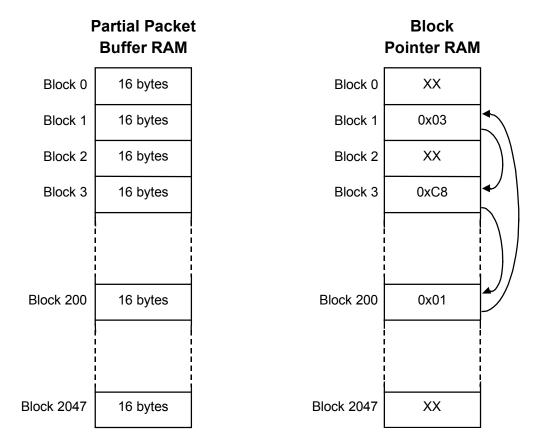

| FIGURE 3 – PARTIAL PACKET BUFFER STRUCTURE                 | 40  |

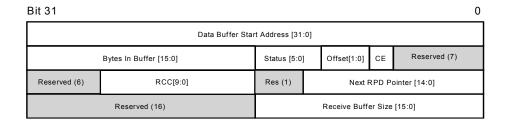

| FIGURE 4 – RECEIVE PACKET DESCRIPTOR                       | 42  |

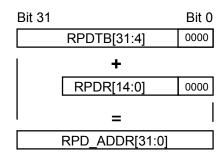

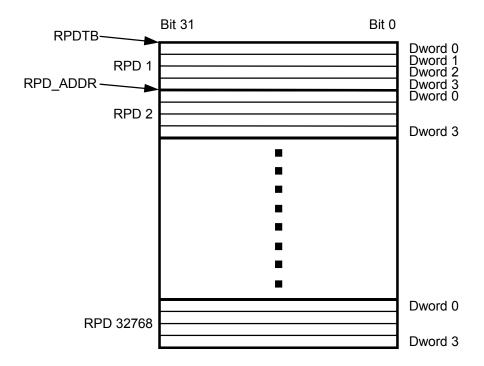

| FIGURE 5 – RECEIVE PACKET DESCRIPTOR TABLE                 | 45  |

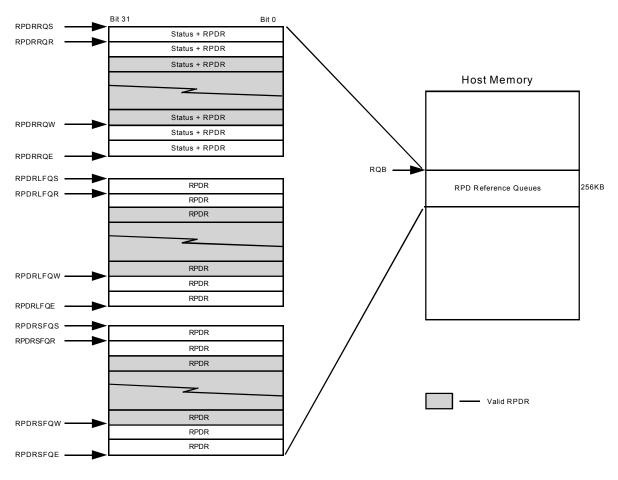

| FIGURE 6 – RPDRF AND RPDRR QUEUES                          | 48  |

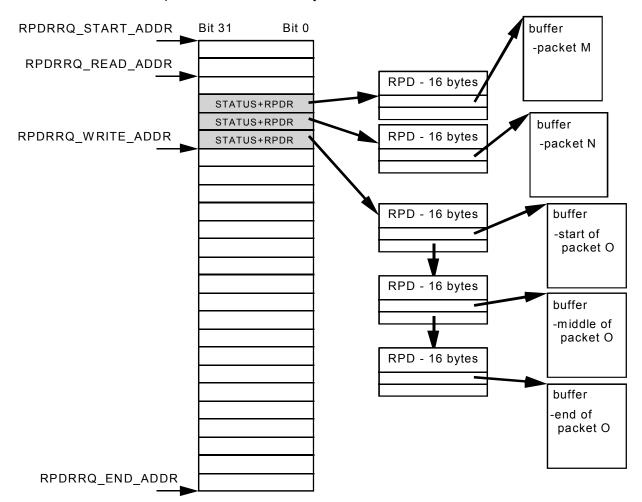

| FIGURE 7 – RPDRR QUEUE OPERATION                           | 50  |

| FIGURE 8 – RECEIVE CHANNEL DESCRIPTOR REFERENCE TABLE      | 51  |

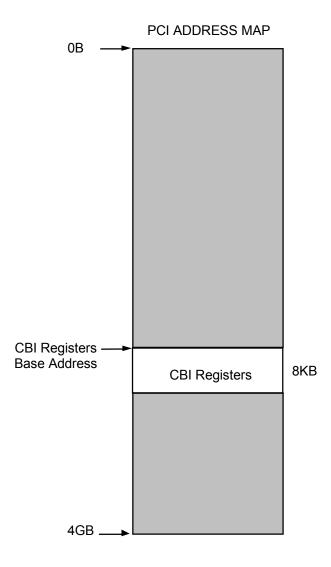

| FIGURE 9 – GPIC ADDRESS MAP                                | 58  |

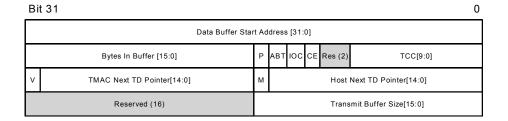

| FIGURE 10 – TRANSMIT DESCRIPTOR                            | 60  |

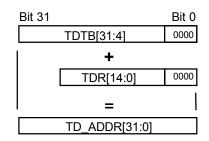

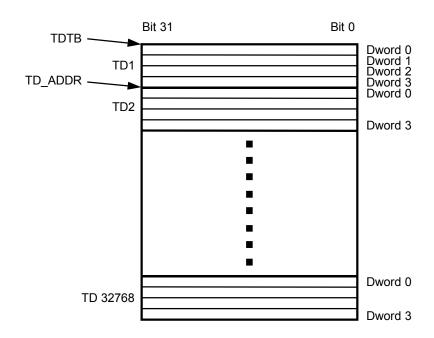

| FIGURE 11 – TRANSMIT DESCRIPTOR TABLE                      | 64  |

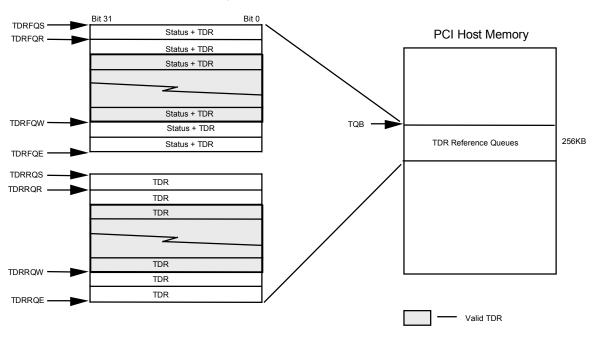

| FIGURE 12 – TDRR AND TDRF QUEUES                           | 66  |

| FIGURE 13 – TRANSMIT CHANNEL DESCRIPTOR REFERENCE TABLE    | 68  |

| FIGURE 14 – TD LINKING                                     | 71  |

| FIGURE 15 – PARTIAL PACKET BUFFER STRUCTURE                | 75  |

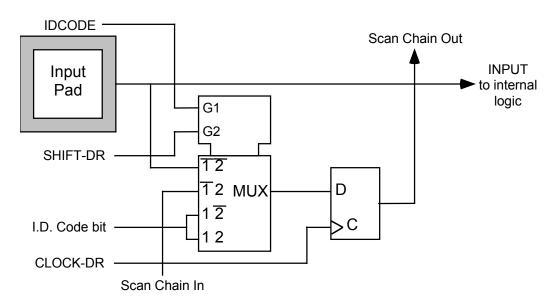

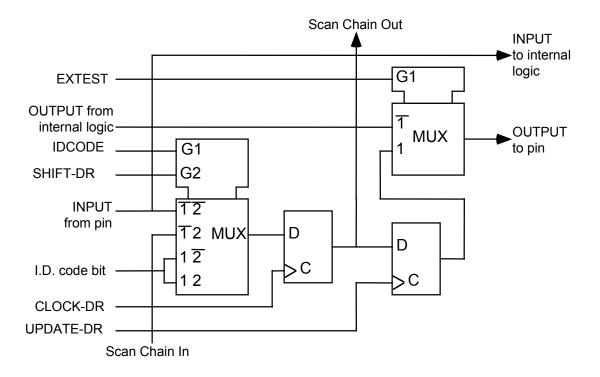

| FIGURE 16 – INPUT OBSERVATION CELL (IN_CELL)               | 311 |

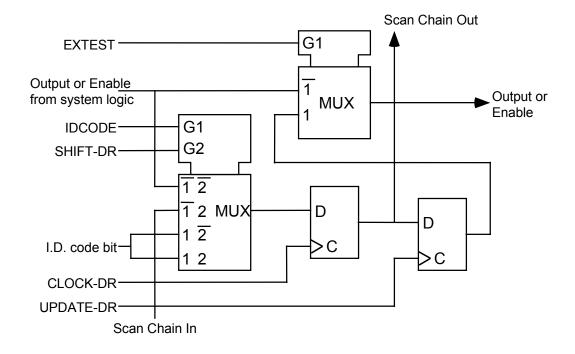

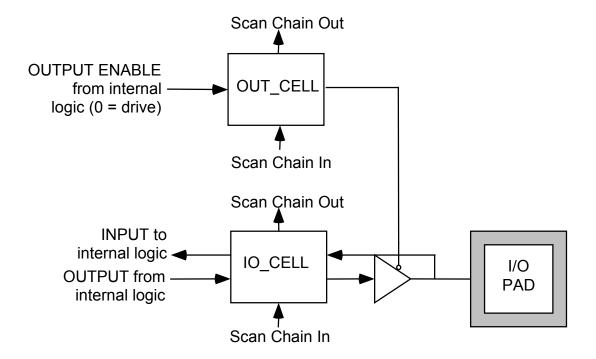

| FIGURE 17 – OUTPUT CELL (OUT_CELL)                         | 312 |

| FIGURE 18 – BI-DIRECTIONAL CELL (IO_CELL)                  | 312 |

| FIGURE 19 – LAYOUT OF OUTPUT ENABLE AND BI-DIRECTIONAL CEL | _   |

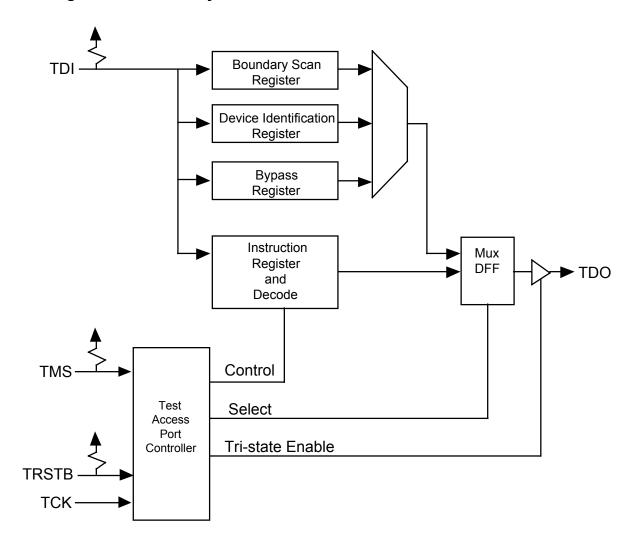

| FIGURE 20 – BOUNDARY SCAN ARCHITECTURE                     | 315 |

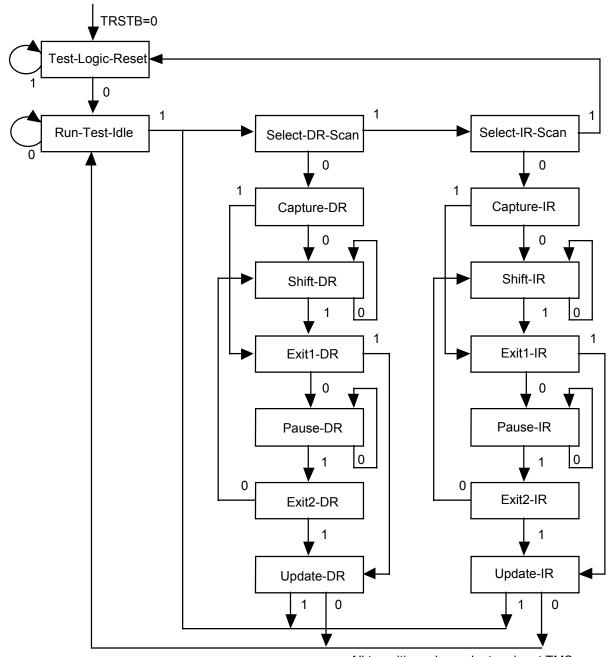

| FIGURE 21 – TAP CONTROLLER FINITE STATE MACHINE            | 317 |

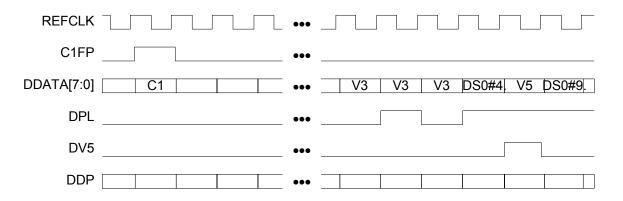

| FIGURE 22 – T1/E1 DROP BUS FUNCTIONAL TIMING               | 321 |

| FIGURE 23 – DS3 DROP BUS FUNCTIONAL TIMING                | 321 |

|-----------------------------------------------------------|-----|

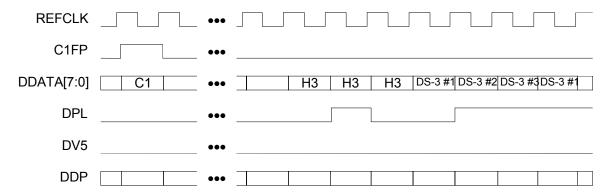

| FIGURE 24 – DS3 ADD BUS ADJUSTMENT REQUEST FUNCTIONAL TII |     |

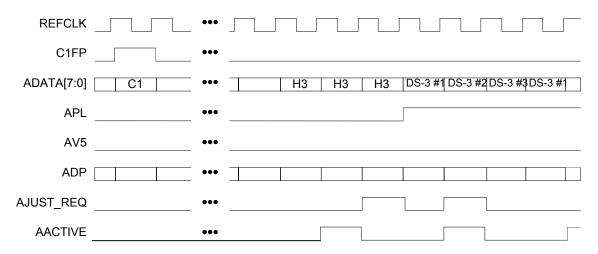

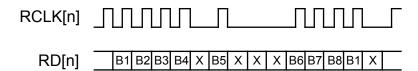

| FIGURE 25 – RECEIVE LINK TIMING                           |     |

| FIGURE 26 – TRANSMIT LINK TIMING                          | 323 |

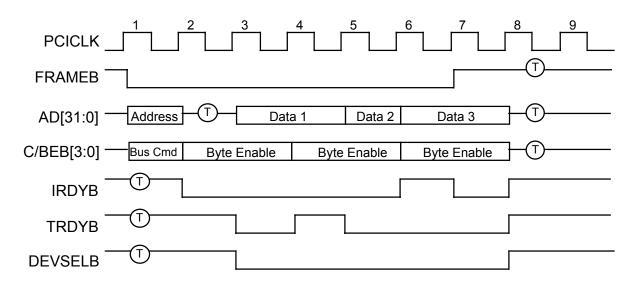

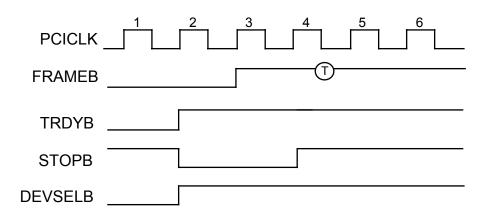

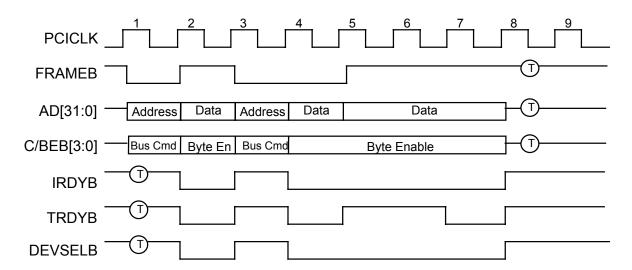

| FIGURE 27 – PCI READ CYCLE                                | 325 |

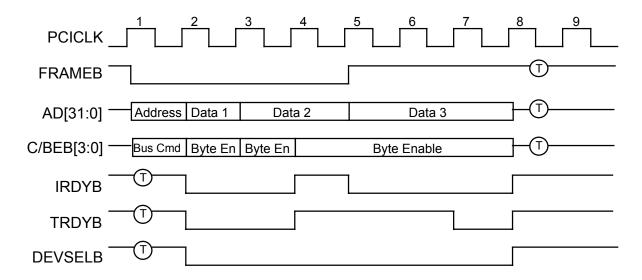

| FIGURE 28 – PCI WRITE CYCLE                               | 326 |

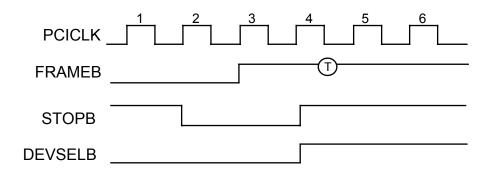

| FIGURE 29 – PCI TARGET DISCONNECT                         | 327 |

| FIGURE 30 – PCI TARGET ABORT                              | 328 |

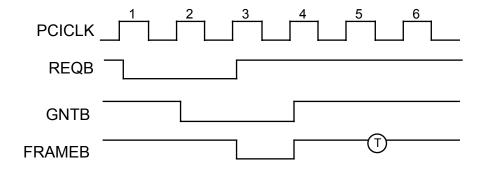

| FIGURE 31 – PCI BUS REQUEST CYCLE                         | 328 |

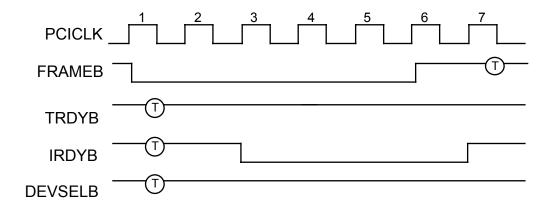

| FIGURE 32 – PCI INITIATOR ABORT TERMINATION               | 329 |

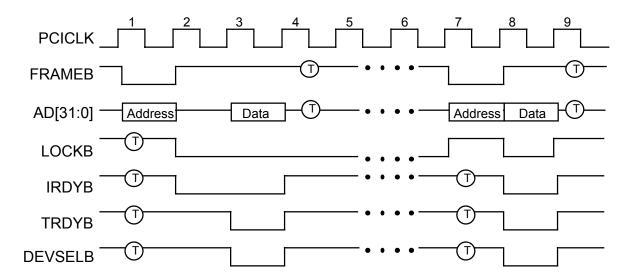

| FIGURE 33 – PCI EXCLUSIVE LOCK CYCLE                      | 330 |

| FIGURE 34 – PCI FAST BACK TO BACK                         | 332 |

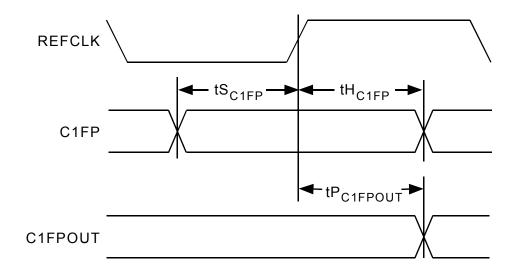

| FIGURE 35 – SBI FRAME PULSE TIMING                        | 337 |

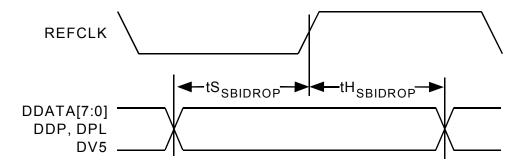

| FIGURE 36 – SBI DROP BUS TIMING                           | 338 |

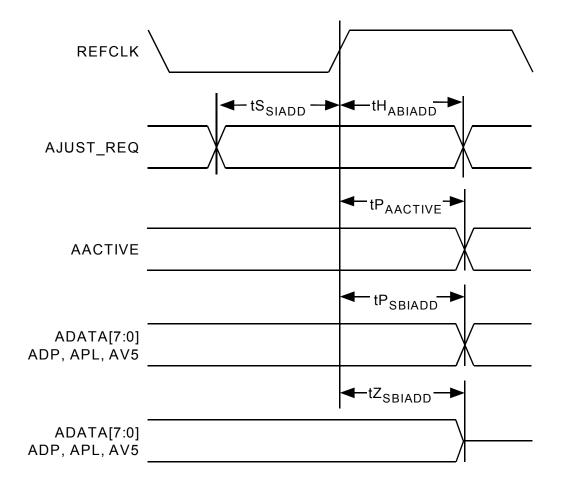

| FIGURE 37 – SBI ADD BUS TIMING                            | 339 |

| FIGURE 38 – SBI ADD BUS COLLISION AVOIDANCE TIMING        | 339 |

| FIGURE 39 – RECEIVE DATA TIMING                           | 340 |

| FIGURE 40 – TRANSMIT DATA TIMING                          | 340 |

| FIGURE 41 – PCI INTERFACE TIMING                          | 342 |

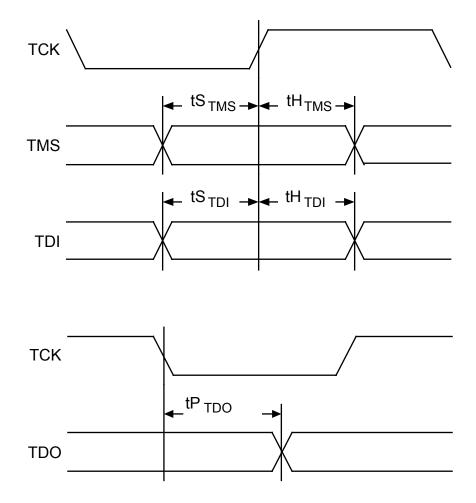

| FIGURE 42 – JTAG PORT INTERFACE TIMING                    | 343 |

| FIGURE 43 – 352 PIN ENHANCED BALL GRID ARRAY (SBGA)       | 345 |

FRAME ENGINE AND DATA LINK MANAGER 84P672

#### **LIST OF TABLES**

| TABLE 1 – SBI INTERFACE SIGNALS (30)                          | 10    |

|---------------------------------------------------------------|-------|

| TABLE 2 – CLOCK/DATA INTERFACE SIGNALS (15)                   | 16    |

| TABLE 3 – PCI HOST INTERFACE SIGNALS (52)                     | 18    |

| TABLE 4 – MISCELLANEOUS INTERFACE SIGNALS (160)               | 27    |

| TABLE 5 – PRODUCTION TEST INTERFACE SIGNALS (31)              | 28    |

| TABLE 6 – POWER AND GROUND SIGNALS (64)                       | 30    |

| TABLE 7 – SBI SPE/TRIBUTARY TO RCAS LINK MAPPING              | 36    |

| TABLE 8 – RECEIVE PACKET DESCRIPTOR FIELDS                    | 43    |

| TABLE 9 – RPDRR QUEUE ELEMENT                                 | 49    |

| TABLE 10 – RECEIVE CHANNEL DESCRIPTOR REFERENCE TABLE FIEL    |       |

| TABLE 11 – TRANSMIT DESCRIPTOR FIELDS                         | 61    |

| TABLE 12 – TRANSMIT DESCRIPTOR REFERENCE                      | 67    |

| TABLE 13 – TRANSMIT CHANNEL DESCRIPTOR REFERENCE TABLE FIELDS | 69    |

| TABLE 14 – SBI SPE/TRIBUTARY TO TCAS LINK MAPPING             | 77    |

| TABLE 15 – NORMAL MODE PCI HOST ACCESSIBLE REGISTER MEMOR     |       |

| TABLE 16 – PCI CONFIGURATION REGISTER MEMORY MAP              | 85    |

| TABLE 17 – SPE TYPE CONFIGURATION                             | . 118 |

| TABLE 18 – FASTCLK FREQUENCY SELECTION                        | . 119 |

| TABLE 19 – SPE TYPE CONFIGURATION                             | .121  |

| TABLE 20 – FASTCLK FREQUENCY SELECTION                        | .121  |

| TABLE 21 – BIG ENDIAN FORMAT                                  | .123  |

| TABLE 22 – LITTLE ENDIAN FORMAT              | 123        |

|----------------------------------------------|------------|

| TABLE 23 – SBI MODE SPE1 CONFIGURATION       | 132        |

| TABLE 24 – SBI MODE SPE2 CONFIGURATION       | 136        |

| TABLE 25 – SBI MODE SPE3 CONFIGURATION       | 140        |

| TABLE 26 – CRC[1:0] SETTINGS                 | 150        |

| TABLE 27 – RPQ_RDYN[2:0] SETTINGS            | 161        |

| TABLE 28 – RPQ_LFN[1:0] SETTINGS             | 162        |

| TABLE 29 – RPQ_SFN[1:0] SETTINGS             | 162        |

| TABLE 30 – TDQ_RDYN[2:0] SETTINGS            | 196        |

| TABLE 31 – TDQ_FRN[1:0] SETTINGS             | 196        |

| TABLE 32 – CRC[1:0] SETTINGS                 | 224        |

| TABLE 33 – FLAG[2:0] SETTINGS                | 230        |

| TABLE 34 – LEVEL[3:0]/TRANS SETTINGS         | 232        |

| TABLE 35 – SBI MODE SPE1 CONFIGURATION       | 248        |

| TABLE 36 – SBI MODE SPE2 CONFIGURATION       | 252        |

| TABLE 37 – SBI MODE SPE3 CONFIGURATION       | 256        |

| TABLE 38 – TRIB_TYP ENCODING                 | 276        |

| TABLE 39 – TRIB_TYP ENCODING                 | 283        |

| TABLE 40 – TEST MODE REGISTER MEMORY MAP     | 296        |

| TABLE 41 – INSTRUCTION REGISTER              | 297        |

| TABLE 42 – BOUNDARY SCAN CHAIN               | 298        |

| TABLE 43 – FREEDM-84P672 ABSOLUTE MAXIMUM I  | RATINGS333 |

| TABLE 44 – FREEDM-84P672 D.C. CHARACTERISTIC | S334       |

| TABLE 45 – CLOCKS AND SBI FRAME PULSE (FIGUR | RE 35)336  |

ISSUE 5

| TABLE 46 – SBI DROP BUS (FIGURE 36)             | 337  |

|-------------------------------------------------|------|

| TABLE 47 – SBI ADD BUS (FIGURE 37 TO FIGURE 38) | .338 |

| TABLE 48 – CLOCK/DATA INPUT (FIGURE 39)         | .340 |

| TABLE 49 – CLOCK/DATA OUTPUT (FIGURE 40)        | 340  |

| TABLE 50 – PCI INTERFACE (FIGURE 41)            | .341 |

| TABLE 51 – JTAG PORT INTERFACE (FIGURE 42)      | 342  |

| TABLE 52 – FREEDM-84P672 ORDERING INFORMATION   | 344  |

| TABLE 53 – EREEDM-84P672 THERMAL INFORMATION    | 344  |

FRAME ENGINE AND DATA LINK MANAGER 84P672

#### 1 FEATURES

- Single-chip multi-channel HDLC controller with a 66 MHz, 32 bit Peripheral Component Interconnect (PCI) Revision 2.1 bus for configuration, monitoring and transfer of packet data, with an on-chip DMA controller with scatter/ gather capabilities.

- Supports up to 672 bi-directional HDLC channels assigned to a maximum of 84 channelised or unchannelised links conveyed via a Scaleable Bandwidth Interconnect (SBI) interface.

- Data on the SBI interface is divided into 3 Synchronous Payload Envelopes (SPEs). Each SPE can be configured independently to carry data for either 28 T1/J1 links, 21 E1 links, or 1 unchannelised DS-3 link.

- Links in a SPE can be configured individually to operate in a clear channel mode, in which case all framing bit locations are assumed to be carrying HDLC data.

- Links in an SPE can be configured individually to operate in channelised mode, in which case, the number of time-slots assigned to an HDLC channel is programmable from 1 to 24 (for T1/J1 links) and from 1 to 31 (for E1 links).

- Supports three bi-directional HDLC channels each assigned to an unchannelised link with arbitrary rate link of up to 51.84 MHz when SYSCLK is running at 45 MHz. Each link may be configured individually to replace one of the SPEs conveyed on the SBI interface.

- For each channel, the HDLC receiver supports programmable flag sequence detection, bit de-stuffing and frame check sequence validation. The receiver supports the validation of both CRC-CCITT and CRC-32 frame check sequences.

- For each channel, the receiver checks for packet abort sequences, octet aligned packet length and for minimum and maximum packet length. The receiver supports filtering of packets that are larger than a user specified maximum value.

- Alternatively, for each channel, the receiver supports a transparent mode where each octet is transferred transparently to host memory. For channelised links, the octets are aligned with the receive time-slots.

- For each channel, time-slots are selectable to be in 56 kbits/s format or 64 kbits/s clear channel format.

- For each channel, the HDLC transmitter supports programmable flag sequence generation, bit stuffing and frame check sequence generation. The transmitter supports the generation of both CRC-CCITT and CRC-32 frame check sequences. The transmitter also aborts packets under the direction of the host or automatically when the channel underflows.

- Supports two levels of non-preemptive packet priority on each transmit channel. Low priority packets will not begin transmission until all high priority packets are transmitted.

- Alternatively, for each channel, the transmitter supports a transparent mode where each octet is inserted transparently from host memory. For channelised links, the octets are aligned with the transmit time-slots.

- Provides 32 Kbytes of on-chip memory for partial packet buffering in both the transmit and receive directions. This memory may be configured to support a variety of different channel configurations from a single channel with 32 Kbytes of buffering to 672 channels, each with a minimum of 48 bytes of buffering.

- Supports PCI burst sizes of up to 256 bytes for transfers of packet data.

- Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

- Supports 3.3 Volt PCI signaling environment.

- Supports 3.3 Volt I/O on non-PCI signals.

- Low power 2.5 Volt 0.25 μm CMOS technology.

- 352 pin enhanced ball grid array (SBGA) package.

FRAME ENGINE AND DATA LINK MANAGER 84P672

#### 2 APPLICATIONS

- IETF PPP interfaces for routers

- Frame Relay interfaces for ATM or Frame Relay switches and multiplexers

- FUNI or Frame Relay service inter-working interfaces for ATM switches and multiplexers.

- Internet/Intranet access equipment.

- Packet-based DSLAM equipment.

- Packet over SONET.

- PPP over SONET.

FRAME ENGINE AND DATA LINK MANAGER 84P672

#### 3 REFERENCES

- International Organization for Standardization, ISO Standard 3309-1993, "Information Technology – Telecommunications and information exchange between systems – High-level data link control (HDLC) procedures – Frame structure", December 1993.

- 2. RFC-1662 "PPP in HDLC-like Framing" Internet Engineering Task Force, July 1994.

- 3. PCI Special Interest Group, PCI Local Bus Specification, June 1, 1995, Version 2.1.

- 4. PMC-981125 "High Density T1/E1 Framer with Integrated VT/TU Mapper and M13 Multiplexer (TEMUX) Data Sheet", PMC-Sierra Inc.

FRAME ENGINE AND DATA LINK MANAGER 84P672

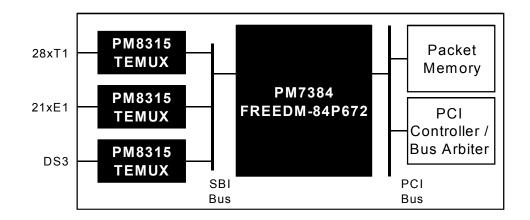

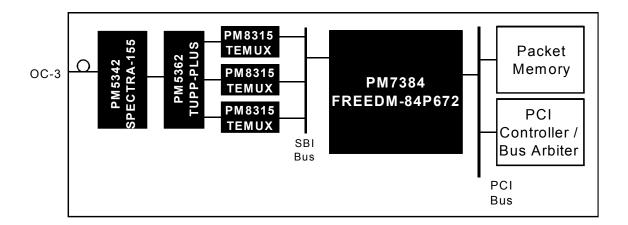

#### 4 <u>APPLICATION EXAMPLES</u>

FRAME ENGINE AND DATA LINK MANAGER 84P672

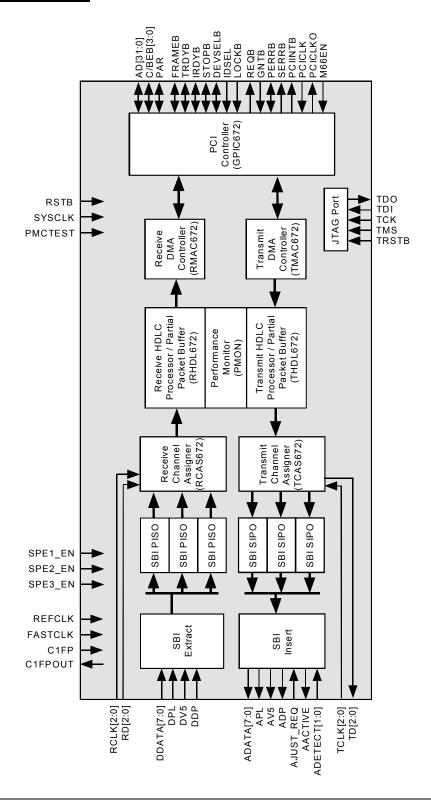

#### 5 BLOCK DIAGRAM

FRAME ENGINE AND DATA LINK MANAGER 84P672

#### 6 DESCRIPTION

The PM7384 FREEDM-84P672 Frame Engine and Datalink Manager device is a monolithic integrated circuit that implements HDLC processing, and PCI Bus memory management functions for a maximum of 672 bi-directional channels.

The FREEDM-84P672 may be configured to support channelised T1/J1/E1 or unchannelised DS-3 traffic on up to 84 links conveyed via a Scaleable Bandwidth Interconnect (SBI) interface. The SBI interface transports data in three Synchronous Payload Envelopes (SPEs), each of which may be configured independently to carry either 28 T1/J1 links, 21 E1 links or a single DS-3 link.

For channelised T1/J1/E1 links, the FREEDM-84P672 allows up to 672 bidirectional HDLC channels to be assigned to individual time-slots within each independently timed T1/J1 or E1 link. The channel assignment supports the concatenation of time-slots (N x DS0) up to a maximum of 24 concatenated time-slots for a T1/J1 link and 31 concatenated time-slots for an E1 link. Time-slots assigned to any particular channel need not be contiguous within a T1/J1 or E1 link. Unchannelised DS-3 links are assigned to a single HDLC channel.

Additionally, links may be configured independently to operate in an unframed or "clear channel" mode, in which the bit periods which are normally reserved for framing information in fact carry HDLC data. In unframed mode, links operate as unchannelised (i.e. the entire link is assigned to a single HDLC channel) regardless of link rate.

The FREEDM-84P672 supports mixing of channelised T1/J1/E1 and unchannelised or unframed links. The total number of channels in each direction is limited to 672. The maximum possible data rate over all links is 134.208 Mbps (which occurs with three DS-3 links running in unframed mode).

The FREEDM-84P672 supports three independently timed bidirectional clock/data links, each carrying a single unchannellised HDLC stream. The links can be of arbitrary frame format and can operate at up to 51.84 MHz provided SYSCLK is running at 45 MHz. When activated, each link replaces one of the SPEs conveyed on the SBI interface. (The maximum possible data rate when all three clock/data links are activated is 156 Mbps.)

In the receive direction, the FREEDM-84P672 performs channel assignment and packet extraction and validation. For each provisioned HDLC channel, the FREEDM-84P672 delineates the packet boundaries using flag sequence detection, and performs bit de-stuffing. Sharing of opening and closing flags, as well as sharing of zeros between flags are supported. The resulting packet data is placed into the internal 32 Kbyte partial packet buffer RAM. The partial packet

ISSUE 5

FRAME ENGINE AND DATA LINK MANAGER 84P672

buffer acts as a logical FIFO for each of the assigned channels. Partial packets are DMA'd out of the RAM, across the PCI bus and into host packet memory. The FREEDM-84P672 validates the frame check sequence for each packet, and verifies that the packet is an integral number of octets in length and is within a programmable minimum and maximum length. The receive packet status is updated before linking the packet into a receive ready queue. The FREEDM-84P672 alerts the PCI Host that there are packets in a receive ready queue by, optionally, asserting an interrupt on the PCI bus.

Alternatively, in the receive direction, the FREEDM-84P672 supports a transparent operating mode. For each provisioned transparent channel, the FREEDM-84P672 directly transfers the received octets into host memory verbatim. If the transparent channel is assigned to a channelised link, then the octets are aligned to the received time-slots.

In the transmit direction, the PCI Host provides packets to transmit using a transmit ready queue. For each provisioned HDLC channel, the FREEDM-84P672 DMA's partial packets across the PCI bus and into the transmit partial packet buffer. The partial packets are read out of the packet buffer by the FREEDM-84P672 and a frame check sequence is optionally calculated and inserted at the end of each packet. Bit stuffing is performed before being assigned to a particular link. The flag sequence is automatically inserted when there is no packet data for a particular channel. Sequential packets are optionally separated by two flags (an opening flag and a closing flag) or a single flag (combined opening and closing flag). Zeros between flags are not shared. PCI bus latency may cause one or more channels to underflow, in which case, the packets are aborted, and the host is notified. For normal traffic, an abort sequence is generated, followed by inter-frame time fill characters (flags or allones bytes) until a new packet is sourced from the PCI host. No attempt is made to automatically re-transmit an aborted packet.

Alternatively, in the transmit direction, the FREEDM-84P672 supports a transparent operating mode. For each provisioned transparent channel, the FREEDM-84P672 directly inserts the transmitted octets from host memory. If the transparent channel is assigned to a channelised link, then the octets are aligned to the transmitted time-slots. If a channel underflows due to excessive PCI bus latency, an abort sequence is generated, followed by inter-frame time fill characters (flags or all-ones bytes) to indicate idle channel. Data resumes immediately when the FREEDM-84P672 receives new data from the host.

The FREEDM-84P672 is configured, controlled and monitored using the PCI bus interface. The PCI bus supports 3.3 Volt signaling. The FREEDM-84P672 is implemented in low power 2.5 Volt 0.25  $\mu$ m CMOS technology. All non-PCI FREEDM-84P672 I/O pins are 3.3 volt tolerant. The FREEDM-84P672 is packaged in a 352 pin enhanced ball grid array (SBGA) package.

ISSUE 5

FRAME ENGINE AND DATA LINK MANAGER 84P672

#### 7 PIN DIAGRAM

The FREEDM-84P672 is manufactured in a 352 pin enhanced ball grid array package.

|    | 26       | 25      | 24      | 23      | 22      | 21        | 20   | 19        | 18        | 17        | 16   | 15      | 14       | 13      | 12        | 11           | 10           | 9              | 8            | 7            | 6            | 5            | 4        | 3       | 2       | 1       |    |

|----|----------|---------|---------|---------|---------|-----------|------|-----------|-----------|-----------|------|---------|----------|---------|-----------|--------------|--------------|----------------|--------------|--------------|--------------|--------------|----------|---------|---------|---------|----|

| A  | VSS      | VSS     | N.C.    | N.C.    | N.C.    | VDD2V5    | N.C. | N.C.      | N.C.      | N.C.      | N.C. | N.C.    | VSS      | VSS     | N.C.      | N.C.         | N.C.         | N.C.           | N.C.         | N.C.         | VDD2V5       | N.C.         | N.C.     | N.C.    | VSS     | VSS     | A  |

| В  | VSS      | VDD3V3  | VSS     | N.C.    | N.C.    | N.C.      | N.C. | N.C.      | N.C.      | N.C.      | N.C. | N.C.    | N.C.     | VDD2V5  | N.C.      | N.C.         | N.C.         | TA[12]/<br>TRS | TWRB         | N.C.         | TA[10]       | TA[8]        | TA[6]    | VSS     | VDD3V3  | VSS     | В  |

| С  | N.C.     | VSS     | VDD3V3  | N.C.    | N.C.    | N.C.      | N.C. | N.C.      | N.C.      | N.C.      | N.C. | N.C.    | N.C.     | N.C.    | N.C.      | N.C.         | N.C.         | N.C.           | TRDB         | N.C.         | N.C.         | N.C.         | N.C.     | VDD3V3  | VSS     | N.C.    | С  |

| D  | N.C.     | N.C.    | N.C.    | VDD3V3  | N.C.    | N.C.      | N.C. | N.C.      | VDD3V3    | N.C.      | N.C. | N.C.    | VDD3V3   | N.C.    | N.C.      | N.C.         | N.C.         | VDD3V3         | TA[11]       | TA[9]        | TA[7]        | N.C.         | VDD3V3   | N.C.    | TA[5]   | N.C.    | D  |

| E  | N.C.     | N.C.    | N.C.    | N.C.    |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | N.C.     | RSTB    | TA[4]   | N.C.    | E  |

| F  | N.C.     | N.C.    | N.C.    | N.C.    |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | N.C.     | N.C.    | TA[2]   | N.C.    | F  |

| G  | PCICLKO  | N.C.    | VDD2V5  | N.C.    |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | TA[3]    | N.C.    | TA[1]   | TA[0]   | G  |

| Н  | REQB     | N.C.    | PCIINTB | N.C.    |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | VDD2V5   | N.C.    | N.C.    | N.C.    | Н  |

| J  | AD[29]   | AD[31]  | PCICLK  | VDD3V3  |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | VDD3V3   | N.C.    | N.C.    | N.C.    | J  |

| K  | AD[25]   | AD[27]  | AD[30]  | GNTB    |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | N.C.     | N.C.    | N.C.    | N.C.    | K  |

| L  | N.C.     | AD[24]  | AD [26] | AD[28]  |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | N.C.     | N.C.    | N.C.    | SYSCLK  | L  |

| М  | AD[23]   | N.C.    | IDSEL   | CBEB[3] |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | N.C.     | N.C.    | N.C.    | N.C.    | М  |

| N  | VSS      | VDD2V5  | AD[21]  | AD[22]  |         |           |      |           |           |           |      | вот     | том      | VIE     | EW        |              |              |                |              |              |              |              | VDD3V3   | N.C.    | N.C.    | VSS     | N  |

| P  | VSS      | AD[20]  | AD[19]  | VDD3V3  |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | VDD2V5   | RCLK[2] | N.C.    | VSS     | P  |

| R  | AD[18]   | AD[17]  | AD[16]  | FRAMEB  |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | RD[0]    | RD[1]   | RCLK[1] | RD[2]   | R  |

| T  | CBEB [2] | IRDYB   | DEVSELB | LOCKB   |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | N.C.     | N.C.    | N.C.    | RCLK[0] | т  |

| U  | TRDYB    | STOPB   | SERRB   | AD[15]  |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | TCK      | N.C.    | N.C.    | N.C.    | U  |

| v  | PERRB    | PAR     | AD[14]  | VDD3V3  |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | VDD3V3   | TDI     | TRSTB   | N.C.    | v  |

| W  | CBEB[1]  | AD[13]  | AD[11]  | AD [9]  |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | SPE3_EN  | N.C.    | TDO     | TMS     | W  |

| Y  | AD[12]   | AD[10]  | AD[8]   | AD[6]   |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | TD[1]    | VDD2V5  | SPE1_EN | FASTCLK | Y  |

| AA | VDD2V5   | CBEB[0] | AD[5]   | AD[2]   |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | C1FP_OUT | TCLK[1] | TD[0]   | SPE2_EN | AA |

| AB | AD[7]    | AD[4]   | AD[1]   | N.C.    |         |           |      |           |           |           |      |         |          |         |           |              |              |                |              |              |              |              | AV5      | REFCLK  | TD[2]   | TCLK[0] | AB |

| AC | AD[3]    | AD[0]   | N.C.    | VDD3V3  | N.C.    | N.C.      | N.C. | TDAT [14] | VDD3V3    | TDAT [11] | N.C. | TDAT[7] | N.C.     | VDD3V3  | AJUST_REQ | ADATA<br>[7] | DDATA<br>[4] | VDD3V3         | DDATA        | N.C.         | DDP          | N.C.         | VDD3V3   | N.C.    | APL     | TCLK[2] | AC |

| AD | N.C.     | VSS     | VDD3V3  | N.C.    | N.C.    | N.C.      | N.C. | TDAT [13] | N.C.      | N.C.      | N.C. | TDAT[6] | TDAT [4] | TDAT[3] | ADSTRUT   | N.C.         | ADATA<br>[6] | ADATA<br>[4]   | DDATA<br>[2] | ADATA        | N.C.         | ADP          | N.C.     | VDD3V3  | VSS     | DPL     | AD |

| AE | VSS      | VDD3V3  | VSS     | M66EN   | PMCTEST | TDAT [15] | N.C. | TDAT [12] | TDAT [10] | TDAT[8]   | N.C. | N.C.    | VDD2V5   | N.C.    | TDAT[2]   | TDAT[0]      | DDATA<br>[7] | DDATA<br>[5]   | DDATA<br>[3] | ADATA<br>[2] | DDATA<br>[0] | CIFP         | DV5      | VSS     | VDD3V3  | VSS     | AE |

| AF | VSS      | vss     | n.c.    | N.C.    | N.C.    | VDD2V5    | N.C. | N.C.      | TDAT[9]   | N.C.      | N.C. | TDAT[5] | VSS      | VSS     | ADSTRUT   | TDAT[1]      | N.C.         | DDATA<br>[6]   | ADATA<br>[5] | ADATA<br>[3] | VDD2V5       | ADATA<br>[0] | AACTIVE  | N.C.    | VSS     | VSS     | AF |

|    | 26       | 25      | 24      | 22      | 22      | 21        | 20   | 10        | 10        | 12        | 16   | 15      | 14       | 12      | 10        | 11           | 10           | 0              | ^            | -            |              | -            |          | 2       | 2       | 1       |    |

ISSUE 5

FRAME ENGINE AND DATA LINK MANAGER 84P672

#### 8 PIN DESCRIPTION

## Table 1 - SBI Interface Signals (30)

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLK   | Input | AB3        | The SBI reference clock signal (REFCLK) provides reference timing for the SBI ADD and DROP busses.                                                                                                                                                                                                                                                                         |

|          |       |            | REFCLK is nominally a 50% duty cycle clock of frequency 19.44 MHz ±50ppm.                                                                                                                                                                                                                                                                                                  |

| FASTCLK  | Input | Y1         | The high-speed reference clock signal (FASTCLK) is used by the FREEDM-84P672 to generate an internal clock for use when processing DS-3 links.                                                                                                                                                                                                                             |

|          |       |            | FASTCLK is nominally a 50% duty cycle, ±50ppm clock having one of the following frequencies: 51.84 MHz, 44.928 MHz or 66 MHz.                                                                                                                                                                                                                                              |

| C1FP     | Input | AE5        | The C1 octet frame pulse signal (C1FP) provides frame synchronisation for devices connected via an SBI interface. C1FP must be asserted for 1 REFCLK cycle every 500 µs or multiples thereof (i.e. every 9720 n REFCLK cycles, where n is a positive integer). All devices interconnected via an SBI interface must be synchronised to a C1FP signal from a single source. |

|          |       |            | C1FP is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                              |

|          |       |            | Note – If the SBI bus is being operated in synchronous mode [Ref. 4], C1FP must be asserted for 1 REFCLK cycle every 6 ms or multiples thereof.                                                                                                                                                                                                                            |

ISSUE 5

| Pin Name                                                                | Туре   | Pin<br>No.                                             | Function                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------|--------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1FPOUT                                                                 | Output | AA4                                                    | The C1 octet frame pulse output signal (C1FPOUT) may be used to provide frame synchronisation for devices interconnected via an SBI interface. C1FPOUT is asserted for 1 REFCLK cycle every 500 µs (i.e. every 9720 REFCLK cycles). If C1FPOUT is used for synchronisation, it must be connected to the C1FP inputs of all the devices connected to the SBI interface. |

|                                                                         |        |                                                        | C1FPOUT is updated on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                       |

|                                                                         |        |                                                        | Note – The C1FPOUT pulse generated by FREEDM-84P672 is not suitable for use in systems in which the SBI bus is operated in synchronous mode [Ref. 4].                                                                                                                                                                                                                  |

| DDATA[0] DDATA[1] DDATA[2] DDATA[3] DDATA[4] DDATA[5] DDATA[6] DDATA[7] | Input  | AE6<br>AC8<br>AD8<br>AE8<br>AC10<br>AE9<br>AF9<br>AE10 | The SBI DROP bus data signals (DDATA[7:0]) contain the time division multiplexed receive data from the up to 84 independently timed links. Data from each link is transported as a tributary within the SBI TDM bus structure. Multiple PHY devices can drive the SBI DROP bus at uniquely assigned tributary column positions.                                        |

|                                                                         |        |                                                        | DDATA[7:0] are sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                   |

| DDP                                                                     | Input  | AC6                                                    | The SBI DROP bus parity signal (DDP) carries the even or odd parity for the DROP bus signals. The parity calculation encompasses the DDATA[7:0], DPL and DV5 signals.                                                                                                                                                                                                  |

|                                                                         |        |                                                        | Multiple PHY devices can drive DDP at uniquely assigned tributary column positions. This parity signal is intended to detect accidental PHY source clashes in the column assignment.                                                                                                                                                                                   |

|                                                                         |        |                                                        | DDP is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                           |

ISSUE 5

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPL      | Input | AD1        | The SBI DROP bus payload signal (DPL) indicates valid data within the SBI TDM bus structure. This signal is asserted during all octets making up a tributary. This signal may be asserted during the V3 or H3 octet within a tributary to accommodate negative timing adjustments between the tributary rate and the fixed TDM bus structure. This signal may be deasserted during the octet following the V3 or H3 octet within a tributary to accommodate positive timing adjustments between the tributary rate and the fixed TDM-BUS structure. |

|          |       |            | Multiple PHY devices can drive DPL at uniquely assigned tributary column positions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |       |            | DPL is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DV5      | Input | AE4        | The SBI DROP bus payload indicator signal (DV5) locates the position of the floating payloads for each tributary within the SBI TDM bus structure. Timing differences between the port timing and the TDM bus timing are indicated by adjustments of this payload indicator relative to the fixed TDM bus structure.                                                                                                                                                                                                                                |

|          |       |            | Multiple PHY devices can drive DV5 at uniquely assigned tributary column positions. All movements indicated by this signal must be accompanied by appropriate adjustments in the DPL signal.                                                                                                                                                                                                                                                                                                                                                        |

|          |       |            | DV5 is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

ISSUE 5

| Pin Name                                                                                     | Туре                   | Pin<br>No.                                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------|------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADATA[0]<br>ADATA[1]<br>ADATA[2]<br>ADATA[3]<br>ADATA[4]<br>ADATA[5]<br>ADATA[6]<br>ADATA[7] | Tristat<br>e<br>Output | AF5<br>AD7<br>AE7<br>AF7<br>AD9<br>AF8<br>AD10<br>AC11 | The SBI ADD bus data signals (ADATA[7:0]) contain the time division multiplexed transmit data from the up to 84 independently timed links. Data from each link is transported as a tributary within the SBI TDM bus structure. Multiple link layer devices can drive the SBI ADD bus at uniquely assigned tributary column positions. ADATA[7:0] are tristated when the FREEDM-84P672 is not outputting data on a particular tributary column. |

|                                                                                              |                        |                                                        | ADATA[7:0] are updated on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                           |

| ADP                                                                                          | Tristat<br>e<br>Output | AD5                                                    | The SBI ADD bus parity signal (ADP) carries the even or odd parity for the ADD bus signals. The parity calculation encompasses the ADATA[7:0], APL and AV5 signals.                                                                                                                                                                                                                                                                            |

|                                                                                              |                        |                                                        | Multiple link layer devices can drive this signal at uniquely assigned tributary column positions. ADP is tristated when the FREEDM-84P672 is not outputting data on a particular tributary column. This parity signal is intended to detect accidental link layer source clashes in the column assignment.                                                                                                                                    |

|                                                                                              |                        |                                                        | ADP is updated on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                   |

ISSUE 5

| Pin Name | Туре                   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APL      | Tristat<br>e<br>Output | AC2        | The SBI ADD bus payload signal (APL) indicates valid data within the SBI TDM bus structure. This signal is asserted during all octets making up a tributary. This signal may be asserted during the V3 or H3 octet within a tributary to accommodate negative timing adjustments between the tributary rate and the fixed TDM bus structure. This signal may be deasserted during the octet following the V3 or H3 octet within a tributary to accommodate positive timing adjustments between the tributary rate and the fixed TDM-BUS structure. |

|          |                        |            | Multiple link layer devices can drive this signal at uniquely assigned tributary column positions. APL is tristated when the FREEDM-84P672 is not outputting data on a particular tributary column.                                                                                                                                                                                                                                                                                                                                                |

|          |                        |            | APL is updated on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AV5      | Tristat<br>e<br>output | AB4        | The SBI ADD bus payload indicator signal (AV5) locates the position of the floating payloads for each tributary within the SBI TDM bus structure. Timing differences between the port timing and the TDM bus timing are indicated by adjustments of this payload indicator relative to the fixed TDM bus structure.                                                                                                                                                                                                                                |

|          |                        |            | Multiple link layer devices can drive this signal at uniquely assigned tributary column positions. APL is tristated when the FREEDM-84P672 is not outputting data on a particular tributary column. All movements indicated by this signal are accompanied by appropriate adjustments in the APL signal.                                                                                                                                                                                                                                           |

|          |                        |            | AV5 is updated on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

ISSUE 5

| Pin Name  | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                              |

|-----------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AJUST_REQ | Input  | AC12       | The SBI ADD bus justification request signal (AJUST_REQ) is used to speed up or slow down the output data rate of the FREEDM-84P672.                                                                                                                                                                                                  |

|           |        |            | Negative timing adjustments are requested by asserting AJUST_REQ during the V3 or H3 octet, depending on the tributary type. In response to this the FREEDM-84P672 will send an extra byte in the V3 or H3 octet of the next frame along with a valid APL indicating a negative justification.                                        |

|           |        |            | Positive timing adjustments are requested by asserting AJUST_REQ during the octet following the V3 or H3 octet, depending on the tributary type. FREEDM-84P672 will respond to this by not sending an octet during the octet following the V3 or H3 octet of the next frame and deasserting APL to indicate a positive justification. |

|           |        |            | AJUST_REQ is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                    |

| AACTIVE   | Output | AF4        | The SBI ADD bus active indicator signal (AACTIVE) is asserted whenever FREEDM-84P672 is driving the SBI ADD bus signals, ADATA[7:0], ADP, APL and AV5.                                                                                                                                                                                |

|           |        |            | All other Link Layer devices driving the SBI ADD bus should listen to this signal (to detect multiple sources accidentaly driving the bus) and should cease driving the bus whenever a conflict is detected.                                                                                                                          |

|           |        |            | AACTIVE is updated on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                      |

ISSUE 5

FRAME ENGINE AND DATA LINK MANAGER 84P672

| Pin Name                 | Туре  | Pin<br>No.   | Function                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADETECT[0]<br>ADETECT[1] | Input | AD12<br>AF12 | The SBI ADD bus conflict detection signals (ADETECT[1:0]) may be connected to the AACTIVE outputs of other link layer devices sharing the SBI ADD bus. FREEDM-84P672 will immediately tristate the SBI ADD bus signals ADATA[7:0], ADP, APL and AV5 if either of ADETECT[1] and ADETECT[0] is asserted.  ADETECT[1:0] are asynchronous inputs. |

## Table 2 - Clock/Data Interface Signals (15)

| Pin Name                      | Туре  | Pin<br>No.     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------|-------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK[0]<br>RCLK[1]<br>RCLK[2] | Input | T1<br>R2<br>P3 | The receive line clock signals (RCLK[2:0]) contain the recovered line clock for the 3 independently timed links. RCLK[n] must be externally gapped during the bits or time-slots that are not part of the transmission format payload (i.e. not part of the HDLC packet). RCLK[2:0] is nominally a 50% duty cycle clock between 0 and 51.84 MHz.                                                                                                                             |

|                               |       |                | The RCLK[n] inputs are invalid and should be tied low when their associated link is not configured for operation (i.e. SPEn_EN input is high).                                                                                                                                                                                                                                                                                                                               |

| RD[0]<br>RD[1]<br>RD[2]       | Input | R4<br>R3<br>R1 | The receive data signals (RD[2:0]) contain the recovered line data for the 3 independently timed links. RD[2:0] contain HDLC packet data. For certain transmission formats, RD[2:0] may contain place holder bits or timeslots. RCLK[n] must be externally gapped during the place holder positions in the RD[n] stream. The FREEDM-84P672 supports a maximum data rate of 51.84 Mbit/s on each link. RD[2:0] are sampled on the rising edge of the corresponding RCLK[2:0]. |

ISSUE 5

| TCLK[0]                       | Input  |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCLK[1]<br>TCLK[2]            | pat    | AB1<br>AA3<br>AC1 | The transmit line clock signals (TCLK[2:0]) contain the transmit clocks for the 3 independently timed links. TCLK[n] must be externally gapped during the bits or time-slots that are not part of the transmission format payload (i.e. not part of the HDLC packet). TCLK[2:0] is nominally a 50% duty cycle clock between 0 and 51.84 MHz.                                                                                                                                                                                                                             |

|                               |        |                   | The TCLK[n] inputs are invalid and should be tied low when their associated link is not configured for operation (i.e. SPEn_EN input is high).                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TD[0]<br>TD[1]<br>TD[2]       | Output | AA2<br>Y4<br>AB2  | The transmit data signals (TD[2:0]) contain the transmit data for the 3 independently timed links. TD[2:0] contain HDLC packet data. For certain transmission formats, TD[2:0] may contain place holder bits or timeslots. TCLK[n] must be externally gapped during the place holder positions in the TD[n] stream. The FREEDM-84P672 supports a maximum data rate of 51.84 Mbit/s on each link.                                                                                                                                                                         |

|                               |        |                   | TD[2:0] are updated on the falling edge of the corresponding TCLK[2:0] clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SPE1_EN<br>SPE2_EN<br>SPE3_EN | Input  | Y2<br>AA1<br>W4   | The Synchronous Payload Envelope Enable signals (SPEn_EN) configure the operation of the clock/data inputs and the SBI Interface. When SPEn_EN is low, the corresponding Synchronous Payload Envelope conveyed on the SBI interface is unused and the corresponding independently timed link (signals RCLK[n-1], RD[n-1], TCLK[n-1] and TD[n-1]) is enabled. When SPEn_EN is high, the corresponding Synchronous Payload Envelope conveyed on the SBI interface is enabled and the corresponding independently timed link is disabled.  SPEn EN are asynchronous inputs. |

ISSUE 5

Table 3 - PCI Host Interface Signals (52)

| Pin Name                                     | Туре   | Pin<br>No.                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------|--------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICLK                                       | Input  | J24                       | The PCI clock signal (PCICLK) provides timing for PCI bus accesses. PCICLK is a nominally 50% duty cycle, 25 to 66 MHz clock.                                                                                                                                                                                                                                                                                                                                                                                                    |

| PCICLKO                                      | Output | G26                       | The PCI clock output signal (PCICLKO) is a buffered version of the PCICLK. PCICLKO may be used to derive the SYSCLK input.                                                                                                                                                                                                                                                                                                                                                                                                       |

| C/BEB[0]<br>C/BEB[1]<br>C/BEB[2]<br>C/BEB[3] | I/O    | AA25<br>W26<br>T26<br>M23 | The PCI bus command and byte enable bus (C/BEB[3:0]) contains the bus command or the byte valid indications. During the first clock cycle of a transaction, C/BEB[3:0] contains the bus command code. For subsequent clock cycles, C/BEB[3:0] identifies which bytes on the AD[31:0] bus carry valid data. C/BEB[3] is associated with byte 3 (AD[31:24]) while C/BEB[0] is associated with byte 0 (AD[7:0]). When C/BEB[n] is set high, the associated byte is invalid. When C/BEB[n] is set low, the associated byte is valid. |

|                                              |        |                           | When the FREEDM-84P672 is the initiator, C/BEB[3:0] is an output bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                              |        |                           | When the FREEDM-84P672 is the target, C/BEB[3:0] is an input bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              |        |                           | When the FREEDM-84P672 is not involved in the current transaction, C/BEB[3:0] is tristated.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                              |        |                           | As an output bus, C/BEB[3:0] is updated on the rising edge of PCICLK. As an input bus, C/BEB[3:0] is sampled on the rising edge of PCICLK.                                                                                                                                                                                                                                                                                                                                                                                       |

ISSUE 5

| Pin Name                                                                                              | Туре | Pin<br>No.                                                                                                                                                                                                                          | Function                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           |

|-------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| AD[0]<br>AD[1]<br>AD[2]<br>AD[3]<br>AD[4]<br>AD[5]<br>AD[6]                                           | I/O  | AC25<br>AB24<br>AA23<br>AC26<br>AB25<br>AA24<br>Y23<br>AB26<br>Y24<br>W23<br>Y25<br>W24<br>Y26<br>W25<br>V24<br>U23<br>R24<br>R25<br>R26<br>P24<br>P25<br>N24<br>N23<br>M26<br>L25<br>K26<br>L24<br>K25<br>L23<br>J26<br>K24<br>J25 | The PCI address and data bus (AD[31:0]) carries the PCI bus multiplexed address and data. During the first clock cycle of a transaction, AD[31:0] contains a physical byte address. During subsequent clock cycles of a transaction, AD[31:0] contains data.                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           |