# MC68LC302

# Low Power Integrated Multiprotocol Processor Reference Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and eregistered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

### **Literature Distribution Centers:**

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912, Arizona 85036.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan.

ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate,

# **PREFACE**

The complete documentation package for the MC68LC302 consists of the MC68LC302RM/AD, MC68LC302 Low Power Integrated Multiprotocol Processor Reference Manual, M68000PM/AD, MC68000 Family Programmer's Reference Manual, MC68302UM/AD, MC68302 Integrated Multiprotocol Processor User's Manual, and the MC68LC302/D, MC68LC302 Low Power Integrated Multiprotocol Processor Product Brief.

The MC68LC302 Low Power Integrated Multiprotocol Processor Reference Manual describes the programming, capabilities, registers, and operation of the MC68LC302 that differ from the original MC68302; the MC68000 Family Programmer's Reference Manual provides instruction details for the MC68LC302; and the MC68LC302 Low Power Integrated Multiprotocol Processor Product Brief provides a brief description of the MC68LC302 capabilities.

The MC68302 Integrated Multiprotocol Processor User's Manual is required, since the MC68LC302 Low Power Integrated Multiprotocol Processor Reference Manual only describes the new features of the MC68LC302.

This user's manual is organized as follows:

| Section 1 | Introduction                                                      |

|-----------|-------------------------------------------------------------------|

| Section 2 | Configuration, Clocking, Low Power Modes, and Internal Memory Map |

| Section 3 | System Integration Block (SIB)                                    |

| Section 4 | Communications Processor (CP)                                     |

| Section 5 | Signal Description                                                |

| Section 6 | Electrical Characteristics                                        |

| Section 7 | Mechanical Data And Ordering Information                          |

# **ELECTRONIC SUPPORT:**

The Technical Support BBS, known as AESOP (Application Engineering Support Through On-Line Productivity), can be reach by modem or the internet. AESOP provides commonly asked application questons, latest device errata, device specs, software code, and many other useful support functions.

Modem: Call 1-800-843-3451 (outside US or Canada 512-891-3650) on a modem that runs at 14,400 bps or slower. Set your software to N/8/1/F emulating a vt100.

Internet: This access is provided by telneting to pirs.aus.sps.mot.com [129.38.233.1] or through the World Wide Web at http://pirs.aus.sps.mot.com.

# — Sales Offices —

For questions or comments pertaining to technical information, questions, and applications, please contact one of the following sales offices nearest you.

# **UNITED STATES**

| ALABAMA, Huntsville ARIZONA, Tempe CALIFORNIA, Agoura Hills CALIFORNIA, Los Angeles CALIFORNIA, Irvine CALIFORNIA, RosevIlle CALIFORNIA, Sunnyvale COLORADO, Colorado Springs COLORADO, Denver CONNECTICUT, Wallingford FLORIDA, Maitland FLORIDA, Pompano Beach/ Fort Lauderdal FLORIDA, Clearwater GEORGIA, Atlanta IDAHO, Boise ILLINOIS, Chicago/Hoffman Estates INDIANA, Fort Wayne INDIANA, Indianapolis INDIANA, Kokomo IOWA, Cedar Rapids KANSAS, Kansas City/Mission MARYLAND, Columbia | (205) 464-6800<br>(602) 897-5056<br>(818) 706-1929<br>(310) 417-8848<br>(714) 753-7360<br>(916) 922-7152<br>(619) 541-2163<br>(408) 749-0510<br>(719) 599-7497<br>(303) 337-3434<br>(203) 949-4100<br>(407) 628-2636<br>(305) 486-9776<br>(813) 538-7750<br>(404) 729-7100<br>(208) 323-9413<br>(708) 490-9500<br>(219) 436-5818<br>(317) 571-0400<br>(317) 457-6634<br>(319) 373-1328<br>(913) 451-8555<br>(410) 381-1570 | MASSACHUSETTS, Marborough MASSACHUSETTS, Woburn MICHIGAN, Detroit MINNESOTA, Minnetonka MISSOURI, St. Louis NEW JERSEY, Fairfield NEW YORK, Fairport NEW YORK, Hauppauge NEW YORK, Poughkeepsie/Fishkill NORTH CAROLINA, Raleigh OHIO, Cleveland OHIO, Columbus Worthington OHIO, Dayton OKLAHOMA, Tulsa OREGON, Portland PENNSYLVANIA, Colmar Philadelphia/Horsham TENNESSEE, Knoxville TEXAS, Austin TEXAS, Houston TEXAS, Houston TEXAS, Plano VIRGINIA, Richmond WASHINGTON, Bellevue Seattle Access WISCONSIN, Milwaukee/Brookfield | (508) 481-8100<br>(617) 932-9700<br>(313) 347-6800<br>(612) 932-1500<br>(314) 275-7380<br>(201) 808-2400<br>(716) 425-4000<br>(516) 361-7000<br>(914) 473-8102<br>(919) 870-4355<br>(216) 349-3100<br>(614) 431-8492<br>(513) 495-6800<br>(800) 544-9496<br>(503) 641-3681<br>(215) 997-1020<br>(215) 957-4100<br>(615) 690-5593<br>(512) 873-2000<br>(800) 343-2692<br>(214) 516-5100<br>(804) 285-2100<br>(206) 454-4160<br>(206) 622-9960<br>(414) 792-0122 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CANADA BRITISH COLUMBIA, Vancouver ONTARIO, Toronto ONTARIO, Ottawa QUEBEC, Montreal                                                                                                                                                                                                                                                                                                                                                                                                             | (604) 293-7605<br>(416) 497-8181<br>(613) 226-3491<br>(514) 731-6881                                                                                                                                                                                                                                                                                                                                                       | MALAYSIA, Penang MEXICO, Mexico City MEXICO, Guadalajara Marketing Customer Service NETHERLANDS, Best PUERTO RICO, San Juan SINGAPORE SPAIN, Madrid                                                                                                                                                                                                                                                                                                                                                                                      | 60(4)374514<br>52(5)282-2864<br>52(36)21-8977<br>52(36)21-9023<br>52(36)669-9160<br>(31)49988 612 11                                                                                                                                                                                                                                                                                                                                                           |

| INTERNATIONAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                            | PUERTO RICO, San Juan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (809)793-2170                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AUSTRALIA, Melbourne<br>AUSTRALIA, Sydney                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (61-3)887-0711<br>(61(2)906-3855                                                                                                                                                                                                                                                                                                                                                                                           | SINGAPORE<br>SPAIN, Madrid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (65)2945438<br>34(1)457-8204                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BRAZIL, Sao Paulo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55(11)815-4200                                                                                                                                                                                                                                                                                                                                                                                                             | or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34(1)457-8254                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CHINA, Beijing<br>FINLAND, Helsinki                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86 505-2180<br>358-0-35161191                                                                                                                                                                                                                                                                                                                                                                                              | SWEDEN, Solna<br>SWITZERLAND, Geneva<br>SWITZERLAND, Zurich<br>TAIWAN, Taipei                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46(8)734-8800<br>41(22)7991111                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Car Phone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 358(49)211501                                                                                                                                                                                                                                                                                                                                                                                                              | SWITZERLAND, Zurich                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41(1)730 4074                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FRANCE, Paris/Vanves GERMANY, Langenhagen/ Hanover                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33(1)40 955 900<br>49(511)789911                                                                                                                                                                                                                                                                                                                                                                                           | TAIWAN, Taipei<br>THAILAND Bangkok                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 886(2)717-7089<br>(66-2)254-4910                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CEDMANIX Munich                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40 00 00400 0                                                                                                                                                                                                                                                                                                                                                                                                              | THAILAND, Bangkok UNITED KINGDOM, Aylesbury                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44(296)395-252                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GERMANY, Munich GERMANY, Nurnemberg GERMANY, Sindelfingen GERMANY, Wiesbaden HONG KONG, Kwai Fong Tai Po                                                                                                                                                                                                                                                                                                                                                                                         | 49 911 64-3044<br>49 7031 69 910                                                                                                                                                                                                                                                                                                                                                                                           | FULL LINE REPRESENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GERMANY, Wiesbaden                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49 611 761921                                                                                                                                                                                                                                                                                                                                                                                                              | COLORADO, Grand Junction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>HONG KONG</b> , Kwai Fong<br>Tai Po                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 852-4808333<br>852-6668333                                                                                                                                                                                                                                                                                                                                                                                                 | Cheryl Lee Whltely<br>KANSAS, Wichita                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (303) 243-9658                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INDIA, Bangalore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (91-812)627094                                                                                                                                                                                                                                                                                                                                                                                                             | Melinda Shores/Kelly Greiving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (316) 838 0190                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ISRAEL, Tel Aviv<br>ITALY, Milan                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 972(3)753-8222<br>39(2)82201                                                                                                                                                                                                                                                                                                                                                                                               | NEVADA, Reno<br>Galena Technology Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (702) 746 0642                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>JAPAN</b> , Aizu                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 81(241)272231                                                                                                                                                                                                                                                                                                                                                                                                              | NEW MEXICO, Albuquerque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| JAPAN, Atsugi<br>JAPAN, Kumagaya                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81(0462)23-0761<br>81(0485)26-2600                                                                                                                                                                                                                                                                                                                                                                                         | S&S Technologies, Inc. UTAH, Salt Lake City                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (505) 298-7177                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| JAPAN, Kyushu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81(092)771-4212                                                                                                                                                                                                                                                                                                                                                                                                            | Utah Component Sales, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (801) 561-5099                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| JAPAN, Mito<br>JAPAN, Nagoya                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81(0292)26-2340<br>81(052)232-1621                                                                                                                                                                                                                                                                                                                                                                                         | WASHINGTON, Spokane<br>Doug Kenley                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (509) 924-2322                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| JAPAN, Osaka                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81(06)305-1801                                                                                                                                                                                                                                                                                                                                                                                                             | ARGENTINA, Buenos Aires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| JAPAN, Sendai<br>JAPAN, Tachikawa                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81(22)268-4333<br>81(0425)23-6700                                                                                                                                                                                                                                                                                                                                                                                          | Argonics, S.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (541) 343-1787                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| JAPAN, Tokyo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81(03)3440-3311                                                                                                                                                                                                                                                                                                                                                                                                            | HYBRID COMPONENTS RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| JAPAN, Yokohama<br>KOREA, Pusan                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 81(045)472-2751<br>82(51)4635-035                                                                                                                                                                                                                                                                                                                                                                                          | Elmo Semiconductor Minco Technology Labs Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (818) 768-7400<br>(512) 834-2022                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0Z(0)  40.55-U.55                                                                                                                                                                                                                                                                                                                                                                                                          | WILLOU LECTION LADS INC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (312) 034-2022                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **TABLE OF CONTENTS**

| Paragraph<br>Number | Title                                                      | Page<br>Numbe    |  |

|---------------------|------------------------------------------------------------|------------------|--|

|                     | Section 1                                                  |                  |  |

|                     | Introduction                                               |                  |  |

| 1.1                 | Block Diagram                                              | 1-1              |  |

| 1.2                 | Features                                                   |                  |  |

| 1.3                 | LC302 Applications                                         |                  |  |

| 1.4                 | LC302 Differences                                          |                  |  |

|                     | Section 2                                                  |                  |  |

| Con                 | figuration, Clocking, Low Power Modes, and Internal Memory | <sup>,</sup> Мар |  |

| 2.1                 | MC68LC302 and MC68302 Signal Differences                   | 2-1              |  |

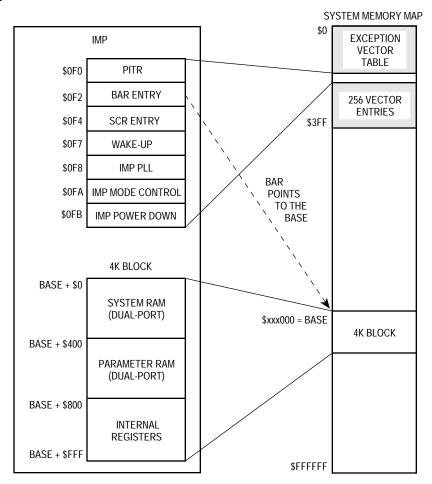

| 2.2                 | IMP Configuration Control                                  | 2-2              |  |

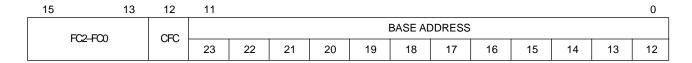

| 2.2.1               | Base Address Register                                      | 2-4              |  |

| 2.3                 | System Configuration Registers                             | 2-5              |  |

| 2.4                 | Clock Generation and Low Power Control                     |                  |  |

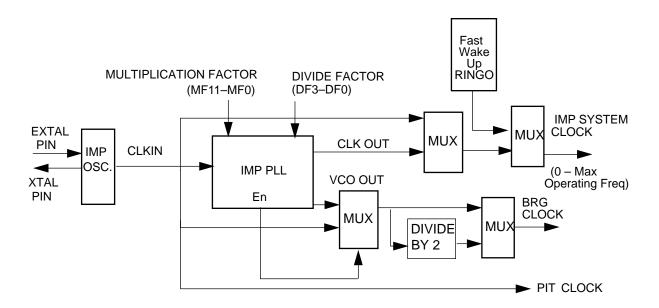

| 2.4.1               | PLL and Oscillator Changes to IMP                          | 2-5              |  |

| 2.4.1.1             | Clock Control Register                                     | 2-6              |  |

| 2.4.2               | MC68LC302 System Clock Generation                          | 2-6              |  |

| 2.4.2.1             | Default System Clock Generation                            |                  |  |

| 2.4.3               | IMP System Clock Generation                                | 2-8              |  |

| 2.4.3.1             | System Clock Configuration                                 |                  |  |

| 2.4.3.2             | On-Chip Oscillator                                         |                  |  |

| 2.4.3.3             | Phase-Locked Loop (PLL)                                    |                  |  |

| 2.4.3.4             | Frequency Multiplication                                   |                  |  |

| 2.4.3.4.1           | Low Power PLL Clock Divider                                |                  |  |

| 2.4.3.4.2           | IMP PLL and Clock Control Register (IPLCR)                 | 2-10             |  |

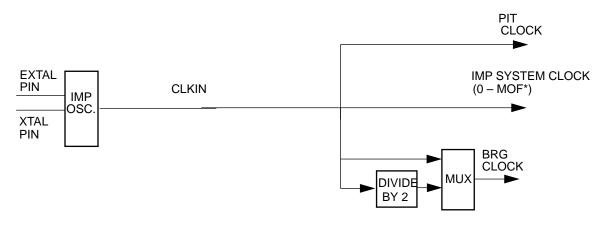

| 2.4.3.5             | IMP Internal Clock Signals                                 |                  |  |

| 2.4.3.5.1           | IMP System Clock                                           | 2-12             |  |

| 2.4.3.5.2           | BRG Ćlock                                                  | 2-12             |  |

| 2.4.3.5.3           | PIT Clock                                                  | 2-12             |  |

| 2.4.3.6             | IMP PLL Pins                                               | 2-12             |  |

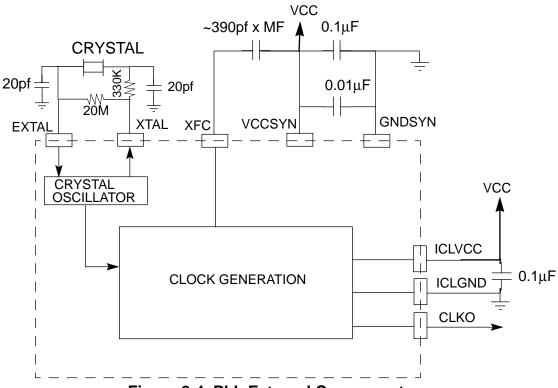

| 2.4.3.6.1           | VCCSYN                                                     | 2-12             |  |

| 2.4.3.6.2           | GNDSYN                                                     | 2-12             |  |

| 2.4.3.6.3           | XFC                                                        | 2-12             |  |

| 2.4.3.6.4           | MODCLK                                                     | 2-12             |  |

| 2.4.4               | IMP Power Management                                       | 2-13             |  |

| 2.4.4.1             | IMP Low Power Modes                                        |                  |  |

| 2.4.4.1.1           | STOP Mode                                                  | 2-13             |  |

| 2.4.4.1.2           | DOZE Mode                                                  | 2-13             |  |

| 2.4.4.1.3           | STAND_BY Mode                                              | 2-13             |  |

| Paragraph<br>Number | Title                                       | Page<br>Numbe |

|---------------------|---------------------------------------------|---------------|

| 2.4.4.1.4           | SLOW_GO Mode                                | 2-14          |

| 2.4.4.1.5           | NORMAL Mode                                 | 2-14          |

| 2.4.4.1.6           | IMP Operation Mode Control Register (IOMCR) | 2-14          |

| 2.4.4.1.7           | Low Power Drive Control Register (LPDCR)    | 2-15          |

| 2.4.4.1.8           | IMP Power Down Register (IPWRD)             | 2-15          |

| 2.4.4.1.9           | Default Operation Modes                     | 2-15          |

| 2.4.4.2             | Low Power Support                           |               |

| 2.4.4.2.1           | Enter the SLOW_GO mode                      |               |

| 2.4.4.2.2           | Entering the STOP/ DOZE/ STAND_BY Mode      |               |

| 2.4.4.2.3           | IMP Wake-Up from Low Power STOP Modes       |               |

| 2.4.4.2.4           | IMP Wake-Up Control Register (IWUCR)        |               |

| 2.4.4.3             | Fast Wake-Up                                |               |

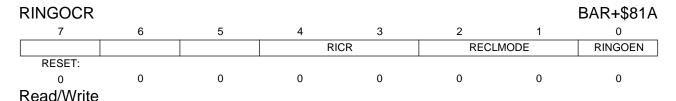

| 2.4.4.3.5           | Ring Oscillator Control Register (RINGOCR)  |               |

| 2.4.4.3.6           | Ring Oscillator Event Register (RINGOEVR)   |               |

| 2.5                 | MC68LC302 Dual Port RAM                     |               |

| 2.6                 | Internal Registers map                      | 2-23          |

|                     | Section 3                                   |               |

| 0.4                 | System Integration Block (SIB)              | 2.4           |

| 3.1                 | System Control                              |               |

| 3.1.1<br>3.1.2      | System Control Register (SCR)               |               |

| 3.1.2               | System Status Bits                          |               |

| 3.1.4               | System Control BitsFreeze Control           |               |

| 3.1.4               | Hardware Watchdog                           |               |

| 3.1.5               | <u> </u>                                    |               |

| 3.2.1               | Programmable Data Bus Size Switch           |               |

| 3.2.1               | Bus Switch Register (BSR)Basic Procedure:   |               |

| 3.3                 | Load Boot Code from An SCC                  |               |

| 3.4                 | DMA Control                                 |               |

| 3.4.1               | MC68LC302 Differences                       |               |

| 3.4.2               | IDMA Registers (Independent DMA Controller) |               |

| 3.4.2.1             | Channel Mode Register (CMR)                 |               |

| 3.4.2.2             | Source Address Pointer Register (SAPR)      | 3-13          |

| 3.4.2.3             | Destination Address Pointer Register (DAPR) |               |

| 3.4.2.4             | Function Code Register (FCR)                |               |

| 3.4.2.5             | Byte Count Register (BCR)                   |               |

| 3.4.2.6             | Channel Status Register (CSR)               |               |

| 3.5                 | Interrupt Controller                        |               |

| 3.5.1               | Interrupt Controller Key Differences        |               |

| 3.5.2               | Interrupt Controller Programming Model      |               |

| 3.5.2.1             | Global Interrupt Mode Register (GIMR)       |               |

| 3.5.2.2             | Interrupt Pending Register (IPR)            |               |

| 3.5.2.3             | Interrupt Mask Register (IMR)               |               |

| 3.5.2.4             | Interrupt In-Service Register (ISR)         | 3-16          |

| Paragraph<br>Number | Title                                             | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

| 3.6                 | Parallel I/O Ports                                | 3-17           |

| 3.6.1               | Parallel I/O Port Differences                     |                |

| 3.6.2               | Port A                                            | _              |

| 3.6.3               | Port B                                            |                |

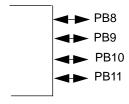

| 3.6.3.1             | PB7–PB3                                           |                |

| 3.6.3.2             | PB11–PB8                                          |                |

| 3.6.4               | Port N                                            |                |

| 3.6.5               | Port Registers                                    |                |

| 3.7                 | Timers                                            |                |

| 3.7.1               | MC68LC302 General Purpose Timer Difference        |                |

| 3.7.2               | General Purpose Timers Programming Mode           |                |

| 3.7.2.1             | Timer Mode Register (TMR1, TMR2)                  |                |

| 3.7.2.2             | Timer Reference Registers (TRR1, TRR2)            |                |

| 3.7.2.3             | Timer Capture Registers (TCR1, TCR2)              |                |

| 3.7.2.4             | Timer Counter (TCN1, TCN2)                        |                |

| 3.7.2.5             | Timer Event Registers (TER1, TER2)                |                |

| 3.7.3               | Timer 3 - Software Watchdog Timer                 |                |

| 3.7.3.1             | Software Watchdog Reference Register (WRR)        |                |

| 3.7.3.2             | Software Watchdog Counter (WCN)                   |                |

| 3.7.4               | Periodic Interrupt Timer (PIT)                    |                |

| 3.7.4.1             | Overview                                          |                |

| 3.7.4.2             | Periodic Timer Period Calculation                 | 3-23           |

| 3.7.4.3             | Using the Periodic Timer As a Real-Time Clock     |                |

| 3.7.4.4             | Periodic Interrupt Timer Register (PITR)          | 3-24           |

| 3.8                 | External Chip-Select Signals and Wait-State Logic |                |

| 3.8.1               | Chip-Select Registers                             |                |

| 3.8.1.1             | Base Register (BR3-BR0)                           | 3-26           |

| 3.8.1.2             | Option Registers (OR3–OR0)                        | 3-26           |

| 3.8.2               | Disable CPU Logic (M68000)                        |                |

| 3.8.3               | Bus Arbitration Logic                             | 3-28           |

| 3.8.3.1             | Internal Bus Arbitration                          | 3-28           |

| 3.8.3.2             | External Bus Arbitration                          |                |

| 3.9                 | Dynamic RAM Refresh Controller                    | 3-29           |

|                     | Section 4                                         |                |

|                     | Communications Processor (CP)                     |                |

| 4.1                 | MC68LC302 Key Differences from the MC68302        |                |

| 4.2                 | Serial Channels Physical Interface                |                |

| 4.2.1               | Serial Interface Registers                        | 4-2            |

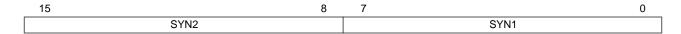

| 4.2.1.1             | Serial Interface Mode Register (SIMODE)           |                |

| 4.2.1.2             | Serial Interface Mask Register (SIMASK)           |                |

| 4.3                 | Serial Communication Controllers (SCCs)           |                |

| 4.3.1               | SCC Configuration Register (SCON)                 |                |

| 4.3.1.1             | Divide by 2 Input Blocks (New Feature)            |                |

| 4.3.2               | Disable SCC1 Serial Clocks Out (DISC)             |                |

| 4.3.2.1             | RCLK1 and TCLK1 Pin Options                       | 4-5            |

| Paragraph | Title                                          | Page   |

|-----------|------------------------------------------------|--------|

| Number    |                                                | Number |

| 4.3.3     | SCC Mode Register (SCM)                        |        |

| 4.3.4     | SCC Data Synchronization Register (DSR)        |        |

| 4.3.5     | Buffer Descriptors Table                       |        |

| 4.3.6     | SCC Parameter RAM Memory Map                   |        |

| 4.3.7     | Interrupt Mechanism                            |        |

| 4.3.8     | UART Controller                                |        |

| 4.3.8.1   | UART Memory Map                                |        |

| 4.3.8.2   | UART Mode Register                             |        |

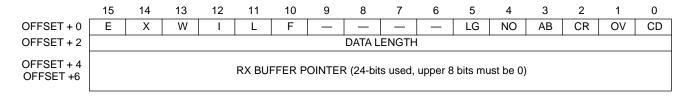

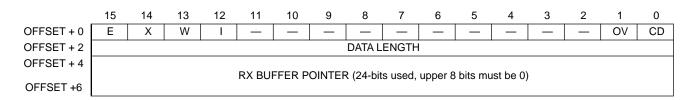

| 4.3.8.3   | UART Receive Buffer Descriptor (Rx BD)         |        |

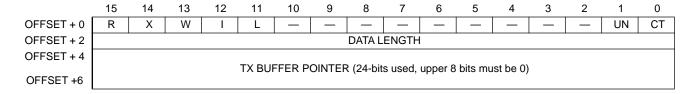

| 4.3.8.4   | UART Transmit Buffer Descriptor (Tx BD)        |        |

| 4.3.8.5   | UART Event Register                            |        |

| 4.3.8.6   | UART MASK Register                             |        |

| 4.3.9     | Autobaud Controller (New)                      |        |

| 4.3.9.1   | Autobaud Channel Reception Process             |        |

| 4.3.9.2   | Autobaud Channel Transmit Process              |        |

| 4.3.9.3   | Autobaud Parameter RAM                         |        |

| 4.3.9.4   | Autobaud Programming Model                     | 4-13   |

| 4.3.9.4.1 | Preparing for the Autobaud Process             | 4-13   |

| 4.3.9.4.2 | Enter_Baud_Hunt Command                        | 4-14   |

| 4.3.9.4.3 | Autobaud Command Descriptor                    | 4-14   |

| 4.3.9.4.4 | Autobaud Lookup Table                          | 4-15   |

| 4.3.9.5   | Lookup Table Example                           | 4-17   |

| 4.3.9.6   | Determining Character Length and Parity        | 4-17   |

| 4.3.9.7   | Autobaud Reception Error Handling Procedure    | 4-18   |

| 4.3.9.8   | Autobaud Transmission                          | 4-18   |

| 4.3.9.8.1 | Automatic Echo                                 | 4-19   |

| 4.3.9.8.2 | Smart Echo                                     | 4-19   |

| 4.3.9.9   | Reprogramming to UART Mode or Another Protocol | 4-20   |

| 4.3.10    | HDLC Controller                                | 4-20   |

| 4.3.10.1  | HDLC Memory Map                                | 4-20   |

| 4.3.10.2  | HDLC Mode Register                             | 4-20   |

| 4.3.10.3  | HDLC Receive Buffer Descriptor (Rx BD)         | 4-21   |

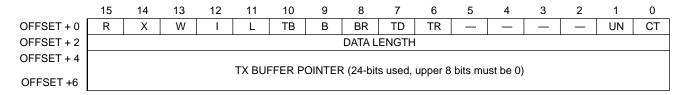

| 4.3.10.4  | HDLC Transmit Buffer Descriptor (Tx BD)        | 4-21   |

| 4.3.10.5  | HDLC Event Register                            |        |

| 4.3.10.6  | HDLC Mask Register                             | 4-21   |

| 4.3.11    | BISYNC Controller                              | 4-22   |

| 4.3.11.1  | BISYNC Memory Map                              | 4-22   |

| 4.3.11.2  | BISYNC Mode Register                           |        |

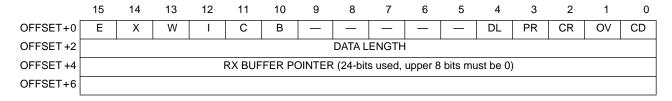

| 4.3.11.3  | BISYNC Receive Buffer Descriptor (Rx BD)       |        |

| 4.3.11.4  | BISYNC Transmit Buffer Descriptor (Tx BD)      |        |

| 4.3.11.5  | BISYNC Event Register                          |        |

| 4.3.11.6  | BISYNC Mask Register                           |        |

| 4.3.12    | Transparent Controller                         |        |

| 4.3.12.1  | Transparent Memory Map                         |        |

| 4.3.12.2  | Transparent Mode Register                      |        |

| Paragraph<br>Number | Title                                                                     | Page<br>Number |

|---------------------|---------------------------------------------------------------------------|----------------|

| 4.3.12.3            | Transparent Receive Buffer Descriptor (RxBD)                              | 4-24           |

| 4.3.12.4            | Transparent Transmit Buffer Descriptor (Tx BD)                            | 4-25           |

| 4.3.12.5            | Transparent Event Register                                                | 4-25           |

| 4.3.12.6            | Transparent Mask Register                                                 | 4-25           |

| 4.4                 | Serial Communication Port (SCP)                                           | 4-25           |

| 4.4.1               | SCP Programming Model                                                     |                |

| 4.4.2               | SCP Transmit/Receive Buffer Descriptor                                    |                |

| 4.5                 | Serial Management Controllers (SMCs)                                      | 4-26           |

| 4.5.1               | SMC Programming Model                                                     |                |

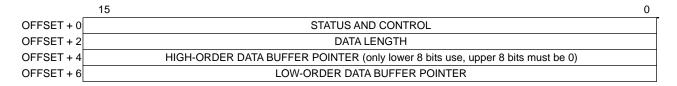

| 4.5.2               | SMC Memory Structure and Buffers Descriptors                              | 4-26           |

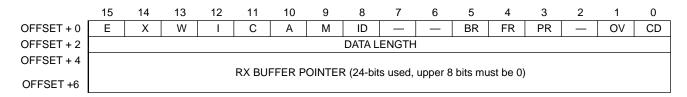

| 4.5.2.1             | SMC1 Receive Buffer Descriptor                                            | 4-26           |

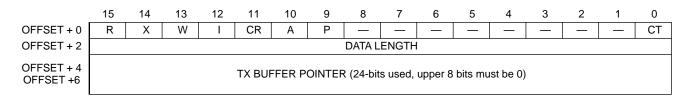

| 4.5.2.2             | SMC1 Transmit Buffer Descriptor                                           |                |

| 4.5.2.3             | SMC2 Receive Buffer Descriptor                                            | 4-27           |

| 4.5.2.4             | SMC2 Transmit Buffer Descriptor                                           | 4-27           |

|                     | Section 5                                                                 |                |

| F 4                 | Signal Description                                                        | F 4            |

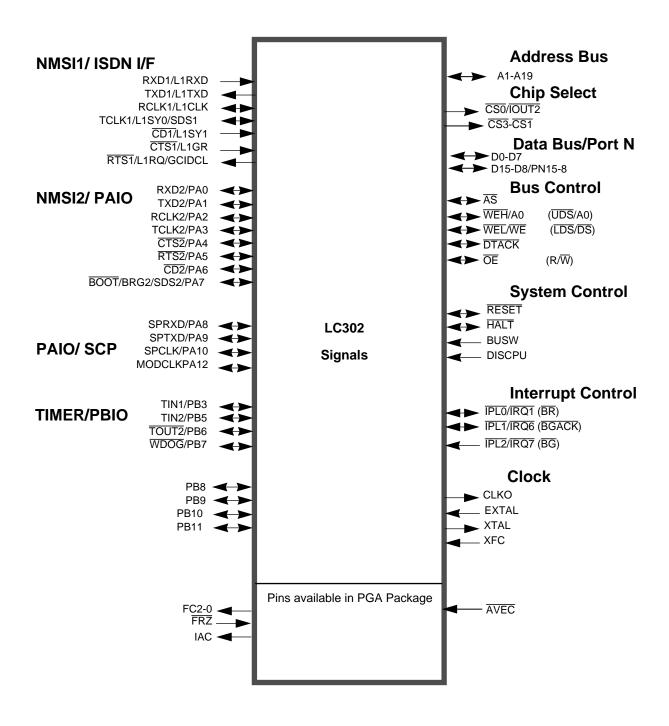

| 5.1                 | Functional Groups                                                         |                |

| 5.2                 | Power Pins                                                                |                |

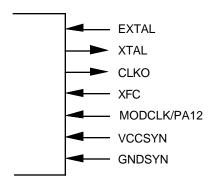

| 5.3                 | Clock Pins                                                                |                |

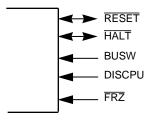

| 5.4                 | System Control Pins                                                       |                |

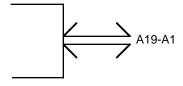

| 5.5                 | Address Bus Pins (A19–A1)                                                 |                |

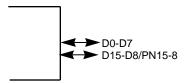

| 5.6                 | Data Bus Pins (D15—D0)                                                    |                |

| 5.7                 | Bus Control Pins                                                          |                |

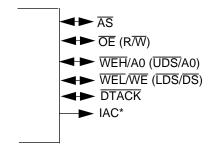

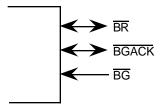

| 5.8                 | Bus Arbitration Pins                                                      |                |

| 5.9<br>5.10         | Interrupt Control Pins                                                    |                |

| 5.10                | MC68LC302 Bus Interface Signal Summary                                    |                |

|                     | Physical Layer Serial Interface Pins                                      |                |

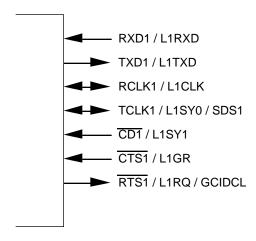

| 5.12                | Typical Serial Interface Pin Configurations  NMSI1 or ISDN Interface Pins |                |

| 5.13                |                                                                           |                |

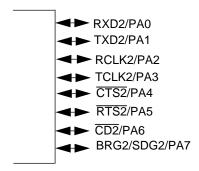

| 5.14<br>5.15        | NMSI2 Port or Port a Pins                                                 |                |

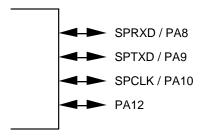

| 5.16                | PAIO / SCP Pins                                                           |                |

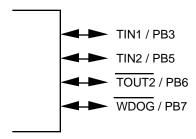

| 5.16                | Timer Pins                                                                |                |

| _                   | Parallel I/O Pins with Interrupt Capability                               |                |

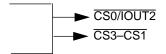

| 5.18                | Chip-Select Pins                                                          |                |

| 5.19                | When to Use Pullup Resistors                                              | 5-21           |

|                     | Section 6 Electrical Characteristics                                      |                |

| 6.1                 | Maximum Ratings                                                           | 6-2            |

| 6.2                 | Thermal Characteristics                                                   |                |

| 6.3                 | Power Considerations                                                      |                |

| 6.4                 | Power Dissipation                                                         |                |

| 6.5                 | DC Electrical Characteristics                                             |                |

| 6.6                 | DC Electrical Characteristics—NMSI1 in IDL Mode                           |                |

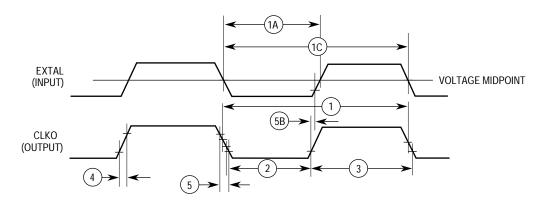

| 6.7                 | AC Electrical Specifications—Clock Timing                                 |                |

|                     |                                                                           |                |

| Paragraph<br>Number | Title                                                             | Page<br>Number |

|---------------------|-------------------------------------------------------------------|----------------|

| 6.7.1               | AC Electrical Characteristics - IMP Phased Lock Loop (PLL)        |                |

|                     | Characteristics                                                   | 6-7            |

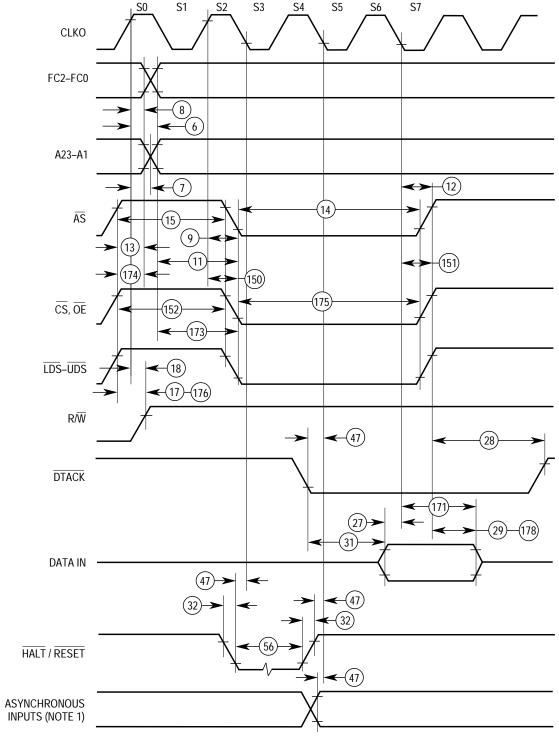

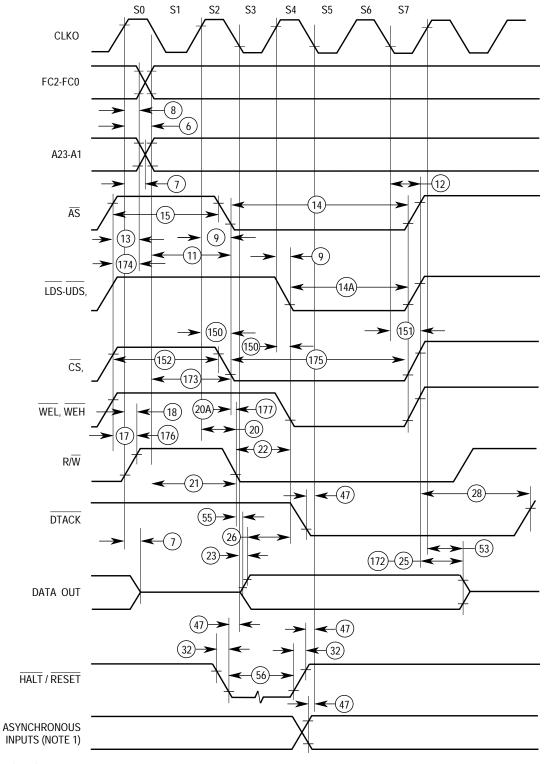

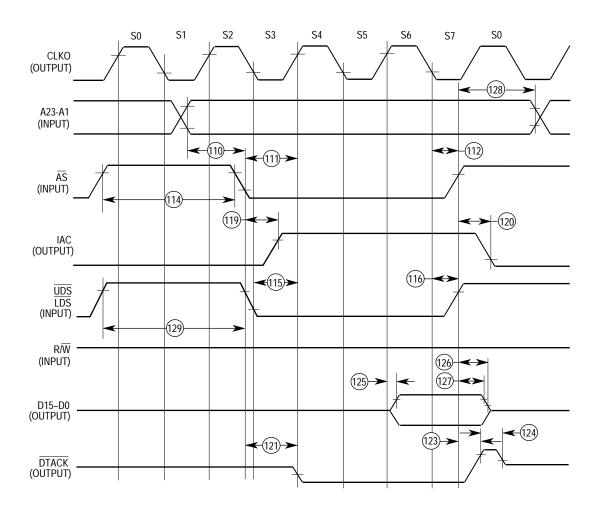

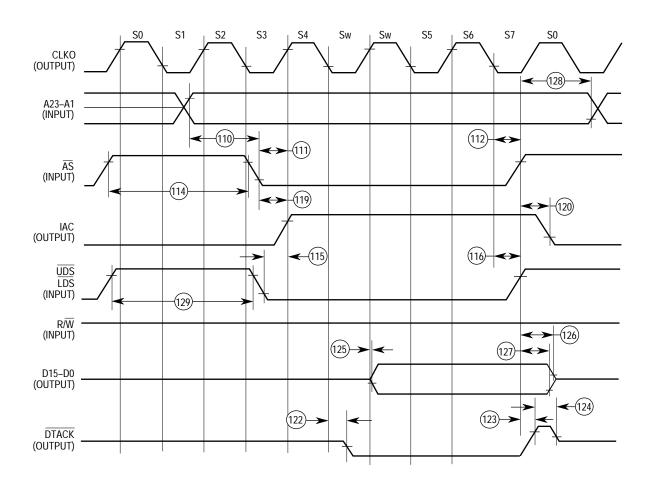

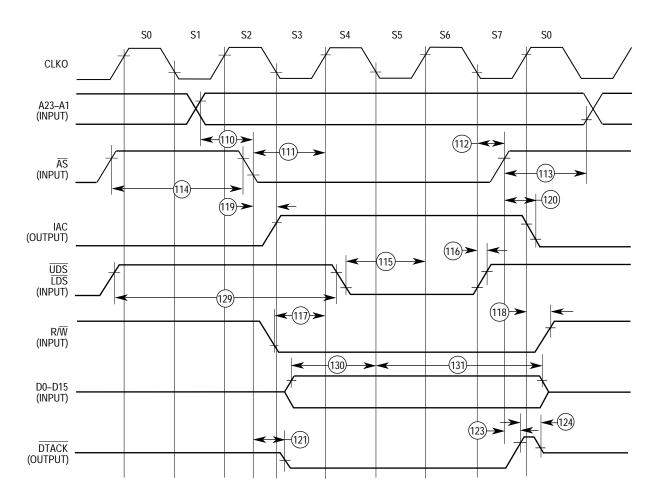

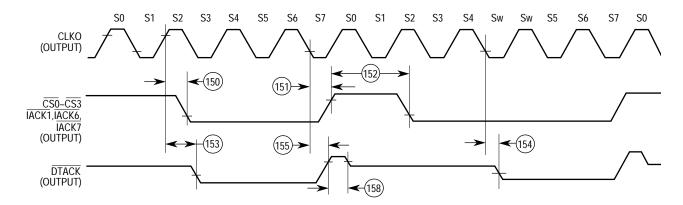

| 6.8                 | AC Electrical Specifications—IMP Bus Master Cycles                | 6-8            |

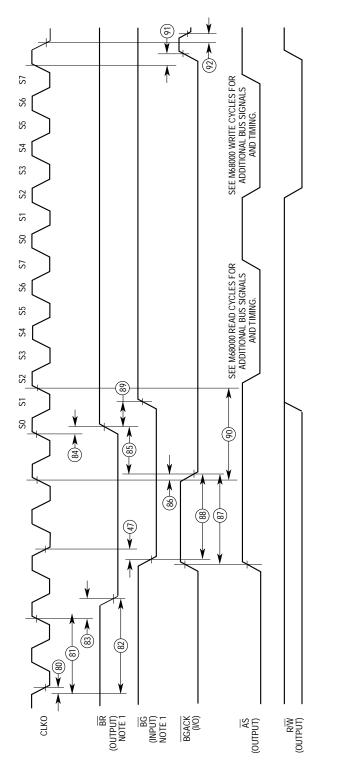

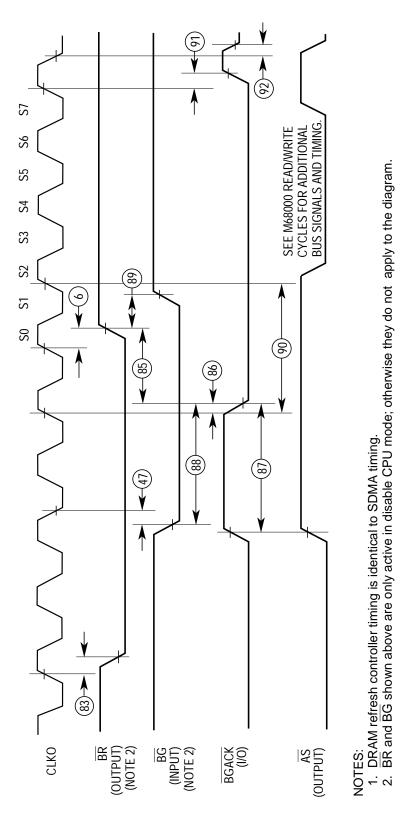

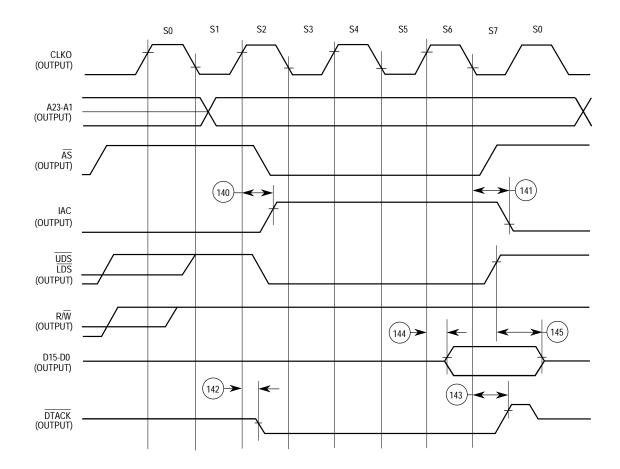

| 6.9                 | AC Electrical Specifications—DMA                                  | 6-13           |

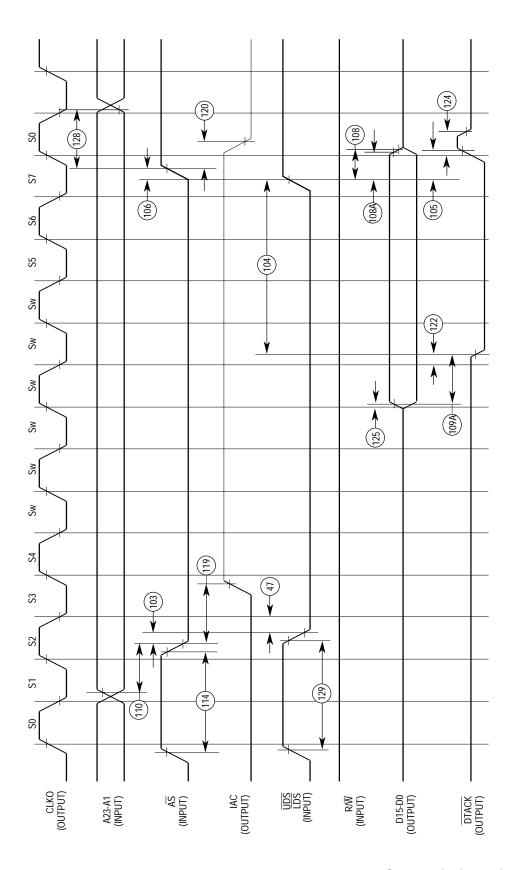

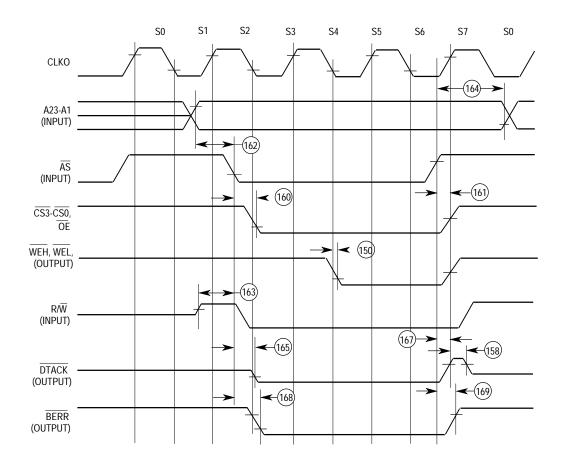

| 6.10                | AC Electrical Specifications—External Master                      |                |

|                     | Internal Asynchronous Read/Write Cycles                           | 6-16           |

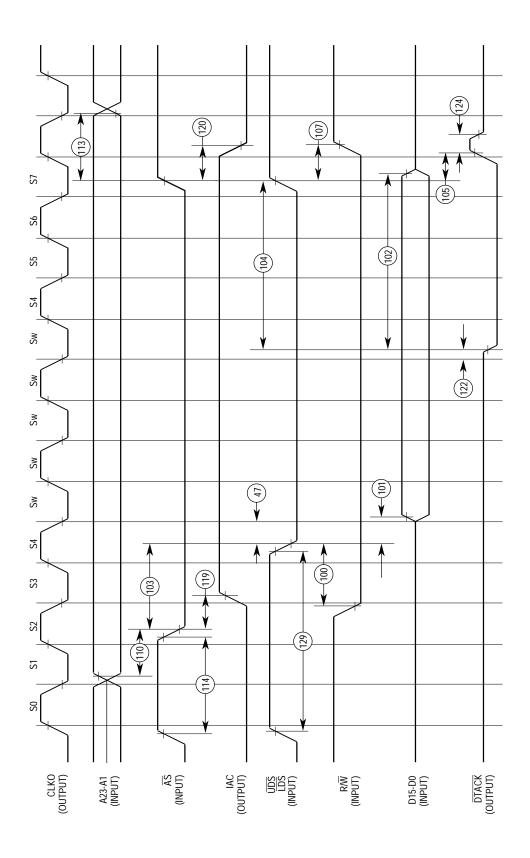

| 6.11                | AC Electrical Specifications—External Master Internal Synchronous | S              |

|                     | Read/Write Cycles                                                 | 6-19           |

| 6.12                | AC Electrical Specifications—Internal Master Internal Read/Write  |                |

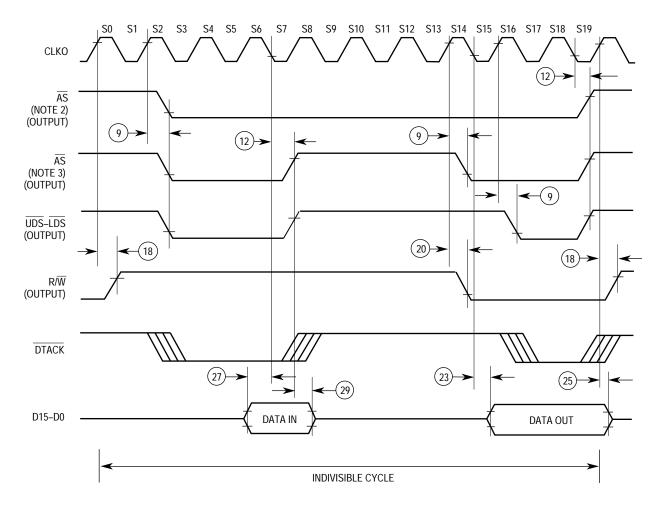

|                     | Cycles                                                            | 6-23           |

| 6.13                | AC Electrical Specifications—Chip-Select Timing Internal Master   | 6-24           |

| 6.14                | AC Electrical Specifications—Chip-Select Timing External Master   |                |

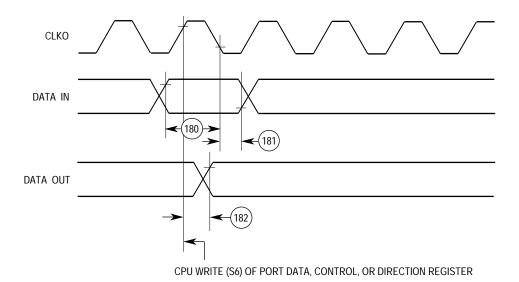

| 6.15                | AC Electrical Specifications—Parallel I/O                         | 6-26           |

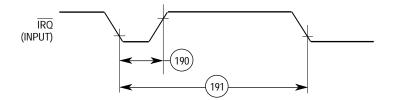

| 6.16                | AC Electrical Specifications—Interrupts                           | 6-26           |

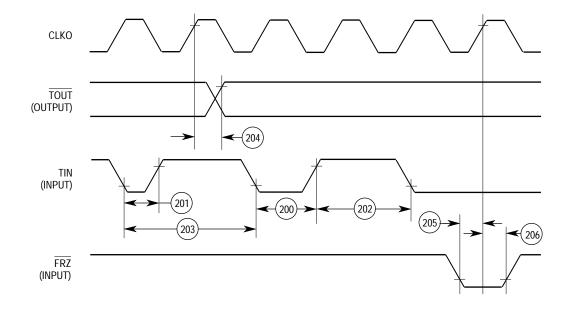

| 6.17                | AC Electrical Specifications—Timers                               |                |

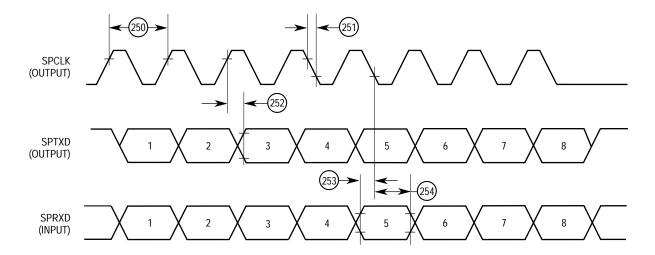

| 6.18                | AC Electrical Specifications—Serial Communications Port           | 6-29           |

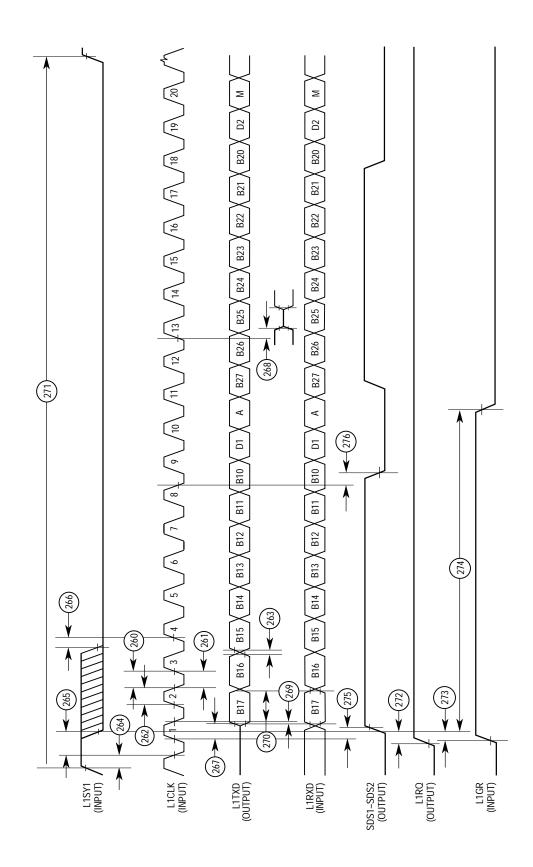

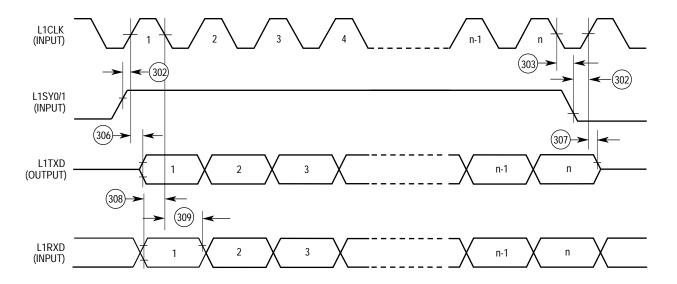

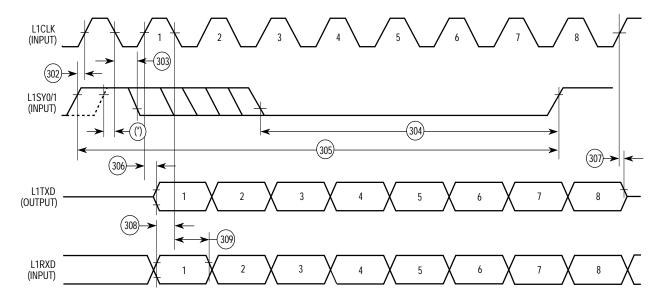

| 6.19                | AC Electrical Specifications—IDL Timing)                          | 6-30           |

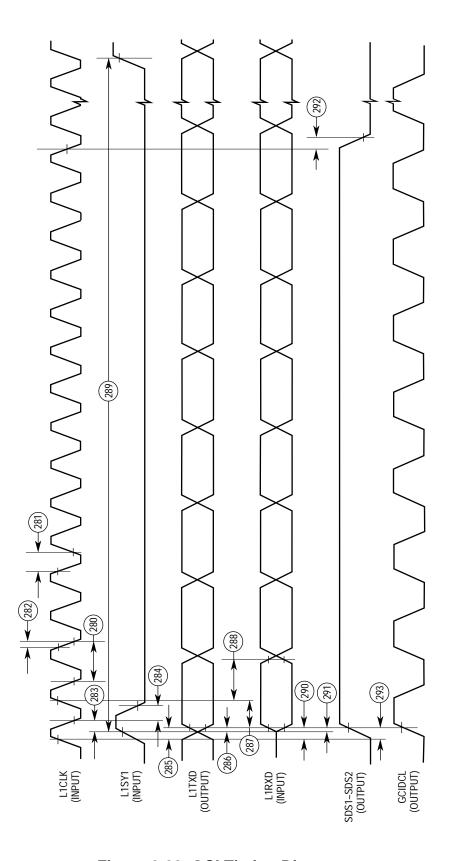

| 6.20                | AC Electrical Specifications—GCI Timing                           |                |

| 6.21                | AC Electrical Specifications—PCM Timing                           |                |

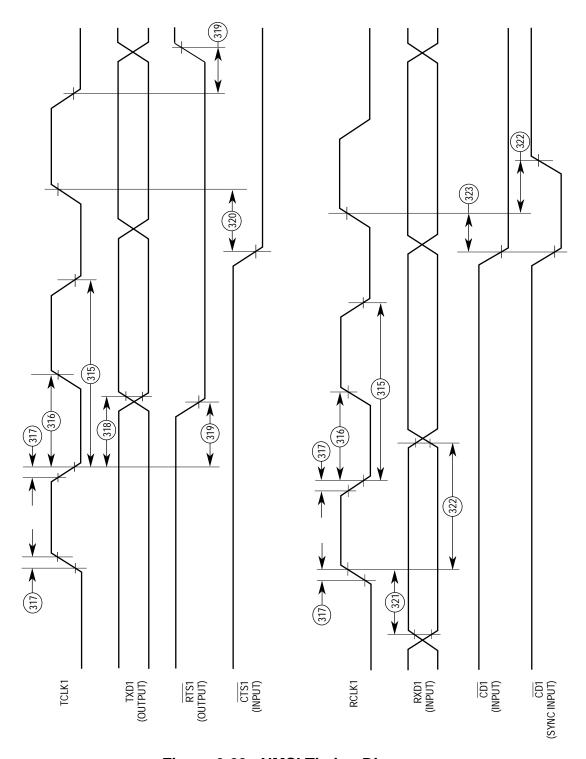

| 6.22                | AC Electrical Specifications—NMSI Timing                          | 6-36           |

|                     | Section 7                                                         |                |

|                     | Mechanical Data and Ordering Information                          |                |

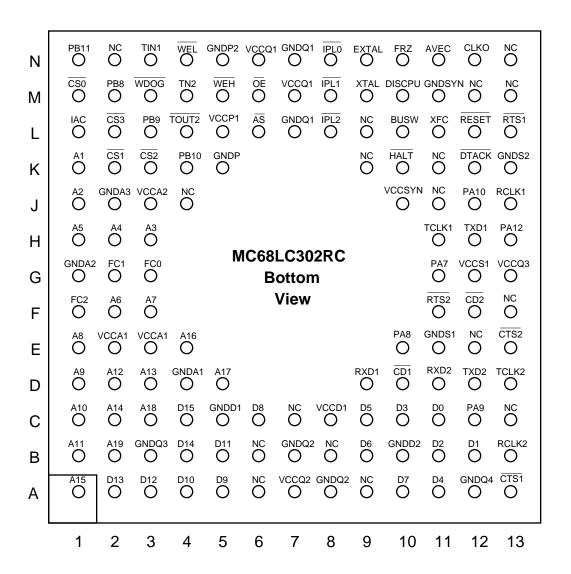

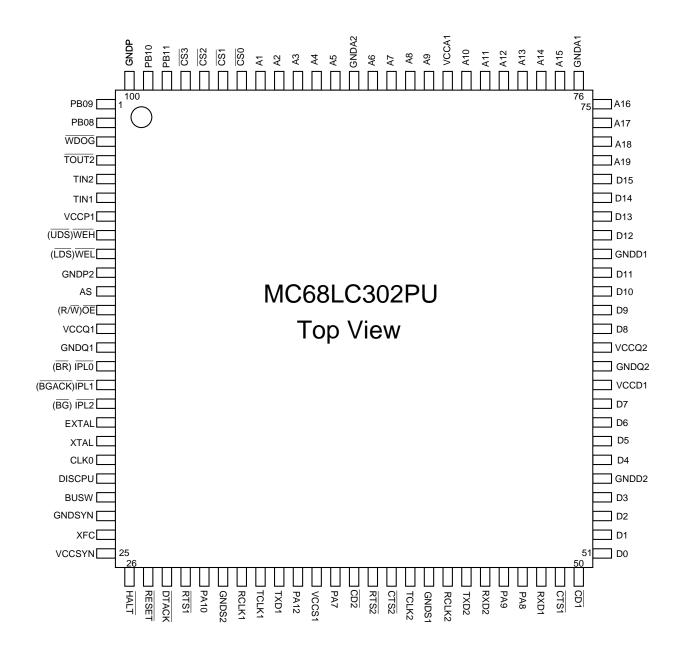

| 7.1                 | Pin Assignments                                                   | 7-1            |

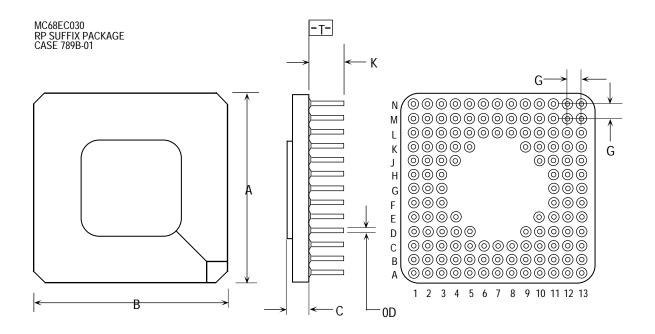

| 7.1.1               | Pin Grid Array (PGA)                                              | 7-1            |

| 7.1.2               | Surface Mount (TQFP)                                              | 7-2            |

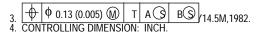

| 7.2                 | Package Dimensions                                                | 7-3            |

| 7.2.1               | Pin Grid Array (PGA)                                              | 7-3            |

| 7.2.2               | Surface Mount (TQFP)                                              | 7-4            |

| 7.3                 | Ordering Information                                              | 7-5            |

# SECTION 1 INTRODUCTION

Motorola has developed a low-cost version of the well-known MC68302 integrated multiprotocol processor (IMP) called the MC68LC302. Simply put, the LC302 is a traditional 68302 minus the third serial communication controller (SCC3) and has a new static 68000 core, a new timer and low power modes. It is packaged in a low profile 100 TQFP that reduces board space from the regular 68302, as well as making it suitable for use in height restricted applications such as PCMCIA.

The document fully describes all the differences between the LC302 and the regular 68302. Any feature not described in this document will operate as described in the *MC68302 User's Manual*. In addition this document contains the full set of electrical descriptions for the LC302, even though most of them are exactly the same as the 68302.

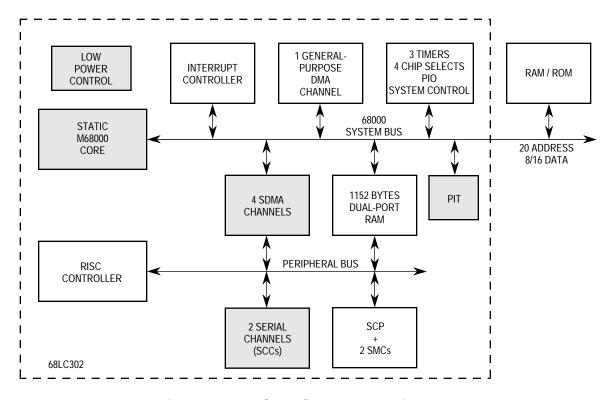

# 1.1 BLOCK DIAGRAM

The block diagram is shown in Figure 1-1.

Figure 1-1. MC68LC302 Block Diagram

# 1.2 FEATURES

The features of the LC302 are as follows. The items in **bold face** type show major differences from the MC68302, although a complete list of differences is given in 1.4 LC302 Differences.

- On-Chip Static 68000 Core Supporting a 16- or 8-Bit M68000 Family-System

- SIB Including:

Independent Direct Memory Access (IDMA) Controller.

Interrupt Controller with Two Modes of Operation

Parallel Input/Output (I/O) Ports, some with Interrupt Capability

# Parallel Input/Output (I/O) Ports on D15-D8 in 8 bit mode

On-Chip 1152-Byte Dual-Port RAM

Three Timers Including a Watchdog Timer

# **New Periodic Interrupt Timer (PIT)**

Four Programmable Chip-Select Lines with Wait-State Generator Logic

Programmable Address Mapping of the Dual-Port RAM and IMP Registers

On-Chip Clock Generator with Output Signal

# On-Chip PLL Allows Operation with 32kHz or 4MHz Crystals

Glueless Interface to EPROM, SRAM, Flash EPROM, and EEPROM

# Allows Boot in 8-bit Mode, and Running Switch to 16-bit Mode

**System Control:**

System Status and Control Logic

Disable CPU Logic (Slave Mode Operation)

Hardware Watchdog

# New Low-Power (Standby) Modes With Wake-up From 2 Pins or PIT

Freeze Control for Debugging (Available Only in the PGA Package)

**DRAM Refresh Controller**

# CP Including:

Main Controller (RISC Processor)

# Two Independent Full-Duplex Serial Communications Controllers (SCCs)

Supporting Various Protocols:

High-Level/Synchronous Data Link Control (HDLC/SDLC)

Universal Asynchronous Receiver Transmitter (UART)

Binary Synchronous Communication (BISYNC)

**Transparent Modes**

**Autobaud Support Instead of DDCMP and V.110**

**Boot from SCC Capability**

# Four Serial DMA Channels for the Two SCCs

Flexible Physical Interface Accessible by SCCs Including:

Motorola Interchip Digital Link (IDL)

General Circuit Interface (GCI, Also Known as IOM<sup>1</sup>-2)

Pulse Code Modulation (PCM) Highway Interface

Nonmultiplexed Serial Interface (NMSI) Implementing Standard

Modem Signals

SCP for Synchronous Communication

Two Serial Management Controllers (SMCs) To Support IDL and GCI Auxiliary Channels

100 Pin Thin Quad Flat Pack (TQFP) Packaging

# 1.3 LC302 APPLICATIONS

The LC302 excels in several applications areas.

First, any application using the 68302, but not needing all three serial channels is a potential candidate for the LC302. Note however, that the LC302 sacrifices most of the provision for external bus mastership, thus the LC302 may not be appropriate where the 68302 is used as part of larger systems.