www.ti.com

bq25010 bq25011 bq25012

SLUS615-DECEMBER 2004

# SINGLE-CHIP CHARGER AND DC/DC CONVERTER IC FOR BLUETOOTH HEADSETS AND OTHER PORTABLE APPLICATIONS (bqHYBRID™)

#### **FEATURES**

- Li-Ion Or Li-Pol Charge Management and Synchronous DC-DC Power Conversion In a Single Chip

- Optimized for Powering Bluetooth Headsets and Accessories

- Charges and Powers the System from Either the AC Adapter or USB with Autonomous Power Source Selection

- Integrated USB Charge Control with Selectable 100 mA and 500 mA Charge Rates

- Integrated Power FET and Current Sensor for Up to 500 mA Charge Applications AND 100 mA 1.8 V DC-DC Controller with Integrated FET

- Reverse Leakage Protection Prevents Battery Drainage

- Automatic Power Save Mode For High Efficiency at Low Current, or Forced PWM for Frequency Sensitive Applications

#### **APPLICATIONS**

- Bluetooth Headsets

- Bluetooth Accessories

- Low-Power Handheld Devices

#### DESCRIPTION

The bqHYBRID™ series are highly integrated charge and power management devices targeted at space-limited bluetooth applications. The bqHYBRID series offer integrated power FET and current sensor for charge control, reverse blocking protection, high accuracy current and voltage regulation, charge status, charge termination, and a highly efficient and low-power dc-dc converter in a small package.

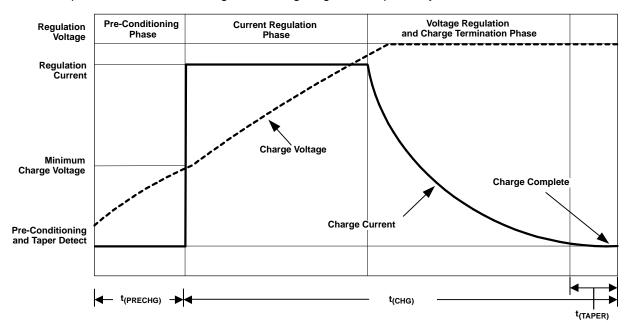

The bqHYBRID charges the battery in three phases: conditioning, constant current and constant voltage. Charge is terminated based on minimum current. An internal charge timer provides a backup safety feature for charge termination. The bqHYBRID automatically re-starts the charge if the battery voltage falls below an internal threshold. The bqHYBRID automatically enters sleep mode when V<sub>CC</sub> supply is removed.

The integrated low-power high-efficiency dc-dc converter is designed to operate directly from a single-cell Li-lon or Li-Pol battery pack. The output voltage is either adjustable from 0.7 V to VBAT (bq25010), fixed at 3.3 V (bq25011), or fixed at 1.8 V (bq25012), and is capable of delivering up to 150-mA of load current. The dc-dc converter operates at a synchronized 1 MHz switching frequency allowing for the use of small inductors.

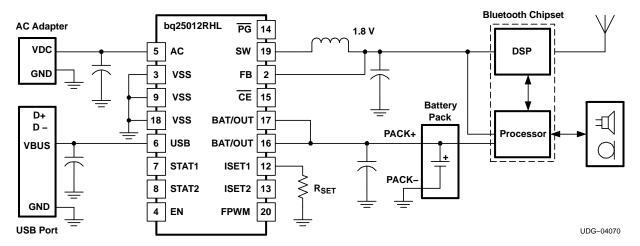

#### TYPICAL APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

bgHYBRID is a trademark of Benchmark.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**

| T <sub>A</sub> | OUTPUT VOLTAGE (V) | PART NUMBER (1)(2)         | PACKAGE<br>MARKING |

|----------------|--------------------|----------------------------|--------------------|

|                | Adjustable         | bq25010RHLR                | ANC                |

| -40°C to 125°C | 3.3                | bq25011RHLR <sup>(3)</sup> | ANE                |

|                | 1.8                | bq25012RHLR <sup>(3)</sup> | ANF                |

1) The RHL package is available taped and reeled only in quantities of 3,000 devices per reel.

(3) Advanced Information, contact factory for availability.

#### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                                             |                                                   | bq25010<br>bq25011<br>bq25012 |

|---------------------------------------------|---------------------------------------------------|-------------------------------|

| Supply voltage                              | AC, USB (wrt VSS)                                 | –0.3 V to 7 V                 |

| lanut voltage                               | PG, OUT, ISET1, ISET2, STAT1, STAT2, TS (wrt VSS) | –0.3 V to 7 V                 |

| Input voltage                               | EN, FB, FPWM, SW (wrt VSS)                        | V <sub>OUT</sub> + 0.3 V      |

| Output sink/source surrent                  | PG, STAT1, STAT2                                  | 15 mA                         |

| Output sink/source current                  | TS                                                | 200 μΑ                        |

| Output source current                       | OUT                                               | 1.5 A                         |

| Storage temperature range, T <sub>stg</sub> | -65°C to 150°C                                    |                               |

| Junction temperature range, T <sub>J</sub>  |                                                   | 0°C to 125°C                  |

| Lead temperature (solderig, 10 sec          | conds)                                            | 260°C                         |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

#### **RECOMMENDED OPERATING CONDITIONS**

|          |                                      | MIN  | MAX | UNIT |

|----------|--------------------------------------|------|-----|------|

| $V_{CC}$ | Supply voltage (from AC input)       | 4.5  | 6.5 | \/   |

| $V_{CC}$ | Supply voltage (from USB input)      | 4.35 | 6.5 | V    |

| $T_J$    | Operating junction temperature range | -40  | 125 | °C   |

#### **DISSIPATION RATINGS**

| PACKAGE                   | T <sub>A</sub> < 40°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 40°C | $\theta_{JA}$ |

|---------------------------|---------------------------------------|------------------------------------------------|---------------|

| 20-pin RHL <sup>(1)</sup> | 1.81 W                                | 21 mW/°C                                       | 46.87°C/W     |

<sup>(1)</sup> This data is based on using the JEDEC High-K board and the exposed die pad is connected to a Cu pad on the board. This is connected to the ground plane by a 2×3 via matrix.

<sup>(2)</sup> This product is RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and is suitable for use in specified lead-free soldering processes. In addition, this product uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

# **ELECTRICAL CHARACTERISTICS**

over junction temperature range (0°C  $\leq$  T $_{J}$   $\leq$  125°C) and the recommended supply voltage range (unless otherwise noted)

|                                           | PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                               | MIN    | TYP   | MAX   | UNIT |  |

|-------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|------|--|

| INPUT CURREN                              | IT                                                    |                                                                                                                                                                                               |        |       |       |      |  |

| I <sub>CC(VCC)</sub>                      | Supply current 1, VCC                                 | $V_{VCC} > V_{VCC(min)}$                                                                                                                                                                      |        | 1.2   | 2.0   | mA   |  |

| I <sub>CC(SLP)</sub>                      | Sleep current                                         | Sum of currents into OUT/BAT, V <sub>VCC</sub> < V <sub>(SLP)</sub>                                                                                                                           |        | 2     | 5     |      |  |

| I <sub>CC(STDBY)</sub>                    | Standyby current                                      | CE = High, 0°C ≤ T <sub>J</sub> ≤ 85°C                                                                                                                                                        |        |       | 150   | 0    |  |

| I <sub>IB(OUT)</sub>                      | Input current, OUT                                    | Charge DONE, V <sub>VCC</sub> > V <sub>VCC(min)</sub> ,<br>I <sub>OUT(SW)</sub> = 0 mA, Converter not switching                                                                               |        | 15 35 |       | μA   |  |

| I <sub>IB</sub>                           | Input current, CE                                     | , ,                                                                                                                                                                                           |        |       | 1     |      |  |

| CHARGE VOLT                               | AGE REGULATION (V <sub>BAT(REG)</sub> + \             | / <sub>(DO-MAX)</sub> ≤ V <sub>VCC</sub> , I <sub>(TERM)</sub> < I <sub>OUT(BAT)</sub> ≤ 0.5 A)                                                                                               |        |       |       |      |  |

| V <sub>REG(BAT)</sub>                     | Charger output voltage                                |                                                                                                                                                                                               |        | 4.2   |       | V    |  |

|                                           | Charge voltage regulation                             | T <sub>A</sub> = 25°C                                                                                                                                                                         | -0.35% |       | 0.35% |      |  |

|                                           | accuracy                                              |                                                                                                                                                                                               | -1%    |       | 1%    |      |  |

| (V <sub>(AC)</sub> - V <sub>(OUT)</sub> ) | AC dropout voltage                                    | $V_{OUT (BAT)} = V_{REG (BAT)}, I_{OUT (BAT)} = 0.5 A$                                                                                                                                        |        | 175   | 250   |      |  |

|                                           |                                                       | $V_{OUT (BAT)} = V_{REG (BAT)}$ , ISET2 = High                                                                                                                                                |        | 350   | 500   | mV   |  |

| $(V_{(USB)} - V_{(OUT)})$                 | USB dropout voltage                                   | $V_{OUT (BAT)} = V_{REG (BAT)}$ , ISET2 = Low                                                                                                                                                 |        | 60    | 100   |      |  |

| CHARGE CURR                               | RENT REGULATION                                       |                                                                                                                                                                                               |        |       |       | II   |  |

| I <sub>OUT (BAT)</sub>                    | AC output current range                               | $\begin{split} & V_{VCC}{\geq}~4.5~V,~V_{OUT~(BAT)} = V_{(LOWV)},\\ & V_{VCC}{-}~V_{OUT~(BAT)} > V_{(DO\text{-MAX)}},\\ & I_{OUT(BAT)} = (K_{(SET)}{\times}~V_{(SET)}~/~R_{SET}) \end{split}$ | 50     |       | 500   |      |  |

| 1                                         | LICE output ourrent rongs                             | $V_{VCC(min)} \ge 4.5 \text{ V}, V_{OUT (BAT)} = V_{(LOWV)}, V_{VCC} - V_{OUT (BAT)} > V_{(DO-MAX)}, ISET2 = Low$                                                                             | 80     |       | 100   | mA   |  |

| IOUT (BAT)                                | USB output current range                              | $V_{VCC(min)} \ge 4.5 \text{ V}, V_{OUT \text{ (BAT)}} = V_{\text{(LOWV)}}, V_{VCC} - V_{OUT \text{ (BAT)}} > V_{\text{(DO-MAX)}}, \text{ ISET2} = \text{High}$                               | 400    |       | 500   |      |  |

| V <sub>(SET)</sub>                        | Output current set voltage                            | Voltage on ISET1, $V_{VCC} \ge 4.5 \text{ V}$ , $V_{OUT (BAT)} = V_{(LOWV)}$ , $V_{VCC} - V_{OUT (BAT)} > V_{(DO-MAX)}$ , ISET2 = High                                                        | 2.436  | 2.500 | 2.538 | V    |  |

|                                           |                                                       | 50 mA ≤ I <sub>OUT(OUT)</sub> ≤ 500 mA                                                                                                                                                        | 307    | 322   | 337   |      |  |

| K <sub>(SET)</sub>                        | Output current set factor                             | 10 mA ≤ I <sub>OUT(OUT)</sub> ≤ 50 mA                                                                                                                                                         | 296    | 320   | 346   |      |  |

| ,                                         |                                                       | 10 mA ≤ I <sub>OUT(OUT)</sub> ≤ 10 mA                                                                                                                                                         | 246    | 320   | 416   |      |  |

| PRECHARGE a                               | nd SHORT-CIRCUIT CURRENT R                            | EGULATION                                                                                                                                                                                     |        |       |       |      |  |

| V <sub>(LOWV)</sub>                       | Precharge to fast-charge transition threshold         | Voltage on OUT/BAT                                                                                                                                                                            | 2.8    | 3.0   | 3.2   | V    |  |

| t <sub>PRECHG_DG</sub>                    | Deglitch time for fast-charge to precharge transition | $V_{VCC(min)} \ge 4.5 \text{ V}, t_{FALL} = 100 \text{ ns},$ 10 mV overdrive, $V_{IN(BAT)}$ decreasing below threshold                                                                        | 250    | 375   | 500   | ms   |  |

| I <sub>OUT(PRECHG)</sub>                  | Precharge range                                       | 0 V < $V_{IN(BAT)}$ < $V_{(LOWV)}$ , $t < t_{(PRECHG)}$ , $I_{OUT(PRECHG)} = (K_{(SET)} \times V_{(PRECHG)})/R_{SET}$                                                                         | 5      |       | 100   | mA   |  |

| V <sub>(PRECHG)</sub>                     | Precharge set voltage                                 | Voltage on ISET1, $V_{REG(BAT)} = 4.2 \text{ V}$ , $0 \text{ V} < V_{IN(BAT)} < V_{(LOWV)}$ , $t < t_{(PRECHG)}$                                                                              | 240    | 255   | 270   | mV   |  |

| CHARGE TAPE                               | R and TERMINATION DETECTION                           |                                                                                                                                                                                               |        |       |       | 1    |  |

| I <sub>(TAPER)</sub>                      | Charge taper detection range                          | $V_{\text{IN(BAT)}} > V_{\text{(RCH)}}, t < t_{\text{(PRECHG)}},$ $I_{\text{(TAPER)}} = (K_{\text{(SET)}} \times V_{\text{(TAPER)}}) / R_{\text{SET}}$                                        | 5      |       | 100   | mA   |  |

| V <sub>(TAPER)</sub>                      | Charge taper detection set voltage                    | Voltage on ISET1, $V_{REG(BAT)} = 4.2 \text{ V}$ , $V_{IN(BAT)} > V_{(RCH)}$ , $t < t_{(PRECHG)}$                                                                                             | 235    | 250   | 265   |      |  |

| V <sub>(TERM)</sub>                       | Charge termination detection set voltage              | Voltage on ISET1, $V_{REG(BAT)} = 4.2 \text{ V}$ , $V_{IN(BAT)} > V_{(RCH)}$ , $t < t_{(PRECHG)}$ , $I_{(TERM)} = (K_{(SET)} \times V_{(TERM)})/R_{SET}$                                      | 11     | 18    | 25    | mV   |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

over junction temperature range (0°C  $\leq$  T $_{J}$   $\leq$  125°C) and the recommended supply voltage range (unless otherwise noted)

|                         | PARAMETER                               | TEST CONDITIONS                                                                                                                                   | MIN                                                   | TYP                             | MAX                                                  | UNIT |

|-------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------|------------------------------------------------------|------|

| t <sub>TPRDET_DG</sub>  | Deglitch time for taper detection       | V <sub>VCC(min)</sub> ≥ 4.5 V, t <sub>FALL</sub> = 100 ns,<br>10 mV overdrive, I <sub>CHG</sub> increasing above or<br>decreasong below threshold | 250                                                   | 375                             | 500                                                  | ma   |

| t <sub>TERMDET_DG</sub> | Deglitch time for termination detection | $V_{VCC(min)} \ge 4.5 \text{ V}, t_{FALL} = 100 \text{ ns},$<br>10 mV overdrive,<br>$I_{CHG}$ decreasing below threshold                          | 350                                                   | 375                             | 500                                                  | ms   |

| BATTERY REC             | CHARGE THRESHOLD                        |                                                                                                                                                   |                                                       |                                 |                                                      |      |

| V <sub>RCH</sub>        | Recharge threshold voltage              |                                                                                                                                                   | V <sub>REG(BAT)</sub><br>- 0.115                      | V <sub>REG(BAT)</sub><br>- 0.10 | V <sub>REG(BAT)</sub><br>- 0.085                     | V    |

| t <sub>RCHDET</sub>     | Deglitch time for recharge detect       | V <sub>VCC(min)</sub> ≥ 4.5 V, t <sub>FALL</sub> = 100 ns,<br>10 mV overdrive, I <sub>CHG</sub> decreasing below or<br>increasing above threshold | 250                                                   | 375                             | 500                                                  | ms   |

| STAT1, STAT2            | and PG OUTPUTS                          |                                                                                                                                                   |                                                       |                                 |                                                      |      |

| V <sub>OL</sub>         | Low-level output voltage                | I <sub>OL</sub> = 5 mA                                                                                                                            |                                                       |                                 | 0.25                                                 | V    |

| ISET2 and CE            | INPUTS                                  |                                                                                                                                                   |                                                       |                                 |                                                      |      |

| $V_{IL}$                | Low-level input voltage                 | I <sub>IL</sub> = 10 μA                                                                                                                           | 0                                                     |                                 | 0.4                                                  |      |

| V <sub>IH</sub>         | High-level input voltage                | I <sub>IL</sub> = 20 μA                                                                                                                           | 1.4                                                   |                                 |                                                      | V    |

| I <sub>IL</sub>         | Low-level input current, CE             |                                                                                                                                                   | -1                                                    |                                 |                                                      |      |

| I <sub>IH</sub>         | High-level input current, CE            |                                                                                                                                                   |                                                       |                                 | 1                                                    |      |

| I <sub>IL</sub>         | Low-level input current, ISET2          | V <sub>ISET2</sub> = 0 V                                                                                                                          | -20                                                   |                                 |                                                      | μΑ   |

| I <sub>IH</sub>         | High-level input current, ISET2         |                                                                                                                                                   |                                                       |                                 | 40                                                   |      |

| I <sub>IHZ</sub>        | High-Z input current, ISET2             | V <sub>ISET2</sub> = High-Z                                                                                                                       |                                                       |                                 | 1                                                    | 1    |

| TIMERS                  |                                         | .02.2                                                                                                                                             |                                                       |                                 |                                                      | 1    |

| t <sub>(PRECHG)</sub>   | Precharge time                          |                                                                                                                                                   | 1620                                                  | 1800                            | 1930                                                 |      |

| t <sub>(TAPER)</sub>    | Taper time                              |                                                                                                                                                   | 1620                                                  | 1800                            | 1930                                                 | s    |

| t <sub>(CHG)</sub>      | Charge time                             |                                                                                                                                                   | 16200                                                 | 18000                           | 19300                                                |      |

| I <sub>(FAULT)</sub>    | Timer fault recovery current            |                                                                                                                                                   |                                                       | 200                             |                                                      | μA   |

|                         | ARATOR for CHARGER                      | I                                                                                                                                                 |                                                       |                                 |                                                      |      |

| $V_{(SLP)}$             | Sleep mode entry threshold              | $2.3 \text{ V} \leq V_{\text{IN(BAT)}} \leq V_{\text{REG(BAT)}}$                                                                                  |                                                       |                                 | V <sub>VCC</sub> ≤<br>V <sub>IN(BAT)</sub><br>+80 mV | .,   |

| V <sub>(SLP_DG)</sub>   | Sleep mode exit threshold               | $2.3 \text{ V} \leq V_{\text{IN(BAT)}} \leq V_{\text{REG(BAT)}}$                                                                                  | V <sub>VCC</sub> ≥<br>V <sub>IN(BAT)</sub><br>+190 mV |                                 |                                                      | V    |

| t <sub>(DEGL)</sub>     | Deglitch time for sleep mode            | V <sub>CC</sub> decreasing below threshold,<br>t <sub>FALL</sub> = 100 ns, 10 mV overdrive,                                                       | 250                                                   | 375                             | 500                                                  | ms   |

| THERMAL SHU             |                                         |                                                                                                                                                   |                                                       |                                 |                                                      |      |

| T <sub>(SHTDWN)</sub>   | Thermal trip threshold temperature      |                                                                                                                                                   |                                                       | 165                             |                                                      | °C   |

|                         | Thermal hysteresis                      |                                                                                                                                                   |                                                       | 15                              |                                                      |      |

| UNDERVOLTA              | GE LOCKOUT AND POR                      |                                                                                                                                                   | 1                                                     |                                 |                                                      | 1    |

| V <sub>(UVLO_CHG)</sub> | Undervoltage lockout threshold voltage  | Decreasing V <sub>CC</sub>                                                                                                                        | 2.4                                                   | 2.5                             | 2.6                                                  | V    |

|                         | Hysteresis                              |                                                                                                                                                   |                                                       | 27                              |                                                      | mV   |

| $V_{POR}$               | POR threshold voltage <sup>(1)</sup>    |                                                                                                                                                   | 2.3                                                   | 2.4                             | 2.5                                                  | V    |

| DC-DC INPUT/            | OUTPUT CURRENT                          |                                                                                                                                                   |                                                       |                                 |                                                      |      |

| V <sub>(BAT)</sub>      | Input voltage range                     | Input power absent Input power present                                                                                                            | V <sub>(LOWV)</sub>                                   |                                 | 4.2<br>4.2                                           | V    |

| V                       | Undervoltage lockout                    | mpat power present                                                                                                                                | V (UVLO)                                              |                                 | 2.0                                                  | ļ -  |

| $V_{(UVLO)}$            | Undervollage lockout                    |                                                                                                                                                   |                                                       |                                 | 2.0                                                  |      |

(1) Ensured by design. Not production tested.

# **ELECTRICAL CHARACTERISTICS (continued)**

over junction temperature range (0°C  $\leq$  T $_{J}$   $\leq$  125°C) and the recommended supply voltage range (unless otherwise noted)

| PARAMETER                    |                                 | TEST CONDITIONS | MIN                                                                                                                    | TYP   | MAX  | UNIT      |     |

|------------------------------|---------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------|-------|------|-----------|-----|

| I <sub>OUT_L</sub>           | Maximum output cu               | rrent           |                                                                                                                        |       |      | 150       | mA  |

| FPWM - bq2                   | 5010                            |                 |                                                                                                                        |       |      |           |     |

| V <sub>IH(FPWM)</sub>        | High-level input volt           | age             |                                                                                                                        | 2.0   |      |           |     |

| V <sub>IL(FPWM)</sub>        | Low-level input voltage         |                 |                                                                                                                        |       |      | 0.4       |     |

|                              | 11 and bq25012                  |                 | -                                                                                                                      |       |      |           |     |

| V <sub>IH(FPWM)</sub>        | High-level input volt           | age             |                                                                                                                        | 1.3   |      |           |     |

| V <sub>IL(FPWM)</sub>        | Low-level input volta           | age             |                                                                                                                        |       |      | 0.4       | V   |

| I <sub>FPWM</sub>            | Input bias current              |                 | V <sub>EN</sub> = GND or V <sub>BAT</sub> , V <sub>FPWM</sub> = GND or V <sub>BAT</sub>                                |       | 0.01 | 0.1       | μΑ  |

| ENABLE                       |                                 |                 | -                                                                                                                      |       |      |           | 1   |

| $V_{IH(EN)}$                 | High-level input volt           | age             |                                                                                                                        | 1.3   |      |           | .,  |

| V <sub>IL(EN)</sub>          | Low-level input volta           | age             |                                                                                                                        |       |      | 0.4       | V   |

| I <sub>EN</sub>              | Input bias current              |                 | V <sub>EN</sub> = GND or V <sub>BAT</sub> , V <sub>FPWM</sub> = GND or V <sub>BAT</sub>                                |       | 0.01 | 0.1       | μΑ  |

| POWER SWI                    | тсн                             |                 |                                                                                                                        |       |      |           |     |

|                              | Internal P-channel N            | //OSFET         | $V_{IN} = V_{GS} = 3.6 \text{ V}$                                                                                      |       | 0.97 | 1.52      | -   |

| Б                            | on-resistance                   |                 | $V_{IN} = V_{GS} = 2.5 \text{ V}$                                                                                      |       | 1.27 | 2.00      |     |

| R <sub>DS(on)</sub> Internal | Internal N-channel N            | MOSFET          | $V_{IN} = V_{GS} = 3.6 \text{ V}$                                                                                      |       | 0.68 | 1.19      |     |

|                              | on-resistance                   |                 | $V_{IN} = V_{GS} = 2.5 \text{ V}$                                                                                      |       | 0.86 | 1.45      |     |

| I <sub>LEAK(P)</sub>         | P-channel leakage               | current         | V <sub>DS</sub> = 6.0 V                                                                                                |       | 0.1  | 1.0       |     |

| I <sub>LEAK(N)</sub>         | N-channel leakage               | current         | V <sub>DS</sub> = 6.0 V                                                                                                |       | 0.1  | 1.0       | μA  |

| I <sub>(LIM)</sub>           | P-channel current li            | mit             | 2.5 V < V <sub>BAT</sub> < 4.2 V                                                                                       | 190   | 230  | 350       | mA  |

| OSCILLATOR                   | ₹                               |                 |                                                                                                                        |       |      |           |     |

| $f_{SW}$                     | Switching frequency             | ,               |                                                                                                                        | 0.65  | 1.00 | 1.50      | MHz |

| OUTPUT                       |                                 |                 |                                                                                                                        |       |      |           | •   |

| $V_{REF}$                    | Reference voltage               | bq25010         |                                                                                                                        |       | 0.5  |           |     |

| $V_{FB}$                     | Feedback voltage <sup>(2)</sup> | bq25010         | 3.6 V ≤ V <sub>BAT</sub> ≤ 4.2 V, 0 mA ≤ I <sub>OUT</sub> ≤ 150 mA                                                     | -3%   |      | +3%       |     |

|                              | Adjustable output voltage range | bq25010         |                                                                                                                        | 0.7   |      | $V_{BAT}$ | V   |

| $V_{DC-DC}$                  | Fixed output volt-              | bq25011         | $3.6 \text{ V} \le \text{V}_{\text{BAT}} \le 4.2 \text{ V}, 0 \text{ mA} \le \text{I}_{\text{OUT}} \le 150 \text{ mA}$ | 3.2   | 3.3  | 3.4       |     |

|                              | age                             | bq25012         | $3.6 \text{ V} \le \text{V}_{\text{BAT}} \le 4.2 \text{ V}, 0 \text{ mA} \le \text{I}_{\text{OUT}} \le 150 \text{ mA}$ | 1.746 | 1.8  | 1.854     |     |

<sup>(2)</sup> For output voltages ≤ 1.2 V a 22-μF output capacitor value is required to achieve a maximum output voltage accuracy of +3% while operating in power save mode (PFM).

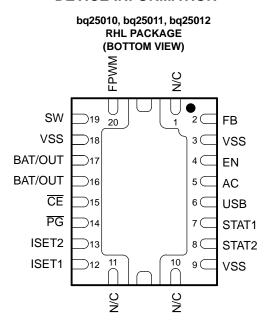

#### **DEVICE INFORMATION**

#### **TERMINAL FUNCTIONS**

|         |           |     | 7                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM    | IINAL     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

| NAME    | NO.       |     |                                                                                                                                                                                                                                                                                                                                                                                |

| AC      | 5         | ı   | Charge input voltage from AC adapter                                                                                                                                                                                                                                                                                                                                           |

| BAT/OUT | 16        | I/O | Charge current output                                                                                                                                                                                                                                                                                                                                                          |

| BAT/OUT | 17        | ı   | Battery input to DC-DC converter                                                                                                                                                                                                                                                                                                                                               |

| CE      | 15        | ı   | Charge enable input (active low)                                                                                                                                                                                                                                                                                                                                               |

| EN      | 4         | ı   | Enable input for DC-DC converter                                                                                                                                                                                                                                                                                                                                               |

| FB      | 2         | ı   | Feedback pin for DC-DC converter                                                                                                                                                                                                                                                                                                                                               |

| FPWM    | 20        | I   | PWM control input for the DC-DC converter                                                                                                                                                                                                                                                                                                                                      |

| ISET1   | 12        | I   | Charge current set point for AC input and precharge and taper set point for both AC and USB                                                                                                                                                                                                                                                                                    |

| ISET2   | 13        | Ĺ   | Charge current set point for USB port (High = 500 mA, Low = 100 mA, High-Z = disable USB charge)                                                                                                                                                                                                                                                                               |

| NC      | 1, 10, 11 | -   | No connect. These pins must be left floating.                                                                                                                                                                                                                                                                                                                                  |

| PG      | 14        | 0   | Power good status output (active low)                                                                                                                                                                                                                                                                                                                                          |

| STAT1   | 7         | 0   | Charge status output 1 (open-drain)                                                                                                                                                                                                                                                                                                                                            |

| STAT2   | 8         | 0   | Charge status output 2 (open-drain)                                                                                                                                                                                                                                                                                                                                            |

| SW      | 19        | 0   | Output of the DC/DC converter                                                                                                                                                                                                                                                                                                                                                  |

| USB     | 6         | I   | Charge input voltage from USB adapter                                                                                                                                                                                                                                                                                                                                          |

| VSS     | 3, 9, 18  | _   | Ground Input. Also note that there is an internal electrical connection between the exposed thermal pad and VSS pins of the device. The exposed thermal pad must be connected to the same potential as the Vss pin on the printed circuit board. Do not use the thermal pad as the primary ground input for the device. All VSS pins must be connected to ground at all times. |

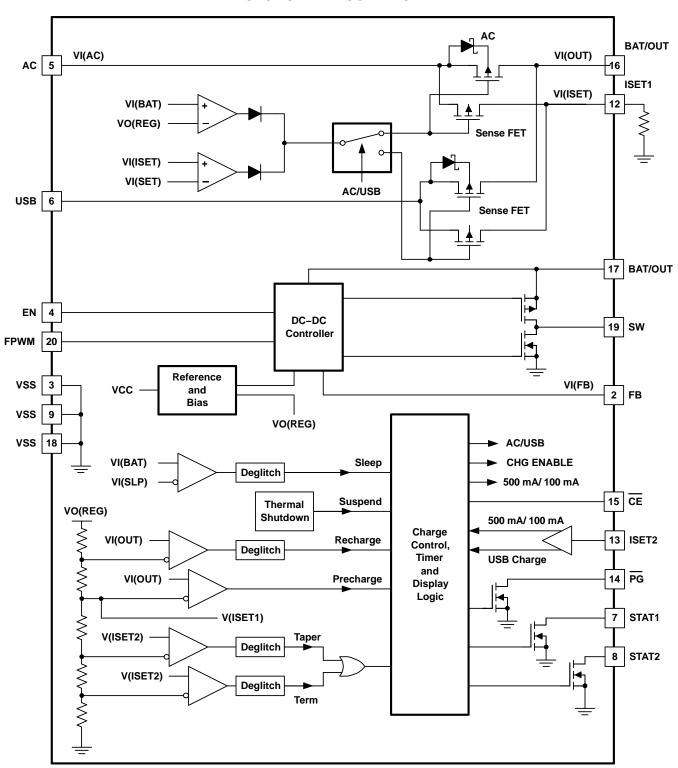

#### **FUNCTIONAL BLOCK DIAGRAM**

UDG-04072

#### **FUNCTIONAL DESCRIPTIONS**

#### **BATTERY CHARGER**

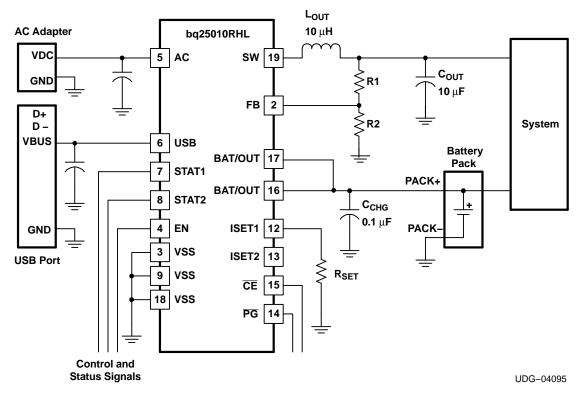

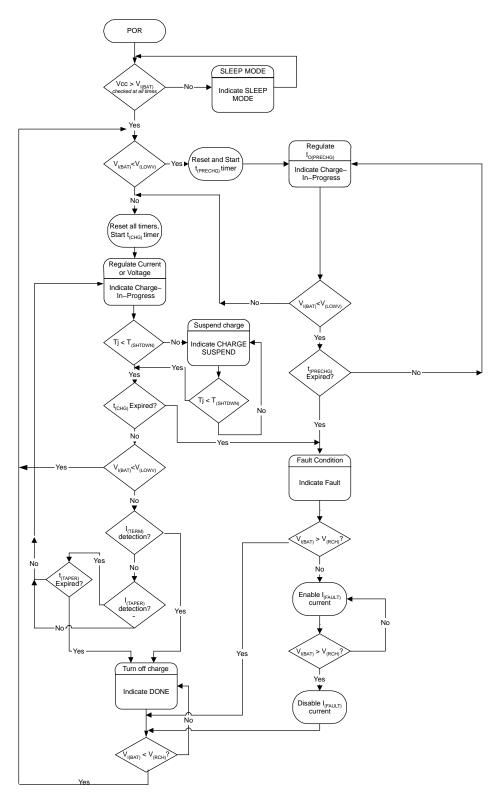

The bqHYBRID supports a precision Li-Ion or Li-Pol charging system suitable for single-cell battery packs and a low-power DC-DC converter for providing power to system processor. See a typical charge profile, application circuit and an operational flow chart in Figure 1 through Figure 3 respectively.

Figure 1. Typical Charger Profile

**Figure 2. Typical Application Circuit**

# **FUNCTIONAL DESCRIPTIONS (continued)**

Figure 3. Operational Flow Chart

#### FUNCTIONAL DESCRIPTIONS (continued)

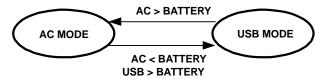

#### **Autononous Power Source Selection**

As default, the bqHYBRID attempts to charge the battery from the AC input. If AC input is not present, the USB input is selected. If both inputs are available, the AC adapter has the priority. Refer to Figure 4 for details.

Figure 4. Power Source Selection

#### **Battery Pre-Conditioning**

During a charge cycle if the battery voltage is below the  $V_{(LOWV)}$  threshold, the bqHYBRID applies a precharge current,  $I_{O(PRECHG)}$ , to the battery. This feature revives deeply discharged cells. The resistor connected between the ISET1 and VSS pins,  $R_{SET}$ , determines the precharge rate. The  $V_{(PRECHG)}$  and  $K_{(SET)}$  parameters are specified in the specifications table.

$$I_{O (PRECHG)} - \frac{V_{(PRECHG)} + K_{(SET)}}{R_{SET}}$$

(1)

The bqHYBRID activates a safety timer,  $t_{(PRECHG)}$ , during the conditioning phase. If  $V_{(LOWV)}$  threshold is not reached within the timer period, the bqHYBRID turns off the charger and enunciates FAULT on the STAT1 and STAT2 pins. Please refer to *Timer Fault Recovery* section for additional details.

#### **Battery Charge Current**

The bqHYBRID offers on-chip current regulation with programmable set point. The resistor connected between the ISET1 and VSS pins,  $R_{SET}$ , determines the charge rate. The  $V_{(SET)}$  and  $K_{(SET)}$  parameters are specified in the specifications table.

$$I_{O (OUT)} - \frac{V_{(SET)} + K_{(SET)}}{R_{SET}}$$

(2)

When charging from a USB port, the host controller has the option of selecting either 100 mA or 500 mA charge rate using the ISET2 pin. A low-level signal sets the current at 100 mA and a high-level signal sets the current at 500 mA. A high-Z input disables USB charging.

#### **Battery Voltage Regulation**

The voltage regulation feedback is through the BAT/OUT pin. This input is tied directly to the positive side of the battery pack. The bqHYBRID monitors the battery-pack voltage between the BAT/OUT and VSS pins. When the battery voltage rises to  $V_{O(REG)}$  threshold, the voltage regulation phase begins and the charging current begins to taper down.

As a safety backup, the bqHYBRID also monitors the charge time in the charge mode. If taper threshold is not detected within this time period,  $t_{(CHG)}$ , the bqHYBRID turns off the charger and enunciates FAULT on the STAT1 and STAT2 pins. Please refer to section titled *Timer Fault Recovery*section for additional details.

#### **Charge Taper Detection, Termination and Regharge**

The bqHYBRID monitors the charging current during the voltage regulation phase. Once the taper threshold,  $I_{(TAPER)}$ , is detected the bqHYBRID initiates the taper timer,  $t_{(TAPER)}$ . Charge is terminated after the timer expires. The resistor connected between the ISET1 and VSS pins,  $R_{SET}$ , determines the taper detection level. The  $V_{(TAPER)}$  and  $K_{(SET)}$  parameters are specified in the specifications table. Note that this applies to both AC and USB charging.

#### **FUNCTIONAL DESCRIPTIONS (continued)**

$$I_{(TAPER)} - \frac{V_{(TAPER)} + K_{(SET)}}{R_{SET}}$$

(3)

The bqHYBRID resets the taper timer in the event that the charge current returns above the taper threshold,  $I_{(TAPER)}$ .

In addition to the taper current detection, the bqHYBRID terminates charge in the event that the charge current falls below the  $I_{(TERM)}$  threshold. This feature allows for quick recognition of a battery removal condition or insertion of a fully charged battery. Note that taper timer is not activated. The resistor connected between the ISET1 and VSS pins,  $R_{SET}$ , determines the taper detection level. The  $V_{(TERM)}$  and  $K_{(SET)}$  parameters are specified in the specifications table. Note that this applies to both AC and USB charging.

$$I_{(TERM)} - \frac{V_{(TERM)} + K_{(SET)}}{R_{SET}}$$

(4)

After charge termination, the bqHYBRID restarts the charge once the voltage on the BAT/OUT pin falls below the  $V_{(RCH)}$  threshold. This feature keeps the battery at full capacity at all times.

### **Sleep Mode for Charger**

The bqHYBRID enters the low-power sleep mode if both AC and USB are removed from the circuit. This feature prevents draining the battery during the absence of  $V_{CC}$ .

#### **Operation Modes**

Operational modes of the bqHYBRID are summarized in Table 1. Operation of DC-DC is not recommended while charger is in precharge mode.

**BATTERY VOLTAGE AC or USB ADAPTER STATUS CHARGER STATUS DC-DC STATUS** Present Fast ΕN  $V_{I(BAT)} > V_{(LOWV)}$  $0 \text{ V} < V_{\text{I(BAT)}} < V_{\text{(LOWV)}}$ Present Precharge ΕN  $V_{I(BAT)} < V_{(UVLO)}$ Both absent Off Off

**Table 1. Operation Modes**

#### **Status Outputs**

The STAT1 and STAT2 open-drain outputs indicate various charger and battery conditions as shown in Table 2. These status pins can be used to communicate to the host processor. Note that OFF indicates the open-drain transistor is turned off.

**Table 2. Status Pins Summary**

| CHARGE STATE            | INPUT POWER STATE | STAT1 | STAT2 |

|-------------------------|-------------------|-------|-------|

| Precharge in progress   | Present           | ON    | ON    |

| Fast charge in progress | Present           | ON    | OFF   |

| Charge done             | Not reported      | OFF   | ON    |

| Timer fault             | Not reported      | OFF   | OFF   |

| Speel mode              | Absent            | OFF   | OFF   |

#### **PG** Output (Power Good)

The open-drain  $\overline{PG}$  output indicates when the AC adapter is present. The output turns ON when a valid voltage is detected. This output is turned off in the sleep mode. The  $\overline{PG}$  pin can be used to drive an LED or communicate to the host processor.

SLUS615-DECEMBER 2004

#### **CE** Input (Charge Enable)

The  $\overline{\text{CE}}$  digital input is used to enable or disable the charge process. A low-level signal on this pin enables the charge and a high-level signal disables the charge and places the device into a low-power mode. A high-to-low transition on this pin also resets all timers and timer fault conditions. Note that this applies to both AC and USB charging.

#### **Thermal Shutdown and Protection**

The bqHYBRID monitors the junction temperature,  $T_J$ , of the die and suspends charging if  $T_J$  exceeds  $T_{(SHTDWN)}$ . Charging resumes when  $T_J$  falls below  $T_{(SHTDWN)}$  by approximately 15°C.

#### **Timer Fault Recovery**

As shown in Figure 3, bqHYBRID provides a recovery method to deal with timer fault conditions. The following summarizes this method:

Condition 1: Charge voltage above recharge threshold (V<sub>(RCH)</sub>) and timeout fault occurs.

Recovery method: bqHYBRID waits for the battery voltage to fall below the recharge threshold. This could happen as a result of a load on the battery, self-discharge or battery removal. Once the battery falls below the recharge threshold, the bqHYBRID clears the fault and starts a new charge cycle. A POR or  $\overline{\text{CE}}$  toggle also clears the fault.

**Condition 2:** Charge voltage below recharge threshold (V<sub>(RCH)</sub>) and timeout fault occurs.

Recovery method: Under this scenario, the bqHYBRID applies the  $I_{(FAULT)}$  current. This small current is used to detect a battery removal condition and remains on as long as the battery voltage stays below the recharge threshold. If the battery voltage goes above the recharge threshold, then the bqHYBRID disables the  $I_{(FAULT)}$  current and executes the recovery method described for Condition 1. Once the battery falls below the recharge threshold, the bqHYBRID clears the fault and starts a new charge cycle. A POR or  $\overline{CE}$  toggle also clears the fault.

#### **DC-DC CONVERTER**

The bqHYBRID provides a low quiescent-current synchronous DC-DC converter. The internally compensated converter is designed to operate over the entire voltage range of a single-cell Li-Ion or Li-Pol battery. Under nominal load current, the device operates with a fixed PWM switching frequency of typically 1 MHz. At light load currents, the device enters the power save mode of operation; the switching frequency is reduced and the quiescent current drawn by the converter from the BAT/OUT pin is typically only 15  $\mu$ A.

During PWM operation the converter uses a unique fast-response voltage mode controller scheme with input voltage feedforward to achieve good line and load regulation allowing the use of small ceramic input and output capacitors. At the beginning of each clock cycle initiated by the clock signal (S), the P-channel MOSFET switch is turned on and the inductor current ramps up until the comparator trips and the control logic turns off the switch. The current limit comparator also turns off the switch in case the current limit of the P-channel switch is exceeded. After the dead time preventing current shoot through the N-channel MOSFET rectifier is turned on and the inductor current ramps down. The next cycle is initiated by the clock signal again turning off the N-channel rectifier and turning on the on the P-channel switch. The g<sub>M</sub> amplifier as well as the input voltage determines the rise time of the saw-tooth generator and therefore any change in input voltage or output voltage directly controls the duty cycle of the converter giving a very good line and load transient regulation.

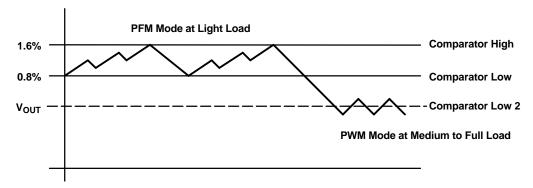

#### **Power Save Mode Operation**

As the load current decreases the converter enters the power save mode operation. During power save mode the converter operates with reduced switching frequency in PFM mode and with a minimum quiescent current to maintain high efficiency.

Two conditions allow the converter to enter the power save mode operation. One is the detection of discontinuous conduction mode. The other is when the peak switch current in the P-channel switch goes below the skip current limit. The typical skip current limit can be calculated as:

$$I_{SKIP} - 66 \text{ mA} + \frac{V_{IN}}{160 \theta} \tag{5}$$

During the power save mode the output voltage is monitored with the comparator by the thresholds comp low and comp high. As the output voltage falls below the comp low threshold (set to typically 0.8% above VOUT nominal) the P-channel switch turns on. The P-channel switch is turned off as the peak switch current is reached. The typical peak switch current can be calculated as:

$$I_{PEAK} - 66 \text{ mA} + \frac{V_{IN}}{80 \text{ }\theta} \tag{6}$$

The N-channel rectifier is turned on and the inductor current ramps down. As the inductor current approaches zero the N-channel rectifier is turned off and the P-channel switch is turned on again starting the next pulse. The converter continues these pulses until the comp high threshold (set to typically 1.6% above VOUT nominal) is reached. The converter enters a sleep mode, reducing the quiescent current to a minimum. The converter wakes up again as the output voltage falls below the comp low threshold again. This control method reduces the quiescent current to typically to 15  $\mu$ A and the switching frequency to a minimum, thereby achieving high converter efficiency. Setting the skip current thresholds to typically 0.8% and 1.6% above the nominal output voltage at light load current results in a dynamic output voltage achieving lower absolute voltage drops during heavy load transient changes. This allows the converter to operate with a small output capacitor of only 10  $\mu$ F and still have a low absolute voltage drop during heavy load transient changes. Refer to Figure 5 as well for detailed operation of the power save mode.

Figure 5. Power Save Mode Thresholds and Dynamic Voltage Positioning

The converter enters the fixed-frequency PWM mode again as soon as the output voltage drops below the comp low 2 threshold.

#### **Dynamic Voltage Positioning**

As described in the power save mode operation section and as detailed in Figure 5, the output voltage is typically 0.8% above the nominal output voltage at light load currents as the device is in power save mode. This gives additional headroom for the voltage drop during a load transient from light load to full load. During a load transient from full load to light load the voltage overshoot is also minimized due to active regulation turning on the N-Channel rectifier switch.

#### **Soft-Start**

The bqHYBRID has an internal soft-start circuit that limits the inrush current during startup. This soft-start is implemented as a digital circuit increasing the switch current in steps of typically 30 mA, 60 mA, 120 mA and then the typical switch current limit of 230 mA. Therefore the starup time depends mainly on the output capacitor and load current. Typical startup time with a 10-µF output capacitor and a 100-mA load current is 1.6 ms.

#### 100% Duty Cycle Low Dropout Operation

The bqHYBRID offers a low input-to-output voltage difference while still maintaining operation with the use of the 100% duty cycle mode. In this mode the P-channel switch is constantly turned on. This is particularly useful in battery-powered applications to achieve longest operation time by taking full advantage of the whole battery voltage range. The minimum input voltage to maintain regulation depends on the load current and output voltage and can be calculated as:

$$V_{IN(min)} V_{OUT(max)} - I_{OUT(max)} + (R_{DS(on)MAX} - R_L)$$

(7)

where

$I_{OUT(max)}$  = maximum output current plus indicator ripple current

$R_{DS(on)MAX}$  = maximum P-channel switch  $R_{DS(on)}$

$R_1$  = DC resistance of the inductor

V<sub>OUT(max)</sub> = nominal output voltage plus maximum output voltage tolerance

#### **Enable**

Pulling the enable pin  $(\overline{EN})$  low forces the DC-DC converter into shutdown mode, with a shutdown quiescent current of typically 0.1  $\mu$ A. In this mode the P-channel switch and N-channel rectifier are turned off, the internal resistor feedback divider is disconnected, and the converter enters shutdown mode. If an output voltage, which could be an external voltage source or a super capacitor, is present during shut down, the reverse leakage current is specified under electrical characteristics. For proper operation the  $\overline{EN}$  pin must be terminated and should not be left floating.

Pulling the EN pin high starts up the DC-DC converter with the soft-start as previously described.

#### **Undervoltage Lockout**

The undervoltage lockout circuit prevents the converter from turning on the switch or rectifier MOSFET at low input voltages or under undefined conditions.

#### **Forced PWM Mode**

The FPWM input pin allows the host system to override the power save mode by driving the FPWM pin high. In this state, the DC-DC converter remains in the PWM mode of operation with continuous current conduction regardless of the load conditions. Tying the FPWM pin low allows the device to enter power save mode automatically as previously described.

#### **APPLICATION INFORMATION**

#### **ADJUSTABLE OUTPUT VOLTAGE VERSION (bg25010)**

When the adjustable output voltage version of the bqHYBRID is being used (bq25010), the output is set by the external resistor divider, as shown in Figure 2.

The output voltage can be calculated as:

$$V_{OUT} = 0.5 V + \left(1 - \frac{R1}{R2}\right)$$

(8)

where

$R1 + R2 \le 1 M\Omega$

Internal reference voltage  $V_{REF(typ)} = 0.5 \text{ V}$

C1 and C2 should be selected as:

$$C1 - \frac{1}{2\theta + 10 \text{ kHz} + R1}$$

(9)

where

R1 = upper resistor of the voltage divider

C1 = upper capacitor of the voltage divider

For C1, a value should be chosen that comes closest to the calculated result.

$$C2 - \frac{R1}{R2} + C1$$

(10)

where

R2 = lower resistor of the voltage divider

C2 = lower capacitor of the voltage divider

For C2, the selected capacitor value should always be selected larger than the calculated result. For example, in Figure 2, a 100-pF capacitor is selected for a calculated result of C2 = 86.17 pF.

If quiescent current is not a key design parameter, C1 and C2 can be omitted and a low-impedance feedback divider must be used with R1 + R2 < 100 k $\Omega$ . This design reduces the noise available on the feedback pin (FB) as well, but increases the overall quiescent current during operation.

#### FIXED OUTPUT VOLTAGE VERSION (bg25011, bg25012)

When a fixed output voltage version of the device is being used, no external resistive divider network is necessary. In this case, the output of the inductor should be connected directly the FB pin, as shown in Figure 2.

#### INPUT CAPACITOR SELECTION

In most applications, all that is needed is a high-frequency decoupling capacitor. A 0.1-µF ceramic, placed in close proximity to AC/USB and VSS pins, works fine. The bqHYBRID is designed to work with both regulated and unregulated external DC supplies. If a non-regulated supply is chosen, the supply unit should have enough capacitance to hold up the supply voltage to the minimum required input voltage at maximum load. If not, more capacitance has to be added to the input of the charger.

#### CHARGER OUTPUT CAPACITOR (DC-DC CONVERTER INPUT CAPACITOR) SELECTION

Because the buck converter has a pulsating input current, a low ESR input capacitor is required. This results in the best input voltage filtering and minimizes the interference with other circuits caused by high input voltage spikes. Also, the input capacitor must be sufficiently large to stabilize the input voltage during heavy load transients.

For good input voltage filtering, usually a 4.7-µF input capacitor is sufficient and can be increased without any limit for better input voltage filtering.

If ceramic output capacitors are used, the capacitor RMS ripple current rating ensures the application requirements. For completeness, the RMS ripple current is calculated as:

#### **APPLICATION INFORMATION (continued)**

$$I_{RMS} I_{OUT(max)} + \sqrt{\frac{V_{OUT}}{V_{IN}} + \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

(11)

The worst case RMS ripple current occurs at D=0.5 and is calculated as:

$$I_{RMS} + \frac{I_{OUT}}{2} \tag{12}$$

Ceramic capacitors perform well because of the low ESR value, and they are less sensitive to voltage transients and spikes compared to tantalum capacitors. The input capacitor should be placed as close as possible to the BAT/OUT pin of the device for best performance. Refer to Table 1for recommended components.

#### DC-DC CONVERTER OUTPUT CAPACITOR SELECTION

The advanced fast response voltage mode control scheme of the bqHYBRID allows the use of tiny ceramic capacitors with a minimum value of 10  $\mu$ F without having large output voltage under and overshoots during heavy load transients. Ceramic capacitors having low ESR values have the lowest output voltage ripple and are therefore recommended. If required, tantalum capacitors may be used as well (refer to Table 1 for recommended components). If ceramic output capacitors are used, the capacitor RMS ripple current rating always meets the application requirements. For completeness, the RMS ripple current is calculated as:

$$I_{RMS(Cout)} V_{OUT} + \frac{\left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{L + f} + \frac{1}{2 + \sqrt{3}}$$

(13)

At nominal load current the device operates in PWM mode and the overall output voltage ripple is the sum of the voltage spike caused by the output capacitor ESR plus the voltage ripple caused by charging and discharging the output capacitor:

$$\theta V_{\text{OUT}} \left( V_{\text{OUT}} + \frac{1}{V_{\text{IN}}} \sqrt{\frac{V_{\text{OUT}}}{V_{\text{IN}}}} \sqrt{\frac{1}{8 + C_{\text{OUT}} + f}} - \text{ESR}_{V} \right)$$

(14)

where the output voltage ripple occurs at the highest input voltage V<sub>IN</sub>.

At light load currents the device operates in power save mode, and the output voltage ripple is independent of the output capacitor value. The output voltage ripple is set by the internal comparator thresholds. The typical output voltage ripple is 1% of the output voltage  $V_{OUT}$ .

#### DC-DC CONVERTER OUTPUT INDUCTOR SELECTION

The bqHYBRID is optimized to operate with a typical inductor value of 10 µH.

For high efficiencies, the inductor should have a low DC resistance to minimize conduction losses. Although the inductor core material has less effect on efficiency than its DC resistance, an appropriate inductor core material must be used. The inductor value determines the inductor ripple current. The larger the inductor value, the smaller the inductor ripple current, and the lower the conduction losses of the converter. On the other hand, larger inductor values causes a slower load transient response. Usually the inductor ripple current, as calculated below, should be around 30% of the average output current.

In order to avoid saturation of the inductor, the inductor should be rated at least for the maximum output current of the converter plus the inductor ripple current that is calculated as:

$$\theta I_{L} V_{OUT} + \frac{\left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{L + f}$$

(15)

where

f = switching frequency (1 MHz typical, 650 kHz minimal)

L = inductor value

$\Delta I_L$  = peak-to-peak inductor ripple current

$I_{L(max)}$  = maximum inductor current

The highest inductor current occurs at maximum  $V_{IN}$ . A more conservative approach is to select the inductor current rating just for the maximum switch current of 350 mA.

| TYPICAL OUTPUT CURRENT (mA) | INDUCTOR VALUE<br>(µH) | CAPACITOR VALUE (µF) | APPLICATION                            |

|-----------------------------|------------------------|----------------------|----------------------------------------|

| 30                          | 100                    | 1                    | For low current, smallest capacitor    |

| 60                          | 48                     | 2.2                  | For low current, small capacitor       |

| 80                          | 33                     | 3.3                  | For medium current, small capacitor    |

| 120                         | 22                     | 4.7                  | For medium current                     |

| 150                         | 10                     | 10                   | For highest current, smallest inductor |

Table 3. Recommended Inductor and Capacitor Values

#### CHARGING WHILE UNDER LOAD

The bqHYBRID is designed such that maximum charging safety and efficiency can be obtained by suspending normal operation while the device is actively charging the battery. In this mode of operation, the timeout function prevents a defective battery from being charged indefinitely. If charging does not terminate normally within five hours, the device annunciates a fault condition on the STAT1 and STAT2 pins as indicated in Table 2.

If a load is applied to the device while it is being used to charge a battery, a false fault condition may result due to a slower rate of charge being applied to the battery. For this reason it is recommended that the load be disconnected from the bqHYBRID while it is charging a battery.

#### THERMAL CONSIDERATIONS

The bqHYBRID is packaged in a thermally enhanced MLP package. The package includes a thermal pad to provide an effective thermal contact between the device and the printed circuit board (PCB). Full PCB design guidelines for this package are provided in the application note QFN/SON PCB Attachment (SLUA271). The most common measure of package thermal performance is thermal impedance ( $\theta_{JA}$ ) measured (or modeled) from the chip junction to the air surrounding the package surface (ambient). The mathematical expression for  $\theta_{JA}$  is:

$$\theta_{\mathsf{JA}} - \frac{\mathsf{T}_{\mathsf{J}} + \mathsf{T}_{\mathsf{A}}}{\mathsf{P}} \tag{16}$$

where

$T_J$  = chip junction temperature

$T_A$  = ambient temperature

P = device power dissipation

Factors that can greatly influence the measurement and calculation of  $\theta_{\text{JA}}$  include:

- Whether or not the device is board mounted

- Trace size, composition, thickness, and geometry

- Orientation of the device (horizontal or vertical)

- Volume of the ambient air surrounding the device under test and airflow

- Whether other surfaces are in close proximity to the device being tested

The device power dissipation (P) is a function of the charge rate and the voltage drop across the internal power FET. It can be calculated from the following equation:

$$P \quad \left(V_{IN} - V_{IN(BAT)}\right) + I_{OUT(OUT)} \tag{17}$$

Due to the charge profile of Li-xx batteries, the maximum power dissipation is typically seen at the beginning of the charge cycle when the battery voltage is at its lowest.

#### PCB LAYOUT CONSIDERATIONS

For all switching power supplies, the layout is an important step in the design, especially at high peak currents and switching frequencies. If the layout is not carefully done the regulator could exhibit stability problems as well as EMI problems. With this in mind, one should lay out the PCB using wide, short traces for the main current paths. The input capacitor, as well as the inductor and output capacitors, should be placed as close as possible to the IC pins.

The feedback resistor network (bq25010) must be routed away from the inductor and switch node to minimize noise and magnetic interference. To further minimize noise from coupling into the feedback network and feedback pin, the ground plane or ground traces must be used for shielding. This becomes very important especially at high switching frequencies.

The following are some additional guidelines that should be observed:

- To obtain optimal performance, the decoupling capacitor from AC to VSS (and from USB to VSS) and the

output filter capacitors from BAT/OUT to VSS should be placed as close as possible to the bqHYBRID, with

short trace runs to both signal and VSS pins.

- All low-current VSS connections should be kept separate from the high-current charge or discharge paths

from the battery. Use a single-point ground technique incorporating both the small signal ground path and the

power ground path.

- The BAT/OUT pin provides voltage feedback to the IC for the charging function and should be connected with its trace as close to the battery pack as possible.

- The high current charge paths into AC and USB and from the BAT/OUT and SW pins must be sized appropriately for the maximum charge or output current in order to avoid voltage drops in these traces.

- The bqHYBRID is packaged in a thermally enhanced MLP package. The package includes a thermal pad to

provide an effective thermal contact between the IC and the printed circuit board (PCB). Full PCB design

guidelines for this package are provided in the application note QFN/SON PCB Attachment (SLUA271).

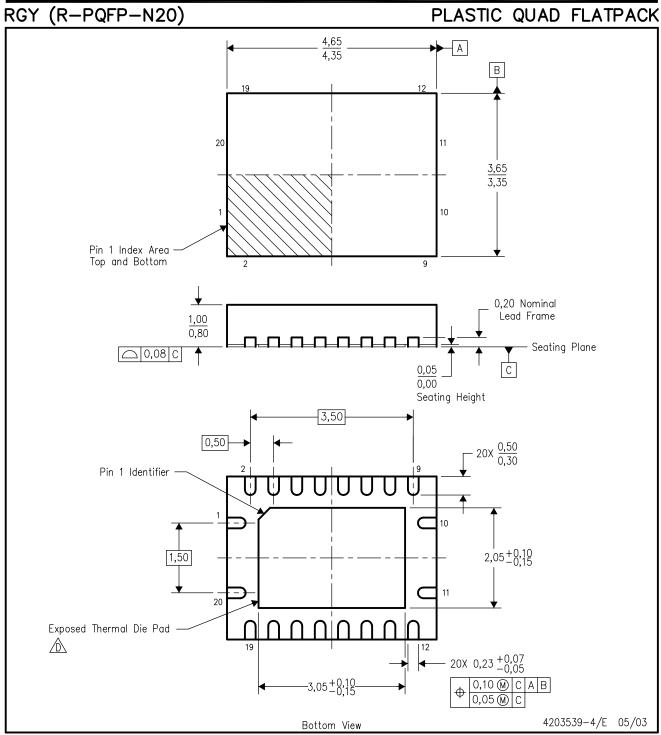

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) package configuration.

- The package thermal performance may be enhanced by bonding the thermal die pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected ground leads.

- E. Package complies to JEDEC MO-241 variation BC.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |