## LINCMOS™ DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

SLCS011B - MAY 1992 - REVISED MARCH 1999

- Wide Range of Supply Voltages 2 V to 8 V

- Fully Characterized at 3 V and 5 V

- **Very-Low Supply-Current Drain** 120 μA Typ at 3 V

- Output Compatible With TTL, MOS, and

- Fast Response Time . . . 200 ns Typ for **TTL-Level Input Step**

- High Input Impedance . . .  $10^{12} \Omega$  Typ

- **Extremely Low Input Bias Current** 5 pA Typ

- **Common-Mode Input Voltage Range Includes Ground**

- **Built-In ESD Protection**

### description

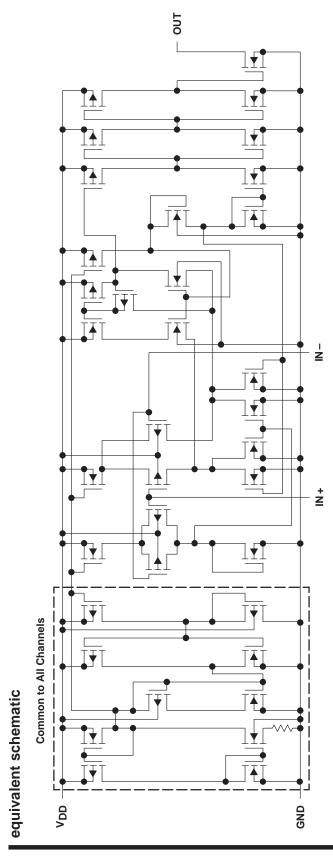

The TLV2352 consists of two independent, low-power comparators specifically designed for single power-supply applications and operates with power-supply rails as low as 2 V. When powered from a 3-V supply, the typical supply current is only 120 μA.

#### symbol (each comparator)

The TLV2352 is designed using the Texas Instruments LinCMOS™ technology and therefore features an extremely high input impedance (typically greater than  $10^{12} \Omega$ ), which allows direct interfacing with high-impedance sources. The outputs are N-channel open-drain configurations that require an external pullup resistor to provide a positive output voltage swing, and they can be connected to achieve positive-logic wired-AND relationships. The TLV2352I is fully characterized at 3 V and 5 V for operation from – 40°C to 85°C. The TLV2352M is fully characterized at 3 V and 5 V for operation from – 55°C to 125°C.

The TLV2352 has internal electrostatic-discharge (ESD)-protection circuits and has been classified with a 1000-V ESD rating using Human Body Model testing. However, care should be exercised in handling this device as exposure to ESD may result in degradation of the device parametric performance.

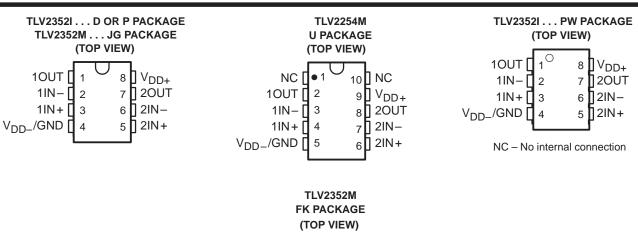

#### **AVAILABLE OPTIONS**

|                   |                                |                                      |                         | PACKAGE                | DEVICES               |                |                       | CUID                |

|-------------------|--------------------------------|--------------------------------------|-------------------------|------------------------|-----------------------|----------------|-----------------------|---------------------|

| TA                | V <sub>IO</sub> max<br>at 25°C | SMALL<br>OUTLINE<br>(D) <sup>†</sup> | CHIP<br>CARRIER<br>(FK) | CERAMIC<br>DIP<br>(JG) | PLASTIC<br>DIP<br>(P) | TSSOP<br>(PW)‡ | PLASTIC<br>DIP<br>(U) | CHIP<br>FORM<br>(Y) |

| -40°C to<br>85°C  | 5 mV                           | TLV2352ID                            |                         |                        | TLV2352IP             | TLV2352IPWLE   |                       | TLV2352Y            |

| −55°C to<br>125°C | 5 mV                           | _                                    | TLV2352MFK              | TLV2352MJG             | _                     | _              | TLV2352MU             | 1LV23321            |

<sup>†</sup> The D package is available taped and reeled. Add the suffix R to the device type (e.g., TLV2352IDR).

These devices have limited built-in protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LinCMOS is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

<sup>&</sup>lt;sup>‡</sup> The PW packages are only available left-ended taped and reeled (e.g., TLV2352IPWLE)

## TLV2352, TLV2352Y LinCMOS™ DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

SLCS011B - MAY 1992 - REVISED MARCH 1999

NC VDD+

3 2 1 20 19

9 10 11 12 13

NC

17 ∏

16 NC

15

2OUT

2IN-

NC

NC

5

NC 6

7

П 8

1IN-

1IN+

NC

INSTRUMENTS

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

### **TLV2352Y chip information**

These chips, when properly assembled, display characteristics similar to the TLV2352. Thermal compression or ultrasonic bonding may be used on the doped-aluminum bonding pads. This chip can be mounted with conductive epoxy or a gold-silicon preform.

## TLV2352, TLV2352Y LinCMOS™ DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

SLCS011B - MAY 1992 - REVISED MARCH 1999

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>DD</sub> (see Note 1)                               | 8 V                            |

|----------------------------------------------------------------------------|--------------------------------|

| Differential input voltage, V <sub>ID</sub> (see Note 2)                   |                                |

| Input voltage range, V <sub>I</sub>                                        | 0.3 to 8 V                     |

| Output voltage, VO                                                         | 8 V                            |

| Input current, I <sub>1</sub>                                              |                                |

| Output current, I <sub>O</sub>                                             | 20 mA                          |

| Duration of output short-circuit current to GND (see Note 3)               | unlimited                      |

| Continuous total power dissipation                                         | . See Dissipation Rating Table |

| Operating free-air temperature range, T <sub>A</sub> : TLV2352I            | 40°C to 85°C                   |

| TLV2352M                                                                   | –55°C to 125°C                 |

| Storage temperature range, T <sub>stq</sub>                                | 65°C to 150°C                  |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: D, P, and PV |                                |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: FK, JG, and  | U Packages 300°C               |

<sup>†</sup> Stress beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. All voltage values, except differential voltages, are with respect to network ground.

- 2. Differential voltages are at IN+ with respect to IN-.

- 3. Short circuits from outputs to  $V_{\mbox{DD}}$  can cause excessive heating and eventual device destruction.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING<br>FACTOR | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------|--------------------|---------------------------------------|----------------------------------------|

| D       | 725 mW                                                                     | 5.8 mW/°C          | 377 mW                                | _                                      |

| FK      | 1375 mW                                                                    | 11.0 mW/°C         | 715 mW                                | 275 mW                                 |

| JG      | 1050 mW                                                                    | 8.4 mW/°C          | 546 mW                                | 210 mW                                 |

| Р       | 1000 mW                                                                    | 8.0 mW/°C          | 520 mW                                | _                                      |

| PW      | 525 mW                                                                     | 4.2 mW/°C          | 273 mW                                | _                                      |

| U       | 700 mW                                                                     | 5.5 mW/°C          | 370 mW                                | 150 mW                                 |

#### recommended operating conditions

|                                                |                       | MIN | MAX  | UNIT |

|------------------------------------------------|-----------------------|-----|------|------|

| Supply voltage, V <sub>DD</sub>                |                       | 2   | 8    | V    |

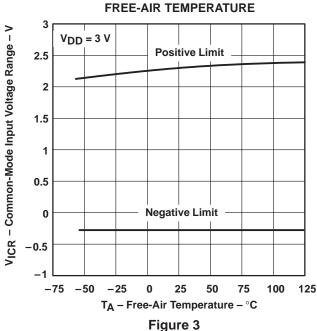

| Common mode input voltage V                    | V <sub>DD</sub> = 3 V | 0   | 1.75 | V    |

| Common-mode input voltage, V <sub>IC</sub>     | V <sub>DD</sub> = 5 V | 0   | 3.75 | V    |

| Operating free-air temperature, T <sub>A</sub> | TLV2352I              | -40 | 85   | °C   |

| Operating free-air temperature, 14             | TLV2352M              | -55 | 125  | )    |

## electrical characteristics at specified free-air temperature

|                 |                          |                           |                         |                  |              |                     | TLV2 | .352I        |                     |     |      |

|-----------------|--------------------------|---------------------------|-------------------------|------------------|--------------|---------------------|------|--------------|---------------------|-----|------|

|                 | PARAMETER                | TEST CON                  | IDITIONS                | T <sub>A</sub> ‡ | V            | <sub>DD</sub> = 3 V | '    | VI           | <sub>DD</sub> = 5 V | '   | UNIT |

|                 |                          |                           |                         |                  | MIN          | TYP                 | MAX  | MIN          | TYP                 | MAX |      |

| V. 0            | Input offeet voltage     | \/.a - \/.a=min           | Soo Note 4              | 25°C             |              | 1                   | 5    |              | 1                   | 5   | mV   |

| VIO             | Input offset voltage     | $V_{IC} = V_{ICRmin}$     | See Note 4              | Full range       |              |                     | 7    |              |                     | 7   | IIIV |

| lio.            | Input offset current     |                           |                         | 25°C             |              | 1                   |      |              | 1                   |     | pА   |

| 110             | input onset current      |                           |                         | 85°C             |              |                     | 1    |              |                     | 1   | nA   |

| lin.            | Input bias current       |                           |                         | 25°C             |              | 5                   |      |              | 5                   |     | pA   |

| ΙΒ              | input bias current       |                           |                         | 85°C             |              |                     | 2    |              |                     | 2   | nA   |

|                 | Common-mode input        |                           |                         | 25°C             | 0 to 2       |                     |      | 0 to 4       |                     |     |      |

| VICR            | voltage range            |                           |                         | Full range       | 0 to<br>1.75 |                     |      | 0 to<br>3.75 |                     |     | V    |

| 1               | High-level output        | V:= - 1 V                 |                         | 25°C             |              | 0.1                 |      |              | 0.1                 |     | nA   |

| ЮН              | current                  | V <sub>ID</sub> = 1 V     |                         | Full range       |              |                     | 1    |              |                     | 1   | μΑ   |

| VOL             | Low-level output         | V <sub>ID</sub> = −1 V,   | I <sub>OL</sub> = 2 mA  | 25°C             |              | 115                 | 300  |              | 150                 | 400 | mV   |

| VOL             | voltage                  | ν <sub>1</sub> D = - τ ν, | IOL = 2 IIIA            | Full range       |              |                     | 600  |              |                     | 700 | IIIV |

| l <sub>OL</sub> | Low-level output current | V <sub>ID</sub> = -1 V,   | V <sub>OL</sub> = 1.5 V | 25°C             | 6            | 16                  |      | 6            | 16                  |     | mA   |

| IDD             | Supply current           | V <sub>ID</sub> = 1 V,    | No load                 | 25°C             |              | 120                 | 250  |              | 140                 | 300 |      |

| IDD             | очрріу сипепі            | ν <sub>ID</sub> = τ ν,    | INO IOAU                | Full range       |              |                     | 350  |              |                     | 400 | μΑ   |

<sup>†</sup> All characteristics are measured with zero common-mode input voltages unless otherwise noted.

NOTE 4: The offset voltage limits given are the maximum values required to drive the output above 4 V with VDD = 5 V, 2 V with VDD = 3 V, or below 400 mV with a 10-k $\Omega$  resistor between the output and V<sub>DD</sub>. They can be verified by applying the limit value to the input and checking for the appropriate output state.

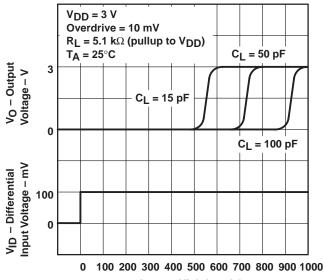

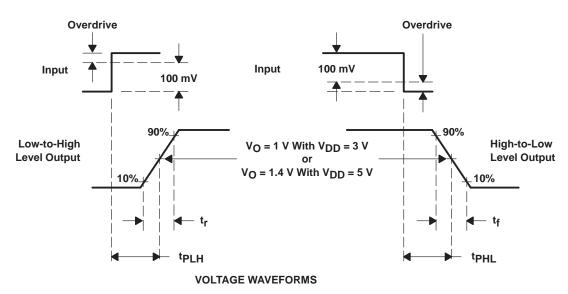

## switching characteristics, $V_{DD} = 3 \text{ V}$ , $T_A = 25^{\circ}\text{C}$

| PARAMETER     |                               | TEST CONDITIONS          |            |                                       |  |     |     | UNIT |

|---------------|-------------------------------|--------------------------|------------|---------------------------------------|--|-----|-----|------|

| PARAMETER     | R TEST CONDITIONS             |                          |            |                                       |  | TYP | MAX | UNIT |

| Response time | $R_L = 5.1 \text{ k}\Omega$ , | C <sub>L</sub> = 15 pF§, | See Note 5 | 100-mV input step with 5-mV overdrive |  | 640 |     | ns   |

<sup>§</sup> C<sub>L</sub> includes probe and jig capacitance.

NOTE 5: The response time specified is the interval between the input step function and the instant when the output crosses VO = 1 V with  $V_{DD} = 3 \text{ V or } V_O = 1.4 \text{ V with } V_{DD} = 5 \text{ V}.$

### switching characteristics, V<sub>DD</sub> = 5 V, T<sub>A</sub> = 25°C

| PARAMETER     |                           | Т                        | UNIT       |                                       |     |     |     |      |

|---------------|---------------------------|--------------------------|------------|---------------------------------------|-----|-----|-----|------|

| PARAMETER     |                           |                          | TEST CON   | BITIONS                               | MIN | TYP | MAX | UNIT |

| Response time | D 5.1 kO                  | C <sub>I</sub> = 15 pF§, | Coo Noto E | 100-mV input step with 5-mV overdrive |     | 650 |     | no   |

| Response time | $KL = 0.1 \text{ K}_{22}$ | C[ = 15 prs,             | See Note 5 | TTL-level input step                  |     | 200 |     | ns   |

<sup>§</sup> C<sub>L</sub> includes probe and jig capacitance.

NOTE 5: The response time specified is the interval between the input step function and the instant when the output crosses VO = 1 V with  $V_{DD} = 3 \text{ V or } V_O = 1.4 \text{ V with } V_{DD} = 5 \text{ V}.$

<sup>‡</sup> Full range is -40°C to 85°C. IMPORTANT: See Parameter Measurement Information.

## electrical characteristics at specified free-air temperature†

|      |                          |                                         |                         |                  |              |                     | TLV2 | 352M         |                     |     |      |

|------|--------------------------|-----------------------------------------|-------------------------|------------------|--------------|---------------------|------|--------------|---------------------|-----|------|

|      | PARAMETER                | TEST COM                                | IDITIONS                | T <sub>A</sub> ‡ | V            | <sub>DD</sub> = 3 V | 1    | V            | <sub>DD</sub> = 5 V | '   | UNIT |

|      |                          |                                         |                         |                  | MIN          | TYP                 | MAX  | MIN          | TYP                 | MAX |      |

| V10  | Input offset voltage     | Via – Vianmin                           | See Note 4              | 25°C             |              | 1                   | 5    |              | 1                   | 5   | mV   |

| VIO  | input onset voltage      | V <sub>IC</sub> = V <sub>ICR</sub> min, | See Note 4              | Full range       |              |                     | 10   |              |                     | 10  | IIIV |

| lio. | Input offset current     |                                         |                         | 25°C             |              | 1                   |      |              | 1                   |     | pА   |

| lio  | input onset current      |                                         |                         | 125°C            |              |                     | 10   |              |                     | 10  | nA   |

| l.s  | Input bias current       |                                         |                         | 25°C             |              | 5                   |      |              | 5                   |     | pА   |

| IB   | input bias current       |                                         |                         | 125°C            |              |                     | 20   |              |                     | 20  | nA   |

|      | Common-mode input        |                                         |                         | 25°C             | 0 to 2       |                     |      | 0 to 4       |                     |     |      |

| VICR | voltage range            |                                         |                         | Full range       | 0 to<br>1.75 |                     |      | 0 to<br>3.75 |                     |     | V    |

| 1    | High-level output        | V 4 V                                   |                         | 25°C             |              | 0.1                 |      |              | 0.1                 |     | nA   |

| ЮН   | current                  | V <sub>ID</sub> = 1 V                   |                         | Full range       |              |                     | 1    |              |                     | 1   | μА   |

| Vai  | Low-level output         | V <sub>ID</sub> = −1 V,                 | I <sub>OL</sub> = 2 mA  | 25°C             |              | 115                 | 300  |              | 150                 | 400 | mV   |

| VOL  | voltage                  | $V_{\text{ID}} = -1 \text{ V},$         | IOC = 2 IIIA            | Full range       |              |                     | 600  |              |                     | 700 | IIIV |

| lOL  | Low-level output current | V <sub>ID</sub> = −1 V,                 | V <sub>OL</sub> = 1.5 V | 25°C             | 6            | 16                  |      | 6            | 16                  |     | mA   |

| la a | Cupply ourrent           | V:= -1 V                                | No load                 | 25°C             |              | 120                 | 250  |              | 140                 | 300 |      |

| IDD  | Supply current           | $V_{ID} = 1 V$ ,                        | INU IUAU                | Full range       |              |                     | 350  |              |                     | 400 | μΑ   |

<sup>†</sup> All characteristics are measured with zero common-mode input voltages unless otherwise noted.

## switching characteristics, V<sub>DD</sub> = 3 V, T<sub>A</sub> = 25°C

| PARAMETER     | т.                                                        | TL        | UNIT                                  |     |     |      |      |

|---------------|-----------------------------------------------------------|-----------|---------------------------------------|-----|-----|------|------|

| PARAMETER     |                                                           | EST COND  | ITIONS                                | MIN | TYP | MAX  | UNIT |

| Response time | $R_L = 5.1 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$ , Se | ee Note 5 | 100-mV input step with 5-mV overdrive |     |     | 1400 | ns   |

<sup>§</sup> C<sub>L</sub> includes probe and jig capacitance.

NOTE 5: The response time specified is the interval between the input step function and the instant when the output crosses  $V_O = 1 \text{ V}$  with  $V_{DD} = 3 \text{ V}$  or  $V_O = 1.4 \text{ V}$  with  $V_{DD} = 5 \text{ V}$ .

## switching characteristics, $V_{DD} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$

| PARAMETER TEST CONDITIONS |                                 |               |            |                                       |     | TLV2352M |      |      |  |  |

|---------------------------|---------------------------------|---------------|------------|---------------------------------------|-----|----------|------|------|--|--|

| PARAMETER                 |                                 |               | TEST CONL  | OTTONS                                | MIN | TYP      | MAX  | UNIT |  |  |

| Response time             | B 51kO (                        | C: 100 pF8    | Saa Nata E | 100-mV input step with 5-mV overdrive |     |          | 1300 | 20   |  |  |

| Response time             | $R_L = 5.1 \text{ k}\Omega$ , ( | CL = 100 prs, | See Note 5 | TTL-level input step                  |     |          | 900  | ns   |  |  |

<sup>§</sup> C<sub>L</sub> includes probe and jig capacitance.

NOTE 5: The response time specified is the interval between the input step function and the instant when the output crosses  $V_O = 1 \text{ V}$  with  $V_{DD} = 3 \text{ V}$  or  $V_O = 1.4 \text{ V}$  with  $V_{DD} = 5 \text{ V}$ .

<sup>‡</sup> Full range is -55°C to 125°C. IMPORTANT: See Parameter Measurement Information.

NOTE 4: The offset voltage limits given are the maximum values required to drive the output above 4 V with V<sub>DD</sub> = 5 V, 2 V with V<sub>DD</sub> = 3 V, or below 400 mV with a 10-kΩ resistor between the output and V<sub>DD</sub>. They can be verified by applying the limit value to the input and checking for the appropriate output state.

## TLV2352, TLV2352Y LinCMOS™ DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

SLCS011B - MAY 1992 - REVISED MARCH 1999

## electrical characteristics at specified free-air temperature, $T_A = 25^{\circ}C^{\dagger}$

|                 |                                 |                        |                         |        |                       | TLV2 | 352Y   |                       |     |    |

|-----------------|---------------------------------|------------------------|-------------------------|--------|-----------------------|------|--------|-----------------------|-----|----|

|                 | PARAMETER                       | TEST CONDITIONS        |                         | V      | V <sub>DD</sub> = 3 V |      |        | V <sub>DD</sub> = 5 V |     |    |

|                 |                                 |                        |                         | MIN    | TYP                   | MAX  | MIN    | TYP                   | MAX |    |

| V <sub>IO</sub> | Input offset voltage            | $V_{IC} = V_{ICR}min,$ | See Note 4              |        | 1                     | 5    |        | 1                     | 5   | mV |

| I <sub>IO</sub> | Input offset current            |                        |                         |        | 1                     |      |        | 1                     |     | pA |

| $I_{IB}$        | Input bias current              |                        |                         |        | 5                     |      |        | 5                     |     | pA |

| VICR            | Common-mode input voltage range |                        |                         | 0 to 2 |                       |      | 0 to 4 |                       |     | V  |

| loh             | High-level output current       | V <sub>ID</sub> = 1 V  |                         |        | 0.1                   |      |        | 0.1                   |     | nA |

| VOL             | Low-level output voltage        | $V_{ID} = -1 V$ ,      | $I_{OL} = 2 \text{ mA}$ |        | 115                   | 300  |        | 150                   | 400 | mV |

| loL             | Low-level output current        | $V_{ID} = -1 V$ ,      | V <sub>OL</sub> = 1.5 V | 6      | 16                    |      | 6      | 16                    |     | mA |

| $I_{DD}$        | Supply current                  | V <sub>ID</sub> = 1 V  | No load                 |        | 120                   | 250  |        | 140                   | 300 | μΑ |

<sup>†</sup> All characteristics are measured with zero common-mode input voltages unless otherwise noted.

NOTE 4: The offset voltage limits given are the maximum values required to drive the output above 4 V with V<sub>DD</sub> = 5 V, 2 V with V<sub>DD</sub> = 3 V, or below 400 mV with a 10-kΩ resistor between the output and V<sub>DD</sub>. They can be verified by applying the limit value to the input and checking for the appropriate output state.

**SUPPLY CURRENT**

#### TYPICAL CHARACTERISTICS

#### LOW-LEVEL OUTPUT VOLTAGE **LOW-LEVEL OUTPUT CURRENT** 1100 $V_{DD} = 3 V$ 990 T<sub>A</sub> = 25°C VOL - Low-Level Output Voltage - mV 880 770 660 550 440 330 220 110 0 0 8 10 12 14 16 I<sub>OL</sub> – Low-Level Output Current – mA Figure 1

## COMMON-MODE INPUT VOLTAGE RANGE vs

#### FREE-AIR TEMPERATURE 190 No Load 180 170 I<sub>DD</sub> - Supply Current - μA 160 $V_{DD} = 5 V$ 150 140 $V_{DD} = 3 V$ 130 120 110 100 90 \_75 - 50 - 25 25 50 75 100 125

Figure 2

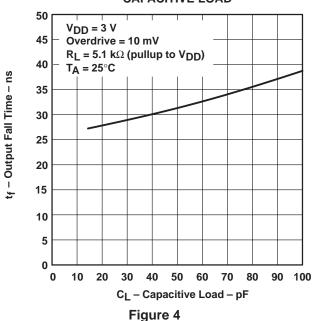

# OUTPUT FALL TIME vs CAPACITIVE LOAD

T<sub>A</sub> - Free-Air Temperature - °C

#### TYPICAL CHARACTERISTICS

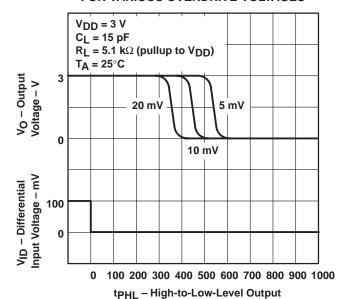

#### HIGH-TO-LOW-LEVEL OUTPUT PROPAGATION DELAY FOR VARIOUS OVERDRIVE VOLTAGES

Figure 5

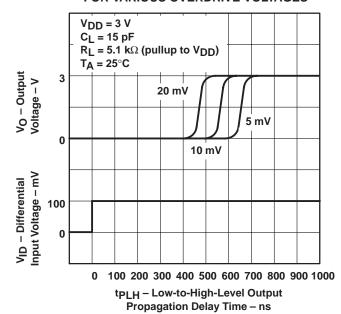

#### LOW-TO-HIGH-LEVEL OUTPUT PROPAGATION DELAY FOR VARIOUS OVERDRIVE VOLTAGES

Propagation Delay Time - ns

Figure 7

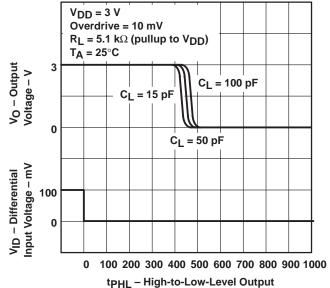

#### **HIGH-TO-LOW-LEVEL OUTPUT** PROPAGATION DELAY FOR VARIOUS CAPACITIVE LOADS

Figure 6

#### LOW-TO-HIGH-LEVEL OUTPUT PROPAGATION DELAY FOR VARIOUS CAPACITIVE LOADS

Propagation Delay Time - ns

tpLH - Low-to-High-Level Output Propagation Delay Time - ns

Figure 8

#### PARAMETER MEASUREMENT INFORMATION

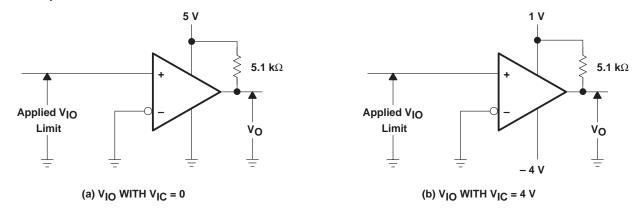

The digital output stage of the TLV2352 can be damaged if it is held in the linear region of the transfer curve. Conventional operational amplifier/comparator testing incorporates the use of a servo loop that is designed to force the device output to a level within this linear region. Since the servo-loop method of testing cannot be used, the following alternatives for measuring parameters such as input offset voltage, common-mode rejection, etc., are offered.

To verify that the input offset voltage falls within the limits specified, the limit value is applied to the input as shown in Figure 9(a). With the noninverting input positive with respect to the inverting input, the output should be high. With the input polarity reversed, the output should be low.

A similar test can be made to verify the input offset voltage at the common-mode extremes. The supply voltages can be slewed as shown in Figure 9(b) for the  $V_{ICR}$  test, rather than changing the input voltages to provide greater accuracy.

Figure 9. Method for Verifying That Input Offset Voltage Is Within Specified Limits

A close approximation of the input offset voltage can be obtained by using a binary search method to vary the differential input voltage while monitoring the output state. When the applied input voltage differential is equal but opposite in polarity to the input offset voltage, the output changes states.

#### PARAMETER MEASUREMENT INFORMATION

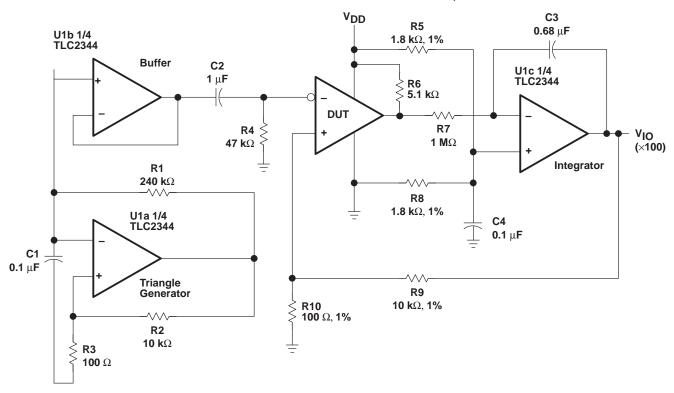

Figure 10 illustrates a practical circuit for direct dc measurement of input offset voltage that does not bias the comparator in the linear region. The circuit consists of a switching-mode servo loop in which U1a generates a triangular waveform of approximately 20-mV amplitude. U1b acts as a buffer with C2 and R4 removing any residual dc offset. The signal is then applied to the inverting input of the comparator under test while the noninverting input is driven by the output of the integrator formed by U1c through the voltage divider formed by R9 and R10. The loop reaches a stable operating point when the output of the comparator under test has a duty cycle of exactly 50%, which can only occur when the incoming triangle wave is sliced symmetrically or when the voltage at the noninverting input exactly equals the input offset voltage.

Voltage dividers R9 and R10 provide a step up of the input offset voltage by a factor of 100 to make measurement easier. The values of R5, R8, R9, and R10 can significantly influence the accuracy of the reading; therefore, it is suggested that their tolerance level be 1% or lower.

Measuring the extremely low values of input current requires isolation from all other sources of leakage current and compensation for the leakage of the test socket and board. With a good picoammeter, the socket and board leakage can be measured with no device in the socket. Subsequently, this open-socket leakage value can be subtracted from the measurement obtained with a device in the socket to obtain the actual input current of the device.

Figure 10. Circuit for Input Offset Voltage Measurement

#### PARAMETER MEASUREMENT INFORMATION

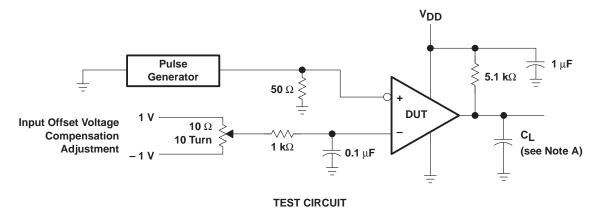

Propagation delay time is defined as the interval between the application of an input step function and the instant when the output crosses  $V_O = 1.4 \text{ V}$  with  $V_{DD} = 3 \text{ V}$  or when the output crosses  $V_O = 1.4 \text{ V}$  with  $V_{DD} = 5 \text{ V}$ . Propagation delay time, low-to-high-level output, is measured from the leading edge of the input pulse while propagation delay time, high-to-low-level output, is measured from the trailing edge of the input pulse. Propagation-delay-time measurement at low input signal levels can be greatly affected by the input offset voltage. The offset voltage should be balanced by the adjustment at the inverting input (as shown in Figure 11) so that the circuit is just at the transition point. Then a low signal, for example 105-mV or 5-mV overdrive, causes the output to change states.

NOTE A: C<sub>L</sub> includes probe and jig capacitance.

Figure 11. Propagation Delay, Rise, and Fall Times Test Circuit and Voltage Waveforms

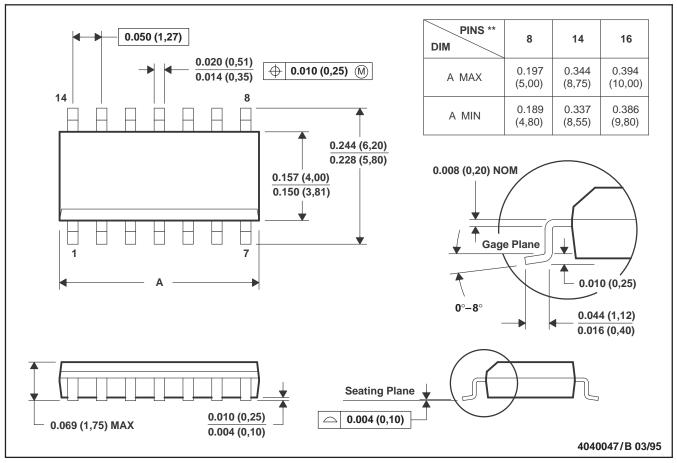

#### **MECHANICAL INFORMATION**

#### D (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### 14 PIN SHOWN

- NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

- D. Four center pins are connected to die mount pad.

- E. Falls within JEDEC MS-012

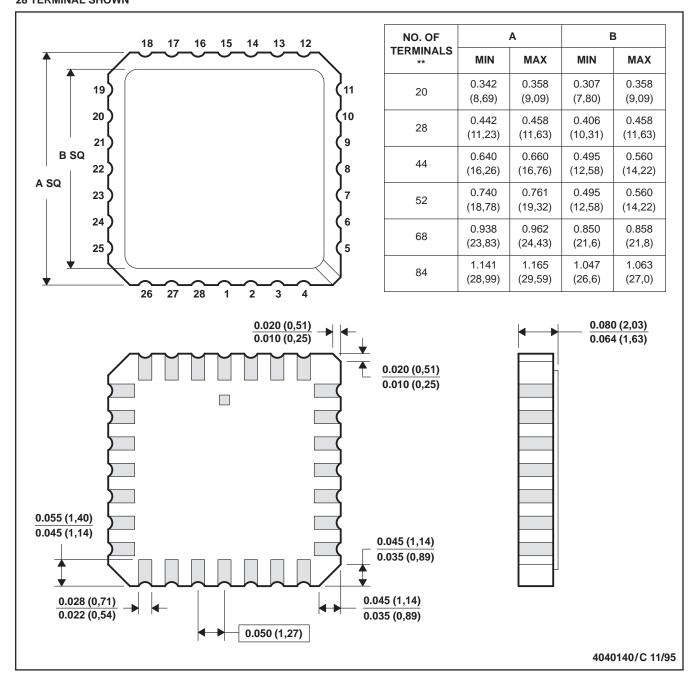

#### **MECHANICAL INFORMATION**

#### FK (S-CQCC-N\*\*)

#### 28 TERMINAL SHOWN

#### LEADLESS CERAMIC CHIP CARRIER

- NOTES: A. All linear dimensions are in inches (millimeters).

- This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a metal lid.

- D. The terminals are gold plated.

- E. Falls within JEDEC MS-004

#### **MECHANICAL INFORMATION**

#### JG (R-GDIP-T8)

#### **CERAMIC DUAL-IN-LINE PACKAGE**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only

- E. Falls within MIL-STD-1835 GDIP1-T8

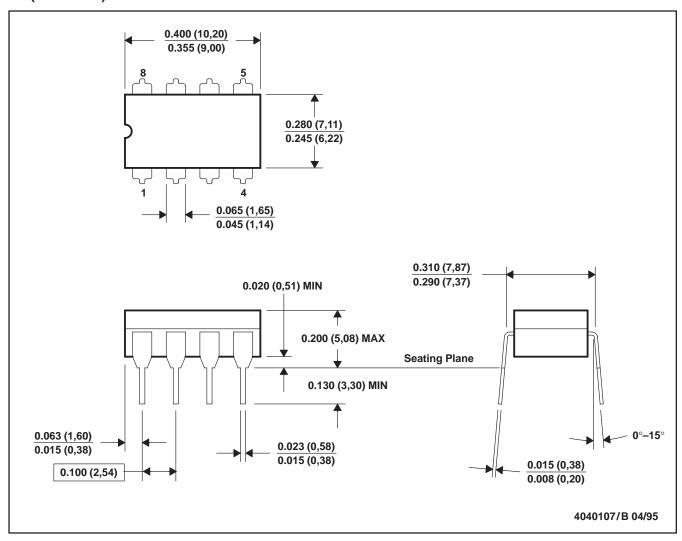

#### **MECHANICAL INFORMATION**

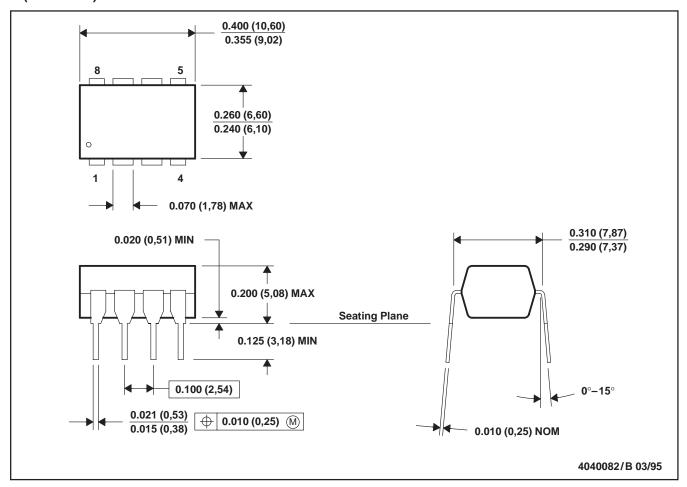

#### P (R-PDIP-T8)

#### PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001

#### **MECHANICAL INFORMATION**

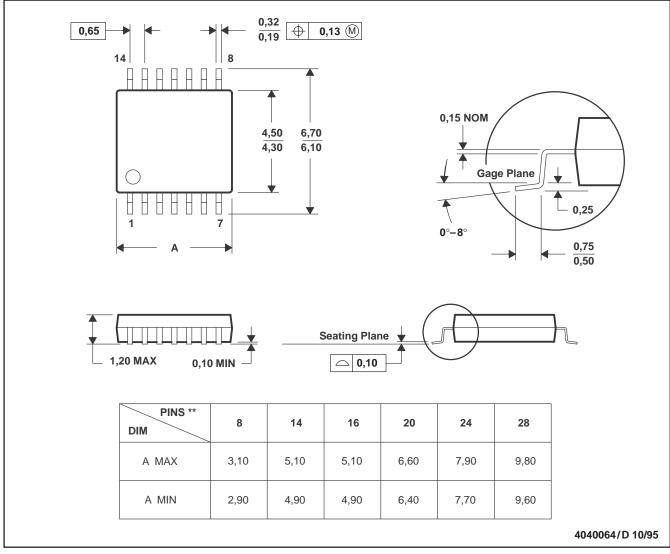

#### PW (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### 14 PIN SHOWN

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

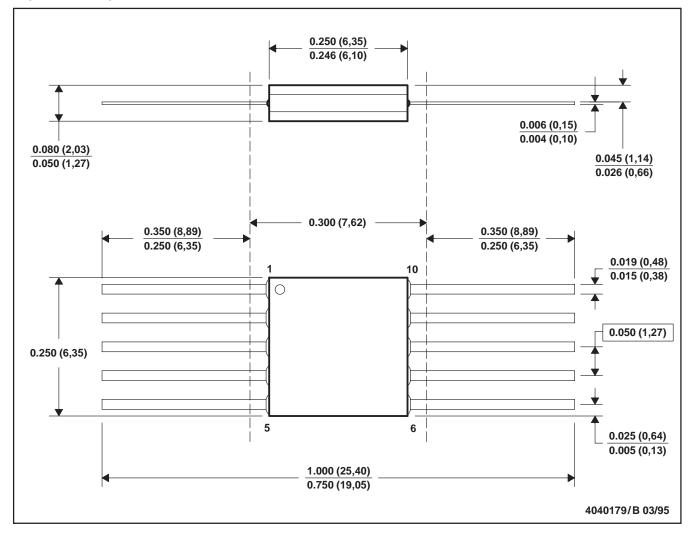

#### **MECHANICAL INFORMATION**

#### U (S-GDFP-F10)

#### **CERAMIC DUAL FLATPACK**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only.

- E. Falls within MIL STD 1835 GDFP1-F10 and JEDEC MO-092AA

i.com 22-Feb-2005

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup>              |

|------------------|-----------------------|-----------------|--------------------|------|----------------|-------------------------|------------------|-------------------------------------------|

| 5962-9688101Q2A  | ACTIVE                | LCCC            | FK                 | 20   | 1              | None                    | POST-PLATE       | Level-NC-NC-NC                            |

| 5962-9688101QHA  | ACTIVE                | CFP             | U                  | 10   | 1              | None                    | A42 SNPB         | Level-NC-NC-NC                            |

| 5962-9688101QPA  | ACTIVE                | CDIP            | JG                 | 8    | 1              | None                    | A42 SNPB         | Level-NC-NC-NC                            |

| TLV2352ID        | ACTIVE                | SOIC            | D                  | 8    | 75             | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-2-260C-1YEAR/<br>Level-1-220C-UNLIM |

| TLV2352IDR       | ACTIVE                | SOIC            | D                  | 8    | 2500           | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-2-260C-1YEAR/<br>Level-1-220C-UNLIM |

| TLV2352IP        | ACTIVE                | PDIP            | Р                  | 8    | 50             | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-NC-NC-NC                            |

| TLV2352IPW       | ACTIVE                | TSSOP           | PW                 | 8    | 150            | None                    | CU NIPDAU        | Level-1-220C-UNLIM                        |

| TLV2352IPWLE     | OBSOLETE              | TSSOP           | PW                 | 8    |                | None                    | Call TI          | Call TI                                   |

| TLV2352IPWR      | ACTIVE                | TSSOP           | PW                 | 8    | 2000           | None                    | CU NIPDAU        | Level-1-220C-UNLIM                        |

| TLV2352MFKB      | ACTIVE                | LCCC            | FK                 | 20   | 1              | None                    | POST-PLATE       | Level-NC-NC-NC                            |

| TLV2352MJG       | ACTIVE                | CDIP            | JG                 | 8    | 1              | None                    | A42 SNPB         | Level-NC-NC-NC                            |

| TLV2352MJGB      | ACTIVE                | CDIP            | JG                 | 8    | 1              | None                    | A42 SNPB         | Level-NC-NC-NC                            |

| TLV2352MUB       | ACTIVE                | CFP             | U                  | 10   | 1              | None                    | A42 SNPB         | Level-NC-NC-NC                            |

<sup>&</sup>lt;sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - May not be currently available - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

None: Not yet available Lead (Pb-Free).

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean "Pb-Free" and in addition, uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated

## Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from:

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com