# QPP-015 120W, 869-894MHz Class AB Power Stage

## QuikPAC Module Data

#### **General description:**

The **QPP-015 QuikPAC<sup>TM</sup>** RF power module is an impedance matched Class AB amplifier stage designed for use in the output stage of linear RF power amplifiers for cellular base stations. The power transistor is fabricated using Xemod's advanced design LDMOS process. The gate terminal is connected directly to the control voltage pin, allowing direct control of the bias. The user must supply the proper value of V<sub>GS</sub> to set the desired quiescent current.

#### Features:

Single Polarity Operation Matched for 50 Ω RF interfaces XeMOS FET Technology Stable Performance QuikPAC System Compatible QuikClip or Flange Mounting

## **Standard Operating Conditions**

| Parameter                                              | Symbol          | Min  | Nom  | Max  | Units |

|--------------------------------------------------------|-----------------|------|------|------|-------|

| Frequency Range                                        | F               | 869  |      | 894  | MHz   |

| Supply (Drain) Voltage                                 | VD              | 26.0 | 28.0 | 32.0 | VDC   |

| Bias (Gate) Voltage                                    | V <sub>G</sub>  | 3.0  | 3.5  | 5.0  | VDC   |

| Bias (Gate) Current, Average                           | I <sub>G</sub>  |      | E WW | 2.0  | mA    |

| RF Source & Load Impedance                             | Ω               |      | 50   |      | Ohms  |

| Load Impedance for Stable Operation (All Phases)       | VSWR            |      |      | 10:1 |       |

| Operating Baseplate Temperature                        | T <sub>OP</sub> | -20  |      | +90  | °C    |

| Output Device Thermal Resistance, Channel to Baseplate | Θјс             |      | 0.8  |      | °C/W  |

### **Maximum Ratings**

| Parameter                                              | Symbol           | Value       | Units |

|--------------------------------------------------------|------------------|-------------|-------|

| Supply (Drain) Voltage                                 | V <sub>DD</sub>  | 35          | VDC   |

| Control (Gate) Voltage, V <sub>DD</sub> = 0 VDC        | V <sub>G</sub>   | 15          | VDC   |

| Input RF Power                                         | P <sub>IN</sub>  | 10          | W     |

| Load Impedance for continuous operation without damage | VSWR             | 3:1         |       |

| Output Device Channel Temperature                      |                  | 200         | °C    |

| Lead Soldering Temperature                             |                  | +190        | °C    |

| Storage Temperature                                    | T <sub>STG</sub> | -65 to +150 | °C    |

### Performance at 28VDC & 25°C

| Parameter                                                            | Symbol            | Min         | Nom   | Max    | Units |

|----------------------------------------------------------------------|-------------------|-------------|-------|--------|-------|

| Supply (Drain) Voltage                                               | V <sub>D1,2</sub> | 27.5        | 28.0  | 28.5   | VDC   |

| Quiescent Current (total) (1)                                        | I <sub>DQ</sub>   | 900         | 1,000 | 1,100  | mA    |

| Power Output at 1 dB Compression (single tone)                       | P <sub>-1</sub>   | 120         | 130   | . 0750 | W     |

| Gain at 24W PEP (two tone)                                           | G                 | <b>13.0</b> | 14.0  |        | dB    |

| Gain Variation over frequency at 24W Output (two tone)               | ΔG                | LIG.V.      | 0.3   | 0.5    | dB    |

| Input Return Loss (50 $\Omega$ Ref) at 24W PEP (two tone)            | IRL               | 12.0        | 14.0  |        | dB    |

| Drain Efficiency at 120W Pout (single tone)                          | η                 | 43          | 45    |        | %     |

| Drain Efficiency at 120W PEP (two tone)                              | η                 | 32          | 35    |        | %     |

| 3 <sup>rd</sup> Order IMD Product (2 tone at 120W PEP;1 MHz spacing) |                   |             | -30   | -28    | dBc   |

XEMOD RESERVES THE RIGHT TO MAKE CHANGES TO THIS SPECIFICATION WITHOUT FURTHER NOTICE. BEFORE THE PRODUCT DESCRIBED HERE IS WRITTEN INTO SPECIFICATIONS OR USED IN CRITICAL APPLICATIONS, THE PERFORMANCE CHARACTERISTICS SHOULD BE VERIFIED BY CONTACTING XEMOD.

### Performance at 28VDC & 25°C (continued)

| Parameter                                                       | Symbol     | Min | Nom | Max | Units   |

|-----------------------------------------------------------------|------------|-----|-----|-----|---------|

| IMD Variation – 100 kHz to 25 MHz tone spacing                  |            |     | 1.0 | 2.0 | dB      |

| 2 <sup>nd</sup> Harmonic at 120W Pout(single tone)              |            |     |     |     | dBc     |

| 3 <sup>rd</sup> Harmonic at 120W P <sub>out</sub> (single tone) |            |     |     |     | dBc     |

| Group (Signal) Delay                                            | $\tau_{d}$ |     | 4.0 |     | ns      |

| Transmission Phase Flatness                                     |            |     | 0.5 |     | degrees |

| CDMA ACPR at 24W Pout avg                                       |            |     | 46  |     | dB      |

#### Notes:

This QuikPAC module requires an externally supplied gate voltage ( $V_{GS}$ ) on each gate lead (pins 1 and 5) to set the operating point (quiescent current-  $I_{DQ}$ ) of the power transistors.  $V_{GS}$  may be safely set to any voltage in the range listed in the table. This permits a wide range of quiescent current to be used. Since the operating characteristics of the module will vary as  $I_{DQ}$  changes, the bias setting will depend on the application. The data provided in the Performance section of this data sheet was obtained with  $I_{DQ}$  set to a value within the range listed (a nominal value ±10%). This particular value was chosen to optimize gain, IMD performance, and efficiency simultaneously.

Gate voltage must be applied coincident with or after application of the drain voltage to prevent potentially destructive oscillations. Bias voltages should never be applied to a module unless it is terminated on both input and output.

The  $V_{GS}$  corresponding to a specific  $I_{DQ}$  will vary from module to module and may vary between the two sides of a dual RF module by as much as ±0.10 volts. This is due to the normal die-to-die variation in threshold voltage of LDMOS transistors.

Since the gate bias of an LDMOS transistor changes with device temperature, it may be necessary to use a  $V_{GS}$  supply with thermal compensation if operation over a wide temperature range is required.

Internal RF decoupling is included on all bias leads. No additional bypass elements are required, however some applications may require energy storage on the drain leads to accommodate time-varying waveforms.

The RF leads are internally protected against DC voltages up to 100V. Care should be taken to avoid video transients that may damage the active devices.

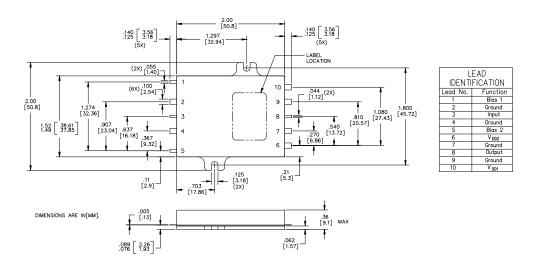

#### **Package Styles**

This model is available in both B2 (H10537) and B2F (H10894) package styles. Style B2F is shown for reference. Please see the applicable outline drawing for specific dimensions.