# *MVIDIA*

## RIVA 128™ 128-BIT 3D MULTIMEDIA ACCELERATOR

#### **DESCRIPTION**

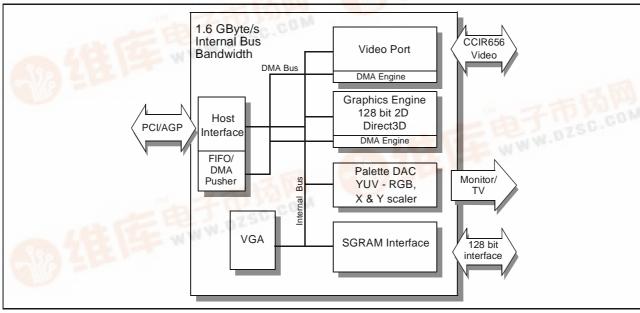

The RIVA 128<sup>™</sup> is the first 128-bit 3D Multimedia Accelerator to offer unparalleled 2D and 3D performance, meeting all the requirements of the mainstream PC graphics market and Microsoft's PC'97. The RIVA 128 introduces the most advanced Direct3D<sup>™</sup> acceleration solution and also delivers leadership VGA, 2D and Video performance, enabling a range of applications from 3D games through to DVD, Intercast<sup>™</sup> and video conferencing.

## **KEY FEATURES**

- Fast 32-bit VGA/SVGA

- High performance 128-bit 2D/GUI/DirectDraw Acceleration

- Interactive, Photorealistic Direct3D Acceleration with advanced effects

- Massive 1.6Gbytes/s, 100MHz 128-bit wide frame buffer interface

- Video Acceleration for DirectDraw/DirectVideo, MPEG-1/2 and Indeo<sup>®</sup>

- Planar 4:2:0 and packed 4:2:2 Color Space Conversion

- X and Y smooth up and down scaling

- 230MHz Palette-DAC supporting up to 1600x1200@75Hz

- · NTSC and PAL output with flicker-filter

- Multi-function Video Port and serial interface

- Bus mastering DMA 66MHz Accelerated Graphics Port (AGP) 1.0 Interface

- Bus mastering DMA PCI 2.1 interface

- 0.35 micron 5LM CMOS

- 300 PBGA

#### **BLOCK DIAGRAM**

## **TABLE OF CONTENTS**

| 1 | REV   | ISION HISTORY                                        | 4  |  |  |  |  |  |  |  |  |

|---|-------|------------------------------------------------------|----|--|--|--|--|--|--|--|--|

| 1 | RIVA  | A 128 300PBGA DEVICE PINOUT                          | 5  |  |  |  |  |  |  |  |  |

| 2 | PIN   | DESCRIPTIONS                                         | 6  |  |  |  |  |  |  |  |  |

|   | 2.1   | ACCELERATED GRAPHICS PORT (AGP) INTERFACE            |    |  |  |  |  |  |  |  |  |

|   | 2.2   | PCI 2.1 LOCAL BUS INTERFACE                          | 6  |  |  |  |  |  |  |  |  |

|   | 2.3   | SGRAM FRAMEBUFFER INTERFACE                          | 8  |  |  |  |  |  |  |  |  |

|   | 2.4   | VIDEO PORT                                           | 8  |  |  |  |  |  |  |  |  |

|   | 2.5   | DEVICE ENABLE SIGNALS                                | 9  |  |  |  |  |  |  |  |  |

|   | 2.6   | DISPLAY INTERFACE                                    | 9  |  |  |  |  |  |  |  |  |

|   | 2.7   | VIDEO DAC AND PLL ANALOG SIGNALS                     | 9  |  |  |  |  |  |  |  |  |

|   | 2.8   | POWER SUPPLY                                         | 9  |  |  |  |  |  |  |  |  |

|   | 2.9   | TEST                                                 | 10 |  |  |  |  |  |  |  |  |

| 3 | OVE   | RVIEW OF THE RIVA 128                                | 11 |  |  |  |  |  |  |  |  |

| • | 3.1   | BALANCED PC SYSTEM                                   |    |  |  |  |  |  |  |  |  |

|   | 3.2   | HOST INTERFACE                                       |    |  |  |  |  |  |  |  |  |

|   | 3.3   | 2D ACCELERATION                                      |    |  |  |  |  |  |  |  |  |

|   | 3.4   | 3D ENGINE                                            | 12 |  |  |  |  |  |  |  |  |

|   | 3.5   | VIDEO PROCESSOR                                      | 12 |  |  |  |  |  |  |  |  |

|   | 3.6   | VIDEO PORT                                           | 13 |  |  |  |  |  |  |  |  |

|   | 3.7   | DIRECT RGB OUTPUT TO LOW COST PAL/NTSC ENCODER       |    |  |  |  |  |  |  |  |  |

|   | 3.8   | SUPPORT FOR STANDARDS                                |    |  |  |  |  |  |  |  |  |

|   | 3.9   | RESOLUTIONS SUPPORTED                                | 13 |  |  |  |  |  |  |  |  |

|   | 3.10  | CUSTOMER EVALUATION KIT                              | 14 |  |  |  |  |  |  |  |  |

|   | 3.11  | TURNKEY MANUFACTURING PACKAGE                        | 14 |  |  |  |  |  |  |  |  |

| 4 | ACC   | ELERATED GRAPHICS PORT (AGP) INTERFACE               | 15 |  |  |  |  |  |  |  |  |

|   | 4.1   | RIVA 128 AGP INTERFACE                               | 16 |  |  |  |  |  |  |  |  |

|   | 4.2   | AGP BUS TRANSACTIONS                                 | 16 |  |  |  |  |  |  |  |  |

| 5 | PCI : | PCI 2.1 LOCAL BUS INTERFACE                          |    |  |  |  |  |  |  |  |  |

|   | 5.1   | RIVA 128 PCI INTERFACE                               | 22 |  |  |  |  |  |  |  |  |

|   | 5.2   | PCI TIMING SPECIFICATION                             | 23 |  |  |  |  |  |  |  |  |

| 6 | SGR   | AM FRAMEBUFFER INTERFACE                             | 29 |  |  |  |  |  |  |  |  |

|   | 6.1   | SGRAM INITIALIZATION                                 | 31 |  |  |  |  |  |  |  |  |

|   | 6.2   | SGRAM MODE REGISTER                                  |    |  |  |  |  |  |  |  |  |

|   | 6.3   | LAYOUT OF FRAMEBUFFER CLOCK SIGNALS                  | 32 |  |  |  |  |  |  |  |  |

|   | 6.4   | SGRAM INTERFACE TIMING SPECIFICATION                 |    |  |  |  |  |  |  |  |  |

| 7 | VIDE  | O PLAYBACK ARCHITECTURE                              | 37 |  |  |  |  |  |  |  |  |

|   | 7.1   | VIDEO SCALER PIPELINE                                | 38 |  |  |  |  |  |  |  |  |

| 8 | VIDE  | O PORT                                               | 40 |  |  |  |  |  |  |  |  |

| - | 8.1   | VIDEO INTERFACE PORT FEATURES                        | 40 |  |  |  |  |  |  |  |  |

|   | 8.2   | BI-DIRECTIONAL MEDIA PORT POLLING COMMANDS USING MPC | 41 |  |  |  |  |  |  |  |  |

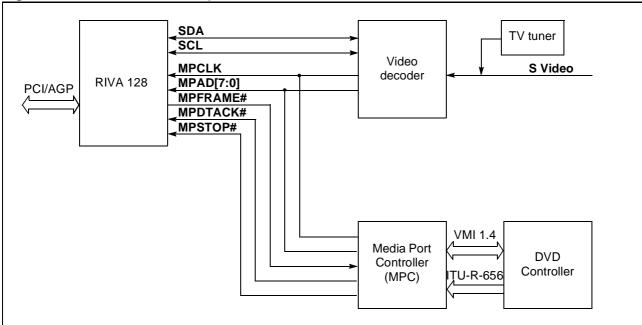

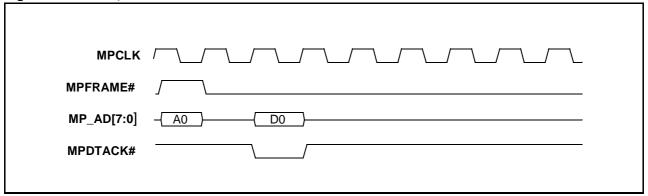

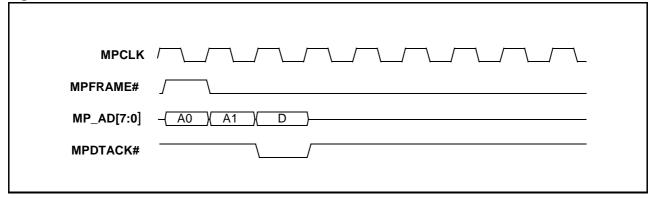

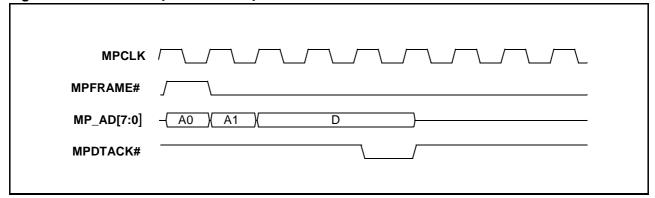

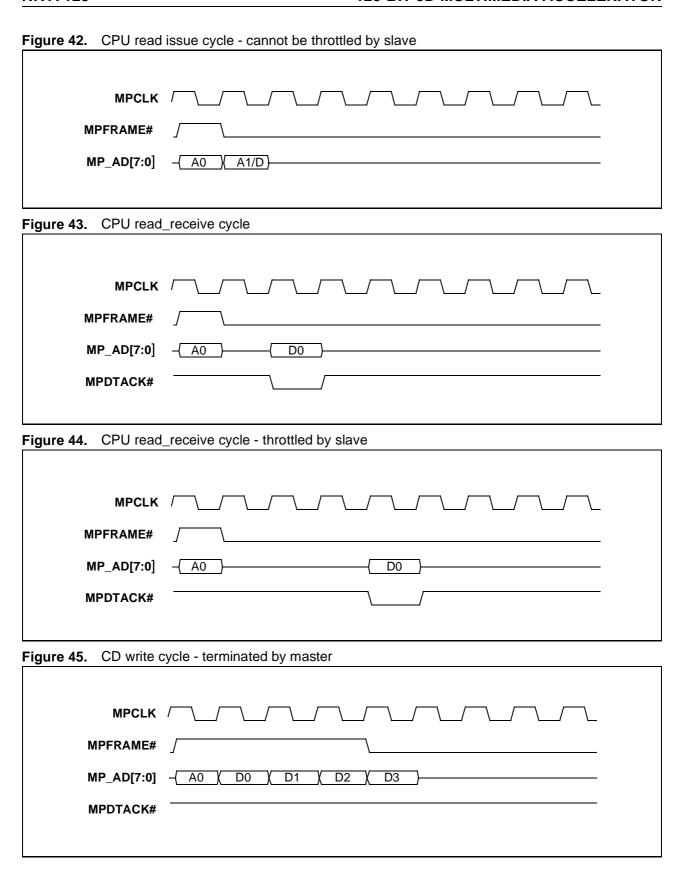

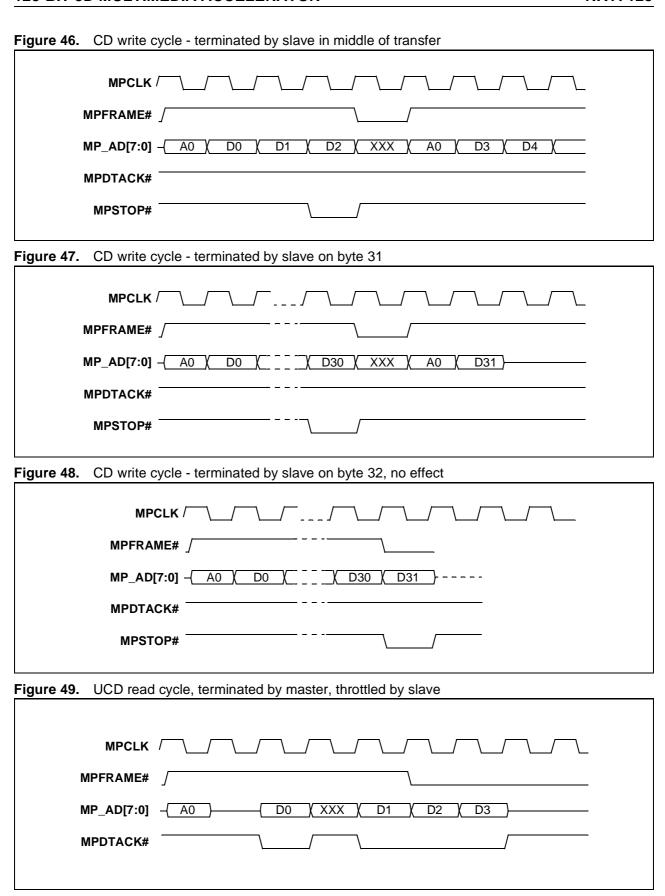

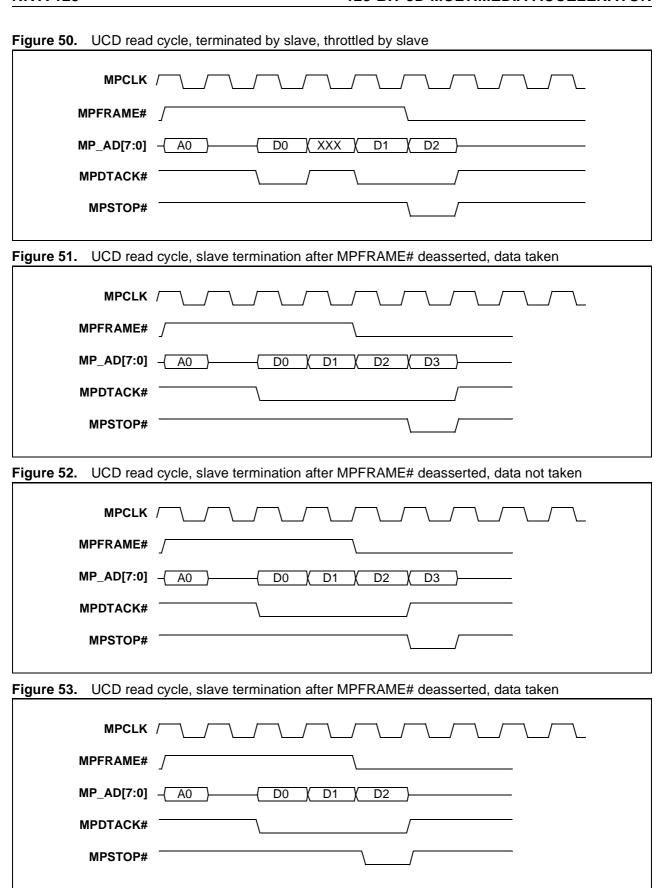

|   | 8.3   | TIMING DIAGRAMS                                      | 42 |  |  |  |  |  |  |  |  |

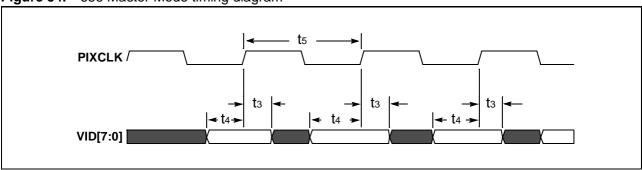

|   | 8.4   | 656 MASTER MODE                                      | 46 |  |  |  |  |  |  |  |  |

|   | 8.5   | VBI HANDLING IN THE VIDEO PORT                       | 47 |  |  |  |  |  |  |  |  |

|   | 8.6   | SCALING IN THE VIDEO PORT                            | 47 |  |  |  |  |  |  |  |  |

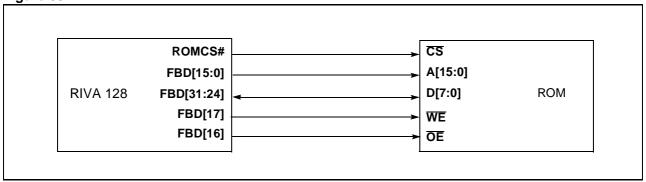

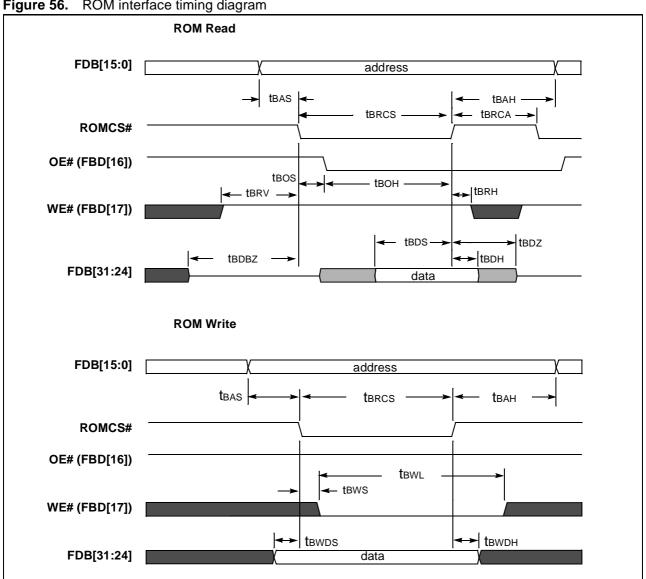

| 9 |       | OT ROM INTERFACE                                     | 48 |  |  |  |  |  |  |  |  |

| - |       |                                                      |    |  |  |  |  |  |  |  |  |

## 128-BIT 3D MULTIMEDIA ACCELERATOR

| 10 | POWER-ON RESET CONFIGURATION                          | 50 |

|----|-------------------------------------------------------|----|

| 11 | DISPLAY INTERFACE                                     | 52 |

|    | 11.1 PALETTE-DAC                                      |    |

|    | 11.2 PIXEL MODES SUPPORTED                            | 52 |

|    | 11.3 HARDWARE CURSOR                                  |    |

|    | 11.4 I2C INTERFACE                                    |    |

|    | 11.5 ANALOG INTERFACE                                 |    |

|    | 11.6 TV OUTPUT SUPPORT                                |    |

| 12 | IN-CIRCUIT BOARD TESTING                              | 58 |

|    | 12.1 TEST MODES                                       |    |

|    | 12.2 CHECKSUM TEST                                    | 58 |

| 13 | ELECTRICAL SPECIFICATIONS                             | 59 |

|    | 13.1 ABSOLUTE MAXIMUM RATINGS                         | 59 |

|    | 13.2 OPERATING CONDITIONS                             | 59 |

|    | 13.3 DC SPECIFICATIONS                                | 59 |

|    | 13.4 ELECTRICAL SPECIFICATIONS                        | 60 |

|    | 13.5 DAC CHARACTERISTICS                              |    |

|    | 13.6 FREQUENCY SYNTHESIS CHARACTERISTICS              | 61 |

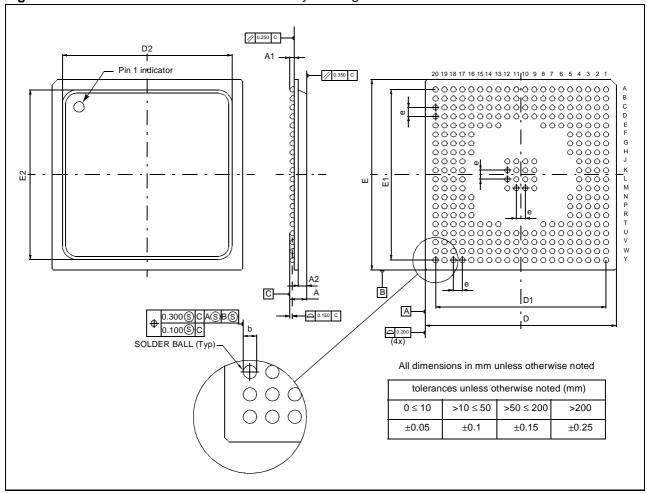

| 14 | PACKAGE DIMENSION SPECIFICATION                       | 62 |

|    | 14.1 300 PIN BALL GRID ARRAY PACKAGE                  | 62 |

| 15 | REFERENCES                                            | 63 |

| 16 | ORDERING INFORMATION                                  | 63 |

|    | APPENDIX                                              | 64 |

| Α  | PCI CONFIGURATION REGISTERS                           | 64 |

|    | A.1 REGISTER DESCRIPTIONS FOR PCI CONFIGURATION SPACE | 64 |

## 1 REVISION HISTORY

| Date      | Section, page | Description of change                                                       |

|-----------|---------------|-----------------------------------------------------------------------------|

| 15 Jul 97 | 6, page 28    | Update of SGRAM framebuffer interface configuration diagrams.               |

| 28 Aug 97 | 13.5, page 59 | Change of DAC specification from 206MHz to 230MHz max. operating frequency. |

| 29 Aug 97 | 6.3, page 31  | Update to recommendation for connection of FBCLK2 and FBCLKB pins.          |

| 4 Sep 97  | 10, page 49   | Update to RAM Type Power-On Reset configuration bits.                       |

| 15 Sep 97 | 13, page 58   | Temperature specification TC now based on case, not ambient temperature.    |

| 15 Sep 97 | 13, page 58   | Change to Power Supply voltage VDD specification.                           |

| 17 Sep 97 | 1, page 5     | Change to Video Port pin names.                                             |

| 17 Sep 97 | 2, page 6     | Change to Video Port pin descriptions.                                      |

| 17 Sep 97 | 8, page 39    | Updates to Video Port section.                                              |

| 18 Sep 97 | 11.6, page 55 | Change to capacitor value in TV output implementation schematic.            |

| 18 Sep 97 | 13.3, page 58 | Change to power dissipation specification.                                  |

| 25 Sep 97 | 4.2, page 16  | Removal of AGP flow control description.                                    |

| 25 Sep 97 | 11.4, page 53 | Updates to Serial Port description.                                         |

## 1 RIVA 128 300PBGA DEVICE PINOUT

| 20 | FBD[57]  | FBD[59]  | FBD[61]  | FBD[63]  | FBD[38] | FBD[36]  | FBD[32]  | FBDQM[13]   | FBD[104] | FBD[106]            | FBD[108] | FBD[110] | FBD[120] | FBD[122] | FBD[124] | FBD[126]       | VIDHSYNC       | ROMCS#      | PCIAD[5]        | PCIAD[1]             |

|----|----------|----------|----------|----------|---------|----------|----------|-------------|----------|---------------------|----------|----------|----------|----------|----------|----------------|----------------|-------------|-----------------|----------------------|

| 19 | FBD[56]  | FBD[58]  | FBD[60]  | FBD[62]  | FBD[39] | FBD[37]  | FBD[33]  | FBDQM[15]   | FBD[105] | FBD[107]            | FBD[109] | FBD[111] | FBD[121] | FBD[123] | FBD[125] | FBD[127]       | VIDVSYNC       | TESTMODE    | PCIAD[7]        | PCIAD[3]             |

| 18 | FBD[47]  | FBD[46]  | FBD[53]  | FBD[51]  | FBD[50] | FBD[49]  | FBD[34]  | FBDQM[14]   | FBD[119] | FBD[117]            | FBD[115] | FBD[113] | FBD[103] | FBD[101] | FBD[99]  | FBD[97]        | FBD[96]        | PCIAD[2] T  | PCIAD[0]        | AGPAD-<br>STBO∗      |

| 17 | FBD[45]  | FBD[44]  | FBD[54]  | FBD[52]  | VDD     | FBD[48]  | FBD[35]  | FBDQM[12] F | FBD[118] | FBD[116]            | FBD[114] | FBD[112] | FBD[102] | FBD[100] | FBD[98]  | VDD            | PCICBE#[0]     | PCIAD[6]    | PCIAD[4]        | PCIAD[8]             |

| 16 | FBD[43]  | FBD[42]  | FBD[55]  | VDD      | VDD     | VDD      | VDD      | N N N       |          |                     |          |          | S        | VDD      | S        | HOST.<br>CLAMP | ноѕтурр        | PCIAD[11]   | PCIAD[9]        | PCIAD[10]            |

| 15 | FBD[41]  | FBD[40]  | FBDQM[4] | FBDQM[6] | VDD     |          |          | '           |          |                     |          |          |          |          |          | НОЅТУББ        | PCIPAR         | PCIAD[15]   | PCIAD[13]       | PCIAD[12]            |

| 14 | FBDQM[5] | FBDQM[7] | FBA[10]* | FBCS1    | VDD     |          |          |             |          |                     |          |          |          |          |          | HOST-<br>CLAMP | PCITRDY#       | PCISTOP#    | PCICBE#[1]      | PCIAD[14]            |

| 13 | FBA[8]   | FBCLK1   | FBRAS#   | FBCS0    | FBCKE*  |          |          |             |          |                     |          |          |          |          |          | НОЅТУЪЪ        | PCIAD[16]      | CIFRAME#    | PCIIRDY# F      | PCI-<br>DEVSEL#      |

| 12 | FBA[6]   | FBA[7]   | FBWE#    | FBCAS#   |         |          |          |             | GND      | GND                 | GND      | GND      |          |          |          |                | PCIAD[20]      | PCIAD[18] P | PCIAD[17]       | ·CICBE#[2]           |

| 11 | FBA[4]   | FBA[5]   | FBDQM[1] | FBDQM[3] |         |          |          |             | GND      | GND                 | GND      | GND      |          |          |          |                | PCICBE#[3]     | PCIAD[22]   | PCIAD[21]       | PCIAD[19] PCICBE#[2] |

| 10 | FBA[2]   | FBA[3]   | FBD[9]   | FBD[8]   |         |          |          |             | GND      | GND                 | GND      | GND      |          |          |          |                | PCIAD[26]      | PCIAD[24]   | AGPAD-<br>STB1* | PCIAD[23]            |

| 6  | FBA[0]   | FBA[1]   | FBD[11]  | FBD[10]  |         |          |          |             | GND      | GND                 | GND      | GND      |          |          |          |                | PCIAD[30]      | PCIAD[28]   | PCIAD[27]       | PCIAD[25]            |

| 8  | FBDQM[2] | FBA[9]   | FBD[13]  | FBD[12]  | VDD     |          |          |             |          |                     |          |          |          |          |          | HOST-<br>CLAMP | AGPST[1]       | AGPPIPE#    | PCIAD[31]       | PCIAD[29]            |

| 7  | FBD[23]  | FBDQM[0] | FBD[15]  | FBD[14]  | VDD     |          |          |             |          |                     |          |          |          |          |          | HOSTVDD        | PCIRST#        | PCIGNT#     | AGPST[2]        | PCIIDSEL/<br>AGPRBF# |

| 9  | FBD[21]  | FBD[22]  | FBD[25]  | FBD[24]  | VDD     |          |          |             |          |                     |          |          |          |          |          | HOSTVDD        | XTALOUT        | PCIINTA#    | PCIREQ#         | AGPST[0]             |

| 2  | FBD[19]  | FBD[20]  | FBD[26]  | VDD      | S       | VDD      | MPCLAMP  | VDD         |          |                     |          |          | S        | VDD      | NIC      | NIC            | HOST.<br>CLAMP | VREF        | PLLVDD          | PCICLK               |

| 4  | FBD[17]  | FBD[18]  | FBD[27]  | FBD[30]  | VDD     | FBCLKFB  | MP_AD[4] | MP_AD[3]    | MP_AD[0] | FBDQM[11]           | FBD[73]  | FBD[75]  | FBD[77]  | FBD[79]  | FBD[89]  | VDD            | FBD[91]        | DACVDD      | COMP            | XTALIN               |

| 3  | FBD[7]   | FBD[16]  | FBD[28]  | FBD[29]  | FBD[31] | SDA      | MP_AD[5] | MPCLK       | MP_AD[1] | FBDQM[10] FBDQM[11] | FBD[72]  | FBD[74]  | FBD[76]  | FBD[78]  | FBD[88]  | [06]QBJ        | FBD[92]        | RED         | BLUE            | RSET                 |

| 2  | FBD[6]   | FBD[5]   | FBD[2]   | FBD[0]   | FBCLK2  | NIC      | MP_AD[7] | MPSTOP#     | MPDTACK# | FBD[87]             | FBD[85]  | FBD[83]  | FBD[81]  | FBD[71]  | [69]GBJ  | FBD[67]        | FBD[65]        | [56]QBJ     | FBD[94]         | GND                  |

| -  | FBD[4]   | FBD[3]   | FBD[1]   | FBCLK0   | SCL     | MP_AD[6] | MPFRAME# | MP_AD[2]    | FBDQM[8] | FBDQM[9]            | FBD[86]  | FBD[84]  | FBD[82]  | FBD[80]  | FBD[70]  | FBD[68]        | FBD[66]        | FBD[64]     | FBD[93]         | GREEN                |

|    | 4        | m        | ()       |          | ш       | ш        | C        | т           | _        | Y                   | -        | 5        | 7        | Δ.       | α-       | _              | _              | >           | >               |                      |

## NOTES

- 1 NIC = No Internal Connection. Do not connect to these pins.

- 2 VDD=3.3V

- \* Signals denoted with an asterisk are defined for future expansion. See Pin Descriptions, Section 2, page 6 for details.

## 2 PIN DESCRIPTIONS

## 2.1 ACCELERATED GRAPHICS PORT (AGP) INTERFACE

| Signal                    | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|---------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AGPST[2:0]                | I   | AGP status bus providing information from the arbiter to the RIVA 128 on what it may do.  AGPST[2:0] only have meaning to the RIVA 128 when PCIGNT# is asserted. When  PCIGNT# is de-asserted these signals have no meaning and must be ignored.                                                                                                                                                                      |  |  |  |  |  |  |

|                           |     | 000 Indicates that previously requested low priority read or flush data is being returned to the RIVA 128.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                           |     | 001 Indicates that previously requested high priority read data is being returned to the RIVA 128.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                           |     | 010 Indicates that the RIVA 128 is to provide low priority write data for a previous enqueued write command.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                           |     | 011 Indicates that the RIVA 128 is to provide high priority write data for a previous enqueued write command.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                           |     | 100 Reserved                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                           |     | 101 Reserved                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                           |     | 110 Reserved                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                           |     | Indicates that the RIVA 128 has been given permission to start a bus transaction. The RIVA 128 may enqueue AGP requests by asserting AGPPIPE# or start a PCI transaction by asserting PCIFRAME#. AGPST[2:0] are always an output from the Core Logic (AGP chipset) and an input to the RIVA 128.                                                                                                                      |  |  |  |  |  |  |

| AGPRBF#                   | 0   | Read Buffer Full indicates when the RIVA 128 is ready to accept previously requested low priority read data or not. When <b>AGPRBF#</b> is asserted the arbiter is not allowed to return (low priority) read data to the RIVA 128. This signal should be pulled up via a $4.7 \mathrm{K}\Omega$ resistor (although it is supposed to be pulled up by the motherboard chipset).                                        |  |  |  |  |  |  |

| AGPPIPE#                  | 0   | Pipelined Read is asserted by RIVA 128 (when the current master) to indicate a full width read address is to be enqueued by the target. The RIVA 128 enqueues one request each rising clock edge while AGPPIPE# is asserted. When AGPPIPE# is de-asserted no new requests are enqueued across PCIAD[31:0]. AGPPIPE# is a sustained tri-state signal from the RIVA 128 and is an input to the target (the core logic). |  |  |  |  |  |  |

| AGPADSTB0*,<br>AGPADSTB1* | I/O | These signals are currently a "no-connect" in this revision of the RIVA 128 but may be activated to support AGP double-edge clocking in future pin compatible devices. It is recommended that these pins are connected directly to the AD_STB0 and AD_STB1 pins defined in the AGP specification.                                                                                                                     |  |  |  |  |  |  |

## 2.2 PCI 2.1 LOCAL BUS INTERFACE

| Signal      | 1/0 | Description                                                                                                                                                                                                                            |

|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICLK      | I   | PCI clock. This signal provides timing for all transactions on the PCI bus, except for PCIRST# and PCIINTA#. All PCI signals are sampled on the rising edge of PCICLK and all timing parameters are defined with respect to this edge. |

| PCIRST#     | I   | PCI reset. This signal is used to bring registers, sequencers and signals to a consistent state. When <b>PCIRST#</b> is asserted all output signals are tristated.                                                                     |

| PCIAD[31:0] | I/O | 32-bit multiplexed address and data bus. A bus transaction consists of an address phase followed by one or more data phases.                                                                                                           |

| Signal       | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICBE[3:0]# | I/O | Multiplexed bus command and byte enable signals. During the address phase of a transaction PCICBE[3:0]# define the bus command, during the data phase PCICBE[3:0]# are used as byte enables. The byte enables are valid for the entire data phase and determine which byte lanes contain valid data. PCICBE[0]# applies to byte 0 (LSB) and PCICBE[3]# applies to byte 3 (MSB).  When connected to AGP these signals carry different commands than PCI when requests are being enqueued using AGPPIPE#. Valid byte information is provided during AGP write transactions. PCICBE[3:0]# are not used during the return of AGP read data. |

| PCIPAR       | I/O | Parity. This signal is the even parity bit generated across PCIAD[31:0] and PCICBE[3:0]#. PCIPAR is stable and valid one clock after the address phase. For data phases PCIPAR is stable and valid one clock after either PCIIRDY# is asserted on a write transaction or PCITRDY# is asserted on a read transaction. Once PCIPAR is valid, it remains valid until one clock after completion of the current data phase. The master drives PCIPAR for address and write data phases; the target drives PCIPAR for read data phases.                                                                                                      |

| PCIFRAME#    | I/O | Cycle frame. This signal is driven by the current master to indicate the beginning of an access and its duration. <b>PCIFRAME#</b> is asserted to indicate that a bus transaction is beginning. Data transfers continue while <b>PCIFRAME#</b> is asserted. When <b>PCIFRAME#</b> is deasserted, the transaction is in the final data phase.                                                                                                                                                                                                                                                                                            |

| PCIIRDY#     | I/O | Initiator ready. This signal indicates the initiator's (bus master's) ability to complete the current data phase of the transaction. See extended description for <b>PCITRDY#</b> .  When connected to AGP this signal indicates the initiator (AGP compliant master) is ready to provide all write data for the current transaction. Once <b>PCIIRDY#</b> is asserted for a write operation, the master is not allowed to insert wait states. The assertion of <b>PCIIRDY#</b> for reads, indicates that the master is ready to transfer a subsequent block of read data. The                                                          |

|              |     | master is never allowed to insert a wait state during the initial block of a read transaction. However, it may insert wait states after each block transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PCITRDY#     | I/O | Target ready. This signal indicates the target's (selected device's) ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |     | PCITRDY# is used in conjunction with PCIIRDY#. A data phase is completed on any clock when both PCITRDY# and PCIIRDY# are sampled as being asserted. During a read, PCITRDY# indicates that valid data is present on PCIAD[31:0]. During a write, it indicates the target is prepared to accept data. Wait cycles are inserted until both PCIIRDY# and PCITRDY# are asserted together.                                                                                                                                                                                                                                                  |

|              |     | When connected to AGP this signal indicates the AGP compliant target is ready to provide read data for the entire transaction (when transaction can complete within four clocks) or is ready to transfer a (initial or subsequent) block of data, when the transfer requires more than four clocks to complete. The target is allowed to insert wait states after each block transfers on both read and write transactions.                                                                                                                                                                                                             |

| PCISTOP#     | I/O | <b>PCISTOP#</b> indicates that the current target is requesting the master to terminate the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PCIIDSEL     | I   | Initialization device select. This signal is used as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              |     | For AGP applications note that IDSEL is not a pin on the AGP connector. The RIVA 128 performs the device select decode internally within its host interface. It is not required to connect the AD16 signal to the IDSEL pin as suggested in the AGP specification.                                                                                                                                                                                                                                                                                                                                                                      |

| PCIDEVSEL#   | I/O | Device select. When acting as an output <b>PCIDEVSEL#</b> indicates that the RIVA 128 has decoded the PCI address and is claiming the current access as the target. As an input <b>PCIDEVSEL#</b> indicates whether any other device on the bus has been selected.                                                                                                                                                                                                                                                                                                                                                                      |

| PCIREQ#      | 0   | Request. This signal is asserted by the RIVA 128 to indicate to the arbiter that it desires to become master of the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Signal   | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIGNT#  | I   | Grant. This signal indicates to the RIVA 128 that access to the bus has been granted and it can now become bus master.  When connected to AGP additional information is provided on AGPST[2:0] indicating that the master is the recipient of previously requested read data (high or low priority), it is to provide write data (high or low priority), for a previously enqueued write command or has been given permission to start a bus transaction (AGP or PCI). |

| PCIINTA# | 0   | Interrupt request line. This open drain output is asserted and deasserted asynchronously to <b>PCICLK</b> .                                                                                                                                                                                                                                                                                                                                                            |

## 2.3 SGRAM FRAMEBUFFER INTERFACE

| Signal                       | I/O | Description                                                                                                                                                                                                                                                                                           |

|------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FBD[127:0]                   | I/O | The 128-bit SGRAM memory data bus.  FBD[31:0] are also used to access up to 64KBytes of 8-bit ROM or Flash ROM, using  FBD[15:0] as address ROMA[15:0], FBD[31:24] as ROMD[7:0], FBD[17] as ROMWE#  and FBD[16] as ROMOE#.                                                                            |

| FBA[10:0]                    | 0   | Memory Address bus. Configuration strapping options are also decoded on these signals during PCIRST# as described in Section 10, page 49. <b>[FBA[10]</b> is reserved for future expansion and should be pulled to <b>GND</b> via a $4.7 \text{K}\Omega$ resistor.                                    |

| FBRAS#                       | 0   | Memory Row Address Strobe for all memory devices.                                                                                                                                                                                                                                                     |

| FBCAS#                       | 0   | Memory Column Address Strobe for all memory devices.                                                                                                                                                                                                                                                  |

| FBCS[1:0]#                   | 0   | Memory Chip Select strobes for each SGRAM bank.                                                                                                                                                                                                                                                       |

| FBWE#                        | 0   | Memory Write Enable strobe for all memory devices.                                                                                                                                                                                                                                                    |

| FBDQM[15:0]                  | 0   | Memory Data/Output Enable strobes for each of the 16 bytes.                                                                                                                                                                                                                                           |

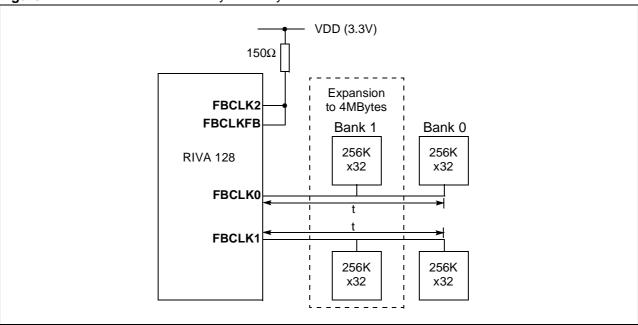

| FBCLK0,<br>FBCLK1,<br>FBCLK2 | 0   | Memory Clock signals. Separate clock signals <b>FBCLK0</b> and <b>FBCLK1</b> are provided for each bank of SGRAM for reduced clock skew and loading. <b>FBCLK2</b> is fed back to <b>FBCLKFB</b> . Details of recommended memory clock layout are given in Section 6.3, page 31.                      |

| FBCLKFB                      | I   | Framebuffer clock feedback. FBCLK2 is fed back to FBCLKFB.                                                                                                                                                                                                                                            |

| FBCKE*                       | 0   | This signal is currently a "no-connect" in this revision of the RIVA 128 but may be activated to support the framebuffer memory clock enable for power management in future pin compatible devices. It is recommended that this pin is tied to VDD through a $4.7 \mathrm{K}\Omega$ pull-up resistor. |

## 2.4 VIDEO PORT

| Signal     | 1/0 | Description                                                                                     |

|------------|-----|-------------------------------------------------------------------------------------------------|

| MP_AD[7:0] | I/O | Media Port 8-bit multiplexed address and data bus or ITU-R-656 video data bus when in 656 mode. |

| MPCLK      | I   | 40MHz Media Port system clock or pixel clock when in 656 mode.                                  |

| MPDTACK#   | I   | Media Port data transfer acknowledgment signal.                                                 |

| MPFRAME#   | 0   | Initiates Media Port transfers when active, terminates transfers when inactive.                 |

| MPSTOP#    | ı   | Media Port control signal used by the slave to terminate transfers.                             |

## 2.5 DEVICE ENABLE SIGNALS

| Signal | I/O | Description                                                                                                                                                        |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROMCS# | 0   | Enables reads from an external 64Kx 8 or 32Kx8 ROM or Flash ROM. This signal is used in conjunction with framebuffer data lines as described above in Section 2.3. |

## 2.6 DISPLAY INTERFACE

| Signal   | I/O | Description                                                                                                                                              |

|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA      | I/O | Used for DDC2B+ monitor communication and interface to video decoder devices.                                                                            |

| SCL      | I/O | Used for DDC2B+ monitor communication and interface to video decoder devices.                                                                            |

| VIDVSYNC | 0   | Vertical sync supplied to the display monitor. No buffering is required. In TV mode this signal supplies composite sync to an external PAL/NTSC encoder. |

| VIDHSYNC | 0   | Horizontal sync supplied to the display monitor. No buffering is required.                                                                               |

## 2.7 VIDEO DAC AND PLL ANALOG SIGNALS

| Signal                 | I/O | Description                                                                                                                                                                                                                                                                                                                                           |

|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RED,<br>GREEN,<br>BLUE | 0   | RGB display monitor outputs. These are software configurable to drive either a doubly terminated or singly terminated 75 $\Omega$ load.                                                                                                                                                                                                               |

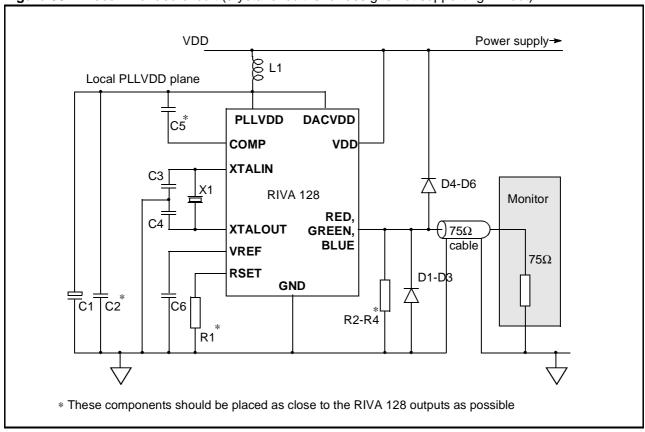

| COMP                   | -   | External compensation capacitor for the video DACs. This pin should be connected to <b>DACVDD</b> via the compensation capacitor, see Figure 58, page 54.                                                                                                                                                                                             |

| RSET                   | -   | A precision resistor placed between this pin and GND sets the full-scale video DAC current, see Figure 58, page 54.                                                                                                                                                                                                                                   |

| VREF                   | -   | A capacitor should be placed between this pin and GND as shown in Figure 58, page 54.                                                                                                                                                                                                                                                                 |

| XTALIN                 | I   | A series resonant crystal is connected between these two points to provide the reference                                                                                                                                                                                                                                                              |

| XTALOUT                | 0   | clock for the internal MCLK and VCLK clock synthesizers, see Figure 58 and Table 16, page 54. Alternately, an external LVTTL clock oscillator output may be driven into <b>XTA-LOUT</b> , connecting <b>XTALIN</b> to GND. For designs supporting TV-out, <b>XTALOUT</b> should be driven by a reference clock as described in Section 11.6, page 55. |

## 2.8 POWER SUPPLY

| Signal    | I/O | Description                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| DACVDD    | Р   | Analog power supply for the video DACs.                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| PLLVDD    | Р   | nalog power supply for all clock synthesizers.                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| VDD       | Р   | Digital power supply.                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| GND       | Р   | Ground.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| MPCLAMP   | Р   | <b>MPCLAMP</b> is connected to +5V to protect the 3.3V RIVA 128 from external devices which will potentially drive 5V signal levels onto the Video Port input pins.                                                                                                                       |  |  |  |  |  |  |

| HOSTVDD   | Р   | <b>HOSTVDD</b> is connected to the Vddq 3.3 pins on the AGP connector. This is the supply voltage for the I/O buffers and is isolated from the core VDD. On AGP designs these pins are also connected to the <b>HOSTCLAMP</b> pins. On PCI designs they are connected to the 3.3V supply. |  |  |  |  |  |  |

| HOSTCLAMP | Р   | <b>HOSTCLAMP</b> is the supply signalling rail protection for the host interface. In AGP designs these signals are connected to Vddq 3.3. For PCI designs they are connected to the I/O power pins $(V_{(I/O)})$ .                                                                        |  |  |  |  |  |  |

## 2.9 TEST

| Signal   | I/O | Description                                                                                                                                                                                                                                                                                                                                         |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TESTMODE | I   | For designs which will be tested in-circuit, this pin should be connected to GND through a 10KΩ pull-down resistor, otherwise this pin should be connected directly to GND. When <b>TESTMODE</b> is asserted, <b>MP_AD[3:0]</b> are reassigned as <b>TESTCTL[3:0]</b> respectively. Information on in-circuit test is given in Section 12, page 57. |

## 3 OVERVIEW OF THE RIVA 128

The RIVA 128 is the first 128-bit 3D Multimedia Accelerator to offer unparalleled 2D and 3D performance, meeting all the requirements of the mainstream PC graphics market and Microsoft's PC'97. The RIVA 128 introduces the most advanced Direct3D™ acceleration solution and also delivers leadership VGA, 2D and Video performance, enabling a range of applications from 3D games through to DVD, Intercast™ and video conferencing.

## 3.1 BALANCED PC SYSTEM

The RIVA 128 is designed to leverage existing PC system resources such as system memory, high bandwidth internal buses and bus master capabilities. The synergy between the RIVA 128 graphics pipeline architecture and that of the current generation PCI and next generation AGP platforms, defines ground breaking performance levels at the cost point currently required for mainstream PC graphics solutions.

## **Execute versus DMA models**

The RIVA 128 is architected to optimize PC system resources in a manner consistent with the AGP "Execute" model. In this model texture map data for 3D applications is stored in system memory and individual texels are accessed as needed by the graphics pipeline. This is a significant enhancement over the DMA model where entire texture maps are transferred into off-screen frame-buffer memory.

The advantages of the Execute versus the DMA model are:

- Improved system performance since only the required texels and not the entire texture map, cross the bus.

- Substantial cost savings since all the framebuffer is usable for the displayed screen and Z buffer and no part of it is required to be dedicated to texture storage or texture caching.

- There is no software overhead in the Direct3D driver to manage texture caching between application memory and the framebuffer.

To extend the advantages of the Execute model, the RIVA 128's proprietary texture cache and virtual DMA bus master design overcomes the bandwidth limitation of PCI, by sustaining a high texel throughput with minimum bus utilization. The host interface supports burst transactions up to 66MHz and provides over 200MBytes/s on AGP. AGP ac-

cesses offer other performance enhancements since they are from non-cacheable memory (no snoop) and can be low priority to prevent processor stalls, or high priority to prevent graphics engine stalls.

## Building a balanced system

RIVA 128 is architected to provide the level of 3D graphics performance and quality available in top arcade platforms. To provide comparable scene complexity in the 1997 time-frame, processors will have to achieve new levels of floating point performance. Profiles have shown that 1997 mainstream CPUs will be able to transform over 1 million lit, meshed triangles/s at 50% utilization using Direct3D. This represents an order of magnitude performance increase over anything attainable in 1996 PC games.

To build a balanced system the graphics pipeline must match the CPU's performance. It must be capable of rendering at least 1 million polygons/s in order to avoid CPU stalls. Factors affecting this system balance include:

- Direct3D compatibility. Minimizing the differences between the hardware interface and the Direct3D data structures.

- Triangle setup. Minimizing the number of format conversions and delta calculations done by the CPU.

- Display-list processing. Avoiding CPU stalls by allowing the graphics pipeline to execute independently of the CPU.

- Vertex caching. Avoids saturating the host interface with repeated vertices, lowering the traffic on the bus and reducing system memory collisions.

- Host interface performance.

#### 3.2 HOST INTERFACE

The host interface boosts communication between the host CPU and the RIVA 128. The optimized interface performs burst DMA bus mastering for efficient and fast data transfer.

- 32-bit PCI version 2.1 or AGP version 1.0

- · Burst DMA Master and target

- 33MHz PCI clock rate or 66MHz AGP clock rate

- Supports over 100MBytes/s with 33MHz PCI and over 200MBytes/s on 66MHz AGP

- · Implements read buffer posting on AGP

- Fully supports the "Execute" model on both PCI and AGP

## 3.3 2D ACCELERATION

The RIVA 128's 2D rendering engine delivers industry-leading Windows acceleration performance:

- 100MHz 128-bit graphics engine optimized for single cycle operation into the 128-bit SGRAM interface supporting up to 1.6GBytes/s

- Acceleration functions optimized for minimal software overhead on key GDI calls

- Extensive support for DirectDraw in Windows95 including optimized Direct Framebuffer (DFB) access with Write-combining

- Accelerated primitives including BLT, transparent BLT, stretchBLT, points, lins, lines, polylines, polygons, fills, patterns, arbitrary rectangular clipping and improved text rendering

- Pipeline optimized for multiple color depths including 8, 15, 24, and 30 bits per pixel

- DMA Pusher allows the 2D graphics pipeline to load rendering methods optimizing RIVA 128/ host multi-tasking

- Execution of all 256 Raster Operations (as defined by Microsoft Windows) at 8, 15, 24 and 30-bit color depths

- 15-bit hardware color cursor

- · Hardware color dithering

- Multi buffering (Double, Triple, Quad buffering) for smooth animation

## 3.4 3D ENGINE

## Triangle setup engine

- Setup hardware optimized for Microsoft's Direct3D API

- 5Gflop floating point geometry processor

- · Slope and setup calculations

- Accepts IEEE Single Precision format used in Direct3D

- Efficient vertex caching

## Rendering engine

The RIVA 128 Multimedia Accelerator integrates an orthodox 3D rendering pipeline and triangle setup function which not only fully utilizes the capabilities of the Accelerated Graphics Port, but also supports advanced texture mapped 3D over the PCI bus. The RIVA 128 3D pipeline offers to Direct3D or similar APIs advanced triangle rendering capabilities:

- Rendering pipeline optimized for Microsoft's Direct3D API

- Perspective correct true-color Gouraud lighting and texture mapping

- Full 32-bit RGBA texture filter and Gouraud lighting pixel data path

- Alpha blending for translucency and transparency

- Sub-pixel accurate texture mapping

- Internal pixel path: up to 24bits, alpha: up to 8 bits

- Texture magnification filtering with high quality bilinear filtering without performance degradation

- Texture minification filtering with MIP mapping without performance degradation

- LOD MIP-mapping: filter shape is dynamically adjusted based on surface orientation

- Texture sizes from 4 to 2048 texels in either U or V

- Textures can be looped and paged in real time for texture animation

- Perspective correct per-pixel fog for atmospheric effects

- Perspective correct specular highlights

- Multi buffering (Double, Triple, Quad buffering) for smooth 3D animation

- Multipass rendering for environmental mapping and advanced texturing

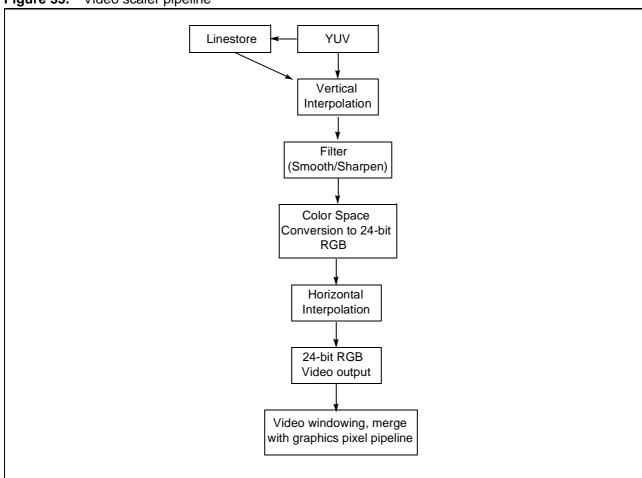

## 3.5 VIDEO PROCESSOR

The RIVA 128 Palette-DAC pipeline accelerates full-motion video playback, sustaining 30 frames per second while retaining the highest quality color resolution, implementing true bilinear filtering for scaled video, and compensating for filtering losses using edge enhancement algorithms.

- Advanced support for DirectDraw (DirectVideo) in Windows 95

- Back-end hardware video scaling for video conferencing and playback

- Hardware color space conversion (YUV 4:2:2 and 4:2:0)

- Multi-tap X and Y filtering for superior image quality

- Optional edge enhancement to retain video sharpness

- Support for scaled field interframing for reduced motion artifacts and reduced storage

- · Per-pixel color keying

- Multiple video windows with hardware color space conversion and filtering

- Planar YUV12 (4:2:0) to/from packed (4:2:2) conversion for software MPEG acceleration and H.261 video conferencing applications

- Accelerated playback of industry standard codecs including MPEG-1/2, Indeo, Cinepak

## 3.6 VIDEO PORT

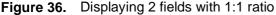

The RIVA 128 Multimedia Accelerator provides connectivity for video input devices such as Philips SAA7111A, ITT 3225 and Samsung KS0127 through an ITU-R-656 video input bus to DVD and MPEG2 decoders through bidirectional media port functionality.

- Supported through VPE extensions to DirectDraw

- Supports filtered down-scaling and decimation

- Supports real time video capture via Bus Mastering DMA

- · Serial interface for decoder control

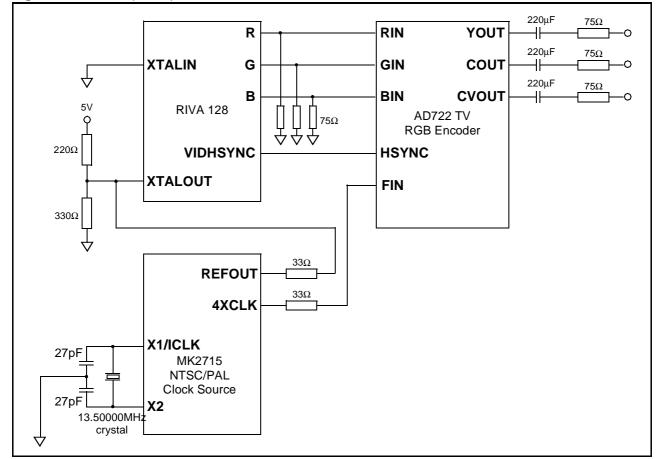

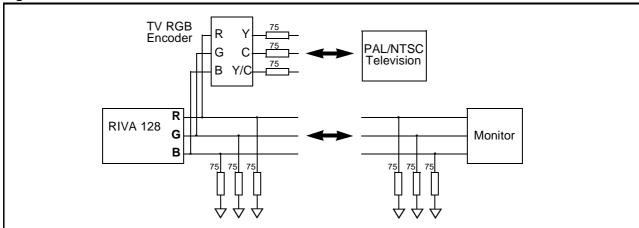

# 3.7 DIRECT RGB OUTPUT TO LOW COST PAL/NTSC ENCODER

The RIVA 128 has also been designed to interface to a standard PAL or NTSC television via a low cost TV encoder chip. In PAL or NTSC display modes the interlaced output is internally flicker-filtered and CCIR/EIA compliant timing reference signals are generated.

## 3.8 SUPPORT FOR STANDARDS

- Multimedia support for MS-DOS, Windows 3.11, Windows 95, and Windows NT

- Acceleration for Windows 95 Direct APIs including Direct3D, DirectDraw and DirectVideo

- VGA and SVGA: The RIVA 128 has an industry standard 32-bit VGA core and BIOS support. In PCI configuration space the VGA can be enabled and disabled independently of the GUI.

- Glue-less Accelerated Graphics Port (AGP 1.0) or PCI 2.1 bus interface

- ITU/CCIR-656 compatible video port

- VESA DDC2B+, DPMS, VBE 2.0 supported

## 3.9 RESOLUTIONS SUPPORTED

| Resolution | BPP                                             | 2MByte | 4MByte (128-bit) |

|------------|-------------------------------------------------|--------|------------------|

|            | 4                                               | 120Hz  | 120Hz            |

| 640x480    | 8                                               | 120Hz  | 120Hz            |

| 040x460    | 16                                              | 120Hz  | 120Hz            |

|            | 32                                              | 120Hz  | 120Hz            |

|            | 4                                               | 120Hz  | 120Hz            |

| 800x600    | 8                                               | 120Hz  | 120Hz            |

| 800,800    | 16                                              | 120Hz  | 120Hz            |

|            | 16 120Hz 32 120Hz 4 120Hz 8 120Hz 16 120Hz 32 - | 120Hz  |                  |

|            | 4                                               | 120Hz  | 120Hz            |

| 1024x768   | 8                                               | 120Hz  | 120Hz            |

| 1024x700   | 16                                              | 120Hz  | 120Hz            |

|            | 32                                              |        | 120Hz            |

|            | 4                                               | 120Hz  | 120Hz            |

| 1152x864   | 8                                               | 120Hz  | 120Hz            |

| 1132x004   | 16                                              | 120Hz  | 120Hz            |

|            | 32                                              | -      | 100Hz            |

|            | 4                                               | 100Hz  | 100Hz            |

| 1280x1024  | 8                                               | 100Hz  | 100Hz            |

| 1200×1024  | 16                                              | -      | 100Hz            |

|            | 32                                              | -      | -                |

|            | 4                                               | 75Hz   | 75Hz             |

| 1600x1200  | 8                                               | 75Hz   | 75Hz             |

| 1000x1200  | 16                                              | -      | 75Hz             |

|            | 32                                              | -      | -                |

#### 3.10 CUSTOMER EVALUATION KIT

A Customer Evaluation Kit (CEK) is available for evaluating the RIVA 128. The CEK includes a PCI or AGP adapter card designed to support the RIVA 128 feature set, an evaluation CD-ROM containing a fast-installation application, extensive device drivers and programs demonstrating the RIVA 128 features and performance.

## This CEK includes:

- RIVA 128 evaluation board and CD-ROM

- · QuickStart install/user guide

- · OS drivers and files

- Windows 3.11

- Windows 95 Direct X/3D

- Windows NT 3.5

- Windows NT 4.0

- · Demonstration files and Game demos

- · Benchmark programs and files

## 3.11 TURNKEY MANUFACTURING PACKAGE

A Turnkey Manufacturing Package (TMP) is available to support OEM designs and development through to production. It delivers a complete manufacturable hardware and software solution that

allows an OEM to rapidly design and bring to volume an RIVA 128-based product.

#### This TMP includes:

- CD-ROM

- RIVA 128 Datasheet and Application Notes

- OrCAD™ schematic capture and PADS™ layout design information

- Quick Start install/user guide/release notes

- BIOS Modification program, BIOS binaries and utilities

- Bring-up and OEM Production Diagnostics

- Software and Utilities

- OS drivers and files

- Windows 3.11

- Windows 95 Direct X/3D

- Windows NT 3.5

- Windows NT 4.0

- FCC/CE Certification Package

- · Content developer and WWW information

- · Partner solutions

- Access to our password-protected web site for upgrade files and release notes.

## 4 ACCELERATED GRAPHICS PORT (AGP) INTERFACE

The Accelerated Graphics Port (AGP) is a high performance, component level interconnect targeted at 3D graphical display applications and based on performance enhancements to the PCI local bus.

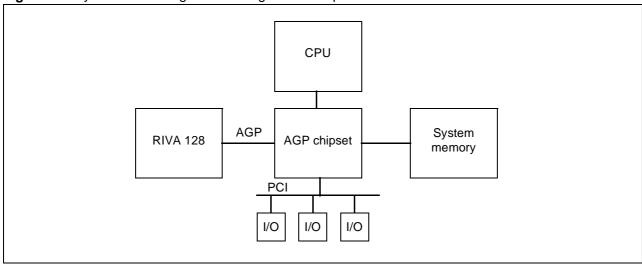

Figure 1. System block diagram showing relationship between AGP and PCI buses

## **Background to AGP**

Although 3D graphics acceleration is becoming a standard feature of multimedia PC platforms, 3D rendering generally has a voracious appetite for memory bandwidth. Consequently there is upward pressure on the PC's memory requirement leading to higher bill of material costs. These trends will increase, requiring high speed access to larger amounts of memory. The primary motivation for AGP therefore was to contain these costs whilst enabling performance improvements.

By providing significant bandwidth improvement between the graphics accelerator and system memory, some of the 3D rendering data structures can be shifted into main memory, thus relieving the pressure to increase the cost of the local graphics memory.

Texture data are the first structures targeted for shifting to system memory for four reasons:

- 1 Textures are generally read only, and therefore do not have special access ordering or coherency problems.

- 2 Shifting textures balances the bandwidth load between system memory and local graphics memory, since a well cached host processor has much lower memory bandwidth requirements than a 3D rendering engine. Texture access comprises perhaps the largest single component of rendering memory bandwidth (compared with rendering, display and Z buffers), so avoiding loading or caching textures in graphics

local memory saves not only this component of local memory bandwidth, but also the bandwidth necessary to load the texture store in the first place. Furthermore, this data must pass through main memory anyway as it is loaded from a mass store device.

- 3 Texture size is dependent upon application quality rather than on display resolution, and therefore subject to the greatest pressure for growth.

- 4 Texture data is not persistent; it resides in memory only for the duration of the application, so any system memory spent on texture storage can be returned to the free memory heap when the application finishes (unlike display buffers which remain in use).

Other data structures can be moved to main memory but the biggest gain results from moving texture data.

## Relationship of AGP to PCI

AGP is a superset of the 66MHz PCI Specification (Revision 2.1) with performance enhancements optimized for high performance 3D graphics applications.

The PCI Specification is unmodified by AGP and 'reserved' PCI fields, encodings and pins, etc. are not used.

AGP does not replace the need for the PCI bus in the system and the two are physically, logically, and electrically independent. As shown in Figure 1 the AGP bridge chip and RIVA 128 are the only devices on the AGP bus - all other I/O devices remain on the PCI bus.

The add-in slot defined for AGP uses a new connector body (for electrical signaling reasons) which is not compatible with the PCI connector; PCI and AGP boards are not mechanically interchangeable.

AGP accesses differ from PCI in that they are pipelined. This compares with serialized PCI

transactions, where the address, wait and data phases need to complete before the next transaction starts. AGP transactions can only access system memory - not other PCI devices or CPU. Bus mastering accesses can be either PCI or AGP-style.

Full details of AGP are given in the *Accelerated Graphics Port Interface Specification* [3] published by Intel Corporation.

## 4.1 RIVA 128 AGP INTERFACE

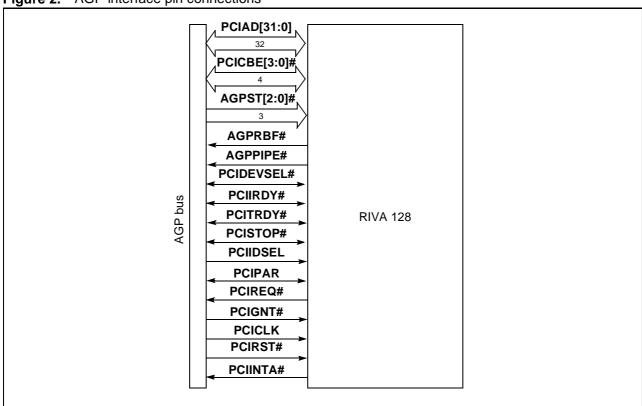

The RIVA 128 glueless interface to AGP 1.0 is shown in Figure 2.

Figure 2. AGP interface pin connections

## 4.2 AGP BUS TRANSACTIONS

## AGP bus commands supported

The following AGP bus commands are supported by the RIVA 128:

- Read

- Read (hi-priority)

#### PCI transactions on the AGP bus

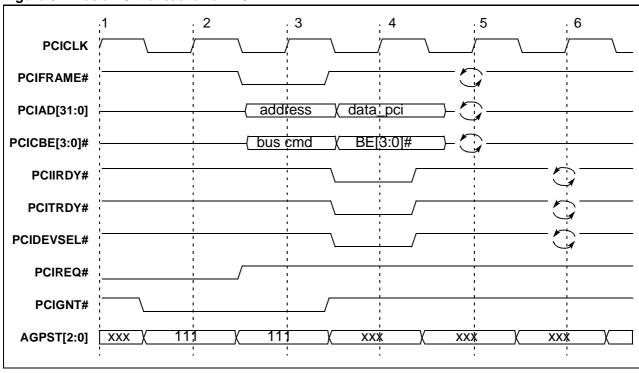

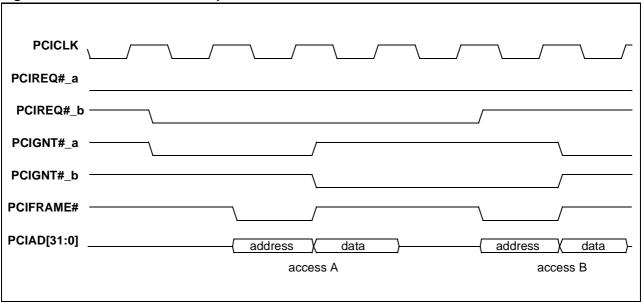

PCI transactions can be interleaved with AGP transactions including between pipelined AGP data transfers. A basic PCI transaction on the AGP interface is shown in Figure 3. If the PCI target is a non AGP compliant master, it will not see AGPST[2:0] and the transaction appears to be on a PCI bus. For AGP aware bus masters, AGPST[2:0] indicate that permission to use the interface has been granted to initiate a request and not to move AGP data.

17/77

Figure 3. Basic PCI transaction on AGP

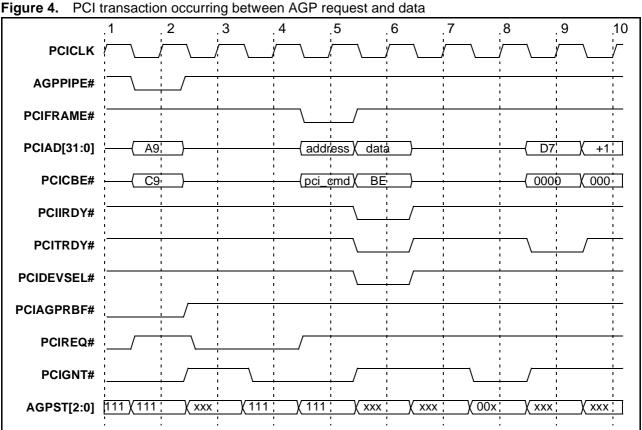

An example of a PCI transaction occurring between an AGP command cycle and return of data is shown in Figure 4. This shows the smallest number of cycles during which an AGP request can be enqueued, a PCI transaction performed and AGP read data returned.

Figure 5. Basic AGP pipeline concept

## Pipeline operation

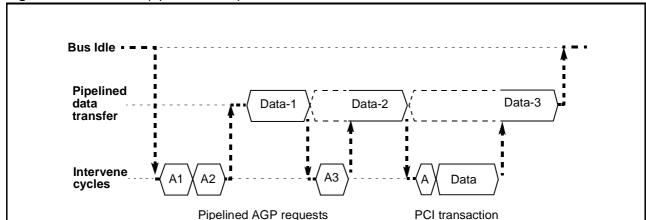

Memory access pipelining provides the main performance enhancement of AGP over PCI. AGP pipelined bus transactions share most of the PCI signal set, and are interleaved with PCI transactions on the bus.

The RIVA 128 supports AGP pipelined reads with a 4-deep queue of outstanding read requests. Pipelined reads are primarily used by the RIVA 128 for cache filling, the cache size being optimized for AGP bursts. Depending on the AGP bridge, a bandwidth of up to 248MByte/s is achievable for 128-byte pipelined reads. This compares with around 100MByte/s for 128-byte 33MHz PCI reads. Another feature of AGP is that for smaller sized reads the bandwidth is not significantly reduced. Whereas 16-byte reads on PCI transfer at around 33MByte/s, on AGP around 175MByte/s is achievable. The RIVA 128 actually requests reads greater than 64 bytes in multiples of 32-byte transactions.

The pipe depth can be maintained by the AGP bus master (RIVA 128) intervening in a pipelined transfer to insert new requests between data replies. This bus sequencing is illustrated in Figure 5.

When the bus is in an idle condition, the pipe can be started by inserting one or more AGP access requests consecutively. Once the data reply to those accesses starts, that stream can be broken (or intervened) by the bus master (RIVA 128) inserting one or more additional AGP access requests or inserting a PCI transaction. This intervention is accomplished with the bus ownership signals, **PCIREQ#** and **PCIGNT#**.

The RIVA 128 implements both high and low priority reads depending of the status of the rendering engine. If the pipeline is likely to stall due to system memory read latency, a high priority read request is posted.

## **Address Transactions**

The RIVA 128 requests permission from the bridge to use **PCIAD[31:0]** to initiate either an AGP request or a PCI transaction by asserting **PCIREQ#**. The arbiter grants permission by asserting **PCIGNT#** with **AGPST[2:0]** equal to '111' (referred to as START). When the RIVA 128 receives START it must start the bus operation within two clocks of the bus becoming available. For example, when the bus is in an idle condition when START is received, the RIVA 128 must initiate the bus transaction on the next clock and the one following.

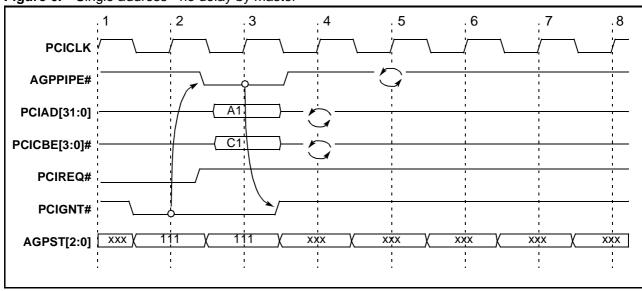

Figure 6 shows a single address being enqueued by the RIVA 128. Sometime before clock 1, the RIVA 128 asserts **PCIREQ#** to gain permission to use PCIAD[31:0]. The arbiter grants permission by indicating START on clock 2. A new request (address, command and length) are enqueued on each clock in which AGPPIPE# is asserted. The address of the request to be enqueued is presented on PCIAD[31:3], the length on PCIAD[2:0] and the command on PCICBE[3:0]#. In Figure 6 only a single address is enqueued since AGPPIPE# is just asserted for a single clock. The RIVA 128 indicates that the current address is the last it intends to enqueue when AGPPIPE# is asserted and PCIREQ# is deasserted (occurring on clock 3). Once the arbiter detects the assertion of AGP-PIPE# or PCIFRAME# it deasserts PCIGNT# on clock 4.

Figure 6. Single address - no delay by master

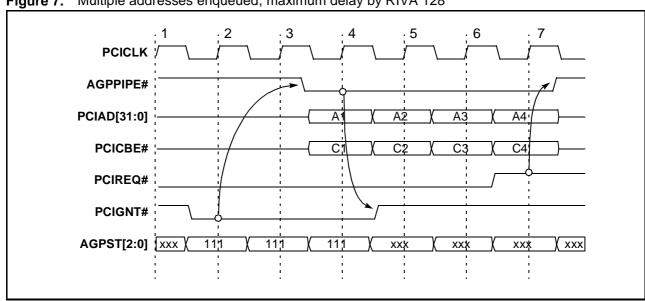

Figure 7 shows the RIVA 128 enqueuing 4 requests, where the first request is delayed by the maximum 2 cycles allowed. START is indicated on clock 2, but the RIVA 128 does not assert AGPPIPE# until clock 4. Note that **PCIREQ#** remains asserted on clock 6 to indicate that the current request is not the last one. When PCIREQ# is deasserted on clock 7 with AGPPIPE# still asserted this indicates that the current address is the last one to be enqueued during this transaction. AGPPIPE# must be deasserted on the next clock when PCIREQ# is sampled as deasserted. If the RIVA 128 wants to enqueue more requests during this bus operation, it continues asserting AGPPIPE# until all of its requests are enqueued or until it has filled all the available request slots provided by the target.

Figure 7. Multiple addresses engueued, maximum delay by RIVA 128

## **AGP timing specification**

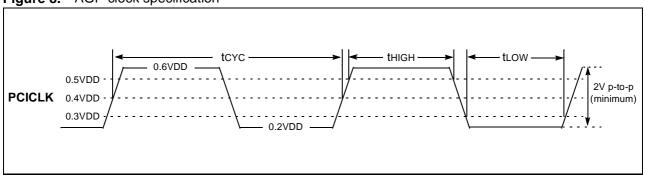

Figure 8. AGP clock specification

Table 1. AGP clock timing parameters

| Symbol | Parameter        | Min. | Max. | Unit | Notes |

|--------|------------------|------|------|------|-------|

| tcyc   | PCICLK period    | 15   | 30   | ns   |       |

| tHIGH  | PCICLK high time | 6    |      | ns   |       |

| tLOW   | PCICLK low time  | 6    |      | ns   |       |

|        | PCICLK slew rate | 1.5  | 4    | V/ns | 1     |

## **NOTES**

1 This rise and fall time is measured across the minimum peak-to-peak range as shown in Figure 8.

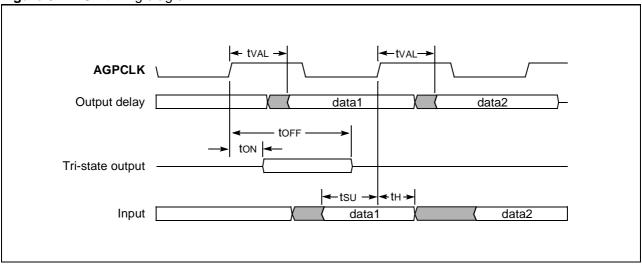

Figure 9. AGP timing diagram

Table 2. AGP timing parameters

| Symbol | Parameter                                                     | Min. | Max. | Unit | Notes |

|--------|---------------------------------------------------------------|------|------|------|-------|

| tVAL   | AGPCLK to signal valid delay (data and control signals)       | 2    | 11   | ns   |       |

| ton    | Float to active delay                                         | 2    |      | ns   |       |

| tOFF   | Active to float delay                                         |      | 28   | ns   |       |

| tsu    | Input set up time to <b>AGPCLK</b> (data and control signals) | 7    |      | ns   |       |

| tH     | Input hold time from AGPCLK                                   | 0    |      | ns   |       |

## 5 PCI 2.1 LOCAL BUS INTERFACE

## 5.1 RIVA 128 PCI INTERFACE

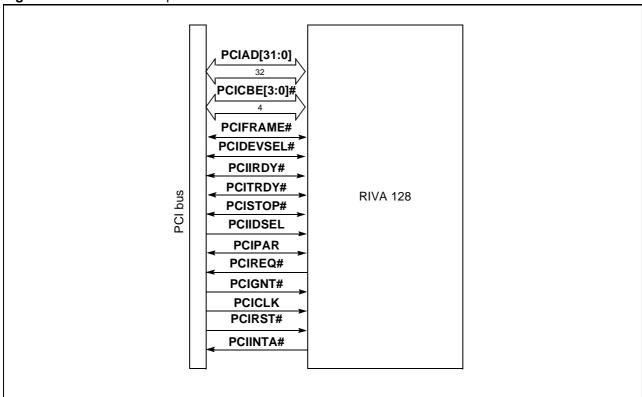

The RIVA 128 supports a glueless interface to PCI 2.1 with both master and slave capabilities. The host interface is fully compliant with the 32-bit PCI 2.1 specification.

The Multimedia Accelerator supports PCI bus operation up to 33MHz with zero-wait state capability and full bus mastering capability handling burst reads and burst writes.

Figure 10. PCI interface pin connections

Table 3. PCI bus commands supported by the RIVA 128

| Bus master            | Bus slave                    |

|-----------------------|------------------------------|

| Memory read and write | Memory read and write        |

| Memory read line      | I/O read and write           |

| Memory read multiple  | Configuration read and write |

|                       | Memory read line             |

|                       | Memory read multiple         |

|                       | Memory write invalidate      |

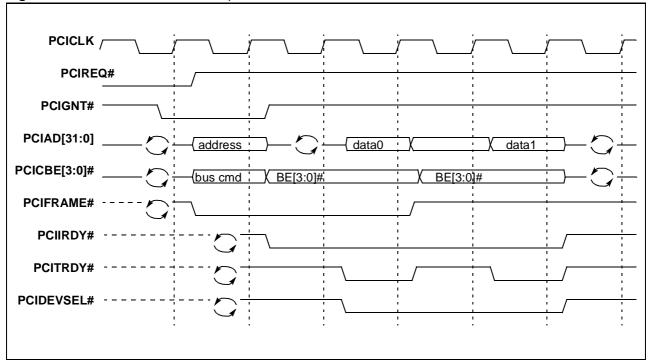

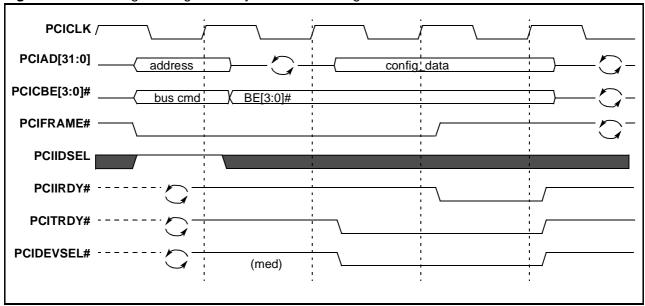

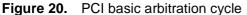

## 5.2 PCI TIMING SPECIFICATION

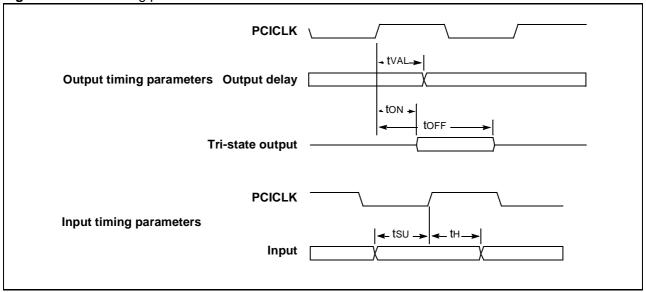

The timing specification of the PCI interface takes the form of generic setup, hold and delay times of transitions to and from the rising edge of **PCICLK** as shown in Figure 11.

Figure 11. PCI timing parameters

Table 4. PCI timing parameters

| Symbol                | Parameter                                     | Min. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------|------|------|------|-------|

| tVAL                  | PCICLK to signal valid delay (bussed signals) | 2    | 11   | ns   | 1     |

| tVAL <sup>(PTP)</sup> | PCICLK to signal valid delay (point to point) | 2    | 12   | ns   | 1     |

| ton                   | Float to active delay                         | 2    |      | ns   |       |

| toff                  | Active to float delay                         |      | 28   | ns   |       |

| tsu                   | Input set up time to PCICLK (bussed signals)  | 7    |      | ns   | 1     |

| tsu <sup>(PTP)</sup>  | Input set up time to PCICLK (PCIGNT#)         | 10   |      | ns   | 1     |

| tsu <sup>(PTP)</sup>  | Input set up time to PCICLK (PCIREQ#)         | 12   |      | ns   |       |

| tH                    | Input hold time from PCICLK                   | 0    |      | ns   |       |

## NOTE

<sup>1</sup> **PCIREQ#** and **PCIGNT#** are point to point signals and have different valid delay and input setup times than bussed signals. All other signals are bussed.

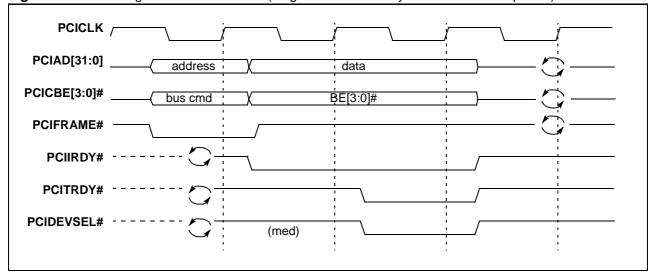

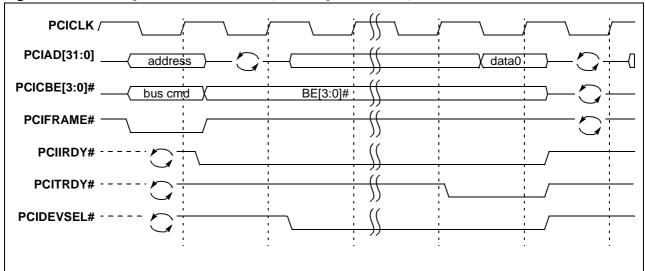

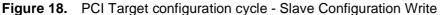

Figure 13. PCI Target write - Slave Write (multiple 32-bit with zero wait state **DEVSEL#** response)

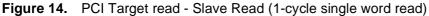

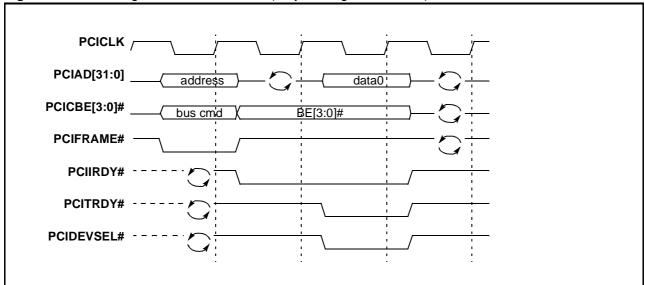

Figure 15. PCI Target read - Slave Read (slow single word read)

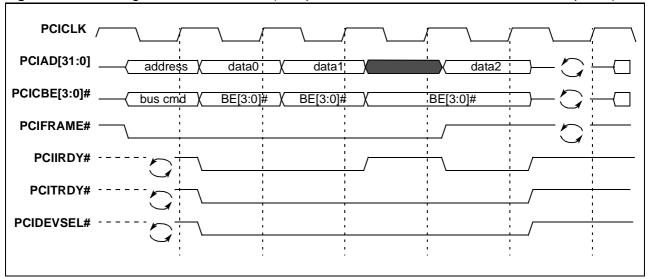

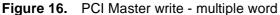

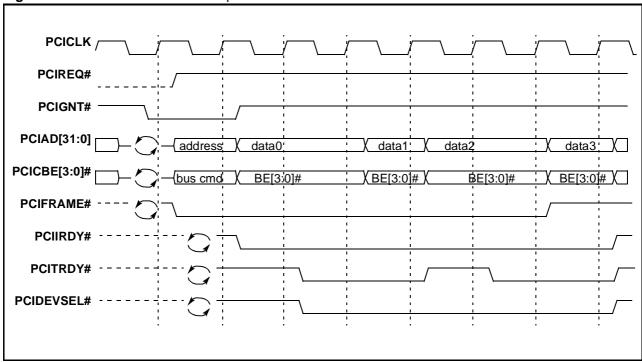

Figure 17. PCI Master read - multiple word

Note: The RIVA 128 does not generate fast back to back cycles as a bus master

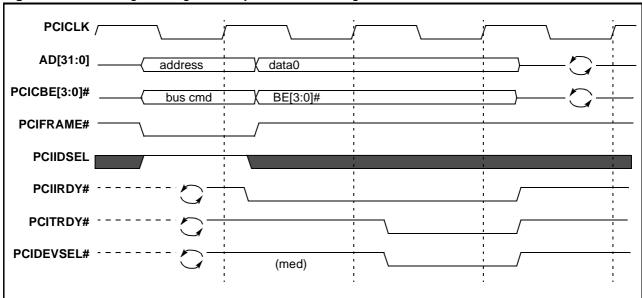

Figure 19. PCI Target configuration cycle - Slave Configuration Read

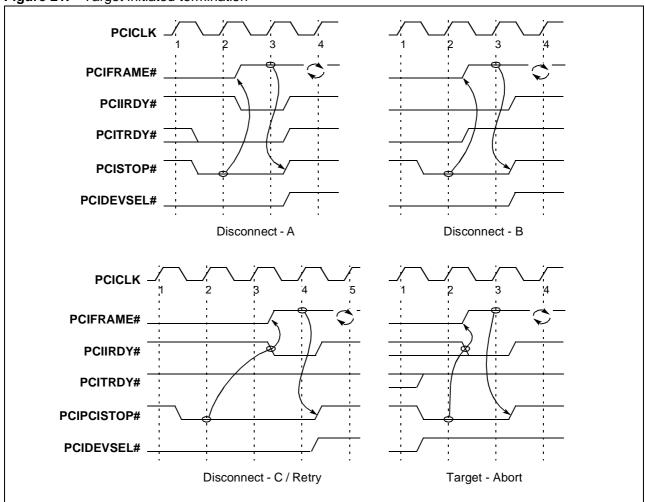

Figure 21. Target initiated termination

#### **6 SGRAM FRAMEBUFFER INTERFACE**

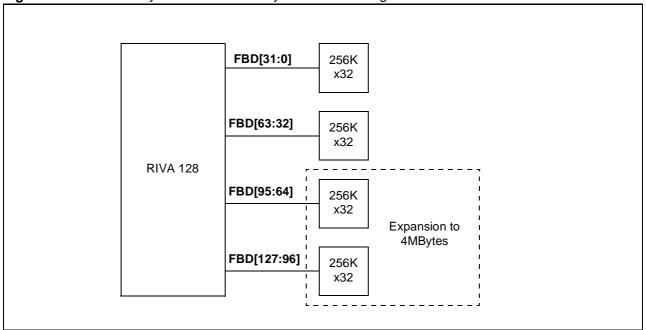

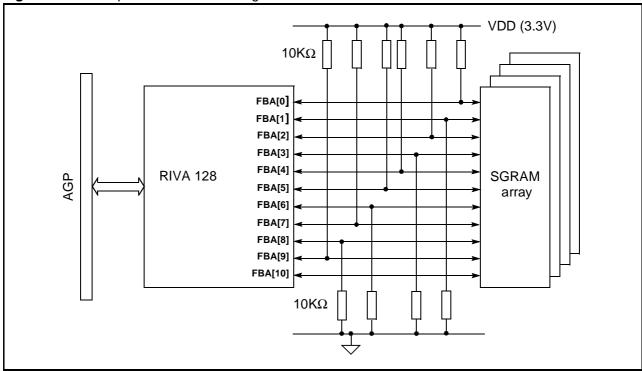

The RIVA 128 SGRAM interface can be configured with a 2MByte 64-bit or 4MByte 128-bit data bus. With a 128-bit bus, 4MBytes of SGRAM is supported as shown in Figure 22. All of the SGRAM signalling environment is 3.3V.

Figure 22. 64-bit 2MByte and 128-bit 4MByte SGRAM configurations

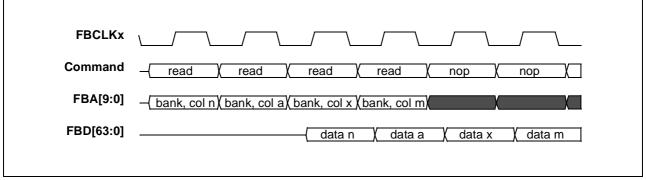

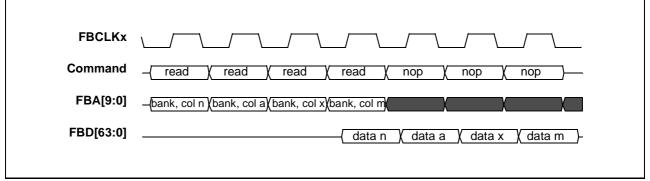

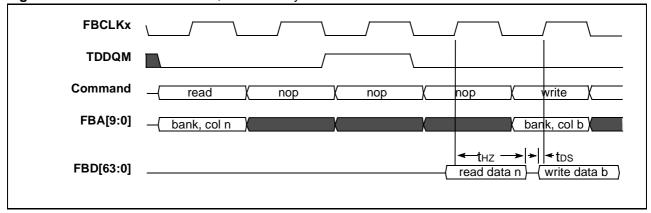

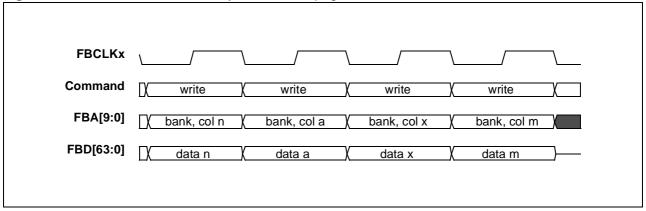

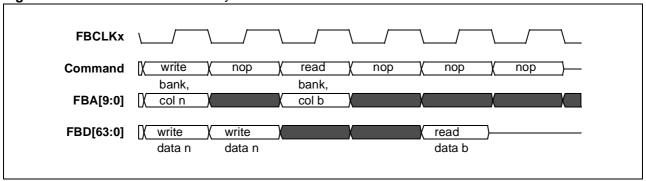

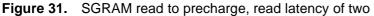

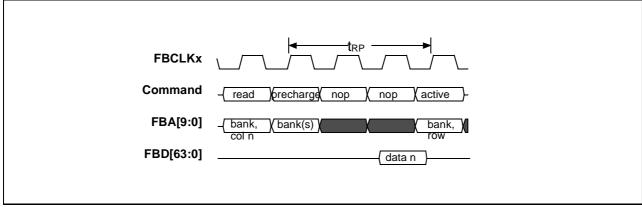

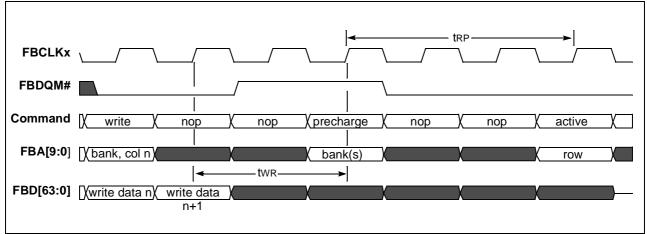

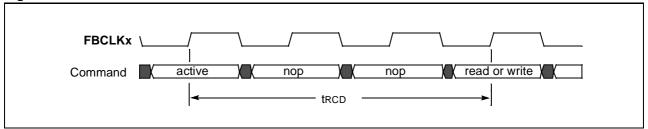

Read and write accesses to SGRAM are burst oriented. SGRAM commands supported by the RIVA 128 are shown in Table 5. Initialization of the memory devices is performed in the standard SGRAM manner as described in Section 6.1. Access sequences begin with an Active command followed by a Read or Write command. The address bits registered coincident with the Read or Write command are used to select the starting column location for the burst access. The RIVA 128 always uses a burst length of one and can launch a new read or write on every cycle.

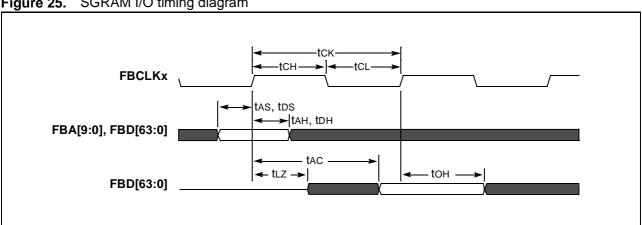

SGRAM has a fully synchronous interface with all signals registered on the positive edge of **FBCLKx**. Multiple clock outputs allow reductions in signal loading and more accuracy in data sampling at high frequency. The clock signals can be interspersed as shown in Figure 23, page 29 for optimal loading with either 2 or 4MBytes. The I/O timings relative to **FBCLKx** are shown in Figure 25, page 31.

FBCAS# FBWE# FBCKE# Expansion to 4MBytes FBDQM[0]# FBDQM[8]# FBDQM[1]# FBDQM[9]# FBD[31:0] FBD[95:64] 256K×32 SGRAM 256K×32 SGRAM FBDQM[2]# FBDQM[10]#-FBDQM[3]#-FBDQM[11]#-FBCS[0]#-FBCS[1]#-FBCLK0-FBCLK0-FBCAS# FBRAS# FBWE# FBDQM[4]# FBDQM[12]# FBDQM[5]# FBDQM[13]#-FBD[127:96] FBD[63:32] 256K×32 SGRAM 256K×32 SGRAM FBDQM[6]#-FBDQM[14]#-FBDQM[7]# FBDQM[15]# FBCS[0]#-FBCS[1]#-FBCLK1-FBCLK1-FBD[127:0] **≺**

Figure 23. 2 and 4MByte SGRAM configurations

1 RIVA 128 has a pin reserved for an eleventh address signal, **FBA[10]**, which may be used in the future with pin compatible 16MBit 256K x 2 x 32 SDRAMs. This signal is a "no-connect" in the initial RIVA 128 but may be activated in a future pin-compatible upgrade. If there is sufficient routing space it may be prudent to route this signal to pin 30 of the 100 pin PQFP SGRAM. **[FBA10]** should be pulled to **GND** with a 47KΩ resistor.

**Table 5.** Truth table of supported SGRAM commands

| Command <sup>1</sup>                                 | FBCSx | FBRAS# | FBCAS# | FBWE# | FBDQM | FBA[9:0]                                | FBD[63:0]  | Notes |