## Contents

|                                        |    |

|----------------------------------------|----|

| Features .....                         | 1  |

| Pin Assignment .....                   | 1  |

| Block Diagram .....                    | 2  |

| Functions .....                        | 2  |

| Operation .....                        | 7  |

| Absolute Maximum Ratings .....         | 12 |

| Recommended Operating Conditions ..... | 12 |

| DC Electrical Characteristics .....    | 13 |

| Measuring Circuits .....               | 13 |

| AC Electrical Characteristics .....    | 14 |

| Application Circuit Design .....       | 15 |

| Dimensions .....                       | 17 |

## REALTIME CLOCK

# S-3520CF

The S-3520CF is a real time clock that inputs/outputs serial clock or calendar data into/from the CPU. A built-in voltage regulator provides good frequency stability and low power consumption. Even during backup operation, the S-3520CF is effective for saving battery life. It has a built-in 120-bit SRAM, it is also useful for CPU data backup.

### ■ Features

- Easy serial interface to CPU with 5 lines (SCK, S<sub>IN</sub>, S<sub>OUT</sub>, CS, and WR)

- Low current consumption:

3.0  $\mu$ A max. at  $V_{DD} = 5.0$  V during backup

- Wide data retention voltage range : 2.0 to 6.0 V

- Good frequency stability against fluctuating power supply voltage :  $\pm 5$  ppm at  $V_{DD} = 2.0$  to 6.0 V

- Reference signal output can be selected from 1 Hz and 1024 Hz

- Data is serially output in BCD

- Clock and calendar data is modified by increment method

- Built-in auto-calendar until the year 2099

- Built-in counters for clock and calendar

- 30-s adjust function by software

- Built-in 30  $\times$  4-bit SRAM

- 14-pin SOP package

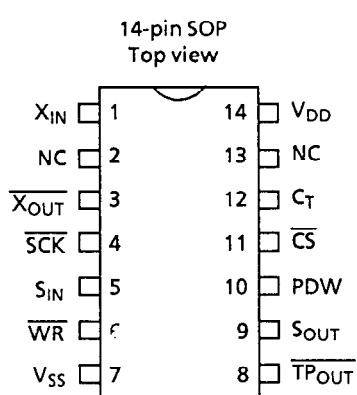

### ■ Pin Assignment

| Pin No. | Name                    | Functions                                                                                                                                                                                                                                                                                                |                       |

|---------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 1       | <u>X<sub>IN</sub></u>   | Input terminal of oscillation circuit                                                                                                                                                                                                                                                                    | Connection<br>Example |

|         | <u>X<sub>OUT</sub></u>  | Output terminal of oscillation circuit                                                                                                                                                                                                                                                                   |                       |

| 4       | <u>SCK</u>              | Synchronous signal input terminal of serial I/O, 8 clocks/cycle                                                                                                                                                                                                                                          |                       |

| 5       | <u>S<sub>IN</sub></u>   | Serial address/data input terminal<br>Counter address or address/data of register/RAM is input                                                                                                                                                                                                           |                       |

| 9       | <u>S<sub>OUT</sub></u>  | Serial address/data output terminal<br>Counter address or address/data of register/RAM is output                                                                                                                                                                                                         |                       |

| 6       | <u>WR</u>               | Read/write selection terminal<br><u>WR</u> = "L" : Write<br><u>WR</u> = "H" : Read                                                                                                                                                                                                                       |                       |

| 11      | <u>CS</u>               | Chip select terminal<br><u>CS</u> = "L" : The S-3520CF is selected<br><u>CS</u> = "H" : <u>S<sub>OUT</sub></u> becomes high impedance                                                                                                                                                                    |                       |

| 10      | <u>PDW</u>              | Acknowledge signal input terminal of system power on.<br>Connected to power-down detection circuit. Unless PDW is used, it is fixed to high level. When <u>PDW</u> is low, it cannot be accessed regardless of <u>CS</u> , and <u>S<sub>OUT</sub></u> and <u>TP<sub>OUT</sub></u> become high impedance. |                       |

| 8       | <u>TP<sub>OUT</sub></u> | Reference signal output terminal, selected from 1Hz/1024Hz                                                                                                                                                                                                                                               |                       |

| 14      | <u>V<sub>DD</sub></u>   | Positive power supply (+ 5 V, + 3 V during backup)                                                                                                                                                                                                                                                       |                       |

| 7       | <u>V<sub>SS</sub></u>   | Negative power supply, connected to ground                                                                                                                                                                                                                                                               |                       |

| 12      | <u>C<sub>T</sub></u>    | Connects a capacitor of 0.0047 $\mu$ F between <u>V<sub>DD</sub></u> pin and <u>C<sub>T</sub></u> pin                                                                                                                                                                                                    |                       |

| 2, 13   | NC                      | Not used (set to open)                                                                                                                                                                                                                                                                                   |                       |

# REALTIME CLOCK S-3520CF

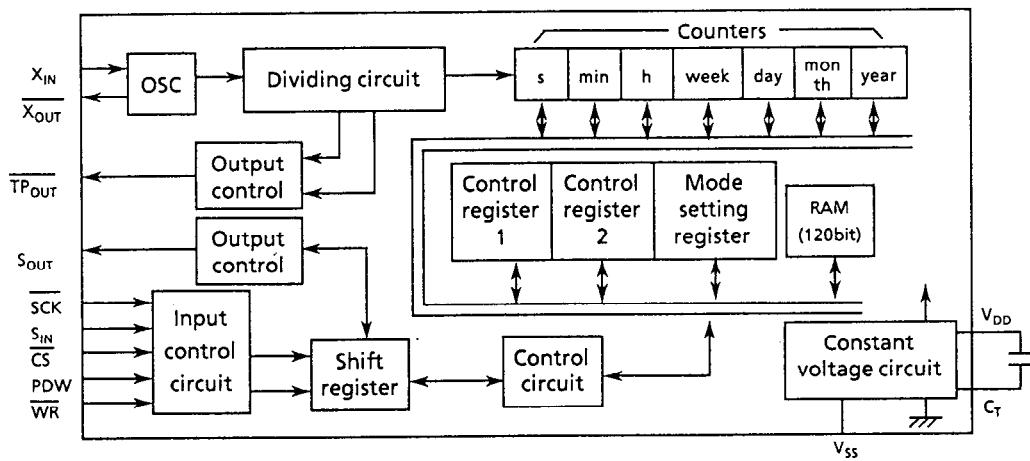

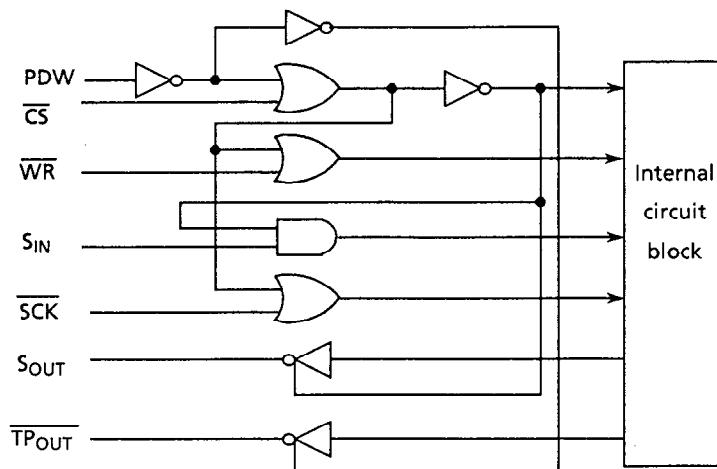

## Block Diagram

Figure 1

## Functions

### 1. Address allocation

The S-3520CF reads and modifies the contents of counters, registers, and RAMs, with 4-bit address and data in a set. Their addresses are allocated as in Table 1.

Table 1

| Address<br>(A3 to A0) | Contents                |       |       |

|-----------------------|-------------------------|-------|-------|

|                       | MODE0                   | MODE1 | MODE2 |

| 0000                  | 1-second digit counter  |       |       |

| 0001                  | 10-second digit counter |       |       |

| 0010                  | 1-minute digit counter  |       |       |

| 0011                  | 10-minute digit counter |       |       |

| 0100                  | 1-hour digit counter    |       |       |

| 0101                  | 10-hour digit counter   |       |       |

| 0110                  | Week counter            |       |       |

| 0111                  | 1-day digit counter     |       |       |

| 1000                  | 10-day digit counter    |       |       |

| 1001                  | 1-month digit counter   |       |       |

| 1010                  | 10-month digit counter  |       |       |

| 1011                  | 1-year digit counter    |       |       |

| 1100                  | 10-year digit counter   |       |       |

| 1101                  | Control register 1      |       |       |

| 1110                  | Control register 2      |       |       |

| 1111                  | Mode setting register   |       |       |

## 2. Registers

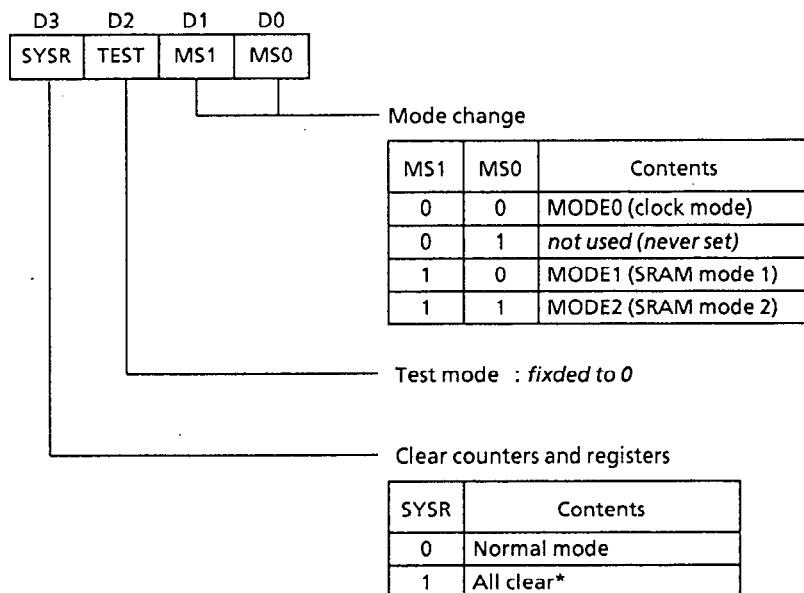

### 2.1 Mode setting register

The mode setting register changes the mode of the S-3520CF between clock mode (MODE0) and SRAM mode (MODE1 and MODE2), and resets all systems. The register data can be written and read.

#### Mode setting register (MODE, 1111)

\* Cleared contents

|           |                                                                                                |

|-----------|------------------------------------------------------------------------------------------------|

| Counters  | Year:00, month:01, day:01, hour:00**, minute:00, second:00, day of week:00                     |

| RAMs      | Data remains                                                                                   |

| Registers | Control registers 1 and 2 : 0 for all bits<br>Mode setting register : 1 for SYSR, 0 for others |

\*\* 12 is displayed.

# REALTIME CLOCK S-3520CF

## 2.2 Control register 1

The control register 1 controls the basic function of the clock mode. Register data can be written and read.

### Control register 1 (CNT1, 1101)

| D3  | D2    | D1   | D0    |

|-----|-------|------|-------|

| TPS | 30ADJ | CNTR | 24/12 |

Display mode change

| 24/12 | Contents       |

|-------|----------------|

| 0     | 12-hour system |

| 1     | 24-hour system |

Note: After the display mode is set to the 24-hour system, perform reset.

Reset counter

| CNTR | Contents      |

|------|---------------|

| 0    | Normal mode   |

| 1    | Reset setting |

The CNTR bit is not a execution bit. The contents of the counter, followed by setting this bit, are reset as follows (see ■ Operation 4.2. (2) ):

1-day or 1-month digit counters : 0001

Other counters : 0000

± 30-s adjust bit (one shot, returned within 220  $\mu$ s)

| 30ADJ | Contents                                                                                                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Normal mode                                                                                                                                                                                         |

| 1     | ± 30-s adjust<br>• When a current time is between 0 to 29 s, digits are reset without carry to min digits<br>• When a current time is between 30 to 59 s, digits are reset with carry to min digits |

Output waveform selection of reference signal

| TPS | Contents |

|-----|----------|

| 0   | 1024 Hz  |

| 1   | 1 Hz     |

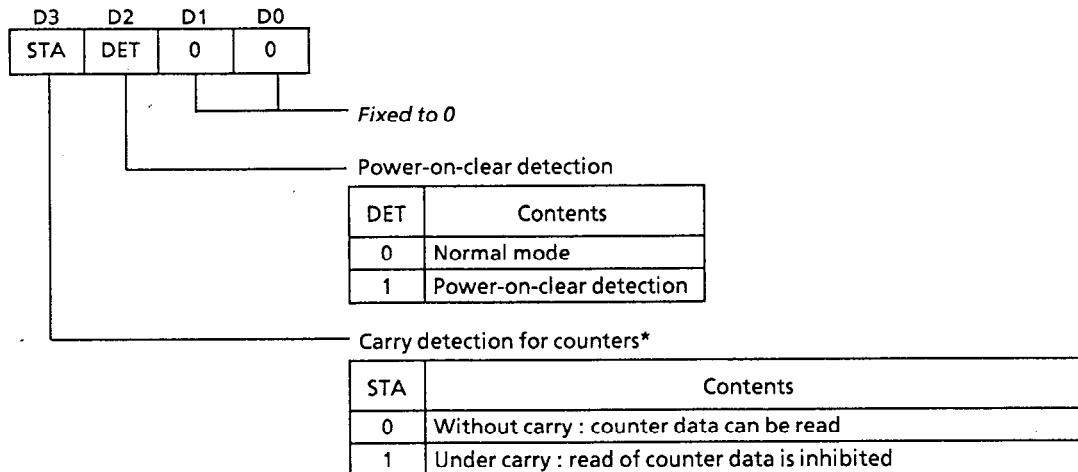

### 2.3 Control register 2

The control register 2 is a flag to detect the status in the clock mode. The register data can be only read.

#### Control register 2 (CNT2, 1110)

\* When STA is 0, no carry is executed in 3.9 ms after STA was read. If STA becomes 1 while the clock data is being read, erroneous data may be read.

## 3. Counters

This section describes counters for the clock and calendar, whose data can be read and incremented for modification.

### 3.1 Second counters

#### 1-second digit counter (sec1, 0000)

|                |                |                |                |

|----------------|----------------|----------------|----------------|

| D3             | D2             | D1             | D0             |

| S <sub>8</sub> | S <sub>4</sub> | S <sub>2</sub> | S <sub>1</sub> |

Counts 0 to 9

Data is carried to the 10-second digit counter

#### 10-second digit counter (sec10, 0001)

|    |                 |                 |                 |

|----|-----------------|-----------------|-----------------|

| D3 | D2              | D1              | D0              |

| 0  | S <sub>40</sub> | S <sub>20</sub> | S <sub>10</sub> |

Counts 0 to 5

Data is carried to the 1-minute digit counter

### 3.2 Minute counters

#### 1-minute digit counter (min1, 0010)

|                |                |                |                |

|----------------|----------------|----------------|----------------|

| D3             | D2             | D1             | D0             |

| M <sub>8</sub> | M <sub>4</sub> | M <sub>2</sub> | M <sub>1</sub> |

Counts 0 to 9

Data is carried to the 10-minute digit counter

#### 10-minute digit counter (min10, 0011)

|    |                 |                 |                 |

|----|-----------------|-----------------|-----------------|

| D3 | D2              | D1              | D0              |

| 0  | M <sub>40</sub> | M <sub>20</sub> | M <sub>10</sub> |

Counts 0 to 5

Data is carried to the 1-hour digit counter

# REALTIME CLOCK

## S-3520CF

---

### 3.3 Hour counters

#### 1-hour digit counter (hou1, 0100)

| D3             | D2             | D1             | D0             |

|----------------|----------------|----------------|----------------|

| H <sub>8</sub> | H <sub>4</sub> | H <sub>2</sub> | H <sub>1</sub> |

Counts 0 to 9

Data is carried to the 10-hour digit counter

#### 10-hour digit counter (hou10, 0101)

| D3     | D2 | D1              | D0              |

|--------|----|-----------------|-----------------|

| PM/AM* | 0  | H <sub>20</sub> | H <sub>10</sub> |

Counts 0 to 2

Data is carried to the 1-day digit and week counters

\* PM/AM is output even if time is displayed in the 24-hour system.

### 3.4 Week counter

#### Week counter (wee, 0110)

| D3 | D2             | D1             | D0             |

|----|----------------|----------------|----------------|

| 0  | W <sub>4</sub> | W <sub>2</sub> | W <sub>1</sub> |

Counts 0 to 6

\* Decide the correspondance of day of the week and counter value.

### 3.5 Day counters

#### 1-day digit counter (day1, 0111)

| D3             | D2             | D1             | D0             |

|----------------|----------------|----------------|----------------|

| D <sub>8</sub> | D <sub>4</sub> | D <sub>2</sub> | D <sub>1</sub> |

Counts 0 to 9

Data is carried to the 10-day digit counter

#### 10-day digit counter (day10, 1000)

| D3 | D2 | D1              | D0              |

|----|----|-----------------|-----------------|

| 0  | 0  | D <sub>20</sub> | D <sub>10</sub> |

Counts 0 to 3

Data is carried to the 1-month digit counter

The auto-calendar function automatically changes the maximum counter value according to the month as follows:

January, March, May, July, August, October, and December ; 31 days

April, June, September, and November ; 30 days

February ; 28 days, but 29 days in leap year

### 3.6 Month counters

#### 1-month digit counter (mon1, 1001)

| D3              | D2              | D1              | D0              |

|-----------------|-----------------|-----------------|-----------------|

| MO <sub>8</sub> | MO <sub>4</sub> | MO <sub>2</sub> | MO <sub>1</sub> |

Counts 0 to 9

Data is carried to the 10-month digit counter

#### 10-month digit counter (mon10, 1010)

| D3 | D2 | D1 | D0               |

|----|----|----|------------------|

| 0  | 0  | 0  | MO <sub>10</sub> |

Counts 0 to 1

Data is carried to the 1-year digit counter

### 3.7 Year counters

The year counters set the last 2 digits (00 to 99) of the year. They counts in liaison with the auto-calendar function until the year 2099.

#### 1-year digit counter (yea1, 1011)

| D3             | D2             | D1             | D0             |

|----------------|----------------|----------------|----------------|

| Y <sub>8</sub> | Y <sub>4</sub> | Y <sub>2</sub> | Y <sub>1</sub> |

Counts 0 to 9

Data is carried to the 10-year digit counter

#### 10-year digit counter (yea10, 1100)

| D3              | D2              | D1              | D0              |

|-----------------|-----------------|-----------------|-----------------|

| Y <sub>80</sub> | Y <sub>40</sub> | Y <sub>20</sub> | Y <sub>10</sub> |

Counts 0 to 9

## 4. SRAM

In MODE1 and MODE2, each of which is selected by the mode setting register, 30 × 4-bit SRAM data can be written or read. The address and data corresponds as follows.

### 4.1 MODE1

| Address | D3               | D2               | D1               | D0               |

|---------|------------------|------------------|------------------|------------------|

| 0000    | RA <sub>3</sub>  | RA <sub>2</sub>  | RA <sub>1</sub>  | RA <sub>0</sub>  |

| 0001    | RA <sub>7</sub>  | RA <sub>6</sub>  | RA <sub>5</sub>  | RA <sub>4</sub>  |

| ⋮       | ⋮                | ⋮                | ⋮                | ⋮                |

| 1101    | RA <sub>55</sub> | RA <sub>54</sub> | RA <sub>53</sub> | RA <sub>52</sub> |

| 1110    | RA <sub>59</sub> | RA <sub>58</sub> | RA <sub>57</sub> | RA <sub>56</sub> |

### 4.2 MODE2

| Address | D3                | D2                | D1                | D0                |

|---------|-------------------|-------------------|-------------------|-------------------|

| 0000    | RA <sub>63</sub>  | RA <sub>62</sub>  | RA <sub>61</sub>  | RA <sub>60</sub>  |

| 0001    | RA <sub>67</sub>  | RA <sub>66</sub>  | RA <sub>65</sub>  | RA <sub>64</sub>  |

| ⋮       | ⋮                 | ⋮                 | ⋮                 | ⋮                 |

| 1101    | RA <sub>115</sub> | RA <sub>114</sub> | RA <sub>113</sub> | RA <sub>112</sub> |

| 1110    | RA <sub>119</sub> | RA <sub>118</sub> | RA <sub>117</sub> | RA <sub>116</sub> |

## ■ Operation

### 1. Read data

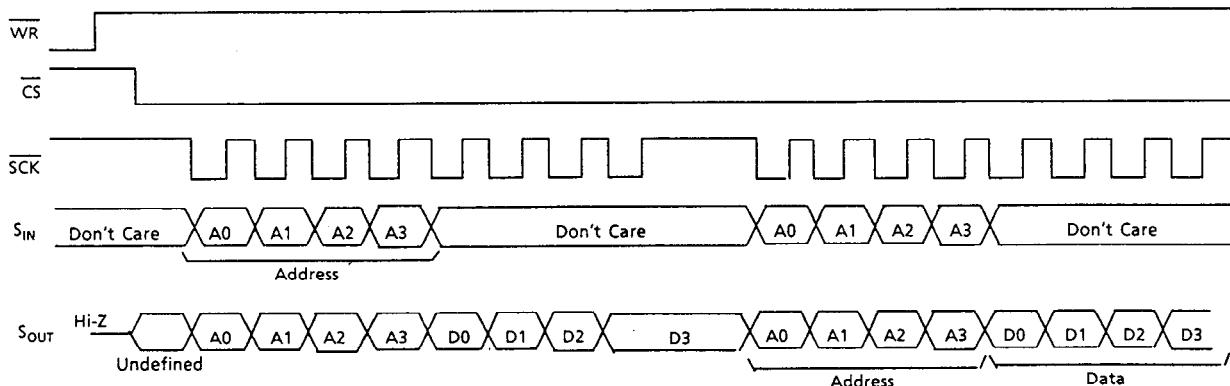

When CS goes low, and a serial address is input from S<sub>IN</sub>; the address is fetched at the rise of the SCK clock. Set high for WR to select the read mode. When WR is fetched at the rise of the 8th SCK clock, input address and data is output in the following cycle from S<sub>OUT</sub>, synchronized with the fall of the SCK clock. Figure 3 shows the read timing.

Note When the SCK clock is less than 8, the S-3520CF waits for command.

When the SCK clock is 9 or more, it executes the command for the first 8 clocks, then waits until 8 more clocks are completed.

# REALTIME CLOCK S-3520CF

Figure 3 Read timing

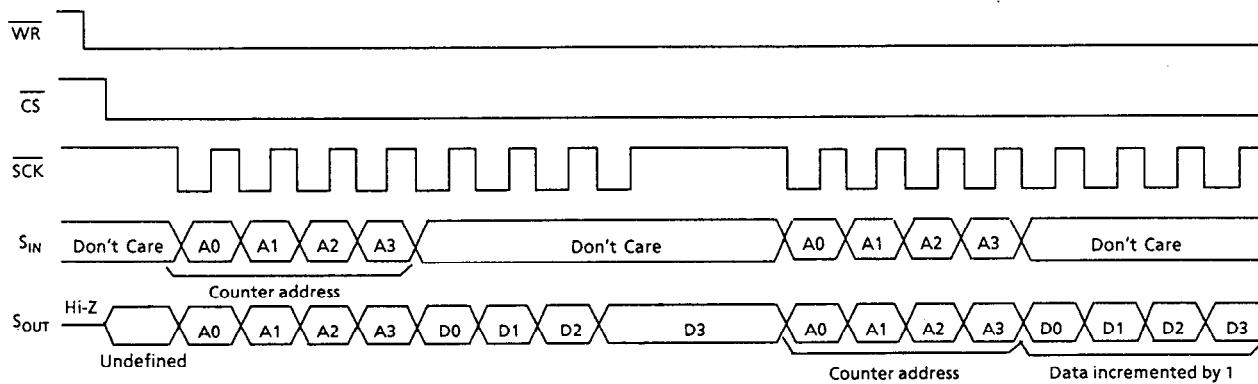

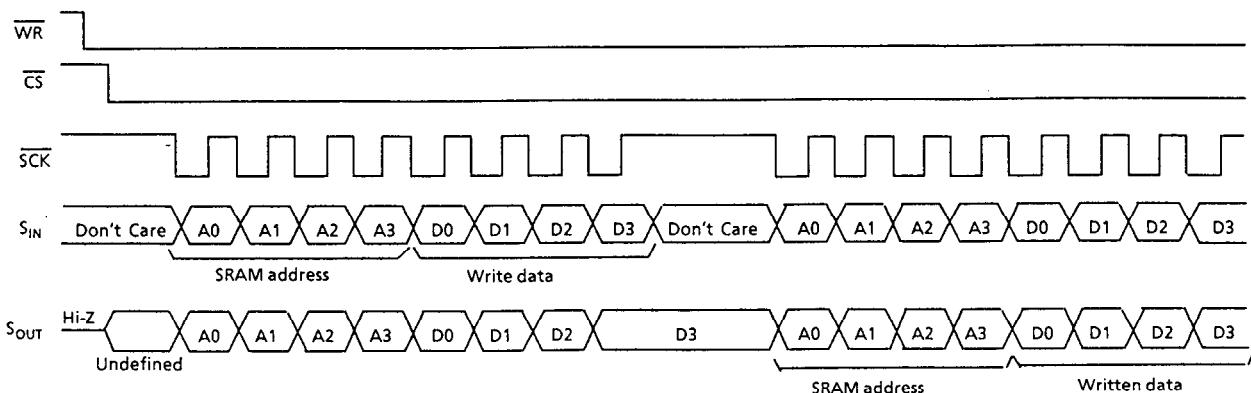

## 2. Write data

When **CS** goes low, and serial address and data (only when written into registers and SRAMs) are input from **S<sub>IN</sub>**; they are fetched at the rise of the **SCK** clock. Set low for **WR** to select the write mode. When **WR** is fetched at the rise of the 8th **SCK** clock, the following data is written in the input address.

Counters : data incremented by 1

Registers and SRAMs : 4-bit data input from **S<sub>IN</sub>**

This data is output from **S<sub>OUT</sub>** in the following cycle, synchronized with the fall of the **SCK** cycle. Figures 4 and 5 show the write timing.

Figure 4 Write timing in clock mode

Figure 5 Write timing in SRAM mode

### 3. Initializing

#### 3.1 Power-on-clear

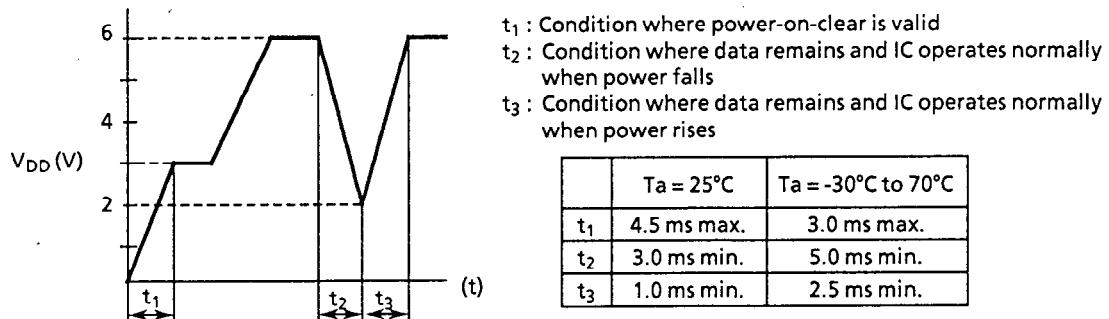

When power is applied ON, the power-on-clear function is automatically executed to initialize all the logic of the S-3520CF. When power-on-clear is valid, the DET bit (D2 of the control register 2) goes to 1. Return it to 0 by system reset and set each clock and calendar data. Figure 6 shows the conditions where power-on-clear is valid at power on, and where data remains and IC operates normally at power fluctuation.

Figure 6 Power-on-clear timing

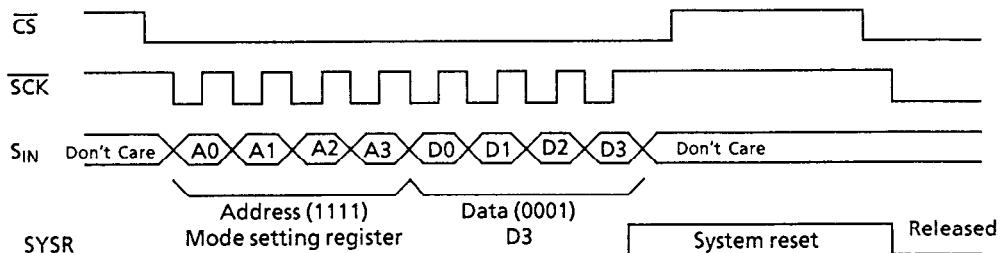

#### 3.2 System reset

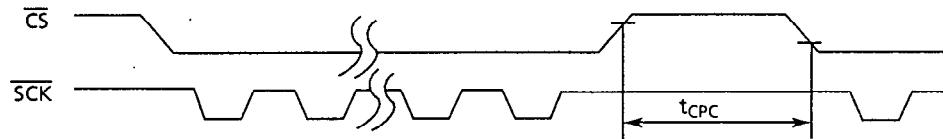

Set 1 for the SYSR bit (D3 of the mode setting register) to initialize all the logic of the S-3520CF. When releasing system reset, input SCK after rise and fall of CS as in Figure 7.

Figure 7 Reset release timing

Table 1 Status under initialization

| Item      | Power-on-clear                                                                           | System reset    |

|-----------|------------------------------------------------------------------------------------------|-----------------|

| Counters  | Year:00, month:01, day:01, hour:00 (12 on display), minute:00, second:00, day of week:00 |                 |

| SRAMs     | Data undefined                                                                           | Data remained   |

| Registers | 1 only for DET                                                                           | 1 only for SYSR |

After initialization, when in clock mode, set the initial data (see the next page 4.2) and start to count.

# REALTIME CLOCK

## S-3520CF

### 4. Clock mode

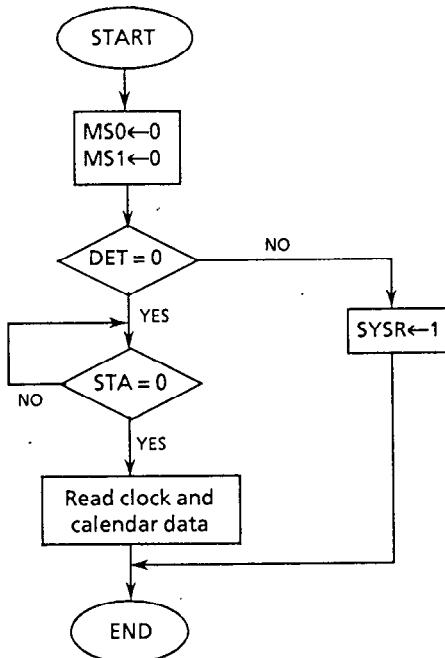

#### 4.1 Data read flowchart

1. Set the S-3520CF in clock mode (MODE0) with the lower 2 bits of the mode setting register

2. When DET is 1, reading is inhibited. Perform system reset to set 0 for DET.

3. Data cannot be read when being carried. So, check that STA is 0, which indicates that carry is not being performed.

4. Read operation starts (see "1. Read Data").

**Note** When STA is 0, no carry is executed 3.9 ms after STA was read. If STA becomes 0 while the clock data is being read, erroneous data may be read.

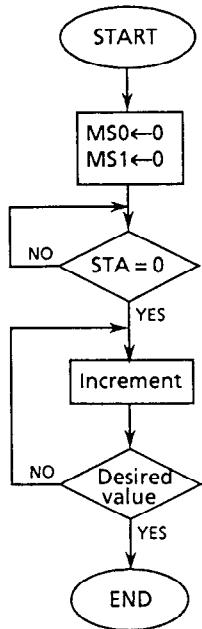

#### 4.2 Modification flowchart

There are two methods: one is increment from the current time, and another is the reset and increment from 0. After initialization, set the desired time with the latter method and start to count.

##### (1) When modifying from current time

1. Set the S-3520CF in clock mode (MODE0) with the lower 2 bits of the mode setting register.

2. Check that STA is 0, which indicates that carry is not being performed.

Reason: During modification, usual carry from the lower digit counter is accepted. If carry is generated in a 1-digit counter while a 10-digit counter is being carried, the 10-digit counter may accept both carries.

3. Increase one by one until the desired value is obtained.

##### Note

- In month and year counters, modification may have nonexistent data generated, for which the lower digits are not adjusted. In February, check whether it is in a leap year.

Example: Increment of month counters in "January (01), 31" results in "February (02), 31".

- If minute counters are modified, recommend to set 1 for 30ADJ (D2 of the control register 1) for 30-s adjust, because the second counters have great influence.

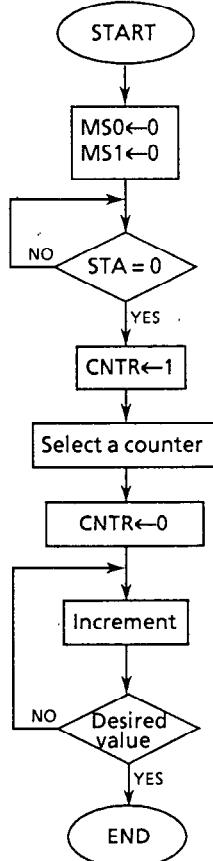

(2) When resetting and modifying from 0

1. Set the S-3520CF in clock mode (MODE0), with lower 2 bits of the mode setting register.

2. Check that STA is 0, which indicates that carry is not being performed.

Reason: During modification, usual carry from the lower digit counter is accepted. If carry is generated in a 1-digit counter while a 10-digit counter is being carried, the 10-digit counter may accept both carries.

3. Set 1 for CNTR to instruct reset of the counter value selected successively.

4. Input the address of the counter you reset.

5. Set 0 for CNTR to return into normal mode.

6. Increase one by one until the desired value is obtained.

Note

- 1-digit and 10-digit counters cannot be reset simultaneously. If both counters must reset, reset one after another.

- In case of 10 of month or 10 of day, if the 10-digit counter is reset, non-existent data such as 0 of month or 0 of day is generated. Do not fail to set data for the 1-digit counter.

- If the minute counters are modified, recommend setting 1 for 30ADJ (D2 of the control register 1) for 30-s adjust, because the second counters have great influence.

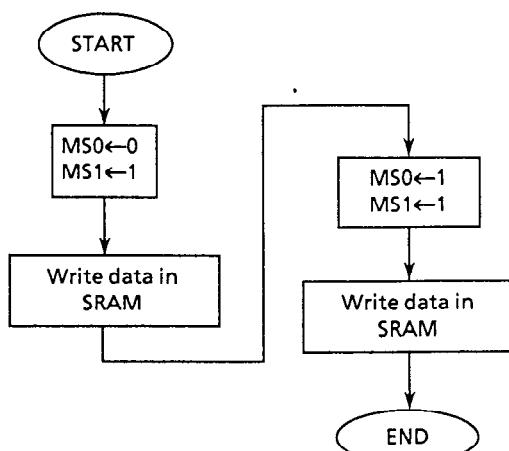

5. SRAM mode

5.1 Write operation flowchart

1. Set the S-3520CF in SRAM mode 1 (MODE1, RA0 to RA59) with the lower 2 bits of the mode setting register.

2. Write data in 4-bit units (see "2. Write Data").

3. Operate in MODE2 (RA60 to RA119), exactly as in MODE1.

# REALTIME CLOCK S-3520CF

## 5.2 Read operation flowchart

1. Set the S-3520CF in SRAM mode 1 (MODE1, RA<sub>0</sub> to RA<sub>59</sub>) with the lower 2 bits of the mode setting register.

2. When DET is 1, reading is inhibited. Perform system reset to set 0 for DET.

3. Read data in 4-bit units (see "1. Read Data").

4. Operate in MODE2 (RA<sub>60</sub> to RA<sub>119</sub>), exactly as in MODE1.

## ■ Absolute Maximum Ratings

Table 2

Unless otherwise specified: Ta = 25°C, V<sub>SS</sub> = 0 V

| Parameter             | Symbol                           | Conditions                       | Ratings                       | Unit |

|-----------------------|----------------------------------|----------------------------------|-------------------------------|------|

| Power supply voltage  | V <sub>DD</sub> -V <sub>SS</sub> |                                  | -0.3 to + 6.5                 | V    |

| Input voltage         | V <sub>IN</sub>                  | SCK, WR, CS, PDW, C <sub>T</sub> | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage        | V <sub>OUT</sub>                 | S <sub>OUT</sub>                 | -0.3 to + 6.5                 | V    |

| Power dissipation     | P <sub>d</sub>                   |                                  | 200                           | mW   |

| Storage temperature   | T <sub>stg</sub>                 |                                  | -55 to + 125                  | °C   |

| Operating temperature | T <sub>opr</sub>                 |                                  | -30 to + 75                   | °C   |

## ■ Recommended Operating Conditions

Table 3

| Parameter             | Symbol           | Conditions | Min. | Typ. | Max. | Unit |

|-----------------------|------------------|------------|------|------|------|------|

| Power supply voltage  | V <sub>DD</sub>  |            | 4.0  | 5.0  | 6.0  | V    |

| Operating temperature | T <sub>opr</sub> |            | -30  | —    | 75   | °C   |

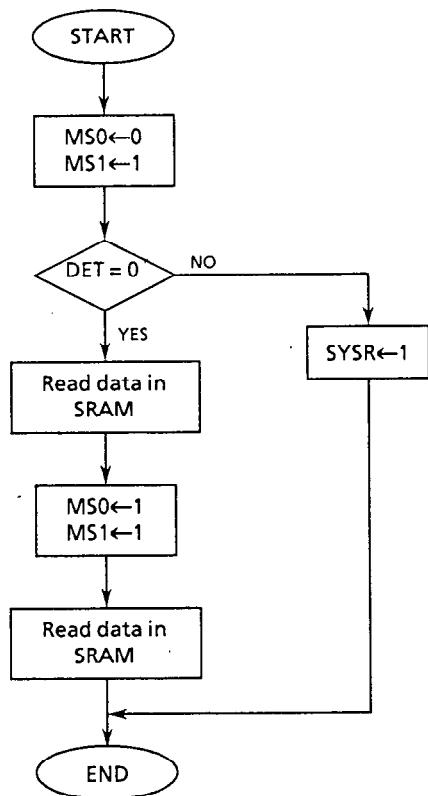

## ■ DC Electrical Characteristics

Table 4

Unless otherwise specified :  $T_a = -30^\circ\text{C}$  to  $+75^\circ\text{C}$ ,

$V_{DD} = 5\text{ V} \pm 10\%$ ,  $V_{SS} = 0\text{ V}$ ,  $C_G = 12\text{ pF}$

Crystal : DS-VT-200 (32.768 kHz,  $CL = 6\text{ pF}$ ,  $\pm 20\text{ ppm}$ ) of

Seiko Instruments Inc,

| Parameter                               | Symbol          | Conditions                                              | Min.                | Typ. | Max.                | Unit          | Circuit |

|-----------------------------------------|-----------------|---------------------------------------------------------|---------------------|------|---------------------|---------------|---------|

| Power supply voltage                    | $V_{DD}$        |                                                         | 3.0                 | 5.0  | 6.0                 | V             | 1       |

| Data retention voltage                  | $V_{DH}$        |                                                         | 2.0                 | —    | 6.0                 | V             | 1       |

| Current consumption                     | $I_{DD1}$       | $SCK = 500\text{ kHz}$                                  | —                   | 30   | 100                 | $\mu\text{A}$ | 3       |

|                                         | $I_{DD2}$       | $SCK = V_{DD}$                                          | —                   | 2.0  | 3.0                 | $\mu\text{A}$ | 2       |

| High level output voltage               | $V_{OH1}$       | CMOS: $I_{OH} = -100\text{ }\mu\text{A}$                | $V_{DD} - 0.3$      | —    | —                   | V             | 6       |

|                                         | $V_{OH2}$       | TTL: $I_{OH} = -400\text{ }\mu\text{A}$                 | 2.4                 | —    | —                   | V             | 6       |

| Low level output voltage                | $V_{OL1}$       | CMOS: $I_{OL} = 100\text{ }\mu\text{A}$                 | —                   | —    | 0.1                 | V             | 6       |

|                                         | $V_{OL2}$       | TTL: $I_{OL} = 1.6\text{ mA}$                           | —                   | —    | 0.4                 | V             | 6       |

| Output leakage current                  | $I_{OZH}$       | $V_{OUT} = 5.5\text{ V}$                                | -2.0                | —    | 2.0                 | $\mu\text{A}$ | 4       |

|                                         | $I_{OZL}$       | $V_{OUT} = 0\text{ V}$                                  | -2.0                | —    | 2.0                 | $\mu\text{A}$ | 4       |

| Input voltage                           | $V_{IH}$        |                                                         | $0.8 \times V_{DD}$ | —    | —                   | V             | 1       |

|                                         | $V_{IL}$        |                                                         | —                   | —    | $0.2 \times V_{DD}$ | V             | 1       |

| Input leakage current                   | $I_{IZH}$       | $V_{IN} = 5.5\text{ V}$                                 | -2.0                | —    | 2.0                 | $\mu\text{A}$ | 5       |

|                                         | $I_{IZL}$       | $V_{IN} = 0\text{ V}$                                   | -2.0                | —    | 2.0                 | $\mu\text{A}$ | 5       |

| Oscillation start time                  | $t_s$           | $T_a = 25^\circ\text{C}$                                | —                   | —    | 3                   | S             | 3       |

| Oscillation start voltage               | $V_{STR}$       | $t_s = 10\text{ s}$ , $T_a = 25^\circ\text{C}$          | 2.0                 | —    | —                   | V             | 3       |

| Oscillation frequency deviation         | $\Delta f_{IC}$ | Deviation between ICs, $T_a = 25^\circ\text{C}$         | -15                 | —    | 15                  | ppm           | 3       |

| Oscillation frequency-voltage deviation | $\Delta f_V$    | $V_{DD} = 2$ to $6\text{ V}$ , $T_a = 25^\circ\text{C}$ | -5                  | —    | 5                   | ppm           | 3       |

| High/low range                          | —               | $C_G = 5$ to $30\text{ pF}$                             | 30                  | —    | —                   | ppm           | 3       |

| External capacity of oscillator         | $C_G$           |                                                         | 3                   | 11   | 35                  | $\text{pF}$   | —       |

| Built-in capacity of oscillator         | $C_D$           |                                                         | —                   | 13.4 | —                   | $\text{pF}$   | —       |

## ■ Measuring Circuits

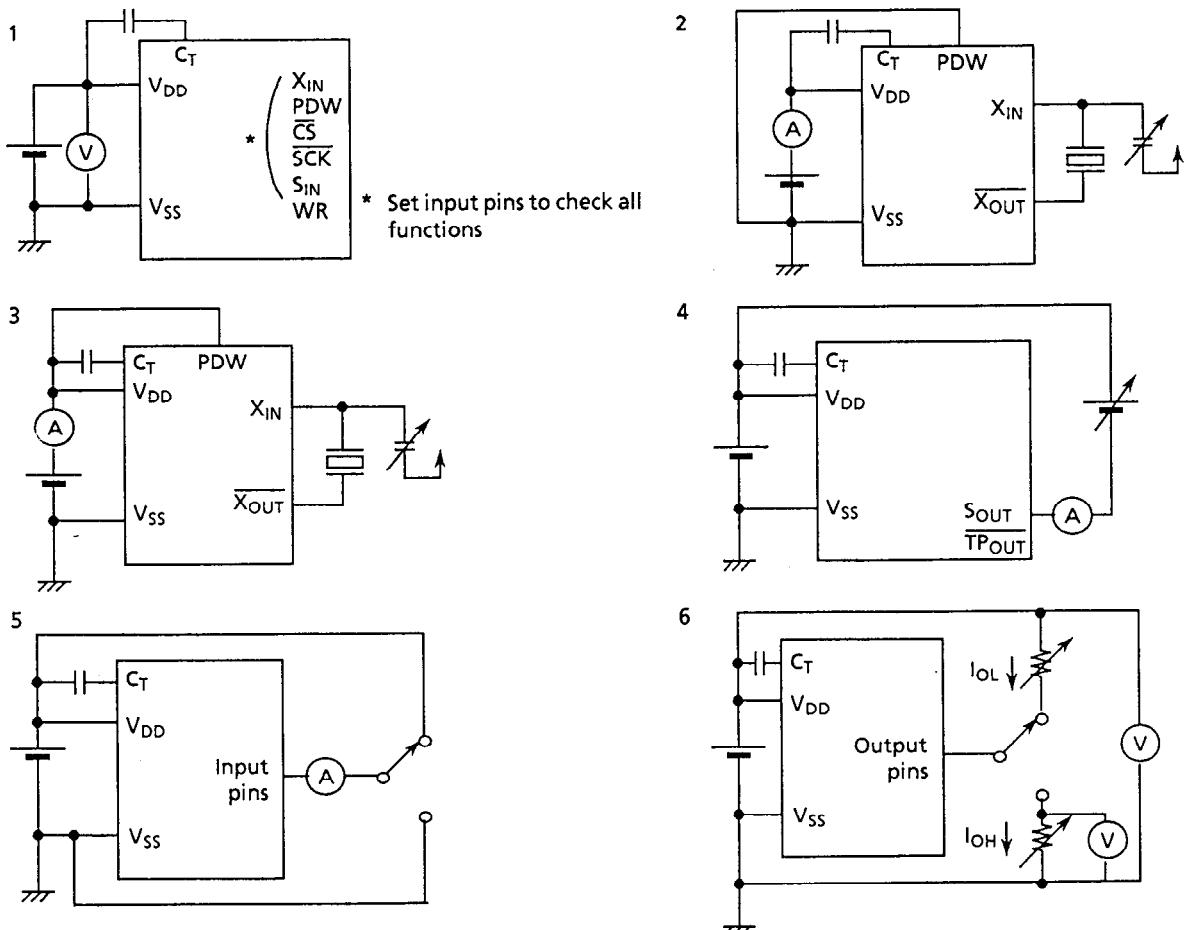

■ AC Electrical Characteristics

Table 5

Unless otherwise specified :

$V_{DD} = 5 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $T_a = -30^\circ\text{C}$  to  $+75^\circ\text{C}$ ,  $C_G = 12 \text{ pF}$

Input pins :  $V_{IH} = 0.8 \times V_{DD}$ ,  $V_{IL} = 0.2 \times V_{DD}$

Output pins :  $V_{OH} = 0.8 \times V_{DD}$ ,  $V_{OL} = 0.2 \times V_{DD}$

| Parameter                                           | Symbol     | Conditions            | Min. | Typ. | Max. | Unit          | Chart |

|-----------------------------------------------------|------------|-----------------------|------|------|------|---------------|-------|

| SCK period                                          | $t_{SCK}$  |                       | 2.0  | —    | —    | $\mu\text{s}$ | 1     |

| Low period of SCK                                   | $t_{SCKL}$ |                       | 1.0  | —    | —    | $\mu\text{s}$ | 1     |

| High period of SCK                                  | $t_{SCKH}$ |                       | 1.0  | —    | —    | $\mu\text{s}$ | 1     |

| Time from fall of CS to fall of SCK                 | $t_{CSL}$  |                       | 5.0  | —    | —    | $\mu\text{s}$ | 1     |

| Time from rise of SCK to rise of CS                 | $t_{CSH}$  |                       | 220  | —    | —    | $\mu\text{s}$ | 1     |

| $S_{IN}$ setup time                                 | $t_{SSET}$ |                       | 1.0  | —    | —    | $\mu\text{s}$ | 1     |

| $S_{IN}$ hold time                                  | $t_{SHOL}$ |                       | 1.0  | —    | —    | $\mu\text{s}$ | 1     |

| WR setup time                                       | $t_{WSET}$ |                       | 5.0  | —    | —    | $\mu\text{s}$ | 1     |

| WR hold time                                        | $t_{WHOL}$ |                       | 5.0  | —    | —    | $\mu\text{s}$ | 1     |

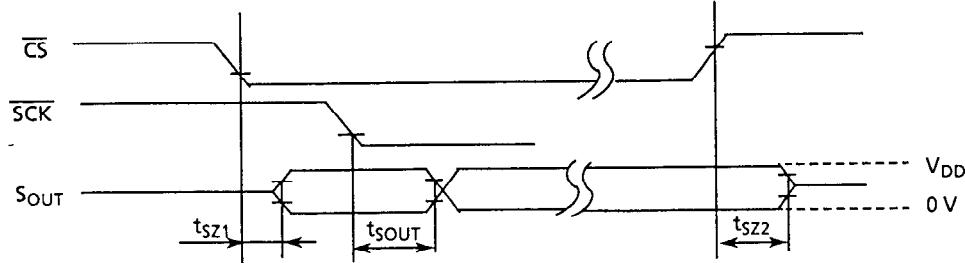

| Time from fall of SCK to $S_{OUT}$ output           | $t_{SOUT}$ | $CL = 100 \text{ pF}$ | —    | 300  | 500  | ns            | 2     |

| Time from fall of CS to $S_{OUT}$ output            | $t_{SZ1}$  | $CL = 100 \text{ pF}$ | —    | —    | 100  | ns            | 2     |

| Time from rise of CS to $S_{OUT}$ output            | $t_{SZ2}$  | $CL = 100 \text{ pF}$ | —    | —    | 100  | ns            | 2     |

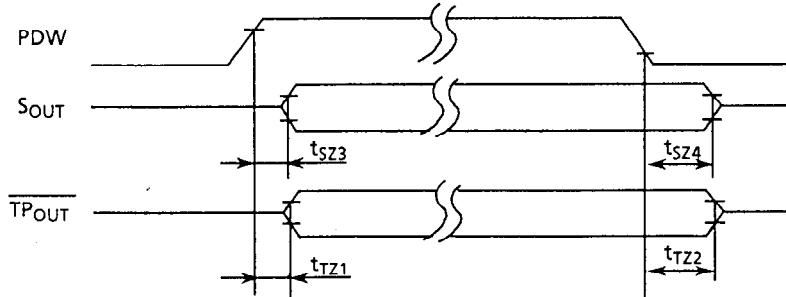

| Time from rise of PDW to $S_{OUT}$ output           | $t_{SZ3}$  | $CL = 100 \text{ pF}$ | —    | —    | 100  | ns            | 3     |

| Time from fall of PDW to High-Z of $S_{OUT}$        | $t_{SZ4}$  | $CL = 100 \text{ pF}$ | —    | —    | 100  | ns            | 3     |

| Time from rise of PDW to $\bar{T}_{POUT}$ output    | $t_{TZ1}$  | $CL = 100 \text{ pF}$ | —    | —    | 100  | ns            | 3     |

| Time from fall of PDW to High-Z of $\bar{T}_{POUT}$ | $t_{TZ2}$  | $CL = 100 \text{ pF}$ | —    | —    | 100  | ns            | 3     |

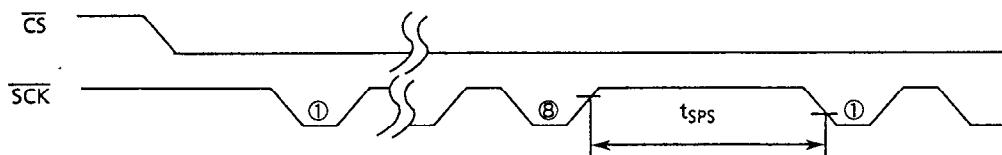

| CS pause time                                       | $t_{SPS}$  |                       | 220  | —    | —    | $\mu\text{s}$ | 4     |

| CS pause time (at system reset release)             | $t_{CPC}$  |                       | 2.0  | —    | —    | $\mu\text{s}$ | 5     |

• Timing chart 1 : basic operation

• Timing chart 2 :  $S_{OUT}$  output

• Timing chart 3 : power down

• Timing chart 4 : pause time

• Timing chart 5 : system reset release

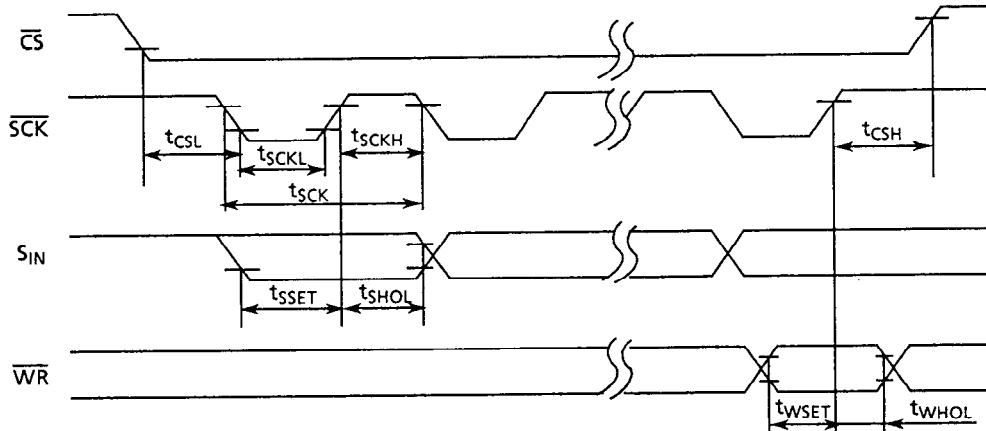

## ■ Application Circuit Design

### 1. Peripheral circuit of PDW and $\overline{CS}$

When PDW is low, any input cannot be accepted, and SOUT and  $\overline{TPOUT}$  become high impedance.

When PDW and  $\overline{CS}$  are high, any input cannot be accepted, and SOUT becomes high impedance. Figure 8 shows the internal circuits of the input block of PDW and  $\overline{CS}$ .

Figure 8

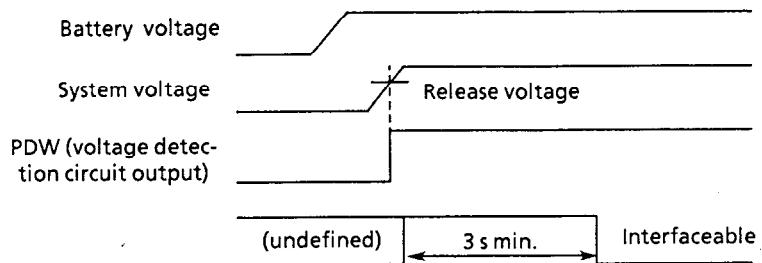

### 2. When using a single power source

After power turns on, the S-3520CF can interface with CPU according to the timing of Figure 9. That is, after PDW goes high,  $\overline{CS}$  stays high for 3 s min. until the oscillation circuit rises. Then,  $\overline{CS}$  goes low to start interfacing.

## REALTIME CLOCK S-3520CF

Figure 9

**Note** When PDW is low, keep PDW in a high or low status, never in a floating status. If PDW is in a floating status, a through-type current may flow to hasten current deterioration.

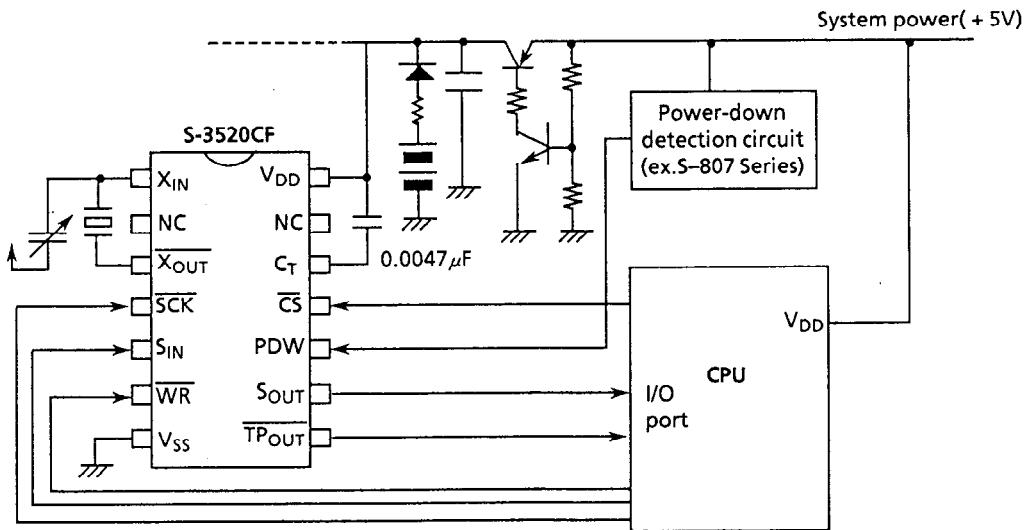

### 3. When using two power sources

Figure 10 shows an example circuit using two power sources.

Figure 10

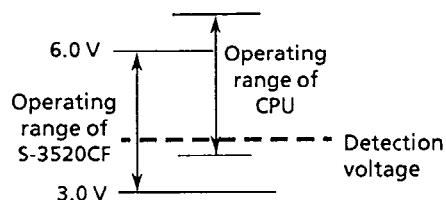

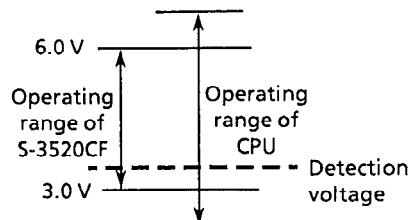

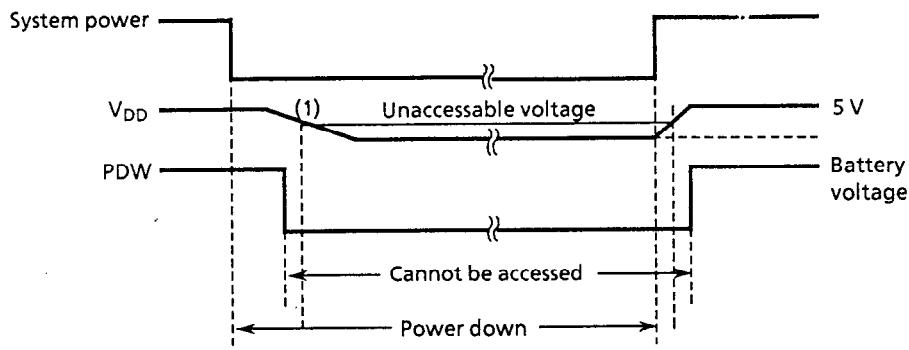

When using the S-3520CF with system power and backup battery power, power-down detection and power supply voltage range where the S-3520CF can interface with a CPU is 3.0 to 6.0 V. To prevent a malfunction, design a circuit so that the S-3520CF cannot be accessed when  $V_{DD}$  is higher than 3.0 V and higher than the minimum operating voltage of the CPU (see Figure 11). As in Figure 12 on the next page, moreover, design so that the PDW goes low before  $V_{DD}$  falls to (1) and goes high after system power returns and  $V_{DD}$  rises to (1).

(1) Minimum operating voltage of the CPU  $\geq 3.0$  V

(2) Minimum operating voltage of the CPU  $< 3.0$  V

Figure 11 Setting of detection voltage at power down of system power

Figure 12

Note When interfacing with the CPU, system power is down (battery power is on) to send the PDW low, data under accessing is invalid. When the system power is restored, a data output from SOUT in a cycle just after PDW goes high is undefined.

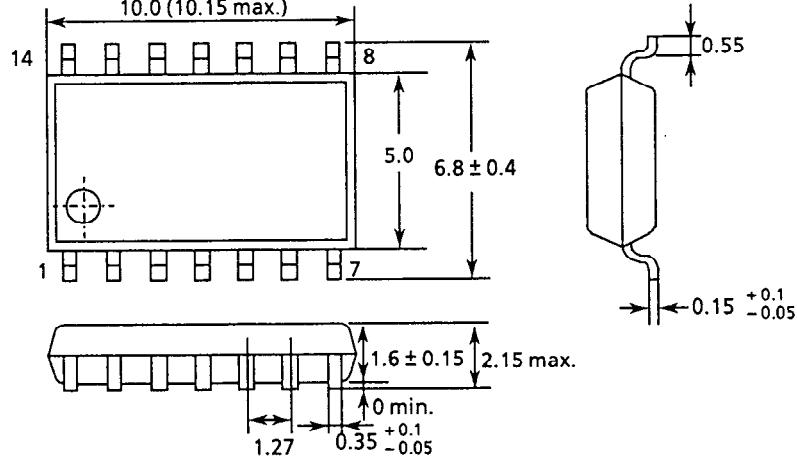

#### ■ Dimensions

14-pin SOP

Figure 13