S1T8825

### INTRODUCTION

The S1T8825 is a high performance dual frequency synthesizer with two integrated high frequency pre-scalers for RF operation up to 1.1 GHz.

The S1T8825 is composed of modulus pre-scalers providing 64 and 66, no dead-zone PFD, selectable charge pump current, selectable power down mode circuits, lock detector output, and loop filter's time constant switch.

It is fabricated using the ASP5HB Bi-CMOS process and is available 16-TSSOP with surface mount plastic packaging. Serial data is transferred into the S1T8825 via three-wire interface (CK, DATA, EN).

#### **FEATURES**

- Two systems for receiver and transmitter

- Very low operating current consumption: Icc = Typ. 5.5mA @ 3.0V

- Low operating power supply voltage: 2.2 ~ 5.5V (200MHz ~ 550MHz Operating)

2.7 ~ 3.6V (550MHz ~ 1.1GHz Operating)

- Modulus pre-scaler: 64 / 66

- No dead-zone PFD

- Colpitts type local oscillation

- Selectable charge pump current

- · Selectable power down mode

- TSSOP 16-pin package (0.65 mm pitch)

### ORDERING INFORMATION

| Device           | Package       | Operating Temperature |

|------------------|---------------|-----------------------|

| +S1T8825X01-R0B0 | 16-TSSOP-0044 | −30 °C to +85 °C      |

+: New Product

#### **APPLICATIONS**

- Cordless telephone systems

- Portable wireless communications (PCS)

- Wireless Local Area Networks (WLANs)

- Other wireless communication systems

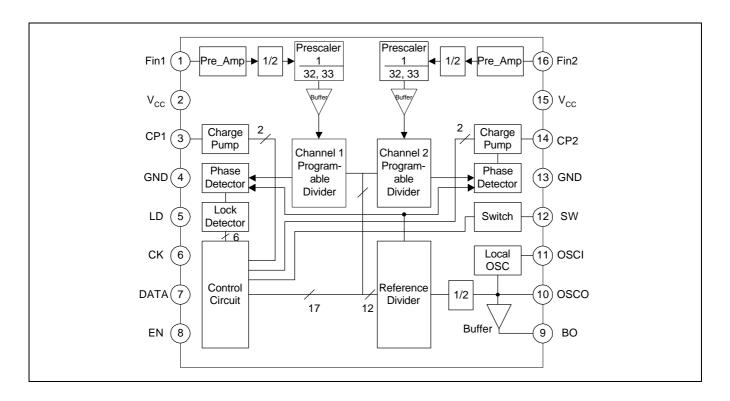

# **BLOCK DIAGRAM**

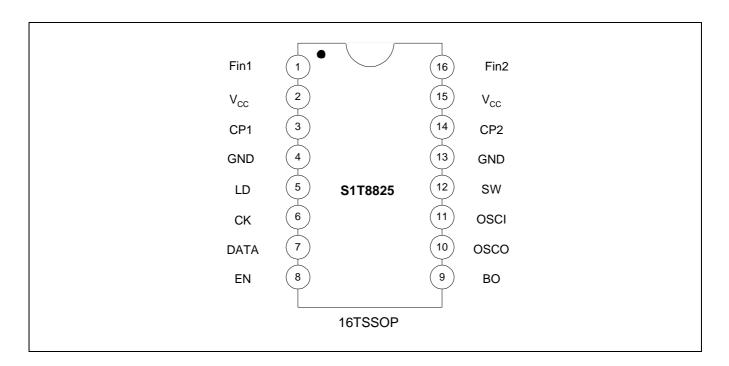

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| Pin No. | Symbol | I/O | Description                                                                                                                                                               |

|---------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Fin1   | ı   | Input terminal of channel 1 RF signal.                                                                                                                                    |

| 2, 15   | Vcc    | _   | Power supply voltage input. PIN2 and PIN15 are connected together.                                                                                                        |

| 3       | CP1    | 0   | Output terminal of channel 1 charge pump. Charge pump is constant current output circuit, and output current is selected by input serial data.                            |

| 4, 13   | GND    | -   | Terminal of GND. PIN4 and PIN13 are connected together.                                                                                                                   |

| 5       | LD     | 0   | Output terminal of lock detection. It is the open drain output.                                                                                                           |

| 6       | СК     | I   | Input terminal of clock.                                                                                                                                                  |

| 7       | DATA   | I   | Input terminal of data.                                                                                                                                                   |

| 8       | EN     | I   | Input terminal of enable signal.                                                                                                                                          |

| 9       | ВО     | 0   | Output terminal of buffer amplifier. The signal of local oscillation is output through the buffer amplifier.                                                              |

| 10      | osco   | 0   | Output terminal of local oscillation signal.                                                                                                                              |

| 11      | OSCI   | I   | Input terminal of local oscillation signal. In case of external input, connecting it to this terminal.                                                                    |

| 12      | SW     | 0   | Switch-over terminal for the time constant of loop filter. It is an open drain output. If you don't switch the time constant of loop filter, general output is available. |

| 14      | CP2    | 0   | Output terminal of channel 2 charge pump. Charge pump is a constant current output circuit, and the output current is selected by input serial data.                      |

| 16      | Fin2   | I   | Input terminal of channel 2 RF signal.                                                                                                                                    |

# **ABSOLUTE MAXIMUM RATINGS**

| Characteristic        | Symbol           | Value             | Unit |

|-----------------------|------------------|-------------------|------|

| Power Supply Voltage  | Vcc              | 6                 | V    |

| Power Dissipation     | P <sub>D</sub>   | 600               | mW   |

| Operating temperature | T <sub>OPR</sub> | −30 <b>— +</b> 85 | °C   |

| Storage temperature   | T <sub>STG</sub> | −55 <b>— 4</b> 50 | °C   |

**✓** Take care! ESD sensitive device

# **ELECTRICAL CHARACTERISTICS**

(Ta =  $25^{\circ}$ C,  $V_{CC}$  = 3V, unless otherwise specified)

| Characteristic                                | Symbol           | Test Co                       | Min.            | Тур.                  | Max.  | Unit |       |  |

|-----------------------------------------------|------------------|-------------------------------|-----------------|-----------------------|-------|------|-------|--|

| Operating power supply                        | V <sub>CC</sub>  | Fin1=Fin2= 200M               | Hz ~ 550MHz     | 2.2                   | 3.0   | 5.5  | V     |  |

| voltage                                       | V CC             | Fin1=Fin2= 550M               | 2.7             | 3.0                   | 3.6   | V    |       |  |

| Operating current consumption                 | I <sub>CC</sub>  | Fin1=Fin2=1.1GH               | Iz/ -5dBm input | 3.5                   | 5.5   | 7.5  | mA    |  |

| Standby current                               | I <sub>SB</sub>  | Standby mode                  |                 | _                     | 0     | 10   | μΑ    |  |

| Fin operating frequency                       | Fin              | Fin1 = Fin2 = -5              | dBm             | 200                   | _     | 1100 | MHz   |  |

|                                               |                  | Fin4 Fin0                     | Vcc=2.2V        | <b>– 15</b>           | _     | 0    |       |  |

|                                               |                  | Fin1 = Fin2<br>= 200MHz       | Vcc=3.0V        | <b>– 15</b>           | _     | 0    |       |  |

|                                               |                  | 20011112                      | Vcc=5.5V        | <b>– 10</b>           | _     | 0    |       |  |

|                                               |                  | F: 4 F: 0                     | Vcc=2.2V        | -15                   | _     | 0    |       |  |

| Fin input sensitivity                         | Fin              | Fin1 = Fin2<br>= 550MHz       | Vcc=3.0V        | -15                   | _     | 0    | dBm   |  |

|                                               |                  | _ 000Wii 12                   | Vcc=5.5V        | - 10                  | _     | 0    |       |  |

|                                               |                  | Fin1 = Fin2 -                 | Vcc=2.7V        | - 10                  | _     | 0    | -     |  |

|                                               |                  |                               | Vcc=3.0V        | - 10                  | _     | 0    |       |  |

|                                               |                  | Vcc=3.6V                      |                 | - 10                  | _     | 0    |       |  |

| OSCI operating frequency                      | F <sub>osc</sub> | V <sub>Fin</sub> = 0dBm, sine | ewave           | 5                     | -     | 25   | MHz   |  |

|                                               |                  |                               | Vcc = 2.2V      | - 10                  | 0     | 5    | - dBm |  |

|                                               |                  | f <sub>osc</sub> = 10MHz      | Vcc = 3.0V      | - 10                  | 0     | 5    |       |  |

| OSCI input voltage                            | V <sub>osc</sub> |                               | Vcc = 5.5V      | 0                     | -     | 5    |       |  |

| o o o o o o o o o o o o o o o o o o o         | v osc            |                               | Vcc = 2.2V      | - 10                  | 0     | 5    |       |  |

|                                               |                  | f <sub>osc</sub> = 20MHz      | Vcc = 3.0V      | - 10                  | 0     | 5    | -     |  |

|                                               |                  |                               | Vcc = 5.5V      | - 5                   | 0     | 5    |       |  |

| Serial data input high voltage (CK, DATA, EN) | V <sub>IH</sub>  | V <sub>CC</sub> = 2.2 to 5.5  | V               | V <sub>CC</sub> – 0.4 | _     | -    | V     |  |

| Serial data input low voltage (CK, DATA, EN)  | V <sub>IL</sub>  | V <sub>CC</sub> = 2.2 to 5.5  | V               | -                     | _     | 0.4  | V     |  |

| Charge pump output                            | I <sub>CP1</sub> | CP1 = 0, CP2 = 0              | VCP = 1.5 V     | _                     | ± 100 | -    | μΑ    |  |

| current                                       | I <sub>CP2</sub> | CP1 = 1, CP2 = 0              | VCP = 1.5V      | _                     | ± 200 | _    | μΑ    |  |

|                                               | I <sub>CP3</sub> | CP1 = 0, CP2 = 1              | VCP = 1.5V      | _                     | ± 400 | _    | μΑ    |  |

|                                               | I <sub>CP4</sub> | CP1 = 1, CP2 = 1              | _               | ± 800                 | _     | μΑ   |       |  |

| Charge pump leakage                           | I <sub>CPL</sub> | Standby mode, V               | /cp = 1.5V      | -1                    | -     | +1   | μΑ    |  |

#### **FUNCTIONAL DESCRIPTIONS**

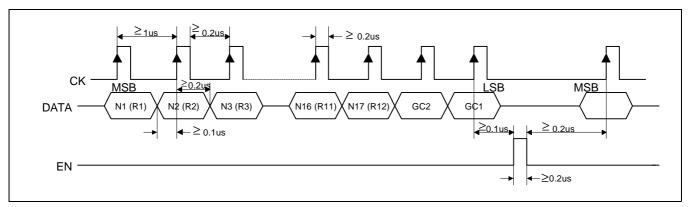

#### **SERIAL DATA INPUT AND TIMING**

CK (Pin6), DATA (Pin7), EN (Pin8) terminals in S1T8825 are used for MCU serial data interface (MSB: 1st input data; LSB: Last input data). Serial data controls the programmable reference divider, programmable divider (CH1), programmable divider (CH2), and control latch separately by means of group code. Binary serial data is entered via the DATA pin.

One bit of data is shifted into the internal shift register on the rising edge of the clock. When EN pin is high, stored data is latched. The three terminals, CK, DATA, and EN, contain Schmitt trigger circuits to keep the data from errors caused by noise, etc.

#### < Notice >

- 1. When power supply of S1T8825 is disconnected, CLK, DATA, EN port from MCU should be pulled low.

- 2. When power goes up first, R counter data should be entered earlier than N1 and N2 counter data.

- 3. When power goes up first, control data should be entered earlier than N1 and N2 counter data.

Figure 1.

NOTE: Start data input with MSB first

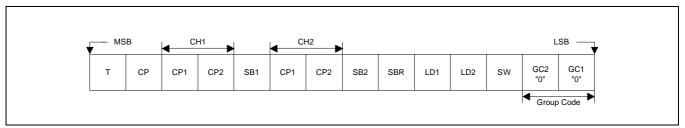

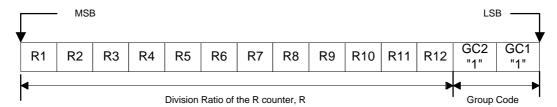

### **SERIAL DATA GROUP AND GROUP CODE**

The S1T8825 can be controlled through 4 kinds of group selection. Each group is identified by selective a 2-bit group code given below.

| Seria     | l Bits      | Group Location |

|-----------|-------------|----------------|

| GC1 (LSB) | GC2 (LSB-1) |                |

| 0         | 0           | Control Latch  |

| 0         | 1           | Ch 1 N Latch   |

| 1         | 0           | Ch 2 N Latch   |

| 1         | 1           | OSC R Latch    |

### **CONTROL LATCH**

The control register executes the following functions:

- Mode selection (H: test mode, L: normal mode)

- Charge pump's polarity and output current selection for each channel.

- Output state selection for Lock Detector.

- Standby control of each channel and reference divider.

- ON / OFF control in filter switch.

Figure 2.

| Bit         | Bit 1     | Bit 2                                | Bit 3                                            | Bit 4                                            | Bit 5                | Bit 6                                            | Bit 7                                            |

|-------------|-----------|--------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------|--------------------------------------------------|--------------------------------------------------|

| Name        | Т         | СР                                   | CP1                                              | CP2                                              | SB1                  | CP1                                              | CP2                                              |

| Description | test mode | charge<br>pump<br>output<br>polarity | channel 1<br>charge<br>pump<br>output<br>current | channel 1<br>charge<br>pump<br>output<br>current | channel 1<br>standby | channel 2<br>charge<br>pump<br>output<br>current | channel 2<br>charge<br>pump<br>output<br>current |

| Bit         | Bit 8                | Bit 9                           | Bit 10                        | Bit 11                        | Bit 12        | Bit 13            | Bit 14         |

|-------------|----------------------|---------------------------------|-------------------------------|-------------------------------|---------------|-------------------|----------------|

| Name        | SB2                  | SBR                             | LD1                           | LD2                           | SW            | GC2               | GC1            |

| Description | channel 2<br>standby | reference<br>divider<br>standby | lock<br>detector<br>control 1 | lock<br>detector<br>control 2 | filter switch | group code<br>"0" | group code "0" |

### 1.1GHZ DUAL PLL

## **CHARGE PUMP OUTPUT POLARITY (CP)**

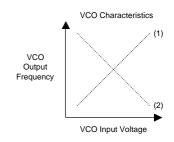

In normal operation, the CP should be "0". In reverse operation, the CP should be "1". Depending upon VCO characteristics, CP should be set accordingly; When VCO characteristics are like (1), CP should be set to low When VCO characteristics are like (2), CP should be set to high.

# **CHARGE PUMP OUTPUT CURRENT (CP1, CP2)**

The S1T8825 includes a constant current output type charge pump circuit. Output current is varied according to control bit "CP1" and "CP2". In order to get high speed lock-up, select the best charge pump output current.

| Cont | rol Bit | Charge Pump    |  |  |  |

|------|---------|----------------|--|--|--|

| CP1  | CP2     | Output Current |  |  |  |

| 0    | 0       | ± 100 μA       |  |  |  |

| 0    | 1       | ± 200 μA       |  |  |  |

| 1    | 0       | ± 400 μA       |  |  |  |

| 1    | 1       | ± 800 μA       |  |  |  |

# TEST MODE AND LOCK DETECTOR OUTPUT (T, LD1, LD2)

When T is normal "0", LD (Pin5) state is varied by controlling "SB1", "SB2", "LD1" and "LD2". When T is high "1", LD (Pin5) state is changed to be useful for test

| Т | SB1 | SB2 | LD1 | LD2 | LD Output State         |   |   |   |   |   |   |

|---|-----|-----|-----|-----|-------------------------|---|---|---|---|---|---|

|   |     |     | 0   | 0   | low                     |   |   |   |   |   |   |

|   |     | 0   | 0   | 1   | channel2                |   |   |   |   |   |   |

|   |     | U   | 1   | 0   | channel1                |   |   |   |   |   |   |

|   | 0   |     | 1   | 1   | channel1. AND. channel2 |   |   |   |   |   |   |

|   | U   |     | 0   | 0   | low                     |   |   |   |   |   |   |

|   |     | 1   | 0   | 1   | high                    |   |   |   |   |   |   |

|   |     | '   | 1   | 0   | channel1                |   |   |   |   |   |   |

|   |     |     | 1   | 1   | channel1                |   |   |   |   |   |   |

| U | 0   |     | 0   | 0   | low                     |   |   |   |   |   |   |

|   |     | _   | 0   | 1   | channel2                |   |   |   |   |   |   |

|   |     | 0   | 1   | 0   | high                    |   |   |   |   |   |   |

|   |     |     | 1   | 1   | channel2                |   |   |   |   |   |   |

|   | 1   |     | 0   | 0   | low                     |   |   |   |   |   |   |

|   |     | 1   | 0   | 1   | high                    |   |   |   |   |   |   |

|   |     |     | ı   | ı   | 1                       | ' | ' | ' | ' | 1 | 0 |

|   |     |     | 1   | 1   | high                    |   |   |   |   |   |   |

|   |     |     | 0   | 0   | low                     |   |   |   |   |   |   |

|   | 4   | _   | 0   | 1   | pres2                   |   |   |   |   |   |   |

|   | 1   | 0   | 1   | 0   | fpll2                   |   |   |   |   |   |   |

|   |     |     | 1   | 1   | fref                    |   |   |   |   |   |   |

| _ |     |     | 0   | 0   | div4                    |   |   |   |   |   |   |

| 1 |     | 4   | 0   | 1   | pres1                   |   |   |   |   |   |   |

|   | 0   | 1   | 1   | 0   | fpll1                   |   |   |   |   |   |   |

|   |     |     | 1   | 1   | fosc/2                  |   |   |   |   |   |   |

|   | 1   | 1   | ×   | ×   | low                     |   |   |   |   |   |   |

|   | 0   | 0   | ×   | ×   | low                     |   |   |   |   |   |   |

S1T8825

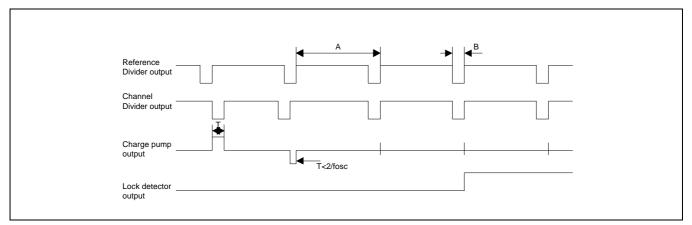

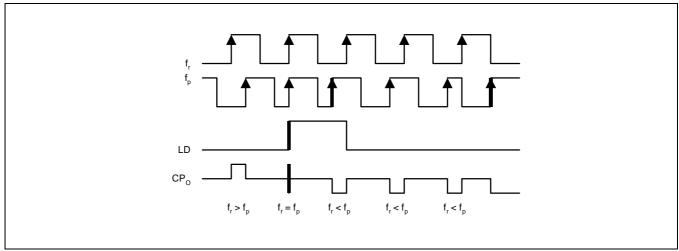

#### LOCK DETECTOR OUTPUT

When the phase comparator detects a phase difference, LD (Pin5) outputs "L".

When the phase comparator locks, LD outputs "H". On standby, it outputs "H".

When T is less than 2/fosc (T<2 /fosc ) for more than three cycles of reference divider output as in the figure below, the lock detector outputs "H".

**Figure 3. Lock Detector Output**

fosc: OSCI operating frequency (LOCAL OSC).

T: time difference of the pulse between reference divider output and channel divider output.

$$A = \frac{\text{Number of divisions by reference divider}}{\text{fosc}}$$

(s)

$$B = \frac{2}{\text{fosc}}$$

(s)

## PROGRAMMABLE STANDBY MODE (SB1, SB2, SBR)

Standby mode can be controlled by 3-control bits such as SB1, SB2 and SBR. SB1 and SB2 can control the standby mode of channel 1 and channel 2. The "SBR" bit can do ON / OFF control of reference divider.

|     | Control Bi | t   | Standby Mode State |     |     |                    |  |

|-----|------------|-----|--------------------|-----|-----|--------------------|--|

| SB1 | SB2        | SBR | CH1                | CH2 | REF | Mode Status        |  |

| 0   | 0          | ×   | ON                 | ON  | ON  | Inter locking Mode |  |

| 0   | 1          | ×   | ON                 | OFF | ON  | CH1 Locking Mode   |  |

| 1   | 0          | ×   | OFF                | ON  | ON  | CH2 Locking Mode   |  |

| 1   | 1          | 0   | OFF                | OFF | ON  | REF On Mode        |  |

| 1   | 1          | 1   | OFF                | OFF | OFF | Standby Mode       |  |

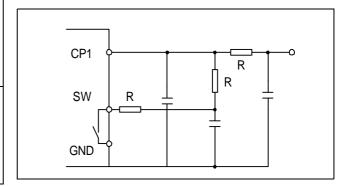

### **FILTER SWITCH CONTROL (SW)**

The operation mode of the SW terminal is set by bit "SW".

SW control is useful for switching the time constant of the loop filter.

Output type of this terminal is an open drain output. High lock mode or normal lock mode can be used, taking advantage of filter switch control (SW) with the charge pump output current.

When fast lock function can't be used, normal lock mode is available.

| Operation Mode     | ts  | ontrol Bi | C  |

|--------------------|-----|-----------|----|

|                    | CP2 | CP1       | SW |

|                    | 0   | 0         | 0  |

| Normal Lock Mode   | 1   | 0         | 0  |

| NOTHIAI LOCK WICKE | 0   | 1         | 0  |

|                    | 1   | 1         | 0  |

|                    | 0   | 0         | 1  |

| High Lock Mode     | 1   | 0         | 1  |

| High Lock Mode     | 0   | 1         | 1  |

|                    | 1   | 1         | 1  |

(SW and LPF example) The third order LPF

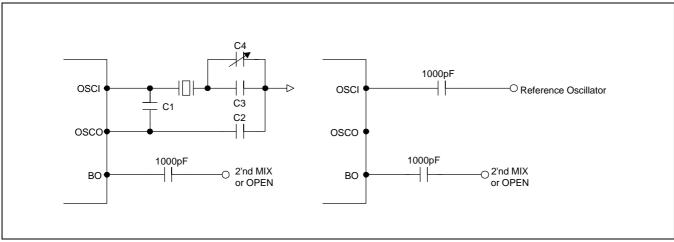

# CRYSTAL OSCILLATOR CIRCUIT (OSCI, OSCO) AND BUFFER OUT (BO)

External capacitors C1, C2, C3, and C4 are required to set the proper crystal's load capacitance and oscillation frequency as shown in figure 4. The value of the capacitors is dependent on the crystal chosen.

The BO (Pin9) outputs local oscillation signal with buffer amplifier.

This terminal (Pin9) can be applied to the 2nd mixer input

Figure 4.

1.1GHZ DUAL PLL S1T8825

## PROGRAMMABLE REFERENCE COUNTER

This block generates the reference frequency for the PLL.

The reference divider is composed of 12-bit reference divider and a half fixed divider

Sending certain data to the reference divider allows the setting of any of 6 to 8190 divisions (multiple of two).

$$R = R1 \times 2^0 + R2 \times 2^1 + ... + R12 \times 2^{11}$$

Division ratio:  $2 \times R = 2 \times (3 \sim 4095) = 6 \sim 8190$

Data is shifted in MSB first.

| Division<br>Ratio | R12 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 |

|-------------------|-----|-----|-----|----|----|----|----|----|----|----|----|----|

| 3                 | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 4                 | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| •                 | •   | •   | •   | •  | •  | •  | •  | •  | •  | •  | •  | •  |

| 4095              | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Example) A 21.25MHz X-tal oscillator is connected, and divided into 25kHz steps. (Reference frequency is 12.5kHz)

$$21.25 \text{ MHz} \div 12.5 \text{ kHz} = 1700$$

$$1700 = 2 \times R$$

$$R = (850)_{10} = (1101010010)_2$$

| MSB |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|     | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

11

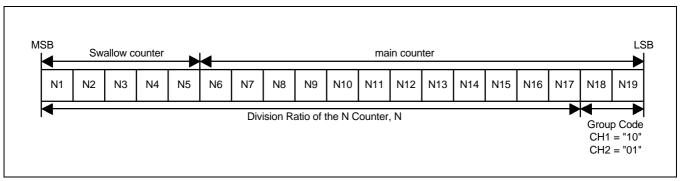

## **CHANNEL 1, CHANNEL 2 PROGRAMMABLE N COUNTER**

These programmable dividers are composed of a 5-bit swallow counter (5-bit programmable divider),

12-bit programmable main counter, and two-modulus prescalers providing 64 and 66 divisions.

Sending certain data to the swallow counter and the 12-bit programmable main counter allows the setting of any of 2048 to 262142 divisions (multiple of two).

The 12-bit programmable divider and swallow counter are set by each channel; each channel is identified by a group code.

Figure 5.

## 5-BIT SWALLOW COUNTER DIVISION RATIO (A COUNTER)

$A = N1 \times 2^0 + N2 \times 2^1 \dots N5 \times 2^4$ Division ratio: 0 to 31,  $B \ge A$

| Division Ratio (A) | N5 | N4 | N3 | N2 | N1 |

|--------------------|----|----|----|----|----|

| 0                  | 0  | 0  | 0  | 0  | 0  |

| 1                  | 0  | 0  | 0  | 0  | 1  |

| •                  | •  | •  | •  | •  | •  |

| 31                 | 1  | 1  | 1  | 1  | 1  |

# 12-BIT MAIN COUNTER DIVISION RATIO (B COUNTER)

$\mathsf{B} = \mathsf{N6} \times \mathsf{2^0} + \mathsf{N7} \times \mathsf{2^1} + \mathsf{N7} \times \mathsf{2^2} \ldots \, \mathsf{N17} \times \mathsf{2^{11}}$

Division ratio: 3 to 4095 Data is shifted in MSB first

| Division<br>Ratio (B) | N17 | N16 | N15 | N14 | N13 | N12 | N11 | N10 | N9 | N8 | N7 | N6 |

|-----------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|

| 3                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 1  | 1  |

| 4                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  |

| •                     | •   | •   | •   | •   | •   | •   | •   | •   | •  | •  | •  | •  |

| 4095                  | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  |

1.1GHZ DUAL PLL S1T8825

Channel1 and 2 Programmable Counter Division Ratio, N

$N = 2 \times (32 \times B + A), B \ge A$ Division ratio: 192 ~ 262142

Example) A Signal of 453 MHz is entered into Fin1, and divided into 25 kHz steps.

(Reference frequency is 12.5 kHz)

453 MHz ÷ 12.5 kHz = 36240

$36240 = 2 \times (32 \times B + A)$

$\therefore$  B =  $(1132)_{10}$  =  $(10001101100)_2$ , A =  $(16)_{10}$  =  $(10000)_2$

| MSB |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | LSB |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| 0   | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0   |

Example) A Signal of 462.9 MHz is entered into Fin2, and divided into 25 kHz step.

(Reference frequency is 12.5 kHz)

$462.9 \text{ MHz} \div 12.5 \text{ kHz} = 37032$

$37032 = 2 \times (32 \times B + A)$

$\therefore$  B = (1157)<sub>10</sub> = (10010000101)<sub>2</sub>, A = (8)<sub>10</sub> = (01000)<sub>2</sub>

| MSB |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | LSE | , |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|---|

| 0   | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1   |   |

#### PHASE DETECTOR AND CHARGE PUMP CHARACTERISTICS

Phase difference detection Range: -2  $\pi$  ~ +2  $\pi$

When SW = Low

Figure 6.

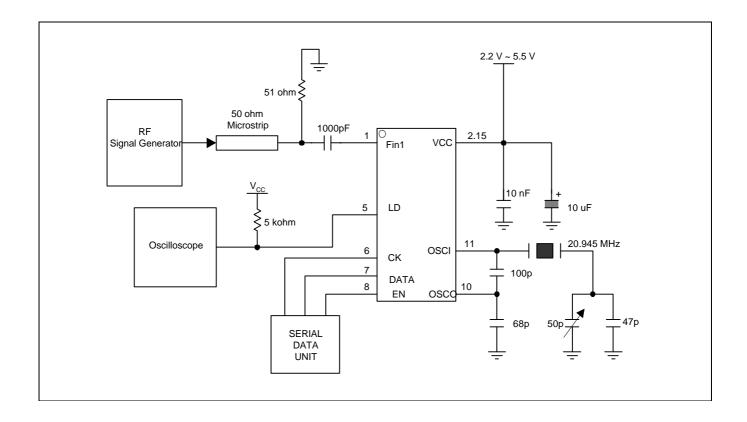

# **SENSITIVITY TEST CIRCUIT**

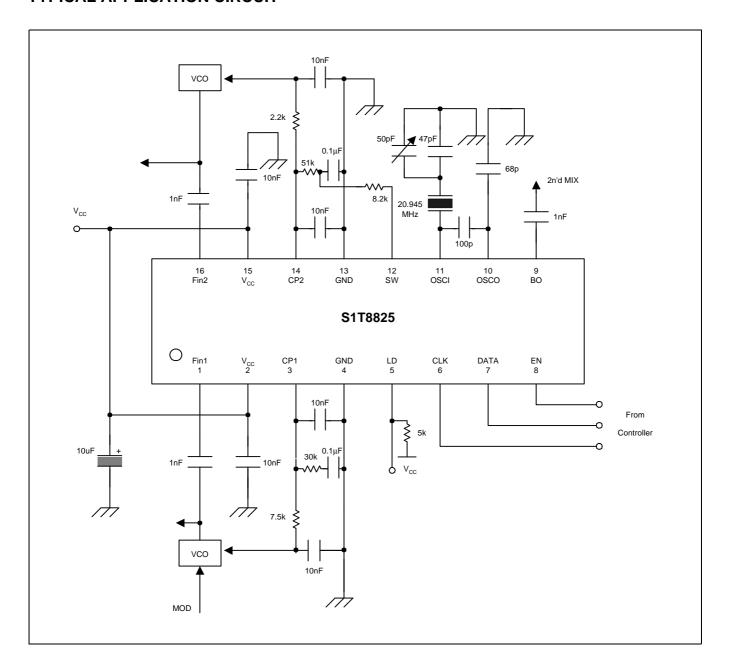

# **TYPICAL APPLICATION CIRCUIT**

**NOTES**